Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 64 x 8                                                                     |

| RAM Size                   | 36 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 6V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf83t-04-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 PIC16F8X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements the proper device option can be selected using the information in this section. When placing orders, please use the "PIC16F8X Product Identification System" at the back of this data sheet to specify the correct part number.

There are four device "types" as indicated in the device number.

- 1. **F**, as in PIC16**F**84. These devices have Flash program memory and operate over the standard voltage range.

- LF, as in PIC16LF84. These devices have Flash program memory and operate over an extended voltage range.

- 3. **CR**, as in PIC16**CR**83. These devices have ROM program memory and operate over the standard voltage range.

- 4. **LCR**, as in PIC16**LCR**84. These devices have ROM program memory and operate over an extended voltage range.

When discussing memory maps and other architectural features, the use of **F** and **CR** also implies the **LF** and **LCR** versions.

### 2.1 Flash Devices

These devices are offered in the lower cost plastic package, even though the device can be erased and reprogrammed. This allows the same device to be used for prototype development and pilot programs as well as production.

A further advantage of the electrically-erasable Flash version is that it can be erased and reprogrammed incircuit, or by device programmers, such as Microchip's PICSTART<sup>®</sup> Plus or PRO MATE<sup>®</sup> II programmers.

#### 2.2 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices have all Flash locations and configuration options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available.

For information on submitting a QTP code, please contact your Microchip Regional Sales Office.

### 2.3 <u>Serialized Quick-Turnaround-</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers the unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

For information on submitting a SQTP code, please contact your Microchip Regional Sales Office.

## 2.4 ROM Devices

Some of Microchip's devices have a corresponding device where the program memory is a ROM. These devices give a cost savings over Microchip's traditional user programmed devices (EPROM, EEPROM).

ROM devices (PIC16CR8X) do not allow serialization information in the program memory space. The user may program this information into the Data EEPROM.

For information on submitting a ROM code, please contact your Microchip Regional Sales Office.

# PIC16F8X

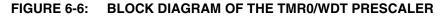

#### 4.2.2.2 OPTION\_REG REGISTER

The OPTION\_REG register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external INT interrupt, TMR0, and the weak pull-ups on PORTB.

## FIGURE 4-1: OPTION\_REG REGISTER (ADDRESS 81h)

**Note:** When the prescaler is assigned to the WDT (PSA = '1'), TMR0 has a 1:1 prescaler assignment.

| R/W-1            | R/W-1                                                                     | R/W-1            | R/W-1    | R/W-1      | R/W-1      | R/W-1    | R/W-1 |                                       |  |  |

|------------------|---------------------------------------------------------------------------|------------------|----------|------------|------------|----------|-------|---------------------------------------|--|--|

| RBPU             | INTEDG                                                                    | TOCS             | T0SE     | PSA        | PS2        | PS1      | PS0   | R = Readable bit                      |  |  |

| bit7             |                                                                           |                  |          |            |            |          | bit0  | W = Writable bit                      |  |  |

|                  |                                                                           |                  |          |            |            |          |       | U = Unimplemented bit,<br>read as '0' |  |  |

|                  |                                                                           |                  |          |            |            |          |       | - n = Value at POR reset              |  |  |

| bit 7:           |                                                                           |                  | ın Enabl | a hit      |            |          |       |                                       |  |  |

| Dit 7.           | <b>RBPU</b> : PORTB Pull-up Enable bit<br>1 = PORTB pull-ups are disabled |                  |          |            |            |          |       |                                       |  |  |

|                  | 0 = PORTB pull-ups are enabled (by individual port latch values)          |                  |          |            |            |          |       |                                       |  |  |

| bit 6:           | INTEDG:                                                                   |                  |          |            | ·          |          | ,     |                                       |  |  |

| bit 0.           | 1 = Interru                                                               | •                | •        |            | nin        |          |       |                                       |  |  |

|                  | 0 = Interru                                                               |                  |          |            |            |          |       |                                       |  |  |

| bit 5:           | TOCS: TM                                                                  |                  |          |            | F.         |          |       |                                       |  |  |

| Dit J.           | 1 = Transit                                                               |                  |          |            |            |          |       |                                       |  |  |

|                  | 0 = Interna                                                               |                  |          | •          | OUT)       |          |       |                                       |  |  |

| bit 4:           | TOSE: TM                                                                  |                  | •        |            |            |          |       |                                       |  |  |

| DIL 4.           |                                                                           |                  |          |            | on RA4/T00 |          |       |                                       |  |  |

|                  |                                                                           |                  |          |            | on RA4/T00 |          |       |                                       |  |  |

| bit 3:           | PSA: Pres                                                                 |                  | •        |            |            | <b>F</b> |       |                                       |  |  |

| DIL 3.           | 1 = Presca                                                                |                  |          |            |            |          |       |                                       |  |  |

|                  | 0 = Presca                                                                |                  |          |            |            |          |       |                                       |  |  |

| hit 2 0.         | PS2:PS0:                                                                  | •                |          |            |            |          |       |                                       |  |  |

| bit <u>∠</u> -0. |                                                                           |                  |          |            |            |          |       |                                       |  |  |

|                  | Bit Value                                                                 | TMR0 Ra          | te WD    | Γ Rate     |            |          |       |                                       |  |  |

|                  | 000                                                                       | 1:2              | 1 :      |            |            |          |       |                                       |  |  |

|                  | 001                                                                       | 1:4              | 1:       |            |            |          |       |                                       |  |  |

|                  | 010<br>011                                                                | 1:8              |          | : 4<br>: 8 |            |          |       |                                       |  |  |

|                  | 100                                                                       | 1 : 16<br>1 : 32 |          | 16         |            |          |       |                                       |  |  |

|                  | 101                                                                       | 1:64             |          | 32         |            |          |       |                                       |  |  |

|                  | 110                                                                       | 1 : 128          |          | 64         |            |          |       |                                       |  |  |

|                  | 111                                                                       | 1 : 256          | 1:       | 128        |            |          |       |                                       |  |  |

|                  |                                                                           |                  |          |            |            |          |       |                                       |  |  |

|                  |                                                                           |                  |          |            |            |          |       |                                       |  |  |

#### 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (i.e., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch is unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (i.e., BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output current may damage the chip.

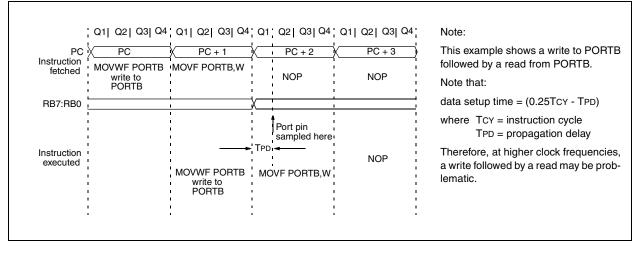

# 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-5). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such that the pin voltage stabilizes (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}\,,\,\,{\tt BSF},\, etc.)$  on an I/O port.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs ; PORTB<3:0> Outputs ;PORTB<7:6> have external pull-ups and are ;not connected to other circuitry

| ' |     |        |       |   |      |       |      |      |

|---|-----|--------|-------|---|------|-------|------|------|

| ; |     |        |       |   | PORT | latch | PORT | pins |

| ; |     |        |       |   |      |       |      |      |

|   | BCF | PORTB, | 7     | ; | 01pp | ppp   | 11pp | ppp  |

|   | BCF | PORTB, | 6     | ; | 10pp | ppp   | 11pp | ppp  |

|   | BSF | STATUS | , RPO | ; |      |       |      |      |

|   | BCF | TRISB, | 7     | ; | 10pp | ppp   | 11pp | ppp  |

|   | BCF | TRISB, | 6     | ; | 10pp | ppp   | 10pp | ppp  |

| : |     |        |       |   |      |       |      |      |

;Note that the user may have expected the ;pin values to be 00pp ppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

# FIGURE 5-5: SUCCESSIVE I/O OPERATION

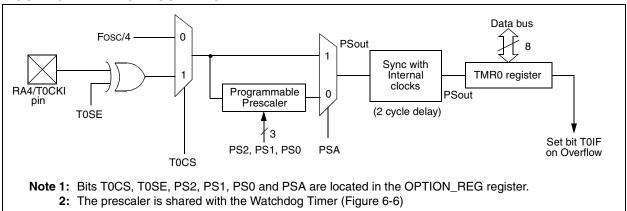

# 6.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Timer mode is selected by clearing the TOCS bit (OPTION\_REG<5>). In timer mode, the Timer0 module (Figure 6-1) will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

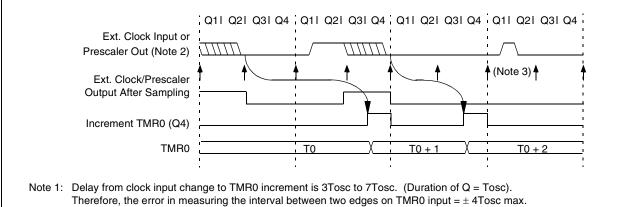

Counter mode is selected by setting the T0CS bit (OPTION\_REG<5>). In this mode TMR0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the T0 source

FIGURE 6-1: TMR0 BLOCK DIAGRAM

edge select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

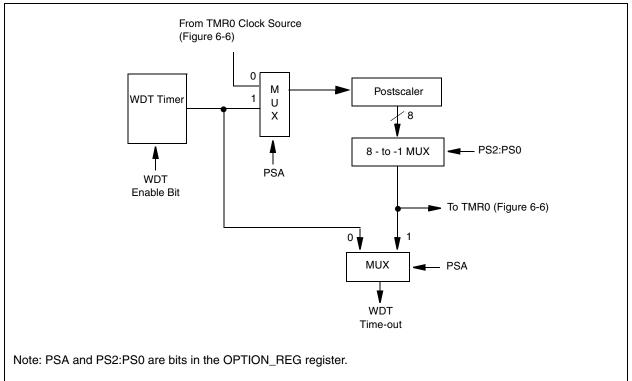

The prescaler is shared between the Timer0 Module and the Watchdog Timer. The prescaler assignment is controlled, in software, by control bit PSA (OPTION\_REG<3>). Clearing bit PSA will assign the prescaler to the Timer0 Module. The prescaler is not readable or writable. When the prescaler (Section 6.3) is assigned to the Timer0 Module, the prescale value (1:2, 1:4, ..., 1:256) is software selectable.

### 6.1 TMR0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets the T0IF bit (INTCON<2>). The interrupt can be masked by clearing enable bit T0IE (INTCON<5>). The T0IF bit must be cleared in software by the Timer0 Module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt (Figure 6-4) cannot wake the processor from SLEEP since the timer is shut off during SLEEP.

# FIGURE 6-2: TMR0 TIMING: INTERNAL CLOCK/NO PRESCALER

|                         | I    | 1                | 1                      | 1                      | 1                      | 1 1                    | . I                        |                            |

|-------------------------|------|------------------|------------------------|------------------------|------------------------|------------------------|----------------------------|----------------------------|

| PC                      | PC-1 | ) PC             | PC+1                   | PC+2                   | PC+3                   | PC+4                   | PC+5 X                     | PC+6                       |

| Instruction<br>Fetch    |      | MOVWF TMR0       | MOVF TMR0,W                |                            |

| TMR0                    |      | Τ0+1 χ           | Τ0+2 χ                 | ΝΤΟ Χ                  | ΝΤΟ χ                  | ΝΤΟ Χ                  | NT0+1                      | NT0+2 X                    |

| Instruction<br>Executed |      | 1<br>1<br>1<br>1 | Write TMR0<br>executed | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1 | Read TMR0<br>reads NT0 + 2 |

2: External clock if no prescaler selected, Prescaler output otherwise.

3: The arrows ↑ indicate where sampling occurs. A small clock pulse may be missed by sampling.

FIGURE 8-2: CONFIGURATION WORD - PIC16F83 AND PIC16F84

|          |       |                                  |          |           |         |         | R/P-u |    | R/P-u | R/P-u | R/P-u | R/P-u   | R/P-u      |   |

|----------|-------|----------------------------------|----------|-----------|---------|---------|-------|----|-------|-------|-------|---------|------------|---|

| CP       | CP    | CP                               | CP       | CP        | CP      | CP      | CP    | CP | CP    | PWRTE | WDTE  | FOSC1   | FOSC0      |   |

| bit13    |       |                                  |          |           |         |         |       |    |       |       |       |         | bit0       |   |

|          |       |                                  |          |           |         |         |       |    |       |       |       | R = Rea | adable bit |   |

|          |       |                                  |          |           |         |         |       |    |       |       |       |         | grammabl   |   |

|          |       |                                  |          |           |         |         |       |    |       |       |       |         | ue at POR  |   |

|          |       | ~                                |          |           |         |         |       |    |       |       |       | u =     | unchange   | a |

| bit 13:4 |       |                                  |          |           |         |         |       |    |       |       |       |         |            |   |

|          |       | Code p                           |          |           |         | ما      |       |    |       |       |       |         |            |   |

|          |       | 0 = All memory is code protected |          |           |         |         |       |    |       |       |       |         |            |   |

| bit 3    |       | PWRTE: Power-up Timer Enable bit |          |           |         |         |       |    |       |       |       |         |            |   |

|          |       | 1 = Power-up timer is disabled   |          |           |         |         |       |    |       |       |       |         |            |   |

|          | 0 = I | Power-                           | up time  | er is ena | abled   |         |       |    |       |       |       |         |            |   |

| bit 2    | WD.   | TE: Wa                           | tchdog   | Timer     | Enable  | e bit   |       |    |       |       |       |         |            |   |

|          | 1 = \ | WDT e                            | nabled   |           |         |         |       |    |       |       |       |         |            |   |

|          | 0 = 1 | WDT di                           | isabled  |           |         |         |       |    |       |       |       |         |            |   |

| bit 1:0  | FOS   | C1:FO                            | SCO.     | Oscillat  | or Sele | ction b | its   |    |       |       |       |         |            |   |

| 511 110  |       | = RC 05                          |          |           |         |         | 110   |    |       |       |       |         |            |   |

|          |       | = HS os                          |          |           |         |         |       |    |       |       |       |         |            |   |

|          |       | = XT os                          |          |           |         |         |       |    |       |       |       |         |            |   |

|          | 00 =  | = LP os                          | cillator |           |         |         |       |    |       |       |       |         |            |   |

|          |       |                                  |          |           |         |         |       |    |       |       |       |         |            |   |

#### 8.2 Oscillator Configurations

#### 8.2.1 OSCILLATOR TYPES

The PIC16F8X can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

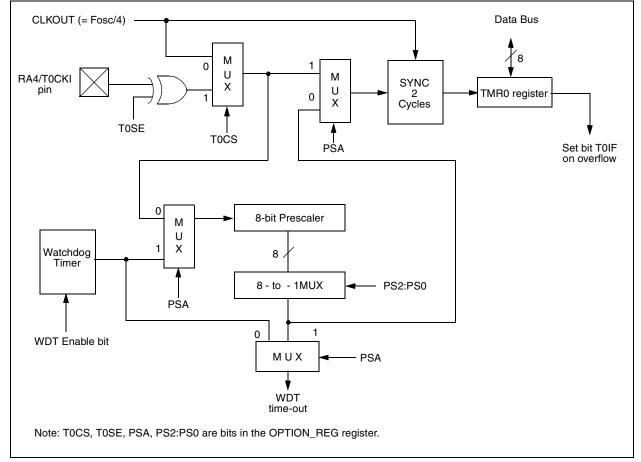

- 8.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 8-3).

#### FIGURE 8-3: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

The PIC16F8X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/CLKIN pin (Figure 8-4).

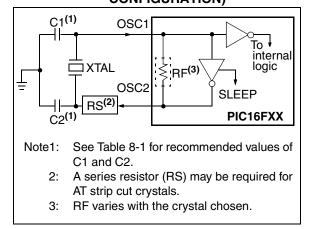

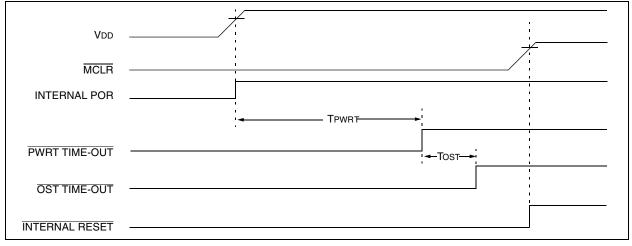

FIGURE 8-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

### FIGURE 8-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

#### 8.7 <u>Time-out Sequence and Power-down</u> Status Bits (TO/PD)

On power-up (Figure 8-10, Figure 8-11, Figure 8-12 and Figure 8-13) the time-out sequence is as follows: First PWRT time-out is invoked after a POR has expired. Then the OST is activated. The total time-out will vary based on oscillator configuration and PWRTE configuration bit status. For example, in RC mode with the PWRT disabled, there will be no time-out at all.

# TABLE 8-5TIME-OUT IN VARIOUSSITUATIONS

| Oscillator    | Powe                | er-up            | Wake-up       |

|---------------|---------------------|------------------|---------------|

| Configuration | PWRT<br>Enabled     | PWRT<br>Disabled | from<br>SLEEP |

| XT, HS, LP    | 72 ms +<br>1024Tosc | 1024Tosc         | 1024Tosc      |

| RC            | 72 ms               | _                | _             |

Since the time-outs occur from the POR reset pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high, execution will begin immediately (Figure 8-10). This is useful for testing purposes or to synchronize more than one PIC16F8X device when operating in parallel.

Table 8-6 shows the significance of the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits. Table 8-3 lists the reset conditions for some special registers, while Table 8-4 lists the reset conditions for all the registers.

# TABLE 8-6STATUS BITS AND THEIRSIGNIFICANCE

| то | PD | Condition                                                         |

|----|----|-------------------------------------------------------------------|

| 1  | 1  | Power-on Reset                                                    |

| 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| x  | 0  | Illegal, PD is set on POR                                         |

| 0  | 1  | WDT Reset (during normal operation)                               |

| 0  | 0  | WDT Wake-up                                                       |

| 1  | 1  | MCLR Reset during normal operation                                |

| 1  | 0  | MCLR Reset during SLEEP or interrupt                              |

|    |    | wake-up from SLEEP                                                |

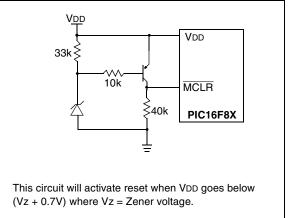

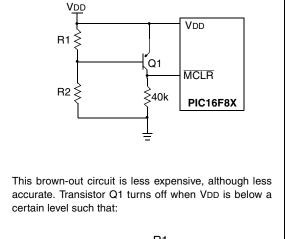

# 8.8 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

To reset a PIC16F8X device when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 8-14 and Figure 8-15.

### FIGURE 8-14: BROWN-OUT PROTECTION CIRCUIT 1

### FIGURE 8-15: BROWN-OUT PROTECTION CIRCUIT 2

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

#### 8.11 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation a WDT time-out generates a device RESET. If the device is in SLEEP mode, a WDT Wake-up causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming configuration bit WDTE as a '0' (Section 8.1).

#### 8.11.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to

FIGURE 8-18: WATCHDOG TIMER BLOCK DIAGRAM

part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION\_REG register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out and generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a WDT time-out.

8.11.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

### TABLE 8-7 SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name           | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|----------------|-------|--------|-------|-------|----------------------|-------|-------|-------|-------------------------------|---------------------------|

| 2007h   | Config. bits   | (2)   | (2)    | (2)   | (2)   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 | (2)                           |                           |

| 81h     | OPTION_<br>REG | RBPU  | INTEDG | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                 |

Legend: x = unknown. Shaded cells are not used by the WDT.

Note 1: See Figure 8-1 and Figure 8-2 for operation of the PWRTE bit.

2: See Figure 8-1, Figure 8-2 and Section 8.13 for operation of the Code and Data protection bits.

#### 8.12 Power-down Mode (SLEEP)

A device may be powered down (SLEEP) and later powered up (Wake-up from SLEEP).

#### 8.12.1 SLEEP

The Power-down mode is entered by executing the SLEEP instruction.

If enabled, the Watchdog Timer is cleared (but keeps running), the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  bit (STATUS<4>) is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For the lowest current consumption in SLEEP mode, place all I/O pins at either at VDD or VSS, with no external circuitry drawing current from the I/O pins, and disable external clocks. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

It should be noted that a RESET generated by a WDT time-out does not drive the MCLR pin low.

#### 8.12.2 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. WDT Wake-up (if WDT was enabled).

- 3. Interrupt from RB0/INT pin, RB port change, or data EEPROM write complete.

Peripherals cannot generate interrupts during SLEEP, since no on-chip Q clocks are present.

The first event ( $\overline{\text{MCLR}}$  reset) will cause a device reset. The two latter events are considered a continuation of program execution. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits can be used to determine the cause of a device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

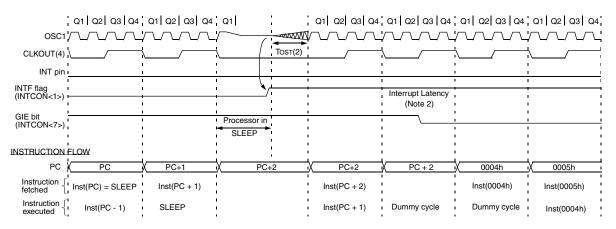

While the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up occurs regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the state of the substant during the state of the substant the instruction after the state of the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

# FIGURE 8-19: WAKE-UP FROM SLEEP THROUGH INTERRUPT

Note 1: XT, HS or LP oscillator mode assumed.

2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 10.4 DC CHARACTERISTICS: PIC16F84, PIC16F83 (Commercial, Industrial) PIC16LF84, PIC16F83 (Commercial, Industrial)

| DC Characteristics<br>All Pins Except<br>Power Supply Pins |       |                                                        | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial)Operating voltage VDD range as described in DC specSection 10.1 and Section 10.2.MinTyptMaxUnitsConditions |                     |             |       |                                                                         |  |  |

|------------------------------------------------------------|-------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|-------|-------------------------------------------------------------------------|--|--|

| Parameter<br>No.                                           | Sym   | Characteristic                                         | Min                                                                                                                                                                                                                                                                                              | Тур†                | Мах         | Units | Conditions                                                              |  |  |

| D100                                                       | Cosc2 | Capacitive Loading Specs<br>on Output Pins<br>OSC2 pin | _                                                                                                                                                                                                                                                                                                | _                   | 15          | pF    | In XT, HS and LP modes<br>when external clock is used to<br>drive OSC1. |  |  |

| D101                                                       | Сю    | All I/O pins and OSC2<br>(RC mode)                     | —                                                                                                                                                                                                                                                                                                | _                   | 50          | pF    |                                                                         |  |  |

|                                                            |       | Data EEPROM Memory                                     |                                                                                                                                                                                                                                                                                                  |                     |             |       | $\langle \vee \rangle \rangle$                                          |  |  |

| D120                                                       | ED    | Endurance                                              | 1M                                                                                                                                                                                                                                                                                               | 10M                 | —           | EAW   | 25°C at 5V                                                              |  |  |

| D121                                                       | Vdrw  | VDD for read/write                                     | VMIN                                                                                                                                                                                                                                                                                             | —                   | 6.0         | V     | VMIN = Minimum operating                                                |  |  |

| D122                                                       | TDEW  | Erase/Write cycle time                                 | —                                                                                                                                                                                                                                                                                                | 10                  | <b>2</b> 0* | miş∖  |                                                                         |  |  |

|                                                            |       | Program Flash Memory                                   |                                                                                                                                                                                                                                                                                                  | ~                   |             |       |                                                                         |  |  |

| D130                                                       | Eр    | Endurance                                              | 100                                                                                                                                                                                                                                                                                              | 1000                |             | ÈXW   | /                                                                       |  |  |

| D131                                                       | Vpr   | VDD for read                                           | VMIN                                                                                                                                                                                                                                                                                             | $\langle  \rangle$  | 6.0         | V     | VMIN = Minimum operating voltage                                        |  |  |

| D132                                                       | VPEW  | VDD for erase/write                                    | 4.5                                                                                                                                                                                                                                                                                              | $\langle - \rangle$ | 5.5         | V     |                                                                         |  |  |

| D133                                                       | TPEW  | Erase/Write cycle time                                 | $  - \rangle$                                                                                                                                                                                                                                                                                    | 10                  | $\searrow$  | ms    |                                                                         |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

DS30430D-page 11-80

#### 11.2 DC CHARACTERISTICS: PIC16LCR84, PIC16LCR83 (Commercial, Industrial)

| DC Charac<br>Power Sup |      | -                                                                |       |      | ditions (unless otherwise stated)<br>$^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial)<br>$^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial) |              |                                                                                   |

|------------------------|------|------------------------------------------------------------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------|

| Parameter<br>No.       | Sym  | Characteristic                                                   | Min   | Тур† | Мах                                                                                                                                           | Units        | Conditions                                                                        |

| D001                   | Vdd  | Supply Voltage                                                   | 2.0   | —    | 6.0                                                                                                                                           | V            | XT, RC, and LP osc configuration                                                  |

| D002                   | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5*  | _    | —                                                                                                                                             | V            | Device in SLEEP mode                                                              |

| D003                   | VPOR | VDD start voltage to<br>ensure internal<br>Power-on Reset signal | _     | Vss  | _                                                                                                                                             | V            | See section on Power-on Reset for details                                         |

| D004                   | Svdd | VDD rise rate to ensure<br>internal Power-on<br>Reset signal     | 0.05* | —    | _                                                                                                                                             | V/ms         | See section on Power-on-Reset for details                                         |

|                        | Idd  | Supply Current <sup>(2)</sup>                                    |       |      |                                                                                                                                               |              | RC and XT osc configuration <sup>(4)</sup>                                        |

| D010                   |      |                                                                  | —     | 1    | 4                                                                                                                                             | mA           | FOSC = 2.0 MHz, $VDD = 5.5V$                                                      |

| D010A                  |      |                                                                  | -     | 7.3  | 10                                                                                                                                            | mA           | Fosc = 2.0 MHz, VDD = 5.5V<br>(During EEPROM programming)<br>LP oso configuration |

| D014                   |      |                                                                  | —     | 15   | 45                                                                                                                                            | μ <b>Α</b> < | Fosc = 32 kHz, VDD = 2.0V,<br>WDT disabled                                        |

| D020                   | IPD  | Power-down Current <sup>(3)</sup>                                | —     | 3.0  | 16                                                                                                                                            | μ <b>Α</b>   | $V_{RD} = 2.0 $ WDT enabled, industrial                                           |

| D021                   |      |                                                                  | —     | 0.4  | 5.0                                                                                                                                           | <μA_         | VDD = 2.QV, WDT disabled, commercial                                              |

| D021A                  |      |                                                                  | —     | 0.4  | <u>ę</u> .0                                                                                                                                   | μÀ           | VDD = 2.0V, WDT disabled, industrial                                              |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEER mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1=external square waye, from rail to rail; all I/O pins tristated, pulled to VDD, TOCKI = VDD,

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula IR =/Vpb/2Rext (mA) with Rext in kOhm.

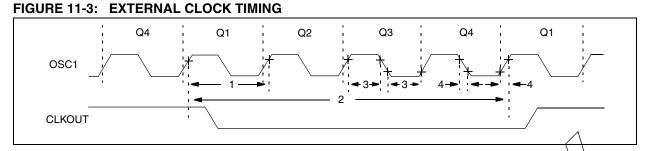

#### **Timing Diagrams and Specifications** 11.5

#### **TABLE 11-3 EXTERNAL CLOCK TIMING REQUIREMENTS**

| Parameter<br>No. | Sym                | Characteristic                          | Min   | Тур†                                          | Мах                 | Units | Co         | onditions     |

|------------------|--------------------|-----------------------------------------|-------|-----------------------------------------------|---------------------|-------|------------|---------------|

|                  | Fosc               | External CLKIN Frequency <sup>(1)</sup> | DC    |                                               | 2                   | MHz   | XT, RC osc | PIQ16LCR8X-04 |

|                  |                    |                                         | DC    | —                                             | 4                   | MHz   | XT, RC OSC | RIC76CR8X-04  |

|                  |                    |                                         | DC    | _                                             | 10                  | MHz   | HS osc     | PIC16CR8X-10  |

|                  |                    |                                         | DC    | —                                             | 200                 | ( kңz | 1⊾₽ osc 🗸  | PIC16LCR8X-04 |

|                  |                    | Oscillator Frequency <sup>(1)</sup>     | DC    |                                               | 2                   | МНя   | RG osc     | PIC16LCR8X-04 |

|                  |                    |                                         | DC    | _                                             | $\langle 4 \rangle$ | \ ·   | RC osc     | PIC16CR8X-04  |

|                  |                    |                                         | 0.1   | -~                                            | 2                   | MHz   | XT osc     | PIC16LCR8X-04 |

|                  |                    |                                         | 0.1   | $\prec$                                       | 4                   | MHz   | XT osc     | PIC16CR8X-04  |

|                  |                    |                                         | 1.0   |                                               | 10                  | MHz   | HS osc     | PIC16CR8X-10  |

|                  |                    |                                         | DČ    | $\setminus - \setminus$                       | 200                 | kHz   | LP osc     | PIC16LCR8X-04 |

| 1                | Tosc               | External CLKIN Period <sup>(1)</sup>    | \$00  | $\langle                                    $ | $\searrow$          | ns    | XT, RC osc | PIC16LCR8X-04 |

|                  |                    |                                         | 250   | $\langle \mathcal{F} \rangle$                 | $\sim -$            | ns    | XT, RC osc | PIC16CR8X-04  |

|                  |                    |                                         | 100   | $\langle - \rangle$                           | —                   | ns    | HS osc     | PIC16CR8X-10  |

|                  |                    | $\land$                                 | 5.0   |                                               | _                   | μs    | LP osc     | PIC16LCR8X-04 |

|                  |                    | Oscillator Period <sup>(1)</sup>        | 500   | <u> </u>                                      | _                   | ns    | RC osc     | PIC16LCR8X-04 |

|                  |                    |                                         | 250   | —                                             | —                   | ns    | RC osc     | PIC16CR8X-04  |

|                  |                    |                                         | >500  | —                                             | 10,000              | ns    | XT osc     | PIC16LCR8X-04 |

|                  |                    | $\land \land \land \land$               | 250   | —                                             | 10,000              | ns    | XT osc     | PIC16CR8X-04  |

|                  |                    |                                         | 100   | —                                             | 1,000               | ns    | HS osc     | PIC16CR8X-10  |

|                  |                    |                                         | 5.0   |                                               | —                   | μs    | LP osc     | PIC16LCR8X-04 |

| 2                | Тсү                | Instruction Cycle Time <sup>(1)</sup>   | 0.4   | 4/Fosc                                        | DC                  | μs    |            |               |

| 3                | TosL, /            | Clock in (QSC1) High or Low             | 60 *  |                                               |                     | ns    | XT osc     | PIC16LCR8X-04 |

|                  | TosH               | Time                                    | 50 *  | —                                             | —                   | ns    | XT osc     | PIC16CR8X-04  |

|                  | $ \langle \langle$ | $\checkmark \land \checkmark$           | 2.0 * | —                                             | —                   | μs    | LP osc     | PIC16LCR8X-04 |

|                  |                    | $\langle \checkmark$                    | 35 *  | _                                             |                     | ns    | HS osc     | PIC16CR8X-10  |

| 4                | JosR,              | Clock in (OSC1) Rise or Fall Time       | 25 *  | _                                             | —                   | ns    | XT osc     | PIC16CR8X-04  |

|                  | Tos⊭               | $\sim$                                  | 50 *  | —                                             | —                   | ns    | LP osc     | PIC16LCR8X-04 |

|                  |                    |                                         | 15 *  |                                               | _                   | ns    | HS osc     | PIC16CR8X-10  |

These parameters are characterized but not tested.

Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only + and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1 pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

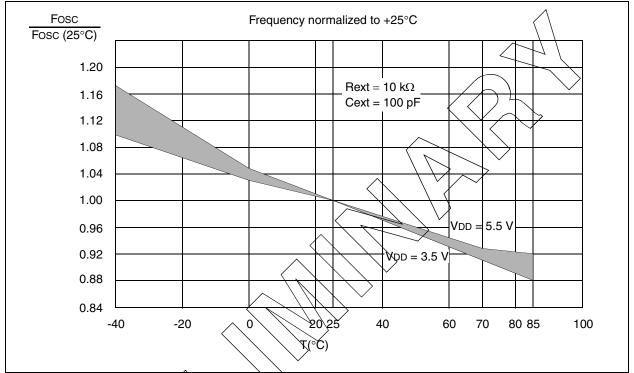

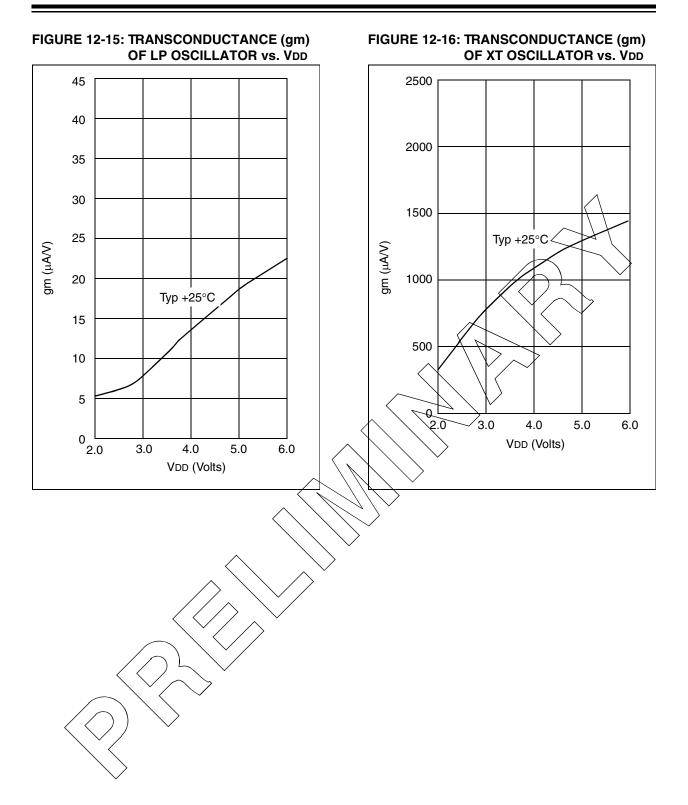

# 12.0 DC & AC CHARACTERISTICS GRAPHS/TABLES

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are guaranteed to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at  $25^{\circ}$ C, while 'max' or 'min' represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation.

FIGURE 12-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

|                   | RC OSCILLATOR  |             |

|-------------------|----------------|-------------|

| <b>TABLE 12-1</b> | RC OSCILLAI OR | FREQUENCIES |

|                   |                |             |

| Cext                              | Rext   | Average<br>Fosc @ 5V, 25°C |                        |

|-----------------------------------|--------|----------------------------|------------------------|

|                                   |        |                            | Part to Part Variation |

| 20 pF                             | 5 k    | 4.61 MHz                   | ± 25%                  |

|                                   | → 10 k | 2.66 MHz                   | ± 24%                  |

|                                   | 100 k  | 311 kHz                    | $\pm$ 39%              |

|                                   | 5 k    | 1.34 MHz                   | ± 21%                  |

| $\langle \langle \rangle \rangle$ | 10 k   | 756 kHz                    | ± 18%                  |

| $\square$                         | 100 k  | 82.8 kHz                   | ± 28%                  |

| 300 pF                            | 5 k    | 428 kHz                    | ± 13%                  |

| $\sim$                            | 10 k   | 243 kHz                    | ± 13%                  |

|                                   | 100 k  | 26.2 kHz                   | ± 23%                  |

\* Measured on DIP packages. The percentage variation indicated here is part-to-part variation due to normal process distribution. The variation indicated is ±3 standard deviation from average value for full VDD range.

# PIC16F8X