#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 13                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | 68 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf84-04-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC16F8X. These are the program memory and the data memory. Each block has its own bus, so that access to each block can occur during the same oscillator cycle.

The data memory can further be broken down into the general purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

The data memory area also contains the data EEPROM memory. This memory is not directly mapped into the data memory, but is indirectly mapped. That is, an indirect address pointer specifies the address of the data EEPROM memory to read/write. The 64 bytes of data EEPROM memory have the address range 0h-3Fh. More details on the EEPROM memory can be found in Section 7.0.

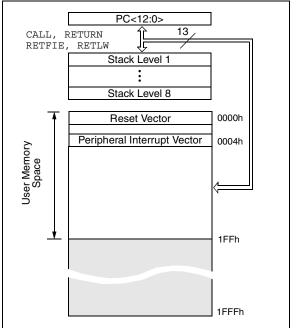

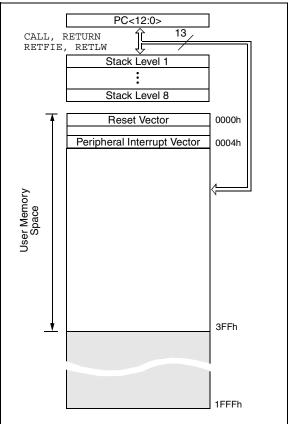

#### 4.1 Program Memory Organization

The PIC16FXX has a 13-bit program counter capable of addressing an 8K x 14 program memory space. For the PIC16F83 and PIC16CR83, the first 512 x 14 (0000h-01FFh) are physically implemented (Figure 4-1). For the PIC16F84 and PIC16CR84, the first 1K x 14 (0000h-03FFh) are physically implemented (Figure 4-2). Accessing a location above the physically implemented address will cause a wraparound. For example, for the PIC16F84 locations 20h, 420h, 820h, C20h, 1020h, 1420h, 1820h, and 1C20h will be the same instruction.

The reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK-PIC16F83/CR83

#### FIGURE 4-2: PROGRAM MEMORY MAP AND STACK - PIC16F84/CR84

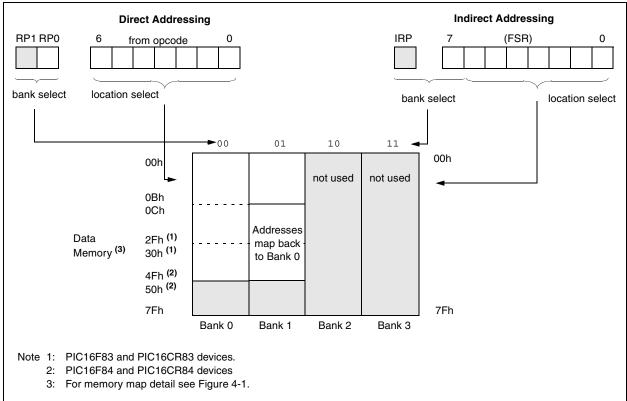

#### 4.5 Indirect Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### EXAMPLE 4-1: INDIRECT ADDRESSING

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

FIGURE 4-1: DIRECT/INDIRECT ADDRESSING

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-2.

#### EXAMPLE 4-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | movlw | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | movwf | FSR   | ; to RAM             |

| NEXT     | clrf  | INDF  | ;clear INDF register |

|          | incf  | FSR   | ;inc pointer         |

|          | btfss | FSR,4 | ;all done?           |

|          | goto  | NEXT  | ;NO, clear next      |

| CONTINUE |       |       |                      |

|          | :     |       | ;YES, continue       |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-1. However, IRP is not used in the PIC16F8X.

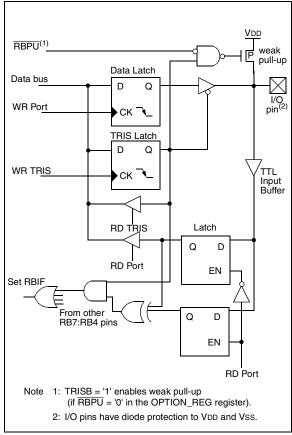

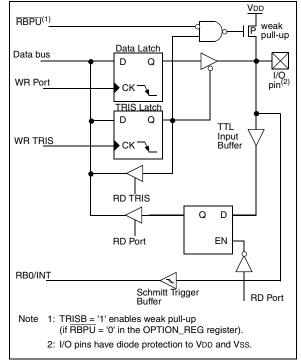

### 5.2 **PORTB and TRISB Registers**

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. A '1' on any bit in the TRISB register puts the corresponding output driver in a hi-impedance mode. A '0' on any bit in the TRISB register puts the contents of the output latch on the selected pin(s).

Each of the PORTB pins have a weak internal pull-up. A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION\_REG<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The pins value in input mode are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of the pins are OR'ed together to generate the RB port change interrupt.

#### FIGURE 5-3: BLOCK DIAGRAM OF PINS RB7:RB4

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Read (or write) PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set the RBIF bit. Reading PORTB will end the mismatch condition, and allow the RBIF bit to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression (see AN552 in the Embedded Control Handbook).

Note 1: For a change on the I/O pin to be recognized, the pulse width must be at least TcY (4/fosc) wide.

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

#### FIGURE 5-4: BLOCK DIAGRAM OF PINS RB3:RB0

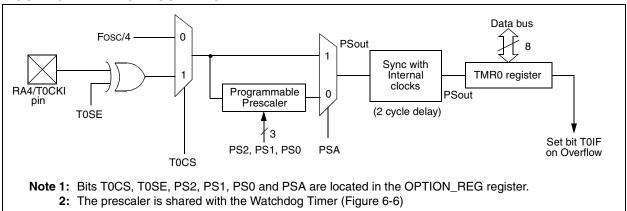

## 6.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Timer mode is selected by clearing the TOCS bit (OPTION\_REG<5>). In timer mode, the Timer0 module (Figure 6-1) will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION\_REG<5>). In this mode TMR0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the T0 source

FIGURE 6-1: TMR0 BLOCK DIAGRAM

edge select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is shared between the Timer0 Module and the Watchdog Timer. The prescaler assignment is controlled, in software, by control bit PSA (OPTION\_REG<3>). Clearing bit PSA will assign the prescaler to the Timer0 Module. The prescaler is not readable or writable. When the prescaler (Section 6.3) is assigned to the Timer0 Module, the prescale value (1:2, 1:4, ..., 1:256) is software selectable.

### 6.1 TMR0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets the T0IF bit (INTCON<2>). The interrupt can be masked by clearing enable bit T0IE (INTCON<5>). The T0IF bit must be cleared in software by the Timer0 Module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt (Figure 6-4) cannot wake the processor from SLEEP since the timer is shut off during SLEEP.

## FIGURE 6-2: TMR0 TIMING: INTERNAL CLOCK/NO PRESCALER

|                         | I    | 1                | 1                      | 1                      | 1                      | 1 1                    | · · · · · · · · · · · · · · · · · · · |                            |

|-------------------------|------|------------------|------------------------|------------------------|------------------------|------------------------|---------------------------------------|----------------------------|

| PC                      | PC-1 | ) PC             | PC+1                   | PC+2                   | PC+3                   | PC+4                   | PC+5 X                                | PC+6                       |

| Instruction<br>Fetch    |      | MOVWF TMR0       | MOVF TMR0,W                           |                            |

| TMR0                    |      | Τ0+1 χ           | Τ0+2 χ                 | ΝΤΟ Χ                  | ΝΤΟ χ                  | ΝΤΟ Χ                  | NT0+1                                 | NT0+2 X                    |

| Instruction<br>Executed |      | 1<br>1<br>1<br>1 | Write TMR0<br>executed | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1            | Read TMR0<br>reads NT0 + 2 |

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution).

Note: To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be taken even if the WDT is disabled. To change prescaler from the WDT to the Timer0 module use the sequence shown in Example 6-2.

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

|        | •           | ,                |

|--------|-------------|------------------|

| BCF    | STATUS, RPO | ;Bank 0          |

| CLRF   | TMR0        | ;Clear TMR0      |

|        |             | ; and Prescaler  |

| BSF    | STATUS, RPO | ;Bank 1          |

| CLRWDT |             | ;Clears WDT      |

| MOVLW  | b'xxxx1xxx' | ;Select new      |

| MOVWF  | OPTION_REG  | ; prescale value |

| BCF    | STATUS, RPO | ;Bank 0          |

|        |             |                  |

#### EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

|        | (=.         | / · · · · · · · · · · · · · · · · · · · |

|--------|-------------|-----------------------------------------|

| CLRWDT |             | ;Clear WDT and                          |

|        |             | ; prescaler                             |

| BSF    | STATUS, RPO | ;Bank 1                                 |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new                       |

|        |             | ; prescale value                        |

|        |             | ' and clock source                      |

| MOVWF  | OPTION_REG  | ;                                       |

| BCF    | STATUS, RPO | ;Bank 0                                 |

|        |             |                                         |

| Address | Name           | Bit 7 | Bit 6                    | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1     | Bit 0     | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|----------------|-------|--------------------------|-------|--------|--------|--------|-----------|-----------|-------------------------------|---------------------------|

| 01h     | TMR0           |       | Timer0 module's register |       |        |        |        | xxxx xxxx | uuuu uuuu |                               |                           |

| 0Bh     | INTCON         | GIE   | EEIE                     | TOIE  | INTE   | RBIE   | T0IF   | INTF      | RBIF      | 0000 000x                     | 0000 0000                 |

| 81h     | OPTION_<br>REG | RBPU  | INTEDG                   | TOCS  | TOSE   | PSA    | PS2    | PS1       | PS0       | 1111 1111                     | 1111 1111                 |

| 85h     | TRISA          | _     | _                        | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1    | TRISA0    | 1 1111                        | 1 1111                    |

## TABLE 6-1 REGISTERS ASSOCIATED WITH TIMER0

Legend: x = unknown, u = unchanged. - = unimplemented read as '0'. Shaded cells are not associated with Timer0.

### 8.10 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users wish to save key register values during an interrupt (e.g., W register and STATUS register). This is implemented in software.

Example 8-1 stores and restores the STATUS and W register's values. The User defined registers, W\_TEMP and STATUS\_TEMP are the temporary storage locations for the W and STATUS registers values.

Example 8-1 does the following:

- a) Stores the W register.

- b) Stores the STATUS register in STATUS\_TEMP.

- c) Executes the Interrupt Service Routine code.

- d) Restores the STATUS (and bank select bit) register.

- e) Restores the W register.

#### EXAMPLE 8-1: SAVING STATUS AND W REGISTERS IN RAM

| PUSH | MOVWF               | W_TEMP                   | ; Copy W to TEMP register,                                                                                                                   |

|------|---------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|      | SWAPF               | STATUS, W                | ; Swap status to be saved into W                                                                                                             |

|      | MOVWF               | STATUS_TEMP              | ; Save status to STATUS_TEMP register                                                                                                        |

| ISR  | :                   |                          | :<br>; Interrupt Service Routine<br>; should configure Bank as required                                                                      |

| POP  | :<br>SWAPF<br>MOVWF | STATUS_TEMP, W<br>STATUS | ;<br>; Swap nibbles in STATUS_TEMP register<br>; and place result into W<br>; Move W into STATUS register<br>; (sets bank to original state) |

|      | SWAPF               | W_TEMP, F                | ; Swap nibbles in W_TEMP and place result in W_TEMP                                                                                          |

|      | SWAPF               | W_TEMP, W                | ; Swap nibbles in W_TEMP and place result into W                                                                                             |

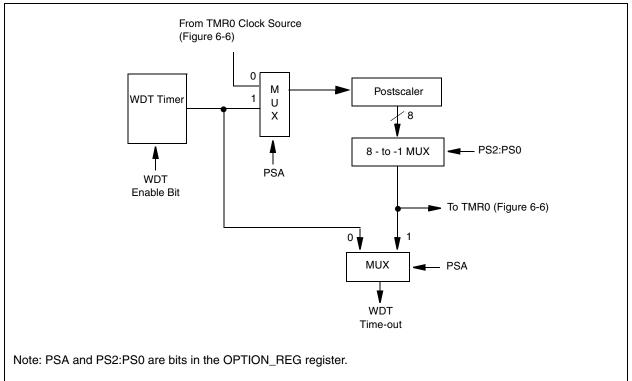

#### 8.11 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation a WDT time-out generates a device RESET. If the device is in SLEEP mode, a WDT Wake-up causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming configuration bit WDTE as a '0' (Section 8.1).

#### 8.11.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to

FIGURE 8-18: WATCHDOG TIMER BLOCK DIAGRAM

part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION\_REG register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out and generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a WDT time-out.

8.11.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

### TABLE 8-7 SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name           | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|----------------|-------|--------|-------|-------|----------------------|-------|-------|-------|-------------------------------|---------------------------|

| 2007h   | Config. bits   | (2)   | (2)    | (2)   | (2)   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 | (2)                           |                           |

| 81h     | OPTION_<br>REG | RBPU  | INTEDG | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                 |

Legend: x = unknown. Shaded cells are not used by the WDT.

Note 1: See Figure 8-1 and Figure 8-2 for operation of the PWRTE bit.

2: See Figure 8-1, Figure 8-2 and Section 8.13 for operation of the Code and Data protection bits.

# PIC16F8X

| IORWF             | Inclusive                                                      | OR W                         | with f           |                      |

|-------------------|----------------------------------------------------------------|------------------------------|------------------|----------------------|

| Syntax:           | [ label ]                                                      | IORWF                        | f,d              |                      |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$ | 27                           |                  |                      |

| Operation:        | (W) .OR.                                                       | $(f) \rightarrow (de)$       | estinatior       | ı)                   |

| Status Affected:  | Z                                                              |                              |                  |                      |

| Encoding:         | 00                                                             | 0100                         | dfff             | ffff                 |

| Description:      | Inclusive C<br>ter 'f'. If 'd'<br>W register<br>back in reg    | is 0 the re<br>. If 'd' is 1 | sult is place    | ced in the           |

| Words:            | 1                                                              |                              |                  |                      |

| Cycles:           | 1                                                              |                              |                  |                      |

| Q Cycle Activity: | Q1                                                             | Q2                           | Q3               | Q4                   |

|                   | Decode                                                         | Read<br>register<br>'f'      | Process<br>data  | Write to destination |

| Example           | IORWF                                                          |                              | RESULT,          | 0                    |

|                   | Before In                                                      |                              |                  |                      |

|                   |                                                                | RESULT<br>W                  | = 0x13<br>= 0x91 | -                    |

|                   | After Inst                                                     | ••                           |                  | 3                    |

| MOVLW             | Move Lite                              | eral to V                         | v               |               |

|-------------------|----------------------------------------|-----------------------------------|-----------------|---------------|

| Syntax:           | [ label ]                              | MOVLW                             | / k             |               |

| Operands:         | $0 \le k \le 25$                       | 55                                |                 |               |

| Operation:        | $k \to (W)$                            |                                   |                 |               |

| Status Affected:  | None                                   |                                   |                 |               |

| Encoding:         | 11                                     | 00xx                              | kkkk            | kkkk          |

| Description:      | The eight b<br>register. Th<br>as 0's. |                                   |                 |               |

| Words:            | 1                                      |                                   |                 |               |

| Cycles:           | 1                                      |                                   |                 |               |

| Q Cycle Activity: | Q1                                     | Q2                                | Q3              | Q4            |

|                   | Decode                                 | Read<br>literal 'k'               | Process<br>data | Write to<br>W |

| Example           | MOVLW<br>After Instr                   | <sup>0x5A</sup><br>ruction<br>N = | 0x5A            |               |

| MOVF              | Move f                                                                                                                                                                                                                                                          |                         |                 |                      |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|----------------------|--|

| Syntax:           | [ label ]                                                                                                                                                                                                                                                       | MOVF                    | f,d             |                      |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                  | 7                       |                 |                      |  |

| Operation:        | (f) $\rightarrow$ (des                                                                                                                                                                                                                                          | stination               | )               |                      |  |

| Status Affected:  | Z                                                                                                                                                                                                                                                               |                         |                 |                      |  |

| Encoding:         | 00                                                                                                                                                                                                                                                              | 1000                    | dfff            | ffff                 |  |

| Description:      | The contents of register f is moved to a destination dependant upon the status of d. If $d = 0$ , destination is W register. If $d = 1$ , the destination is file register f itself. $d = 1$ is useful to test a file register since status flag Z is affected. |                         |                 |                      |  |

| Words:            | 1                                                                                                                                                                                                                                                               |                         |                 |                      |  |

| Cycles:           | 1                                                                                                                                                                                                                                                               |                         |                 |                      |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                                              | Q2                      | Q3              | Q4                   |  |

|                   | Decode                                                                                                                                                                                                                                                          | Read<br>register<br>'f' | Process<br>data | Write to destination |  |

|                   |                                                                                                                                                                                                                                                                 |                         |                 |                      |  |

| Example           | MOVF                                                                                                                                                                                                                                                            | FSR,                    | 0               |                      |  |

|                   |                                                                                                                                                                                                                                                                 |                         | ie in FSR i     | register             |  |

| MOVWF             | Move W to f                                                      |

|-------------------|------------------------------------------------------------------|

| Syntax:           | [label] MOVWF f                                                  |

| Operands:         | $0 \leq f \leq 127$                                              |

| Operation:        | $(W) \rightarrow (f)$                                            |

| Status Affected:  | None                                                             |

| Encoding:         | 00 0000 1fff fff                                                 |

| Description:      | Move data from W register to register<br>'f'.                    |

| Words:            | 1                                                                |

| Cycles:           | 1                                                                |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                      |

|                   | Decode Read register data register 'f'                           |

| Example           | MOVWF OPTION_REG                                                 |

|                   | Before Instruction                                               |

|                   | OPTION = 0xFF<br>W = 0x4F                                        |

|                   | After Instruction                                                |

|                   | $\begin{array}{rcl} OPTION &= & 0x4F \\ W &= & 0x4F \end{array}$ |

|                   | W = 0X4F                                                         |

# PIC16F8X

| RLF               | Rotate Left f thr                                                      | ough Carry                                                                                                   | RRF               | Rotate Right f through Carry                                                                                                                                                                                 |  |  |  |

|-------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:           | [ label ]                                                              | RLF f,d                                                                                                      | Syntax:           | [ <i>label</i> ] RRF f,d                                                                                                                                                                                     |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$      |                                                                                                              | Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                           |  |  |  |

| Operation:        | See description I                                                      | below                                                                                                        | Operation:        | See description below                                                                                                                                                                                        |  |  |  |

| Status Affected:  | С                                                                      |                                                                                                              | Status Affected:  | С                                                                                                                                                                                                            |  |  |  |

| Encoding:         | 00 1101                                                                | dfff ffff                                                                                                    | Encoding:         | 00 1100 dfff ffff                                                                                                                                                                                            |  |  |  |

| Description:      | one bit to the left th<br>Flag. If 'd' is 0 the r                      | gister 'f' are rotated<br>nrough the Carry<br>esult is placed in the<br>1 the result is stored<br>Register f | Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'. |  |  |  |

| Words:            | 1                                                                      |                                                                                                              | Words:            | 1                                                                                                                                                                                                            |  |  |  |

| Cycles:           | 1                                                                      |                                                                                                              | Cycles:           | 1                                                                                                                                                                                                            |  |  |  |

| Q Cycle Activity: | Q1 Q2                                                                  | Q3 Q4                                                                                                        | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                  |  |  |  |

|                   | Decode Read<br>register<br>'f'                                         | Process Write to destination                                                                                 |                   | Decode Read register data Vite to destination                                                                                                                                                                |  |  |  |

| Example           | RLF RE                                                                 | G1,0                                                                                                         | Example           | RRF REG1,0                                                                                                                                                                                                   |  |  |  |

|                   | Before Instruction<br>REG1<br>C<br>After Instruction<br>REG1<br>W<br>C | n<br>= 1110 0110<br>= 0<br>= 1110 0110<br>= 1100 1100                                                        |                   | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                                                         |  |  |  |

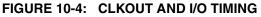

### TABLE 10-4 CLKOUT AND I/O TIMING REQUIREMENTS

| Parameter<br>No. | Sym        | Characteri                               | stic      | Min              | Typt | Max          | Units | Conditions |

|------------------|------------|------------------------------------------|-----------|------------------|------|--------------|-------|------------|

| 10               | TosH2ckL   | OSC1↑ to CLKOUT↓                         | PIC16F8X  | - /              | 15   | 30 *         | ns    | Note 1     |

| 10A              |            |                                          | PIC16LF8X |                  | 15   | 120 *        | ns    | Note 1     |

| 11               | TosH2ckH   | OSC1↑ to CLKOUT↑                         | PIC16F8X  | $f \neq $        |      | 30 *         | ns    | Note 1     |

| 11A              |            |                                          | PIC16LF8X | $/ \neq /$       | 15   | 120 *        | ns    | Note 1     |

| 12               | TckR       | CLKOUT rise time                         | PIC1@F8X  | $\overline{ - }$ | 15   | 30 *         | ns    | Note 1     |

| 12A              |            |                                          | PIC16LF8X | $\rightarrow$    | 15   | 100 *        | ns    | Note 1     |

| 13               | TckF       | CLKOUT fall time                         | PIC16F8X  | <u> </u>         | 15   | 30 *         | ns    | Note 1     |

| 13A              |            |                                          | RICHOLF8X | <u> </u>         | 15   | 100 *        | ns    | Note 1     |

| 14               | TckL2ioV   | CLKOUT ↓ to Port out                     | valid     | —                |      | 0.5TCY +20 * | ns    | Note 1     |

| 15               | TioV2ckH   | Port in valid before                     | PIC16F8X  | 0.30TCY + 30 *   |      | _            | ns    | Note 1     |

|                  |            | CLKOUT                                   | RIC16LF8X | 0.30TCY + 80 *   | —    | _            | ns    | Note 1     |

| 16               | TckH2iol   | Port in hold after CLKØ                  | NT T      | 0 *              |      | _            | ns    | Note 1     |

| 17               | TosH2ioV   | ØSC11 (Q1 cycle) to                      | PIC16F8X  | —                |      | 125 *        | ns    |            |

|                  |            | Port øut valid                           | PIC16LF8X | —                | —    | 250 *        | ns    |            |

| 18               | TosH2iol   | OSC11 (Q2 cycle) to                      | PIC16F8X  | 10 *             |      | _            | ns    |            |

|                  | $\bigcirc$ | Rort input invalid<br>(I/O in hold time) | PIC16LF8X | 10 *             | —    | —            | ns    |            |

| 19 <             | TioV20sH   | Rort input valid to                      | PIC16F8X  | -75 *            | -    | _            | ns    |            |

|                  | $\sum ($   | OSC1↑<br>(I/O in setup time)             | PIC16LF8X | -175 *           | —    | —            | ns    |            |

| 20               | TioR       | Port output rise time                    | PIC16F8X  | —                | 10   | 35 *         | ns    |            |

| 20A              | , ř        |                                          | PIC16LF8X | —                | 10   | 70 *         | ns    |            |

| 21               | TioF       | Port output fall time                    | PIC16F8X  | —                | 10   | 35 *         | ns    |            |

| 21A              |            |                                          | PIC16LF8X |                  | 10   | 70 *         | ns    |            |

| 22               | Tinp       | INT pin high                             | PIC16F8X  | 20 *             |      | _            | ns    |            |

| 22A              |            | or low time                              | PIC16LF8X | 55 *             |      | _            | ns    |            |

| 23               | Trbp       | RB7:RB4 change INT                       | PIC16F8X  | Tosc §           | —    | _            | ns    |            |

| 23A              |            | high or low time                         | PIC16LF8X | Tosc §           |      | _            | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ By design

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

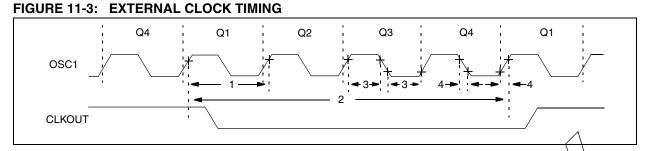

## 11.4 DC CHARACTERISTICS: PIC16CR84, PIC16CR83 (Commercial, Industrial) PIC16LCR84, PIC16LCR83 (Commercial, Industrial)

| DC Characteristics<br>All Pins Except<br>Power Supply Pins |       |                                            | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial)Operating voltage VDD range as described in DC specSection 11.1 and Section 11.2. |      |             |       |                                                                         |  |

|------------------------------------------------------------|-------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|-------|-------------------------------------------------------------------------|--|

| Parameter<br>No.                                           |       |                                            |                                                                                                                                                                                                                                                                         | Тур† | Max         | Units | Conditions                                                              |  |

|                                                            |       | Capacitive Loading Specs<br>on Output Pins |                                                                                                                                                                                                                                                                         |      |             |       | $\square$                                                               |  |

| D100                                                       | Cosc2 | OSC2 pin                                   | _                                                                                                                                                                                                                                                                       | _    | 15          | pF    | In XT, HS and LP modes<br>when external clock is used to<br>drive OSC1. |  |

| D101                                                       | Сю    | All I/O pins and OSC2<br>(RC mode)         | _                                                                                                                                                                                                                                                                       | —    | 50          | pF    |                                                                         |  |

|                                                            |       | Data EEPROM Memory                         |                                                                                                                                                                                                                                                                         |      |             |       | $  \backslash \lor \land \lor \rangle$                                  |  |

| D120                                                       | ED    | Endurance                                  | 1M                                                                                                                                                                                                                                                                      | 10M  | —           | ĘAW   | 25°C at 51                                                              |  |

| D121                                                       | Vdrw  | VDD for read/write                         | VMIN                                                                                                                                                                                                                                                                    | _    | 6.0         |       | VMN = Miximum operating                                                 |  |

| D122                                                       | TDEW  | Erase/Write cycle time                     | —                                                                                                                                                                                                                                                                       | 10   | <b>2</b> 0* | ms    |                                                                         |  |

\* These parameters are characterized but not tested.

Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

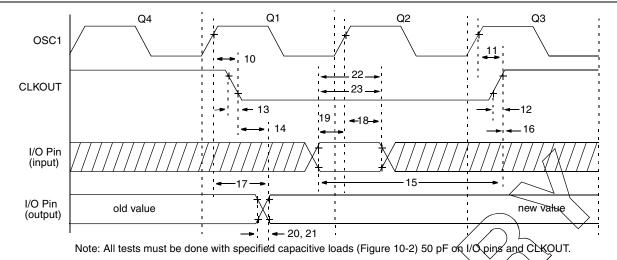

#### **TABLE 11-2** TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

- 1. TppS2ppS

- 2. TppS

#### **Timing Diagrams and Specifications** 11.5

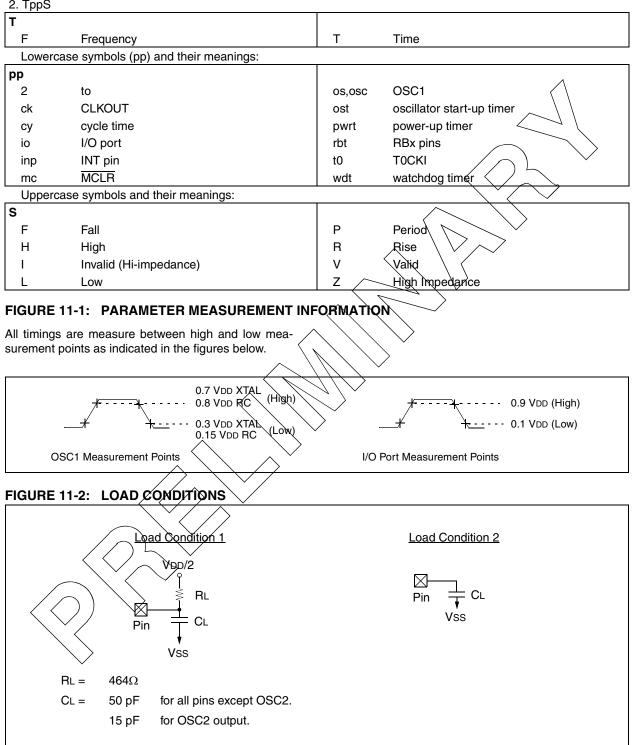

#### **TABLE 11-3 EXTERNAL CLOCK TIMING REQUIREMENTS**

| Parameter<br>No. | Sym                | Characteristic                          | Min   | Тур†                                          | Мах                 | Units | Conditions |               |  |

|------------------|--------------------|-----------------------------------------|-------|-----------------------------------------------|---------------------|-------|------------|---------------|--|

|                  | Fosc               | External CLKIN Frequency <sup>(1)</sup> | DC    |                                               | 2                   | MHz   | XT, RC osc | PIQ16LCR8X-04 |  |

|                  |                    |                                         | DC    | _                                             | 4                   | MHz   | XT, RC OSC | RICT6CR8X-04  |  |

|                  |                    |                                         | DC    | _                                             | 10                  | MHz   | HS osc     | PIC16CR8X-10  |  |

|                  |                    |                                         | DC    | —                                             | 200                 | ( kңz | 1⊾₽ osc 🗸  | PIC16LCR8X-04 |  |

|                  |                    | Oscillator Frequency <sup>(1)</sup>     | DC    |                                               | 2                   | МНа   | RG osc     | PIC16LCR8X-04 |  |

|                  |                    |                                         | DC    | _                                             | $\langle 4 \rangle$ | \ ·   | RC osc     | PIC16CR8X-04  |  |

|                  |                    |                                         | 0.1   | -~                                            | 2                   | MHz   | XT osc     | PIC16LCR8X-04 |  |

|                  |                    |                                         | 0.1   | $\prec$                                       | 4                   | MHz   | XT osc     | PIC16CR8X-04  |  |

|                  |                    |                                         | 1.0   |                                               | 10                  | MHz   | HS osc     | PIC16CR8X-10  |  |

|                  |                    |                                         | DČ    | $\setminus - \setminus$                       | 200                 | kHz   | LP osc     | PIC16LCR8X-04 |  |

| 1                | Tosc               | External CLKIN Period <sup>(1)</sup>    | \$00  | $\langle                                    $ | $\searrow$          | ns    | XT, RC osc | PIC16LCR8X-04 |  |

|                  |                    |                                         | 250   | $\langle \mathcal{F} \rangle$                 | $\sim$ –            | ns    | XT, RC osc | PIC16CR8X-04  |  |

|                  |                    |                                         | 100   | $\langle - \rangle$                           | —                   | ns    | HS osc     | PIC16CR8X-10  |  |

|                  |                    | $\land$                                 | 5.0   |                                               | _                   | μs    | LP osc     | PIC16LCR8X-04 |  |

|                  |                    | Oscillator Period <sup>(1)</sup>        | 500   | <u> </u>                                      | _                   | ns    | RC osc     | PIC16LCR8X-04 |  |

|                  |                    |                                         | 250   | —                                             | —                   | ns    | RC osc     | PIC16CR8X-04  |  |

|                  |                    |                                         | >500  | —                                             | 10,000              | ns    | XT osc     | PIC16LCR8X-04 |  |

|                  |                    | $\land \land \land \land$               | 250   | —                                             | 10,000              | ns    | XT osc     | PIC16CR8X-04  |  |

|                  |                    |                                         | 100   | —                                             | 1,000               | ns    | HS osc     | PIC16CR8X-10  |  |

|                  |                    |                                         | 5.0   |                                               | —                   | μs    | LP osc     | PIC16LCR8X-04 |  |

| 2                | Тсү                | Instruction Cycle Time <sup>(1)</sup>   | 0.4   | 4/Fosc                                        | DC                  | μs    |            |               |  |

| 3                | TosL, /            | Clock in (QSC1) High or Low             | 60 *  |                                               |                     | ns    | XT osc     | PIC16LCR8X-04 |  |

|                  | Tos⊬               | Time                                    | 50 *  | —                                             | —                   | ns    | XT osc     | PIC16CR8X-04  |  |

|                  | $ \langle \langle$ | $\checkmark \land \checkmark$           | 2.0 * | —                                             | —                   | μs    | LP osc     | PIC16LCR8X-04 |  |

|                  |                    | $\langle \checkmark$                    | 35 *  | _                                             |                     | ns    | HS osc     | PIC16CR8X-10  |  |

| 4                | JosR,              | Clock in (OSC1) Rise or Fall Time       | 25 *  | _                                             | —                   | ns    | XT osc     | PIC16CR8X-04  |  |

|                  | Tos⊭               | $\sim$                                  | 50 *  | —                                             | —                   | ns    | LP osc     | PIC16LCR8X-04 |  |

|                  |                    |                                         | 15 *  |                                               | _                   | ns    | HS osc     | PIC16CR8X-10  |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only + and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1 pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

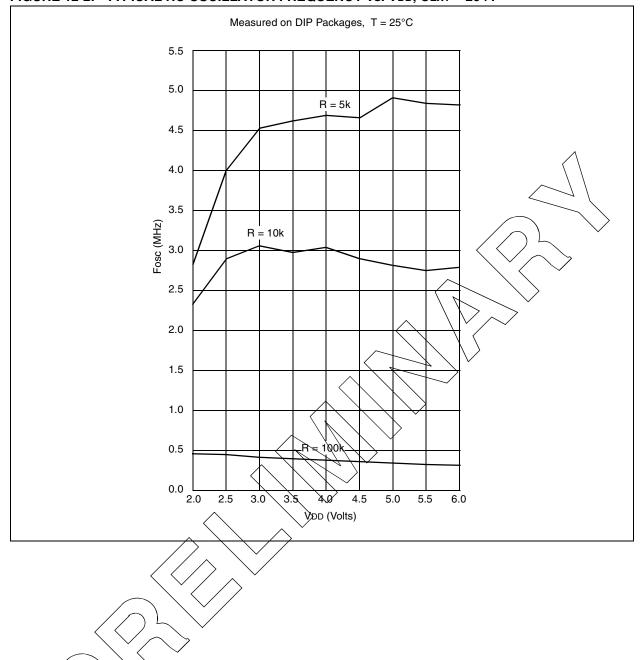

# FIGURE 12-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD, CEXT = 20 PF

VDD (Volts)

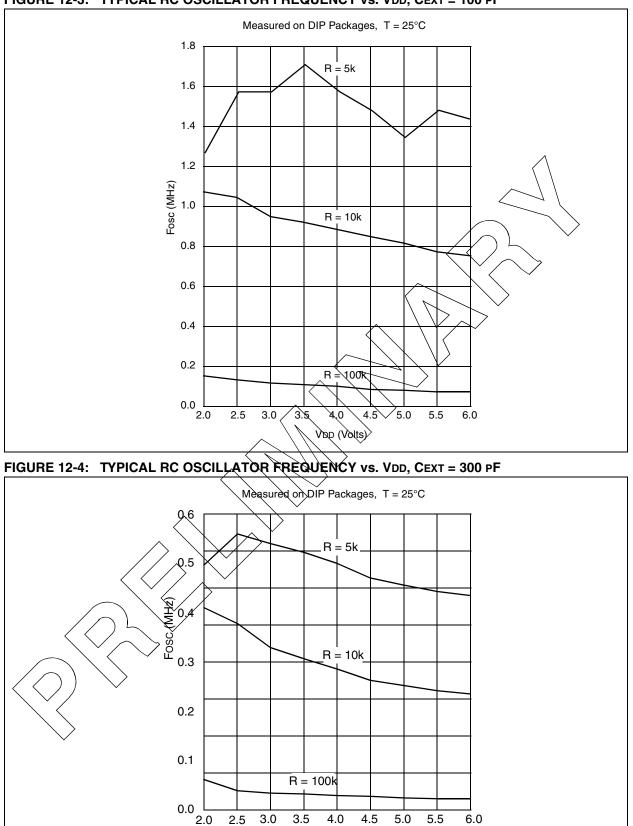

# FIGURE 12-3: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD, CEXT = 100 PF

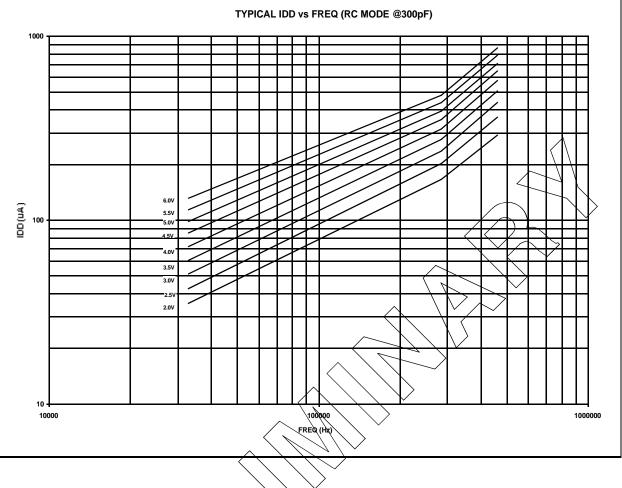

# FIGURE 12-12: TYPICAL IDD vs. FREQUENCY (RC MODE @300PF, 25°C)

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (602) 786-7578.

Please list the following information, and use this outline to provide us with your comments about this Data Sheet.

| To:  | Technical Publications Manager Total Pages Sent                                            |

|------|--------------------------------------------------------------------------------------------|

| RE:  | Reader Response                                                                            |

| From | n: Name                                                                                    |

|      | Company                                                                                    |

|      | Address                                                                                    |

|      | City / State / ZIP / Country                                                               |

| ٨٥٥  | Telephone: () FAX: ()   lication (optional): FAX: ()                                       |

| • •  |                                                                                            |

| vvou | Ild you like a reply?YN                                                                    |

| Devi | ice: PIC16F8X Literature Number: DS30430D                                                  |

| Que  | stions:                                                                                    |

| 1. \ | What are the best features of this document?                                               |

|      |                                                                                            |

| -    |                                                                                            |

| 2. 1 | How does this document meet your hardware and software development needs?                  |

| -    |                                                                                            |

| -    |                                                                                            |

| 3.   | Do you find the organization of this data sheet easy to follow? If not, why?               |

| -    |                                                                                            |

|      |                                                                                            |

| 4.   | What additions to the data sheet do you think would enhance the structure and subject?     |

| -    |                                                                                            |

| 5.   | What deletions from the data sheet could be made without affecting the overall usefulness? |

| 0.   |                                                                                            |

| -    |                                                                                            |

| 6. I | Is there any incorrect or misleading information (what and where)?                         |

|      |                                                                                            |

| -    |                                                                                            |

| 7. I | How would you improve this document?                                                       |

| -    |                                                                                            |

| -    |                                                                                            |

| 8. I | How would you improve our software, systems, and silicon products?                         |

|      |                                                                                            |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 1996-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769300

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.