Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 64 x 8                                                                      |

| RAM Size                   | 68 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 6V                                                                     |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf84t-04i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-1 PIC16F8X FAMILY OF DEVICES

|             |                                         | PIC16F83            | PIC16CR83           | PIC16F84            | PIC16CR84           |

|-------------|-----------------------------------------|---------------------|---------------------|---------------------|---------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz) | 10                  | 10                  | 10                  | 10                  |

|             | Flash Program Memory                    | 512                 | —                   | 1K                  | —                   |

|             | EEPROM Program Memory                   | —                   | —                   | —                   | —                   |

| Memory      | ROM Program Memory                      | —                   | 512                 | —                   | 1K                  |

|             | Data Memory (bytes)                     | 36                  | 36                  | 68                  | 68                  |

|             | Data EEPROM (bytes)                     | 64                  | 64                  | 64                  | 64                  |

| Peripherals | Timer Module(s)                         | TMR0                | TMR0                | TMR0                | TMR0                |

|             | Interrupt Sources                       | 4                   | 4                   | 4                   | 4                   |

|             | I/O Pins                                | 13                  | 13                  | 13                  | 13                  |

| Features    | Voltage Range (Volts)                   | 2.0-6.0             | 2.0-6.0             | 2.0-6.0             | 2.0-6.0             |

|             | Packages                                | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC |

All PIC<sup>®</sup> Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16F8X Family devices use serial programming with clock pin RB6 and data pin RB7.

## TABLE 4-1 REGISTER FILE SUMMARY

| Address | Name                  | Bit 7                   | Bit 6                               | Bit 5        | Bit 4             | Bit 3                                                  | Bit 2         | Bit 1 | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note3) |

|---------|-----------------------|-------------------------|-------------------------------------|--------------|-------------------|--------------------------------------------------------|---------------|-------|---------|-------------------------------|-----------------------------------------|

| Bank 0  |                       |                         |                                     |              | •                 |                                                        |               |       |         |                               | •                                       |

| 00h     | INDF                  | Uses co                 | ntents of F                         | SR to addre  | ess data memor    | y (not a phys                                          | sical registe | r)    |         |                               |                                         |

| 01h     | TMR0                  | 8-bit rea               | I-time clock                        | /counter     |                   |                                                        |               |       |         | xxxx xxxx                     | uuuu uuuu                               |

| 02h     | PCL                   | Low ord                 | er 8 bits of                        | the Program  | m Counter (PC)    |                                                        |               |       |         | 0000 0000                     | 0000 0000                               |

| 03h     | STATUS <sup>(2)</sup> | IRP                     | RP1                                 | RP0          | TO                | TO PD Z DC C                                           |               |       |         |                               | 000q quuu                               |

| 04h     | FSR                   | Indirect                | data memo                           | ry address   | pointer 0         |                                                        |               |       |         | xxxx xxxx                     | uuuu uuuu                               |

| 05h     | PORTA                 | —                       | —                                   | _            | RA4/T0CKI         | RA3                                                    | RA2           | RA1   | RA0     | x xxxx                        | u uuuu                                  |

| 06h     | PORTB                 | RB7                     | RB6                                 | RB5          | RB4               | RB3                                                    | RB2           | RB1   | RB0/INT | XXXX XXXX                     | uuuu uuuu                               |

| 07h     |                       | Unimple                 | Unimplemented location, read as '0' |              |                   |                                                        |               |       |         |                               |                                         |

| 08h     | EEDATA                | EEPROM data register    |                                     |              |                   |                                                        |               |       |         | XXXX XXXX                     | uuuu uuuu                               |

| 09h     | EEADR                 | EEPROM address register |                                     |              |                   |                                                        |               |       |         | XXXX XXXX                     | uuuu uuuu                               |

| 0Ah     | PCLATH                | _                       |                                     | _            | Write buffer for  | Write buffer for upper 5 bits of the PC <sup>(1)</sup> |               |       |         |                               | 0 0000                                  |

| 0Bh     | INTCON                | GIE                     | EEIE                                | TOIE         | INTE              | INTE RBIE TOIF INTE RBIF                               |               |       |         |                               | 0000 000u                               |

| Bank 1  |                       |                         |                                     |              |                   |                                                        |               |       |         |                               |                                         |

| 80h     | INDF                  | Uses co                 | ntents of F                         | SR to addre  | ess data memor    | y (not a phys                                          | sical registe | r)    |         |                               |                                         |

| 81h     | OPTION_<br>REG        | RBPU                    | INTEDG                              | TOCS         | TOSE              | PSA                                                    | PS2           | PS1   | PS0     | 1111 1111                     | 1111 1111                               |

| 82h     | PCL                   | Low ord                 | er 8 bits of                        | Program C    | ounter (PC)       |                                                        |               | •     | •       | 0000 0000                     | 0000 0000                               |

| 83h     | STATUS (2)            | IRP                     | RP1                                 | RP0          | TO                | PD                                                     | Z             | DC    | С       | 0001 1xxx                     | 000q quuu                               |

| 84h     | FSR                   | Indirect                | data memo                           | ry address   | pointer 0         |                                                        |               |       |         | xxxx xxxx                     | uuuu uuuu                               |

| 85h     | TRISA                 | —                       | —                                   | —            | PORTA data d      | irection regis                                         | ster          |       |         | 1 1111                        | 1 1111                                  |

| 86h     | TRISB                 | PORTB                   | data directi                        | on register  | •                 |                                                        |               |       |         | 1111 1111                     | 1111 1111                               |

| 87h     |                       | Unimple                 | mented loc                          | ation, read  | as '0'            |                                                        |               |       |         |                               |                                         |

| 88h     | EECON1                | —                       | —                                   | _            | EEIF              | WRERR                                                  | WREN          | WR    | RD      | 0 x000                        | 0 q000                                  |

| 89h     | EECON2                | EEPRO                   | V control re                        | gister 2 (no | ot a physical reg | ister)                                                 | -             |       |         |                               |                                         |

| 0Ah     | PCLATH                | _                       | _                                   | _            | Write buffer for  | r upper 5 bit                                          | s of the PC   | (1)   |         | 0 0000                        | 0 0000                                  |

| 0Bh     | INTCON                | GIE                     | EEIE                                | TOIE         | INTE              | RBIE                                                   | TOIF          | INTF  | RBIF    | 0000 000x                     | 0000 000u                               |

Legend: x = unknown, u = unchanged. - = unimplemented read as '0', q = value depends on condition.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a slave register for PC<12:8>. The contents of PCLATH can be transferred to the upper byte of the program counter, but the contents of PC<12:8> is never transferred to PCLATH.

2: The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  status bits in the STATUS register are not affected by a  $\overline{\text{MCLR}}$  reset.

3: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

NOTES:

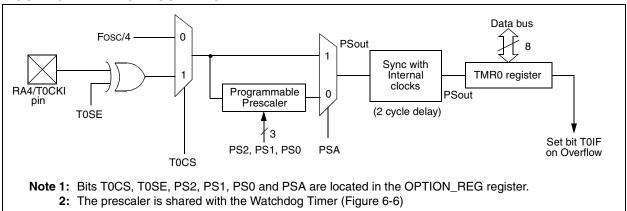

## 6.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

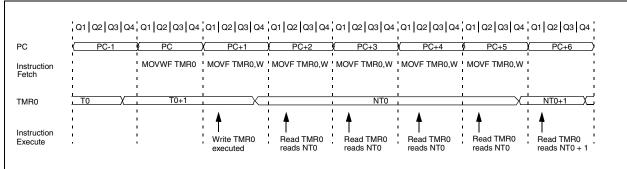

Timer mode is selected by clearing the TOCS bit (OPTION\_REG<5>). In timer mode, the Timer0 module (Figure 6-1) will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

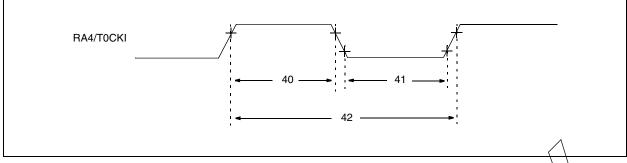

Counter mode is selected by setting the T0CS bit (OPTION\_REG<5>). In this mode TMR0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the T0 source

FIGURE 6-1: TMR0 BLOCK DIAGRAM

edge select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is shared between the Timer0 Module and the Watchdog Timer. The prescaler assignment is controlled, in software, by control bit PSA (OPTION\_REG<3>). Clearing bit PSA will assign the prescaler to the Timer0 Module. The prescaler is not readable or writable. When the prescaler (Section 6.3) is assigned to the Timer0 Module, the prescale value (1:2, 1:4, ..., 1:256) is software selectable.

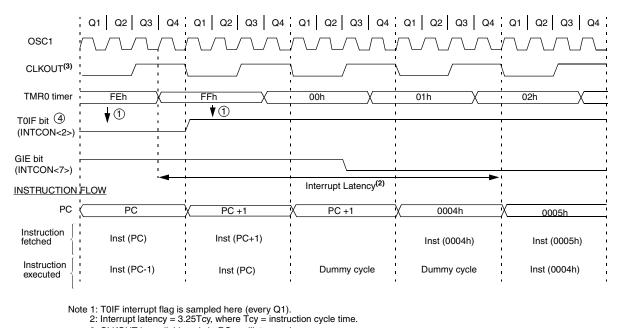

### 6.1 TMR0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets the T0IF bit (INTCON<2>). The interrupt can be masked by clearing enable bit T0IE (INTCON<5>). The T0IF bit must be cleared in software by the Timer0 Module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt (Figure 6-4) cannot wake the processor from SLEEP since the timer is shut off during SLEEP.

## FIGURE 6-2: TMR0 TIMING: INTERNAL CLOCK/NO PRESCALER

|                         | I    | 1                | 1                      | 1                      | 1                      | 1 1                    | · · · · · · · · · · · · · · · · · · · |                            |

|-------------------------|------|------------------|------------------------|------------------------|------------------------|------------------------|---------------------------------------|----------------------------|

| PC                      | PC-1 | ) PC             | PC+1                   | PC+2                   | PC+3                   | PC+4                   | PC+5 X                                | PC+6                       |

| Instruction<br>Fetch    |      | MOVWF TMR0       | MOVF TMR0,W                           |                            |

| TMR0                    |      | Τ0+1 χ           | Τ0+2 χ                 | ΝΤΟ Χ                  | ΝΤΟ χ                  | ΝΤΟ Χ                  | NT0+1                                 | NT0+2 X                    |

| Instruction<br>Executed |      | 1<br>1<br>1<br>1 | Write TMR0<br>executed | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1            | Read TMR0<br>reads NT0 + 2 |

## FIGURE 6-3: TMR0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

### FIGURE 6-4: TMR0 INTERRUPT TIMING

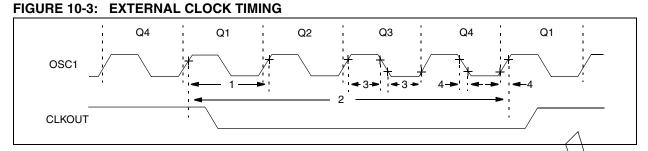

3: CLKOUT is available only in RC oscillator mode.

4: The timer clock (after the synchronizer circuit) which increments the timer from FFh to 00h immediately sets the T0IF bit. The TMR0 register will roll over 3 Tosc cycles later.

# 7.0 DATA EEPROM MEMORY

The EEPROM data memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead it is indirectly addressed through the Special Function Registers. There are four SFRs used to read and write this memory. These registers are:

- EECON1

- EECON2

- EEDATA

- EEADR

EEDATA holds the 8-bit data for read/write, and EEADR holds the address of the EEPROM location being accessed. PIC16F8X devices have 64 bytes of data EEPROM with an address range from 0h to 3Fh.

The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write). The EEPROM data memory is rated for high erase/write cycles. The write time is controlled by an on-chip timer. The writetime will vary with voltage and temperature as well as from chip to chip. Please refer to AC specifications for exact limits.

When the device is code protected, the CPU may continue to read and write the data EEPROM memory. The device programmer can no longer access this memory.

## 7.1 <u>EEADR</u>

The EEADR register can address up to a maximum of 256 bytes of data EEPROM. Only the first 64 bytes of data EEPROM are implemented.

The upper two bits are address decoded. This means that these two bits must always be '0' to ensure that the address is in the 64 byte memory space.

| U       | U                                                                                                                                                                                                                     | U                      | R/W-0                  | R/W-x    | R/W-0      | R/S-0      | R/S-x      |                               |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|----------|------------|------------|------------|-------------------------------|--|--|--|

| _       | _                                                                                                                                                                                                                     |                        | EEIF                   | WRERR    | WREN       | WR         | RD         | R = Readable bit              |  |  |  |

| bit7    | S = Settable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset                                                                                                                                 |                        |                        |          |            |            |            |                               |  |  |  |

| bit 7:5 | Unimplemented: Read as '0'                                                                                                                                                                                            |                        |                        |          |            |            |            |                               |  |  |  |

| bit 4   | <ul> <li>EEIF: EEPROM Write Operation Interrupt Flag bit</li> <li>1 = The write operation completed (must be cleared in software)</li> <li>0 = The write operation is not complete or has not been started</li> </ul> |                        |                        |          |            |            |            |                               |  |  |  |

| bit 3   | WRERR: EEPROM Error Flag bit 1 = A write operation is prematurely terminated     (any MCLR reset or any WDT reset during normal operation) 0 = The write operation completed                                          |                        |                        |          |            |            |            |                               |  |  |  |

| bit 2   | WREN: EB<br>1 = Allows<br>0 = Inhibits                                                                                                                                                                                | write cyc              | cles                   |          |            |            |            |                               |  |  |  |

| bit 1   |                                                                                                                                                                                                                       |                        |                        |          |            |            |            |                               |  |  |  |

| bit 0   |                                                                                                                                                                                                                       | es an EEI<br>(not clea | PROM rea<br>red) in so | ftware). | kes one cy | cle. RD is | cleared in | hardware. The RD bit can only |  |  |  |

## FIGURE 7-1: EECON1 REGISTER (ADDRESS 88h)

### 8.1 <u>Configuration Bits</u>

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

Address 2007h is beyond the user program memory space and it belongs to the special test/configuration memory space (2000h - 3FFFh). This space can only be accessed during programming.

To find out how to program the PIC16C84, refer to *PIC16C84 EEPROM Memory Programming Specifica-tion* (DS30189).

## FIGURE 8-1: CONFIGURATION WORD - PIC16CR83 AND PIC16CR84

| D.u       | <b>D</b>                                                                                                                                             | Π                                                | <b>D</b>                     | <b>D</b>  | <b>D</b>  | D/D         | <b>D</b>  | D         | <b>D</b>  | <b>D</b>     | <b>D</b>    | D                                 | D                                                      |   |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------|-----------|-----------|-------------|-----------|-----------|-----------|--------------|-------------|-----------------------------------|--------------------------------------------------------|---|

| R-u<br>CP | R-u<br>CP                                                                                                                                            | R-u<br>CP                                        | R-u<br>CP                    | R-u<br>CP | R-u<br>CP | R/P-u<br>DP | R-u<br>CP | R-u<br>CP | R-u<br>CP | R-u<br>PWRTE | R-u<br>WDTE | R-u<br>FOSC1                      | R-u<br>FOSC0                                           |   |

| bit13     |                                                                                                                                                      | 01                                               | 01                           |           |           |             | 01        |           | 01        |              |             | R = Rea<br>P = Prog<br>- n = Valu | bit0<br>adable bit<br>grammable bit<br>ue at POR reset | t |

| bit 13:8  | u = unchanged         13:8       CP: Program Memory Code Protection bit         1 = Code protection off         0 = Program memory is code protected |                                                  |                              |           |           |             |           |           |           |              |             |                                   |                                                        |   |

| bit 7     | <ul> <li>DP: Data Memory Code Protection bit</li> <li>1 = Code protection off</li> <li>0 = Data memory is code protected</li> </ul>                  |                                                  |                              |           |           |             |           |           |           |              |             |                                   |                                                        |   |

| bit 6:4   | <b>CP</b> : Program Memory Code Protection bit<br>1 = Code protection off<br>0 = Program memory is code protected                                    |                                                  |                              |           |           |             |           |           |           |              |             |                                   |                                                        |   |

| bit 3     | 1 = F                                                                                                                                                | RTE: Pov<br>Power-up<br>Power-up                 | timer                        | is disal  | oled      | bit         |           |           |           |              |             |                                   |                                                        |   |

| bit 2     | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                                                               |                                                  |                              |           |           |             |           |           |           |              |             |                                   |                                                        |   |

| bit 1:0   | 11 =<br>10 =<br>01 =                                                                                                                                 | C1:FOS<br>RC osc<br>HS osc<br>XT osci<br>LP osci | illator<br>illator<br>llator | cillator  | Selec     | tion bits   |           |           |           |              |             |                                   |                                                        |   |

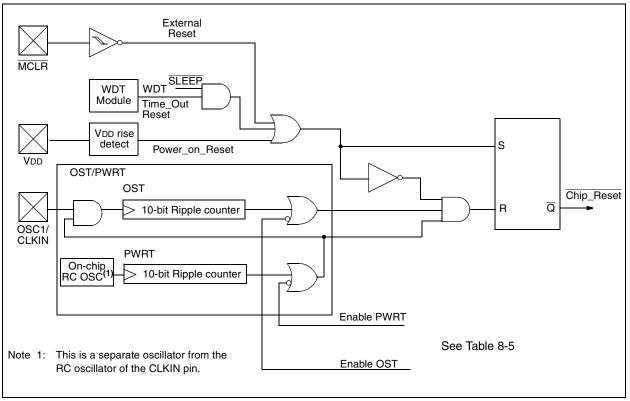

#### FIGURE 8-8: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

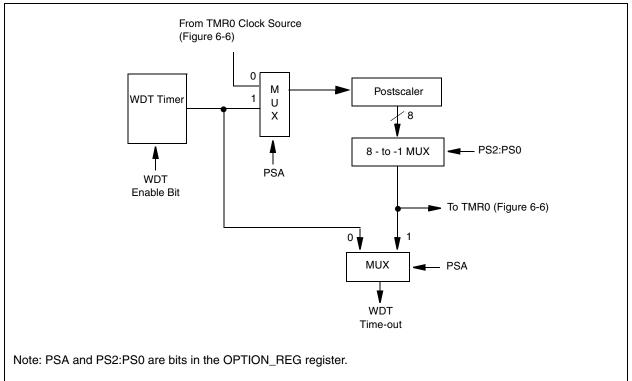

#### 8.11 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation a WDT time-out generates a device RESET. If the device is in SLEEP mode, a WDT Wake-up causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming configuration bit WDTE as a '0' (Section 8.1).

#### 8.11.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to

FIGURE 8-18: WATCHDOG TIMER BLOCK DIAGRAM

part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION\_REG register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out and generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a WDT time-out.

8.11.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

### TABLE 8-7 SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name           | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all other resets |

|---------|----------------|-------|--------|-------|-------|----------------------|-------|-------|-------|-------------------------------|---------------------------|

| 2007h   | Config. bits   | (2)   | (2)    | (2)   | (2)   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 | (2)                           |                           |

| 81h     | OPTION_<br>REG | RBPU  | INTEDG | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                 |

Legend: x = unknown. Shaded cells are not used by the WDT.

Note 1: See Figure 8-1 and Figure 8-2 for operation of the PWRTE bit.

2: See Figure 8-1, Figure 8-2 and Section 8.13 for operation of the Code and Data protection bits.

#### 8.12.3 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

### 8.13 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting widowed devices.               |

#### 8.14 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations to store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable only during program/verify. Only the 4 least significant bits of ID location are usable.

For ROM devices, these values are submitted along with the ROM code.

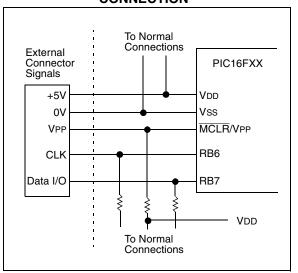

## 8.15 In-Circuit Serial Programming

PIC16F8X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. Customers can manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product, allowing the most recent firmware or custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB6 and RB7 pins low, while raising the MCLR pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) points to location 00h. A 6-bit command is then supplied to the device, 14-bits of program data is then supplied to or from the device, using load or read-type instructions. For complete details of serial programming, please refer to the PIC16CXX Programming Specifications (Literature #DS30189).

#### FIGURE 8-20: TYPICAL IN-SYSTEM SERIAL PROGRAMMING CONNECTION

For ROM devices, both the program memory and Data EEPROM memory may be read, but only the Data EEPROM memory may be programmed.

| BCF               | Bit Clear                                                          | f                                                                          |                 |                       | BT         |  |  |  |  |

|-------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------|-----------------------|------------|--|--|--|--|

| Syntax:           | [ <i>label</i> ] BC                                                | CF f,b                                                                     |                 |                       | Syn        |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b \leq 7 \end{array}$ | $\begin{array}{ll} 0 \leq f \leq 127 & C \\ 0 \leq b \leq 7 & \end{array}$ |                 |                       |            |  |  |  |  |

| Operation:        | $0 \rightarrow (f < b >)$ Of                                       |                                                                            |                 |                       |            |  |  |  |  |

| Status Affected:  | None                                                               |                                                                            |                 |                       | Stat       |  |  |  |  |

| Encoding:         | 01                                                                 | 00bb                                                                       | bfff            | ffff                  | Enc        |  |  |  |  |

| Description:      | Bit 'b' in register 'f' is cleared. De                             |                                                                            |                 |                       |            |  |  |  |  |

| Words:            | 1                                                                  |                                                                            |                 |                       |            |  |  |  |  |

| Cycles:           | 1                                                                  |                                                                            |                 |                       |            |  |  |  |  |

| Q Cycle Activity: | Q1                                                                 | Q2                                                                         | Q3              | Q4                    |            |  |  |  |  |

|                   | Decode                                                             | Read<br>register<br>'f'                                                    | Process<br>data | Write<br>register 'f' | Woi<br>Cyc |  |  |  |  |

| Example           | BCF                                                                | FLAG_                                                                      | REG, 7          |                       | QC         |  |  |  |  |

|                   | Before In<br>After Inst                                            |                                                                            |                 |                       |            |  |  |  |  |

| BTFSC                                                                                                                                       | Bit Test,                                                                                                                                                                                                                          | Skip if Cl       | ear                |                  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|------------------|--|--|--|--|

| Syntax:                                                                                                                                     | [ <i>label</i> ] BT                                                                                                                                                                                                                | FSC f,b          |                    |                  |  |  |  |  |

| Operands:                                                                                                                                   | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                 | 7                |                    |                  |  |  |  |  |

| Operation:                                                                                                                                  | skip if (f<                                                                                                                                                                                                                        | b>) = 0          |                    |                  |  |  |  |  |

| Status Affected:                                                                                                                            | None                                                                                                                                                                                                                               |                  |                    |                  |  |  |  |  |

| Encoding:                                                                                                                                   | 01                                                                                                                                                                                                                                 | 10bb             | bfff               | ffff             |  |  |  |  |

| Description:                                                                                                                                | If bit 'b' in register 'f' is '1' then the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0' then the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a 2Tcy<br>instruction. |                  |                    |                  |  |  |  |  |

| Words:                                                                                                                                      | 1                                                                                                                                                                                                                                  |                  |                    |                  |  |  |  |  |

| Cycles:                                                                                                                                     | 1(2)                                                                                                                                                                                                                               |                  |                    |                  |  |  |  |  |

| Q Cycle Activity:                                                                                                                           | Q1                                                                                                                                                                                                                                 | Q2               | Q3                 | Q4               |  |  |  |  |

|                                                                                                                                             |                                                                                                                                                                                                                                    |                  | Process<br>data    | No-Operat<br>ion |  |  |  |  |

| If Skip:                                                                                                                                    | (2nd Cyc                                                                                                                                                                                                                           | le)              |                    |                  |  |  |  |  |

|                                                                                                                                             | Q1                                                                                                                                                                                                                                 | Q2               | Q3                 | Q4               |  |  |  |  |

|                                                                                                                                             | No-Operat<br>ion                                                                                                                                                                                                                   | No-Operati<br>on | No-Opera<br>tion   | No-Operat<br>ion |  |  |  |  |

| Example                                                                                                                                     | HERE<br>FALSE<br>TRUE                                                                                                                                                                                                              |                  | FLAG,1<br>PROCESS_ | _CODE            |  |  |  |  |

| Before Instruction<br>PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,<br>PC = address TRUE<br>if FLAG<1>=1,<br>PC = address FALSE |                                                                                                                                                                                                                                    |                  |                    |                  |  |  |  |  |

| BSF                                                                           | Bit Set f                                                          |                         |                 |                       |  |  |  |  |  |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|--|--|

| Syntax:                                                                       | [ <i>label</i> ] BS                                                | SF f,b                  |                 |                       |  |  |  |  |  |

| Operands:                                                                     | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b \leq 7 \end{array}$ | 7                       |                 |                       |  |  |  |  |  |

| Operation:                                                                    | $1 \rightarrow (f < b >$                                           | >)                      |                 |                       |  |  |  |  |  |

| Status Affected:                                                              | None                                                               | None                    |                 |                       |  |  |  |  |  |

| Encoding:                                                                     | 01 01bb bfff fff                                                   |                         |                 |                       |  |  |  |  |  |

| Description:                                                                  | Bit 'b' in register 'f' is set.                                    |                         |                 |                       |  |  |  |  |  |

| Words:                                                                        | 1                                                                  |                         |                 |                       |  |  |  |  |  |

| Cycles:                                                                       | 1                                                                  |                         |                 |                       |  |  |  |  |  |

| Q Cycle Activity:                                                             | Q1                                                                 | Q2                      | Q3              | Q4                    |  |  |  |  |  |

|                                                                               | Decode                                                             | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |  |  |

| Example                                                                       | BSF                                                                | FLAG_F                  | REG, 7          |                       |  |  |  |  |  |

| Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG_REG = 0x8A |                                                                    |                         |                 |                       |  |  |  |  |  |

| NOP               | No Oper       | ation            |                  |                  |  |  |  |  |

|-------------------|---------------|------------------|------------------|------------------|--|--|--|--|

| Syntax:           | [ label ]     | NOP              |                  |                  |  |  |  |  |

| Operands:         | None          |                  |                  |                  |  |  |  |  |

| Operation:        | No opera      | ition            |                  |                  |  |  |  |  |

| Status Affected:  | None          |                  |                  |                  |  |  |  |  |

| Encoding:         | 00            | 0000             | 0xx0             | 0000             |  |  |  |  |

| Description:      | No operation. |                  |                  |                  |  |  |  |  |

| Words:            | 1             |                  |                  |                  |  |  |  |  |

| Cycles:           | 1             |                  |                  |                  |  |  |  |  |

| Q Cycle Activity: | Q1            | Q2               | Q3               | Q4               |  |  |  |  |

|                   | Decode        | No-Opera<br>tion | No-Opera<br>tion | No-Operat<br>ion |  |  |  |  |

| Example           | NOP           |                  |                  |                  |  |  |  |  |

| RETFIE            | Return from Interrupt                                                                                                                                                                                             |                  |                    |                    |  |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|--------------------|--|--|--|--|--|--|

| Syntax:           | [label] RETFIE                                                                                                                                                                                                    |                  |                    |                    |  |  |  |  |  |  |

| Operands:         | None                                                                                                                                                                                                              |                  |                    |                    |  |  |  |  |  |  |

| Operation:        | $\begin{array}{l} \text{TOS} \rightarrow \text{PC}, \\ 1 \rightarrow \text{GIE} \end{array}$                                                                                                                      |                  |                    |                    |  |  |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                              |                  |                    |                    |  |  |  |  |  |  |

| Encoding:         | 00 0000 0000 1001                                                                                                                                                                                                 |                  |                    |                    |  |  |  |  |  |  |

| Description:      | Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in the<br>PC. Interrupts are enabled by setting<br>Global Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |                  |                    |                    |  |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                 |                  |                    |                    |  |  |  |  |  |  |

| Cycles:           | 2                                                                                                                                                                                                                 |                  |                    |                    |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                | Q2               | Q3                 | Q4                 |  |  |  |  |  |  |

| 1st Cycle         | Decode                                                                                                                                                                                                            | No-Opera<br>tion | Set the<br>GIE bit | Pop from the Stack |  |  |  |  |  |  |

| 2nd Cycle         | No-Operat<br>ion                                                                                                                                                                                                  | No-Opera<br>tion | No-Opera<br>tion   | No-Operat<br>ion   |  |  |  |  |  |  |

| Example           | RETFIE                                                                                                                                                                                                            |                  |                    |                    |  |  |  |  |  |  |

After Interrupt PC = TOS GIE = 1

| OPTION           | Load Option Register                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] OPTION                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow OPTION$                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 0110 0010                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code com-<br>patibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly address<br>it. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Example          |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                  | To maintain upward compatibility<br>with future PIC16CXX products,<br>do not use this instruction.                                                                                                                                                 |  |  |  |  |  |  |  |

| XORLW                                                       | Exclusive OR Literal with W                                                                   | XORWF                                       | Exclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                     | [ <i>label</i> ] XORLW k                                                                      | Syntax:                                     | [ <i>label</i> ] XORWF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Operands:                                                   | $0 \le k \le 255$                                                                             | Operands:                                   | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Operation:<br>Status Affected:<br>Encoding:<br>Description: | (W) .XOR. $k \rightarrow$ (W)<br>Z<br>11 1010 kkkk kkkk<br>The contents of the W register are | Operation:<br>Status Affected:<br>Encoding: | (W) .XOR. (f) $\rightarrow$ (destination)<br>Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                             | XOR'ed with the eight bit literal 'k'.<br>The result is placed in the W regis-<br>ter.        | Description:                                | Exclusive OR the contents of the W<br>register with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Words:                                                      | 1                                                                                             | Words:                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cycles:<br>Q Cycle Activity:                                | 1<br>Q1 Q2 Q3 Q4                                                                              | Cycles:<br>Q Cycle Activity:                | 1<br>Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                             | Decode Read Process Write to<br>literal 'k' data W                                            |                                             | Decode Read register of the termination of terminatio of termination of termination of termination o |

| Example:                                                    | XORLW 0xAF                                                                                    |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |