Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/dsp56857bue |

|----------------------------|---------------------------------------------------------------------|

| Supplier Device Package    | 100-LQFP (14x14)                                                    |

| Package / Case             | 100-LQFP                                                            |

| Mounting Type              | Surface Mount                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Oscillator Type            | External                                                            |

| Data Converters            | -                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 1.98V                                                       |

| RAM Size                   | 24K x 16                                                            |

| EEPROM Size                | •                                                                   |

| Program Memory Type        | SRAM                                                                |

| Program Memory Size        | 80KB (40K x 16)                                                     |

| Number of I/O              | 47                                                                  |

| Peripherals                | DMA, POR, WDT                                                       |

| Connectivity               | SCI, SPI, SSI                                                       |

| Speed                      | 120MHz                                                              |

| Core Size                  | 16-Bit                                                              |

| Core Processor             | 56800E                                                              |

| Product Status             | Obsolete                                                            |

| Details                    |                                                                     |

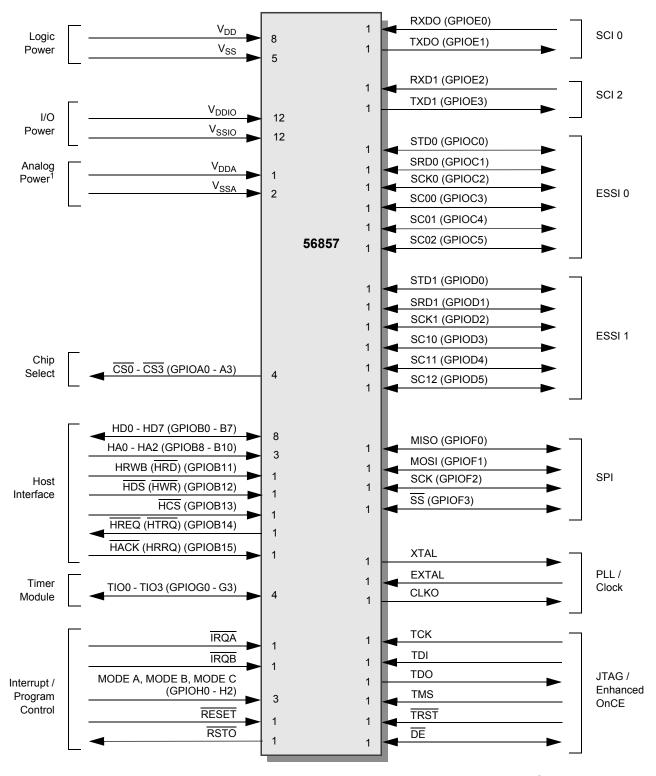

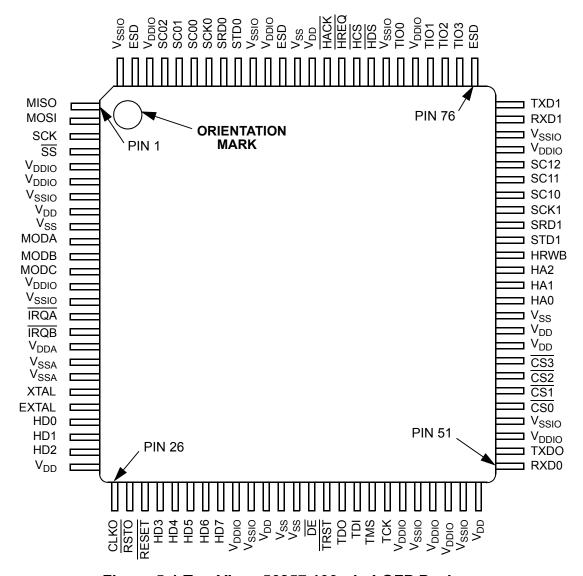

Figure 2-1 56857 Signals Identified by Functional Group<sup>2</sup>

- 1. Specifically for PLL, OSC, and POR.

- 2. Alternate pin functions are shown in parentheses.

Table 3-1 56857 Signal and Package Information for the 100-pin LQFP (Continued)

| Pin No. | Signal Name      | Туре             | Description                                                                                                    |  |  |  |

|---------|------------------|------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| 18      | V <sub>SSA</sub> | V <sub>SSA</sub> | Analog Ground (V <sub>SSA</sub> )—This pin supplies an analog ground.                                          |  |  |  |

| 19      | V <sub>SSA</sub> |                  |                                                                                                                |  |  |  |

| 55      | CS0              | Output           | External Chip Select (CS0)—This pin is used as a dedicated GPIO.                                               |  |  |  |

|         | GPIOA0           | Input/Output     | Port A GPIO (0)—This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.          |  |  |  |

| 56      | CS1              | Output           | External Chip Select (CS1)—This pin is used as a dedicated GPIO.                                               |  |  |  |

|         | GPIOA1           | Input/Output     | Port A GPIO (1)—This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.          |  |  |  |

| 57      | CS2              | Output           | External Chip Select (CS2)—This pin is used as a dedicated GPIO.                                               |  |  |  |

|         | GPIOA2           | Input/Output     | Port A GPIO (2)—This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.          |  |  |  |

| 58      | CS3              | Output           | External Chip Select (CS3)—This pin is used as a dedicated GPIO.                                               |  |  |  |

|         | GPIOA3           | Input/Output     | Port A GPIO (3)—This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.          |  |  |  |

| 22      | HD0              | Input            | Host Address (HD0)—This input provides the address selection for HI registers.                                 |  |  |  |

|         |                  |                  | This pin is disconnected internally.                                                                           |  |  |  |

|         | GPIOB0           | Input/Output     | Port B GPIO (0)—This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.          |  |  |  |

| 23      | HD1              | Input            | Host Address (HD1)—This input provides the address selection for HI registers.                                 |  |  |  |

|         |                  |                  | This pin is disconnected internally.                                                                           |  |  |  |

|         | GPIOB1           | Input/Output     | <b>Port B GPIO (1)</b> —This pin is a General Purpose I/O (GPIO) pins when not configured for host port usage. |  |  |  |

| 24      | HD2              | Input            | Host Address (HD2)—This input provides the address selection for HI registers.                                 |  |  |  |

|         |                  |                  | This pin is disconnected internally.                                                                           |  |  |  |

|         | GPIOB2           | Input/Output     | Port B GPIO (2)—This pin is a General Purpose I/O (GPIO) pins when not configured for host port usage.         |  |  |  |

Table 3-1 56857 Signal and Package Information for the 100-pin LQFP (Continued)

| Pin No. | Signal Name | Туре         | Description                                                                                            |  |  |  |

|---------|-------------|--------------|--------------------------------------------------------------------------------------------------------|--|--|--|

| 29      | HD3         | Input        | Host Address (HD3)—This input provides the address selection for HI registers.                         |  |  |  |

|         |             |              | This pin is disconnected internally.                                                                   |  |  |  |

|         | GPIOB3      | Input/Output | Port B GPIO (3)—This pin is a General Purpose I/O (GPIO) pins when not configured for host port usage. |  |  |  |

| 30      | HD4         | Input        | Host Address (HD4)—This input provides the address selection for HI registers.                         |  |  |  |

|         |             |              | This pin is disconnected internally.                                                                   |  |  |  |

|         | GPIOB4      | Input/Output | Port B GPIO (4)—This pin is a General Purpose I/O (GPIO) pins when not configured for host port usage. |  |  |  |

| 31      | HD5         | Input        | <b>Host Address (HD5)—</b> This input provides the address selection for HI registers.                 |  |  |  |

|         |             |              | This pin is disconnected internally.                                                                   |  |  |  |

|         | GPIOB5      | Input/Output | Port B GPIO (5)—This pin is a General Purpose I/O (GPIO) pins when not configured for host port usage. |  |  |  |

| 32      | HD6         | Input        | Host Address (HD6)—This input provides the address selection for HI registers.                         |  |  |  |

|         |             |              | This pin is disconnected internally.                                                                   |  |  |  |

|         | GPIOB6      | Input/Output | Port B GPIO (6)—This pin is a General Purpose I/O (GPIO) pins when not configured for host port usage. |  |  |  |

| 33      | HD7         | Input        | <b>Host Address (HD7)—</b> This input provides the address selection for HI registers.                 |  |  |  |

|         |             |              | This pin is disconnected internally.                                                                   |  |  |  |

|         | GPIOB7      | Input/Output | Port B GPIO (7)—This pin is a General Purpose I/O (GPIO) pins when not configured for host port usage. |  |  |  |

| 62      | HA0         | Input        | Host Address (HA0)—This input provides the address selection for HI registers.                         |  |  |  |

|         |             |              | This pin is disconnected internally.                                                                   |  |  |  |

|         | GPIOB8      | Input/Output | Port B GPIO (8)—This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.  |  |  |  |

Table 3-1 56857 Signal and Package Information for the 100-pin LQFP (Continued)

| Pin No. | Signal Name | Туре                 | Description                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|---------|-------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 85      | HREQ        | Open Drain<br>Output | Host Request (HREQ)—When the HI08 is programmed for HRMS=0 functionality (typically used on a single-data- strobe bus), this open drain output is used by the HI to request service from the host processor. The HREQ may be connected to an interrupt request pin of a host processor, a transfer request of a DMA controller, or a control input of external circuitry. |  |  |  |

|         |             |                      | These pins are disconnected internally.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|         | HTRQ        | Open Drain<br>Output | Transmit Host Request (HTRQ)—This signal is the Transmit Host Request output when the HI08 is programmed for HRMS=1 functionality and is typically used on a double-data-strobe bus.                                                                                                                                                                                      |  |  |  |

|         | GPIOB14     | Input/Output         | Port B GPIO (14) —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.                                                                                                                                                                                                                                                                   |  |  |  |

| 86      | HACK        | Input                | Host Acknowledge (HACK)—When the HI08 is programmed for HRMS=0 functionality (typically used on a single-data-strobe bus), this input has two functions: (1) provide a Host Acknowledge signal for DMA transfers or (2) to control handshaking and provide a Host Interrupt Acknowledge compatible with the MC68000 family processors.                                    |  |  |  |

|         |             |                      | These pins are disconnected internally during reset.                                                                                                                                                                                                                                                                                                                      |  |  |  |

|         | HRRQ        | Open Drain<br>Output | Receive Host Request (HRRQ)—This signal is the Receive Host Request output when the HI08 is programmed for HRMS=1 functionality and is typically used on a double-data-strobe bus.                                                                                                                                                                                        |  |  |  |

|         | GPIOB15     | Input/Output         | Port B GPIO (15)—This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.                                                                                                                                                                                                                                                                    |  |  |  |

| 81      | TIO0        | Input/Output         | <b>Timer Input/Output (TIO0)</b> —This pin can be independently configured to be either a timer input source or an output flag.                                                                                                                                                                                                                                           |  |  |  |

|         | GPIOG0      | Input/Output         | Port G GPIO (0)—This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as an input or output pin.                                                                                                                                                                                                                                               |  |  |  |

| 79      | TIO1        | Input/Output         | <b>Timer Input/Output (TIO1)</b> —This pin can be independently configured to be either a timer input source or an output flag.                                                                                                                                                                                                                                           |  |  |  |

|         | GPIOG1      | Input/Output         | Port G GPIO (1)—This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as an input or output pin.                                                                                                                                                                                                                                               |  |  |  |

| 78      | TIO2        | Input/Output         | <b>Timer Input/Output (TIO2)</b> —This pin can be independently configured to be either a timer input source or an output flag.                                                                                                                                                                                                                                           |  |  |  |

|         | GPIOG2      | Input/Output         | Port G GPIO (2)—This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as an input or output pin.                                                                                                                                                                                                                                               |  |  |  |

Table 3-1 56857 Signal and Package Information for the 100-pin LQFP (Continued)

| Pin No. | Signal Name | Туре         | Description                                                                                                                                                                                                                                                                                                          |

|---------|-------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52      | TXD0        | Output(Z)    | Serial Transmit Data 0 (TXD0)—This signal transmits data from the SCI 0 transmit data register.                                                                                                                                                                                                                      |

|         | GPIOE1      | Input/Output | <b>Port E GPIO (1)</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin.                                                                                                                                                                                     |

| 74      | RXD1        | Input        | Serial Receive Data 1 (RXD1)—This input receives byte-oriented serial data and transfers it to the SCI 1 receive shift register.                                                                                                                                                                                     |

|         | GPIOE2      | Input/Output | Port E GPIO (2)—This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin.                                                                                                                                                                                             |

| 75      | TXD1        | Output(Z)    | Serial Transmit Data 1 (TXD1)—This signal transmits data from the SCI 1 transmit data register.                                                                                                                                                                                                                      |

|         | GPIOE3      | Input/Output | Port E GPIO (3)—This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin.                                                                                                                                                                                             |

| 92      | STD0        | Output       | <b>ESSI Transmit Data (STD0)</b> —This output pin transmits serial data from the ESSI Transmitter Shift Register.                                                                                                                                                                                                    |

|         | GPIOC0      | Input/Output | Port C GPIO (0)—This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                            |

| 93      | SRD0        | Input        | <b>ESSI Receive Data (SRD0)</b> —This input pin receives serial data and transfers the data to the ESSI Receive Shift Register.                                                                                                                                                                                      |

|         | GPIOC1      | Input/Output | Port C GPIO (1)—This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                            |

| 94      | SCK0        | Input/Output | <b>ESSI Serial Clock (SCK0)</b> —This bidirectional pin provides the serial bit rate clock for the transmit section of the ESSI. The clock signal can be continuous or gated and can be used by both the transmitter and receiver in synchronous mode.                                                               |

|         | GPIOC2      | Input/Output | Port C GPIO (2)—This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                            |

| 95      | SC00        | Input/Output | <b>ESSI Serial Control Pin 0 (SC00)</b> —The function of this pin is determined by the selection of either synchronous or asynchronous mode. For asynchronous mode, this pin will be used for the receive clock I/O. For synchronous mode, this pin is used either for transmitter1 output or for serial I/O flag 0. |

|         | GPIOC3      | Input/Output | Port C GPIO (3)—This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                            |

Table 3-1 56857 Signal and Package Information for the 100-pin LQFP (Continued)

| Pin No. | Signal Name | Туре         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|---------|-------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 96      | SC01        | Input/Output | <b>ESSI Serial Control Pin 1 (SC01)</b> —The function of this pin is determined by the selection of either synchronous or asynchronous mode. For asynchronous mode, this pin is the receiver frame sync I/O. For synchronous mode, this pin is used either for transmitter2 output or for serial I/O flag 1.                                                                                                                                       |  |  |  |  |

|         | GPIOC4      | Input/Output | Port C GPIO (4)—This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 97      | SC02        | Input/Output | <b>ESSI Serial Control Pin 2 (SC02)</b> —This pin is used for frame sync I/O SC02 is the frame sync for both the transmitter and receiver in synchronous mode and for the transmitter only in asynchronous mode When configured as an output, this pin is the internally generated fram sync signal. When configured as an input, this pin receives an external frame sync signal for the transmitter (and the receiver in synchronous operation). |  |  |  |  |

|         | GPIOC5      | Input/Output | Port C GPIO (5)—This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 66      | STD1        | Output       | <b>ESSI Transmit Data (STD1)</b> —This output pin transmits serial data from the ESSI Transmitter Shift Register.                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|         | GPIOD0      | Input/Output | Port D GPIOD0—This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 67      | SRD1        | Input        | ESSI Receive Data (SRD1)—This input pin receives serial data and transfers the data to the ESSI Receive Shift Register.                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|         | GPIOD1      | Input/Output | Port D GPIO (1)—This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 68      | SCK1        | Input/Output | <b>ESSI Serial Clock (SCK1)</b> —This bidirectional pin provides the serial bit rate clock for the transmit section of the ESSI. The clock signal can be continuous or gated and can be used by both the transmitter and receiver in synchronous mode.                                                                                                                                                                                             |  |  |  |  |

|         | GPIOD2      | Input/Output | Port D GPIO (2)—This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 69      | SC10        | Input/Output | <b>ESSI Serial Control Pin 0 (SC10)</b> —The function of this pin is determined by the selection of either synchronous or asynchronous mode. For asynchronous mode, this pin will be used for the receive clock I/O. For synchronous mode, this pin is used either for transmitter1 output or for serial I/O flag 0.                                                                                                                               |  |  |  |  |

|         | GPIOD3      | Input/Output | Port D GPIO (3)—This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

**Table 4-1 Absolute Maximum Ratings**

| Characteristic                                             | Symbol                                                           | Min                              | Max                                               | Unit |

|------------------------------------------------------------|------------------------------------------------------------------|----------------------------------|---------------------------------------------------|------|

| Supply voltage, core                                       | V <sub>DD</sub> <sup>1</sup>                                     | V <sub>SS</sub> – 0.3            | V <sub>SS</sub> + 2.0                             | V    |

| Supply voltage, IO<br>Supply voltage, analog               | V <sub>DDIO</sub> <sup>2</sup><br>V <sub>DDIO</sub> <sup>2</sup> | $V_{SSIO} - 0.3$ $V_{SSA} - 0.3$ | V <sub>SSIO</sub> + 4.0<br>V <sub>DDA</sub> + 4.0 | V    |

| Digital input voltages Analog input voltages (XTAL, EXTAL) | V <sub>IN</sub><br>V <sub>INA</sub>                              | $V_{SSIO} - 0.3$ $V_{SSA} - 0.3$ | $V_{\rm SSIO} + 5.5$ $V_{\rm DDA} + 0.3$          | V    |

| Current drain per pin excluding V <sub>DD</sub> , GND      | I                                                                | _                                | 8                                                 | mA   |

| Junction temperature                                       | T <sub>J</sub>                                                   | -40                              | 120                                               | °C   |

| Storage temperature range                                  | T <sub>STG</sub>                                                 | -55                              | 150                                               | °C   |

<sup>1.</sup>  $V_{DD}$  must not exceed  $V_{DDIO}$

**Table 4-2 Recommended Operating Conditions**

| Characteristic                   | Symbol             | Min  | Max  | Unit |

|----------------------------------|--------------------|------|------|------|

| Supply voltage for Logic Power   | V <sub>DD</sub>    | 1.62 | 1.98 | V    |

| Supply voltage for I/O Power     | V <sub>DDIO</sub>  | 3.0  | 3.6  | V    |

| Supply voltage for Analog Power  | $V_{DDA}$          | 3.0  | 3.6  | V    |

| Ambient operating temperature    | T <sub>A</sub>     | -40  | 85   | °C   |

| PLL clock frequency <sup>1</sup> | f <sub>pll</sub>   | _    | 240  | MHz  |

| Operating Frequency <sup>2</sup> | f <sub>op</sub>    | _    | 120  | MHz  |

| Frequency of peripheral bus      | f <sub>ipb</sub>   | _    | 60   | MHz  |

| Frequency of external clock      | f <sub>clk</sub>   | _    | 240  | MHz  |

| Frequency of oscillator          | f <sub>osc</sub>   | 2    | 4    | MHz  |

| Frequency of clock via XTAL      | f <sub>xtal</sub>  | _    | 240  | MHz  |

| Frequency of clock via EXTAL     | f <sub>extal</sub> | 2    | 4    | MHz  |

<sup>1.</sup> Assumes clock source is direct clock to EXTAL or crystal oscillator running 2-4MHz. PLL must be enabled, locked, and selected. The actual frequency depends on the source clock frequency and programming of the CGM module.

56857 Technical Data, Rev. 6

<sup>2.</sup>  $V_{DDIO}$  and  $V_{DDA}$  must not differ by more that 0.5V

<sup>2.</sup> Master clock is derived from on of the following four sources:

$f_{clk} = f_{xtal}$  when the source clock is the direct clock to EXTAL

$f_{clk} = f_{pll}$  when PLL is selected

$f_{clk} = f_{osc}$  when the source clock is the crystal oscillator and PLL is not selected

$f_{clk} = f_{extal}$  when the source clock is the direct clock to EXTAL and PLL is not selected

| Table | 4-3 | Thermal | Charac | teristics <sup>1</sup> |

|-------|-----|---------|--------|------------------------|

| Characteristic                                     | 100-pin LQFP      |                                          |      |  |  |

|----------------------------------------------------|-------------------|------------------------------------------|------|--|--|

| Characteristic                                     | Symbol            | Value                                    | Unit |  |  |

| Thermal resistance junction-to-ambient (estimated) | $\theta_{JA}$     | 41.2                                     | °C/W |  |  |

| I/O pin power dissipation                          | P <sub>I/O</sub>  | User Determined                          | W    |  |  |

| Power dissipation                                  | P <sub>D</sub>    | $P_D = (I_{DD} \times V_{DD}) + P_{I/O}$ | W    |  |  |

| Maximum allowed P <sub>D</sub>                     | P <sub>DMAX</sub> | $(T_J - T_A) / R\theta_{JA}^2$           | W    |  |  |

<sup>1.</sup> See Section 6.1 for more detail.

### 4.2 DC Electrical Characteristics

### **Table 4-4 DC Electrical Characteristics**

$Operating \ Conditions: \ V_{SS} = V_{SSIO} = V_{SSA} = 0 \ V, \ V_{DD} = 1.62 - 1.98 V, \ V_{DDIO} = V_{DDA} = 3.0 - 3.6 V, \ T_A = -40^{\circ} \ to \ +120^{\circ} C, \ C_L \leq 50 pF, \ f_{op} = 120 MHz$

| Characteristic                                                     | Symbol                       | Min                     | Тур       | Max                    | Unit |

|--------------------------------------------------------------------|------------------------------|-------------------------|-----------|------------------------|------|

| Input high voltage (XTAL/EXTAL)                                    | V <sub>IHC</sub>             | V <sub>DDA</sub> – 0.8  | $V_{DDA}$ | V <sub>DDA</sub> + 0.3 | V    |

| Input low voltage (XTAL/EXTAL)                                     | V <sub>ILC</sub>             | -0.3                    | _         | 0.5                    | V    |

| Input high voltage                                                 | V <sub>IH</sub>              | 2.0                     | _         | 5.5                    | V    |

| Input low voltage                                                  | V <sub>IL</sub>              | -0.3                    | _         | 0.8                    | V    |

| Input current low (pullups disabled)                               | I <sub>IL</sub>              | -1                      | _         | 1                      | μА   |

| Input current high (pullups disabled)                              | I <sub>IH</sub>              | -1                      | _         | 1                      | μА   |

| Output tri-state current low                                       | I <sub>OZL</sub>             | -10                     | _         | 10                     | μΑ   |

| Output tri-state current high                                      | I <sub>OZH</sub>             | -10                     | _         | 10                     | μΑ   |

| Output High Voltage                                                | V <sub>OH</sub>              | V <sub>DDIO</sub> – 0.7 | _         | _                      | V    |

| Output Low Voltage                                                 | V <sub>OL</sub>              | _                       | _         | 0.4                    | V    |

| Output High Current                                                | I <sub>OH</sub>              | 8                       | _         | 16                     | mA   |

| Output Low Current                                                 | I <sub>OL</sub>              | 8                       | _         | 16                     | mA   |

| Input capacitance                                                  | C <sub>IN</sub>              | _                       | 8         | _                      | pF   |

| Output capacitance                                                 | C <sub>OUT</sub>             | _                       | 12        | _                      | pF   |

| V <sub>DD</sub> supply current (Core logic, memories, peripherals) | I <sub>DD</sub> <sup>4</sup> |                         |           |                        |      |

| Run <sup>1</sup>                                                   |                              | _                       | 70        | 110                    | mA   |

| Deep Stop <sup>2</sup>                                             |                              | _                       | 0.05      | 10                     | mA   |

| Light Stop <sup>3</sup>                                            |                              | _                       | 5         | 14                     | mA   |

56857 Technical Data, Rev. 6

<sup>2.</sup> TJ = Junction Temperature TA = Ambient Temperature

### **Table 4-4 DC Electrical Characteristics (Continued)**

$Operating \ Conditions: \ V_{SS} = V_{SSIO} = V_{SSA} = 0 \ V, \ V_{DD} = 1.62 - 1.98 \\ V, \ V_{DDIO} = V_{DDA} = 3.0 - 3.6 \\ V, \ T_{A} = -40^{\circ} \ to \ +120^{\circ} \\ C, \ C_{L} \leq 50 \\ pF, \ f_{op} = 120 \\ MHz = 1.02 - 1.98 \\$

| Characteristic                                                                          | Symbol            | Min | Тур     | Max       | Unit     |

|-----------------------------------------------------------------------------------------|-------------------|-----|---------|-----------|----------|

| V <sub>DDIO</sub> supply current (I/O circuity) Run <sup>5</sup> Deep Stop <sup>2</sup> | I <sub>DDIO</sub> | _   | 40<br>0 | 50<br>1.5 | mA<br>mA |

| V <sub>DDA</sub> supply current (analog circuity)  Deep Stop <sup>2</sup>               | I <sub>DDA</sub>  | _   | 60      | 120       | μА       |

| Low Voltage Interrupt <sup>6</sup>                                                      | V <sub>EI</sub>   | _   | 2.5     | 2.85      | V        |

| Low Voltage Interrupt Recovery Hysteresis                                               | V <sub>EIH</sub>  | _   | 50      | _         | mV       |

| Power on Reset <sup>7</sup>                                                             | POR               | _   | 1.5     | 2.0       | V        |

**Note:** Run (operating)  $I_{DD}$  measured using external square wave clock source ( $f_{osc} = 4MHz$ ) into XTAL. All inputs 0.2V from rail; no DC loads; outputs unloaded. All ports configured as inputs; measured with all modules enabled. PLL set to 240MHz out.

- 1. Running Core, performing 50% NOP and 50% FIR. Clock at 120 MHz.

- 2. Deep Stop Mode Operation frequency = 4 MHz, PLL set to 4 MHz, crystal oscillator and time of day module operating.

- 3. Light Stop Mode Operation frequency = 120 MHz, PLL set to 240 MHz, crystal oscillator and time of day module operating.

- 4. I<sub>DD</sub> includes current for core logic, internal memories, and all internal peripheral logic circuitry.

- 5. Running core and performing external memory access. Clock at 120 MHz.

- 6. When V<sub>DD</sub> drops below V<sub>EI</sub> max value, an interrupt is generated.

- 7. Power-on reset occurs whenever the digital supply drops below 1.8V. While power is ramping up, this signal remains active for as long as the internal 2.5V is below 1.8V no matter how long the ramp up rate is. The internally regulated voltage is typically 100 mV less than V<sub>DD</sub> during ramp up until 2.5V is reached, at which time it self-regulates.

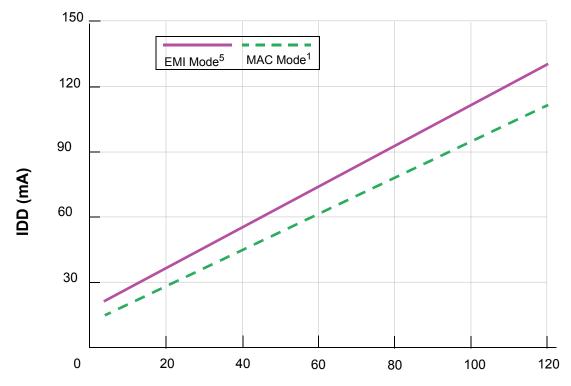

Figure 4-1 Maximum Run I<sub>DDTOTAL</sub> vs. Frequency (see Notes 1. and 5. in Table 4-4)

### 4.4 AC Electrical Characteristics

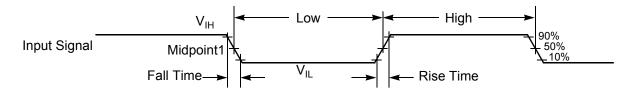

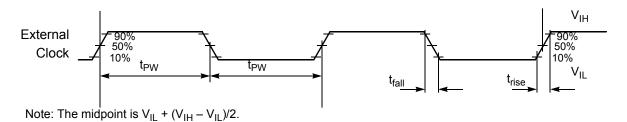

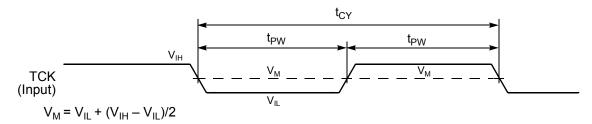

Timing waveforms in Section 4.4 are tested with a  $V_{\rm IL}$  maximum of 0.8V and a  $V_{\rm IH}$  minimum of 2.0V for all pins except XTAL, which is tested using the input levels in Section 4.2. In Figure 4-4 the levels of  $V_{\rm IH}$  and  $V_{\rm IL}$  for an input signal are shown.

Note: The midpoint is  $V_{IL} + (V_{IH} - V_{IL})/2$ .

Figure 4-4 Input Signal Measurement References

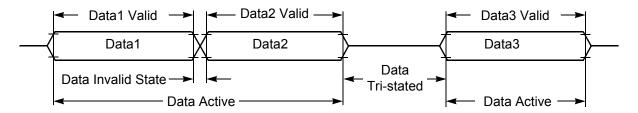

Figure 4-5 shows the definitions of the following signal states:

- Active state, when a bus or signal is driven, and enters a low impedance state

- Tri-stated, when a bus or signal is placed in a high impedance state

- Data Valid state, when a signal level has reached V<sub>OL</sub> or V<sub>OH</sub>

- Data Invalid state, when a signal level is in transition between  $V_{OL}$  and  $V_{OH}$

Figure 4-5 Signal States

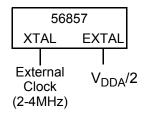

Figure 4-8 Connecting a Low Speed External Clock Signal using XTAL

### Table 4-5 External Clock Operation Timing Requirements<sup>4</sup>

$Operating\ Conditions:\ V_{SS} = V_{SSIO} = V_{SSIO} = V_{SSA} = 0\ V,\ V_{DD} = 1.62-1.98V,\ V_{DDIO} = V_{DDA} = 3.0-3.6V,\ T_{A} = -40^{\circ}\ to\ +120^{\circ}C,\ C_{L} \le 50pF,\ f_{op} = 120MHz$

| Characteristic                                              | Symbol            | Min  | Тур | Max | Unit |

|-------------------------------------------------------------|-------------------|------|-----|-----|------|

| Frequency of operation (external clock driver) <sup>1</sup> | f <sub>osc</sub>  | 0    | _   | 240 | MHz  |

| Clock Pulse Width <sup>4</sup>                              | t <sub>PW</sub>   | 6.25 | _   | _   | ns   |

| External clock input rise time <sup>2, 4</sup>              | t <sub>rise</sub> | _    | _   | TBD | ns   |

| External clock input fall time <sup>3, 4</sup>              | t <sub>fall</sub> | _    |     | TBD | ns   |

- 1. See Figure 4-7 for details on using the recommended connection of an external clock driver.

- 2. External clock input rise time is measured from 10% to 90%.

- 3. External clock input fall time is measured from 90% to 10%.

- 4. Parameters listed are guaranteed by design.

**Figure 4-9 External Clock Timing**

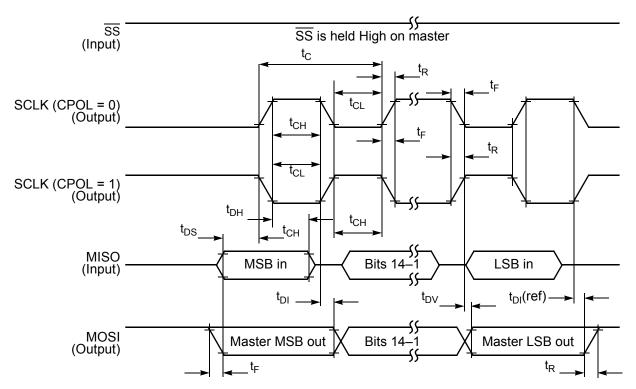

Figure 4-21 SPI Master Timing (CPHA = 0)

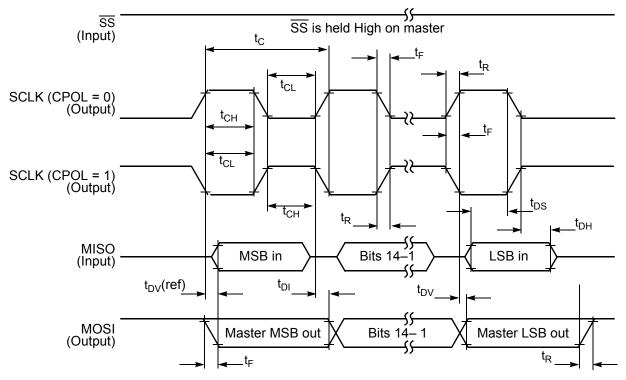

Figure 4-22 SPI Master Timing (CPHA = 1)

56857 Technical Data, Rev. 6

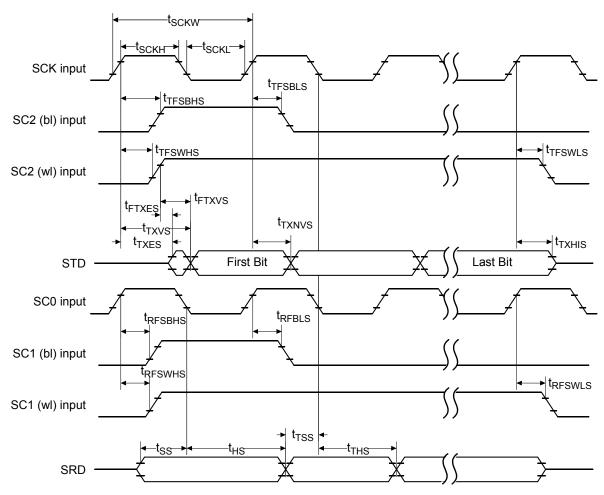

## Table 4-11 ESSI Master Mode<sup>1</sup> Switching Characteristics (Continued)

$Operating \ Conditions: \ V_{SS} = V_{SSIO} = V_{SSA} = 0 \ V, \ V_{DD} = 1.62 - 1.98 \\ V, \ V_{DDIO} = V_{DDA} = 3.0 - 3.6 \\ V, \ T_{A} = -40 \\ ^{\circ} \ to \ +120 \\ ^{\circ} C, \ C_{L} \leq 50 \\ pF, \ f_{op} = 120 \\ MHz = 1.00 \\ MHz$

| Parameter                                                                 | Symbol              | Min  | Тур | Max | Units |

|---------------------------------------------------------------------------|---------------------|------|-----|-----|-------|

| Delay from SCK high to SC2 (bl) high - Master <sup>5</sup>                | t <sub>TFSBHM</sub> | -1.0 | _   | 1.0 | ns    |

| Delay from SCK high to SC2 (wl) high - Master <sup>5</sup>                | t <sub>TFSWHM</sub> | -1.0 | _   | 1.0 | ns    |

| Delay from SC0 high to SC1 (bl) high - Master <sup>5</sup>                | t <sub>RFSBHM</sub> | -1.0 | _   | 1.0 | ns    |

| Delay from SC0 high to SC1 (wl) high - Master <sup>5</sup>                | t <sub>RFSWHM</sub> | -1.0 | _   | 1.0 | ns    |

| Delay from SCK high to SC2 (bl) low - Master <sup>5</sup>                 | t <sub>TFSBLM</sub> | -1.0 | _   | 1.0 | ns    |

| Delay from SCK high to SC2 (wl) low - Master <sup>5</sup>                 | t <sub>TFSWLM</sub> | -1.0 | _   | 1.0 | ns    |

| Delay from SC0 high to SC1 (bl) low - Master <sup>5</sup>                 | t <sub>RFSBLM</sub> | -1.0 | _   | 1.0 | ns    |

| Delay from SC0 high to SC1 (wl) low - Master <sup>5</sup>                 | t <sub>RFSWLM</sub> | -1.0 | _   | 1.0 | ns    |

| SCK high to STD enable from high impedance - Master                       | t <sub>TXEM</sub>   | -0.1 | _   | 2   | ns    |

| SCK high to STD valid - Master                                            | t <sub>TXVM</sub>   | -0.1 | _   | 2   | ns    |

| SCK high to STD not valid - Master                                        | t <sub>TXNVM</sub>  | -0.1 | _   | _   | ns    |

| SCK high to STD high impedance - Master                                   | t <sub>TXHIM</sub>  | -4   | _   | 0   | ns    |

| SRD Setup time before SC0 low - Master                                    | t <sub>SM</sub>     | 4    | _   | _   | ns    |

| SRD Hold time after SC0 low - Master                                      | t <sub>HM</sub>     | 4    | _   | _   | ns    |

| Synchronous Operation (in addition to standard internal clock parameters) |                     |      |     |     |       |

| SRD Setup time before SCK low - Master                                    | t <sub>TSM</sub>    | 4    | _   | _   | ns    |

| SRD Hold time after SCK low - Master                                      | t <sub>THM</sub>    | 4    | _   | _   | ns    |

- 1. Master mode is internally generated clocks and frame syncs

- 2. Max clock frequency is IP\_clk/4 = 60MHz / 4 = 15MHz for an 120MHz part.

- 3. All the timings for the ESSI are given for a non-inverted serial clock polarity (TSCKP=0 in SCR2 and RSCKP=0 in SCSR) and a non-inverted frame sync (TFSI=0 in SCR2 and RFSI=0 in SCSR). If the polarity of the clock and/or the frame sync have been inverted, all the timings remain valid by inverting the clock signal SCK/SC0 and/or the frame sync SC2/SC1 in the tables and in the figures.

- 4. 50 percent duty cycle

- 5. bl = bit length; wl = word length

Figure 4-27 Slave Mode Clock Timing

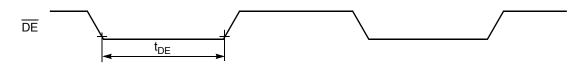

# 4.11 Serial Communication Interface (SCI) Timing

| Characteristic               | Symbol            | Min      | Max                      | Unit |

|------------------------------|-------------------|----------|--------------------------|------|

| Baud Rate <sup>1</sup>       | BR                | _        | (f <sub>MAX</sub> )/(32) | Mbps |

| RXD <sup>2</sup> Pulse Width | RXD <sub>PW</sub> | 0.965/BR | 1.04/BR                  | ns   |

| TXD <sup>3</sup> Pulse Width | TXD <sub>PW</sub> | 0.965/BR | 1.04/BR                  | ns   |

- 1.  $f_{MAX}$  is the frequency of operation of the system clock in MHz.

- 2. The RXD pin in SCI0 is named RXD0 and the RXD pin in SCI1 is named RXD1.

- 3. The TXD pin in SCI0 is named TXD0 and the TXD pin in SCI1 is named TXD1.

- 4. Parameters listed are guaranteed by design.

56857 Technical Data, Rev. 6

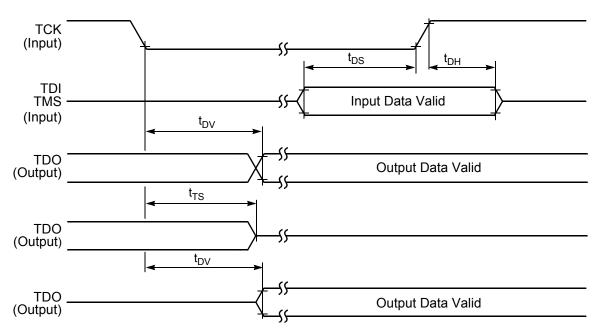

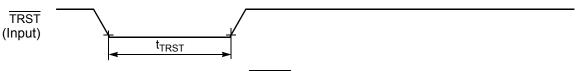

Figure 4-30 Test Clock Input Timing Diagram

Figure 4-31 Test Access Port Timing Diagram

Figure 4-32 TRST Timing Diagram

Figure 4-33 Enhanced OnCE—Debug Event

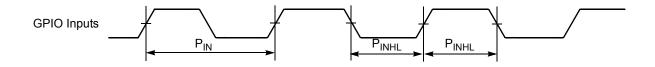

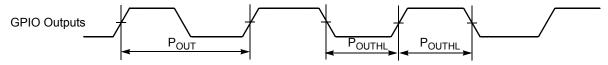

# 4.13 GPIO Timing

# Table 4-15 GPIO Timing<sup>1, 2</sup>

$Operating\ Conditions: V_{SS} = V_{SSIO} = V_{SSA} = 0\ V,\ V_{DD} = 1.62-1.98V,\ V_{DDIO} = V_{DDA} = 3.0-3.6V,\ T_A = -40^{\circ}\ to\ +120^{\circ}C,\ C_L \le 50 pF,\ f_{op} = 120 MHz$

| Characteristic              | Symbol             | Min    | Max | Unit |

|-----------------------------|--------------------|--------|-----|------|

| GPIO input period           | P <sub>IN</sub>    | 2T + 3 | _   | ns   |

| GPIO input high/low period  | P <sub>INHL</sub>  | 1T + 3 | _   | ns   |

| GPIO output period          | P <sub>OUT</sub>   | 2T - 3 | _   | ns   |

| GPIO output high/low period | P <sub>OUTHL</sub> | 1T - 3 | _   | ns   |

- 1. In the formulas listed, T = clock cycle. For  $f_{op}$  = 120MHz operation and fipb = 60MHz, T = 8.33ns

- 2. Parameters listed are guaranteed by design.

Figure 4-34 GPIO Timing

# Part 5 Packaging

## 5.1 Package and Pin-Out Information 56857

This section contains package and pin-out information for the 100-pin LQFP configuration of the 56857.

Figure 5-1 Top View, 56857 100-pin LQFP Package

# Part 6 Design Considerations

### **6.1 Thermal Design Considerations**

An estimation of the chip junction temperature, T<sub>J</sub>, in °C can be obtained from the equation:

**Equation 1:**

$$T_I = T_A + (P_D \times R_{\theta IA})$$

Where:

$T_A$  = ambient temperature °C

$R_{\theta JA}$  = package junction-to-ambient thermal resistance °C/W

$P_D$  = power dissipation in package

Historically, thermal resistance has been expressed as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

**Equation 2:**

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$$

Where:

$R_{\theta IA}$  = package junction-to-ambient thermal resistance °C/W

$R_{\theta JC}$  = package junction-to-case thermal resistance °C/W

$R_{\theta CA}$  = package case-to-ambient thermal resistance °C/W

$R_{\theta JC}$  is device-related and cannot be influenced by the user. The user controls the thermal environment to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For example, the user can change the air flow around the device, add a heat sink, change the mounting arrangement on the Printed Circuit Board (PCB), or otherwise change the thermal dissipation capability of the area surrounding the device on the PCB. This model is most useful for ceramic packages with heat sinks; some 90% of the heat flow is dissipated through the case to the heat sink and out to the ambient environment. For ceramic packages, in situations where the heat flow is split between a path to the case and an alternate path through the PCB, analysis of the device thermal performance may need the additional modeling capability of a system level thermal simulation tool.

The thermal performance of plastic packages is more dependent on the temperature of the PCB to which the package is mounted. Again, if the estimations obtained from  $R_{\theta JA}$  do not satisfactorily answer whether the thermal performance is adequate, a system level model may be appropriate.

A complicating factor is the existence of three common definitions for determining the junction-to-case thermal resistance in plastic packages:

- Measure the thermal resistance from the junction to the outside surface of the package (case) closest to the chip mounting area when that surface has a proper heat sink. This is done to minimize temperature variation across the surface.

- Measure the thermal resistance from the junction to where the leads are attached to the case. This definition is approximately equal to a junction to board thermal resistance.

- Use the value obtained by the equation  $(T_J T_T)/P_D$  where  $T_T$  is the temperature of the package case determined by a thermocouple.

As noted above, the junction-to-case thermal resistances quoted in this data sheet are determined using the first definition. From a practical standpoint, that value is also suitable for determining the junction temperature from a case thermocouple reading in forced convection environments. In natural convection, using the junction-to-case thermal resistance to estimate junction temperature from a thermocouple reading on the case of the package will estimate a junction temperature slightly hotter than actual. Hence, the new thermal metric, Thermal Characterization Parameter, or  $\Psi_{JT}$ , has been defined to be  $(T_J - T_T)/P_D$ . This value gives a better estimate of the junction temperature in natural convection when using the surface temperature of the package. Remember that surface temperature readings of packages are subject to significant errors caused by inadequate attachment of the sensor to the surface and to errors caused by heat loss to the sensor. The recommended technique is to attach a 40-gauge thermocouple wire and bead to the top center of the package with thermally conductive epoxy.

### **6.2 Electrical Design Considerations**

### **CAUTION**

This device contains protective circuitry to guard against damage due to high static voltage or electrical fields. However, normal precautions are advised to avoid application of any voltages higher than maximum rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate voltage level.

Use the following list of considerations to assure correct operation:

- Provide a low-impedance path from the board power supply to each V<sub>DD</sub> pin on the controller, and from the board ground to each V<sub>SS</sub> (GND) pin.

- The minimum bypass requirement is to place six  $0.01-0.1~\mu F$  capacitors positioned as close as possible to the package supply pins. The recommended bypass configuration is to place one bypass capacitor on each of the ten  $V_{DD}/V_{SS}$  pairs, including  $V_{DDA}/V_{SSA}$ .

- Ensure that capacitor leads and associated printed circuit traces that connect to the chip V<sub>DD</sub> and V<sub>SS</sub> (GND) pins are less than 0.5 inch per capacitor lead.

- Use at least a four-layer Printed Circuit Board (PCB) with two inner layers for V<sub>DD</sub> and GND.

- Bypass the  $V_{DD}$  and GND layers of the PCB with approximately 100  $\mu$ F, preferably with a high-grade capacitor such as a tantalum capacitor.

- Because the device's output signals have fast rise and fall times, PCB trace lengths should be minimal.

- Consider all device loads as well as parasitic capacitance due to PCB traces when calculating capacitance.

This is especially critical in systems with higher capacitive loads that could create higher transient currents in the V<sub>DD</sub> and GND circuits.

- All inputs must be terminated (i.e., not allowed to float) using CMOS levels.

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### E-mail:

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc. 2005. All rights reserved.

DSP56857 Rev. 6 01/2007