Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 72MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, Microwire, SPI, SSI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 28                                                                       |

| Program Memory Size        | 8KB (8K x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 4K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-HVQFN (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1311fhn33-551 |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

32-bit ARM Cortex-M3 microcontroller

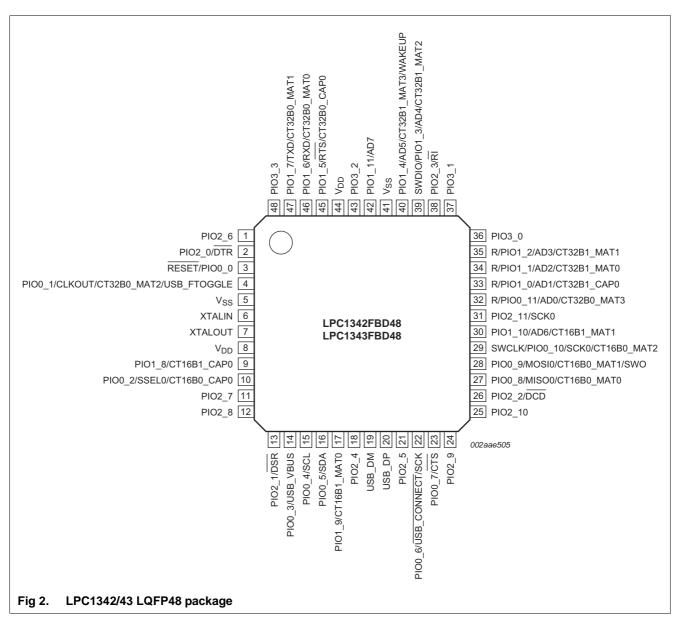

# 6. Pinning information

## 6.1 Pinning

32-bit ARM Cortex-M3 microcontroller

# 6.2 Pin description

| Table 3. LPC1313/4                            | 2/43 LO                  | QFP48 p                 | in desc | ription               | table                                                                                                                                                                                                                                              |

|-----------------------------------------------|--------------------------|-------------------------|---------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                                        | Pin                      | Start<br>logic<br>input | Туре    | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                        |

| RESET/PIO0_0                                  | 3 <u>[2]</u>             | yes                     | I       | I; PU                 | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. |

|                                               |                          |                         | I/O     | -                     | <b>PIO0_0</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                 |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2/<br>USB_FTOGGLE | 4 <u>[3]</u>             | yes                     | I/O     | I; PU                 | <b>PIO0_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler or the USB device enumeration (USB on LPC1342/43 only, see description of PIO0_3).                                   |

|                                               |                          |                         | 0       | -                     | CLKOUT — Clockout pin.                                                                                                                                                                                                                             |

|                                               |                          |                         | 0       | -                     | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                   |

|                                               |                          |                         | 0       | -                     | <b>USB_FTOGGLE</b> — USB 1 ms Start-of-Frame signal (LPC1342/43 only).                                                                                                                                                                             |

| PIO0_2/SSEL0/                                 | 10 <u><sup>[3]</sup></u> | yes                     | I/O     | I; PU                 | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| CT16B0_CAP0                                   |                          |                         | I/O     | -                     | SSEL0 — Slave select for SSP0.                                                                                                                                                                                                                     |

|                                               |                          |                         | Ι       | -                     | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                  |

| PIO0_3/USB_VBUS                               | 14 <u><sup>[3]</sup></u> | yes                     | I/O     | I; PU                 | <b>PIO0_3</b> — General purpose digital input/output pin. LPC1342/43 only: A LOW level on this pin during reset starts the ISP command handler, a HIGH level starts the USB device enumeration.                                                    |

|                                               |                          |                         | I       | -                     | <b>USB_VBUS</b> — Monitors the presence of USB bus power (LPC1342/43 only).                                                                                                                                                                        |

| PIO0_4/SCL                                    | 15 <u><sup>[4]</sup></u> | yes                     | I/O     | I; IA                 | PIO0_4 — General purpose digital input/output pin (open-drain).                                                                                                                                                                                    |

|                                               |                          |                         | I/O     | -                     | <b>SCL</b> — $I^2$ C-bus clock input/output (open-drain). High-current sink only if $I^2$ C Fast-mode Plus is selected in the I/O configuration register.                                                                                          |

| PIO0_5/SDA                                    | 16 <u><sup>[4]</sup></u> | yes                     | I/O     | I; IA                 | PIO0_5 — General purpose digital input/output pin (open-drain).                                                                                                                                                                                    |

|                                               |                          |                         | I/O     | -                     | <b>SDA</b> — I <sup>2</sup> C-bus data input/output (open-drain). High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                         |

| PIO0_6/                                       | 22 <sup>[3]</sup>        | yes                     | I/O     | I; PU                 | PIO0_6 — General purpose digital input/output pin.                                                                                                                                                                                                 |

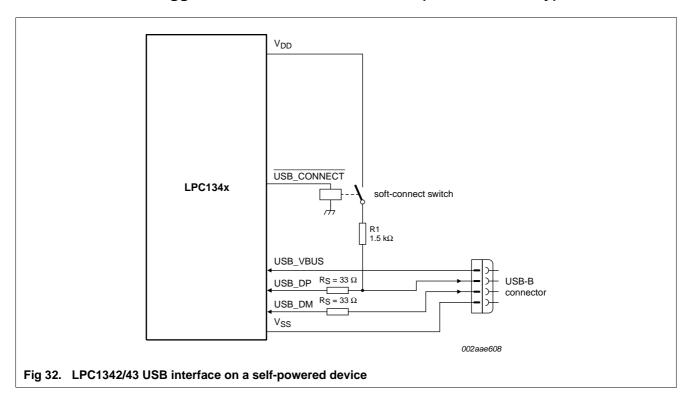

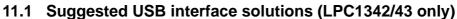

| USB_CONNECT/<br>SCK0                          |                          |                         | 0       | -                     | <b>USB_CONNECT</b> — Signal used to switch an external 1.5 k $\Omega$ resistor under software control. Used with the SoftConnect USB feature (LPC1342/43 only).                                                                                    |

|                                               |                          |                         | I/O     | -                     | SCK0 — Serial clock for SSP0.                                                                                                                                                                                                                      |

| PIO0_7/CTS                                    | 23 <u>[3]</u>            | yes                     | I/O     | I; PU                 | <b>PIO0_7</b> — General purpose digital input/output pin (high-current output driver).                                                                                                                                                             |

|                                               |                          |                         | Ι       | -                     | CTS — Clear To Send input for UART.                                                                                                                                                                                                                |

| PIO0_8/MISO0/                                 | 27 <u>[3]</u>            | yes                     | I/O     | I; PU                 | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| CT16B0_MAT0                                   |                          |                         | I/O     | -                     | MISO0 — Master In Slave Out for SSP0.                                                                                                                                                                                                              |

|                                               |                          |                         | 0       | -                     | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                                   |

### 32-bit ARM Cortex-M3 microcontroller

| Symbol                        | Pin               | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                          |

|-------------------------------|-------------------|-------------------------|------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_9/MOSI0/                 | 28 <u>[3]</u>     | yes                     | I/O  | I; PU                 | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                                                                   |

| CT16B0_MAT1/                  |                   |                         | I/O  | -                     | MOSI0 — Master Out Slave In for SSP0.                                                                                                                                                                                                                |

| SWO                           |                   |                         | 0    | -                     | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                                     |

|                               |                   |                         | 0    | -                     | <b>SWO</b> — Serial wire trace output.                                                                                                                                                                                                               |

| SWCLK/PIO0_10/                | 29 <u>[3]</u>     | yes                     | I    | I; PU                 | SWCLK — Serial wire clock.                                                                                                                                                                                                                           |

| SCK0/CT16B0_MAT2              |                   |                         | I/O  | -                     | PIO0_10 — General purpose digital input/output pin.                                                                                                                                                                                                  |

|                               |                   |                         | I/O  | -                     | SCK0 — Serial clock for SSP0.                                                                                                                                                                                                                        |

|                               |                   |                         | 0    | -                     | CT16B0_MAT2 — Match output 2 for 16-bit timer 0.                                                                                                                                                                                                     |

| R/PIO0_11/<br>AD0/CT32B0_MAT3 | 32 <sup>[5]</sup> | yes                     | -    | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                      |

|                               |                   |                         | I/O  | -                     | PIO0_11 — General purpose digital input/output pin.                                                                                                                                                                                                  |

|                               |                   |                         | I    | -                     | AD0 — A/D converter, input 0.                                                                                                                                                                                                                        |

|                               |                   |                         | 0    | -                     | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                                                                                                     |

| R/PIO1_0/<br>AD1/CT32B1_CAP0  | 33 <u>[5]</u>     | yes                     | -    | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                      |

|                               |                   |                         | I/O  | -                     | PIO1_0 — General purpose digital input/output pin.                                                                                                                                                                                                   |

|                               |                   |                         | Ι    | -                     | AD1 — A/D converter, input 1.                                                                                                                                                                                                                        |

|                               |                   |                         | Ι    | -                     | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                                                                                    |

| R/PIO1_1/<br>AD2/CT32B1_MAT0  | 34 <u>[5]</u>     | yes                     | -    | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                      |

|                               |                   |                         | I/O  | -                     | PIO1_1 — General purpose digital input/output pin.                                                                                                                                                                                                   |

|                               |                   |                         | Ι    | -                     | AD2 — A/D converter, input 2.                                                                                                                                                                                                                        |

|                               |                   |                         | 0    | -                     | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                                                                                     |

| R/PIO1_2/<br>AD3/CT32B1_MAT1  | 35 <u>[5]</u>     | yes                     | -    | I; PU                 | <b>R</b> — Reserved. Configure for an alternate function in the IOCONFIG block.                                                                                                                                                                      |

|                               |                   |                         | I/O  | -                     | PIO1_2 — General purpose digital input/output pin.                                                                                                                                                                                                   |

|                               |                   |                         | I    | -                     | AD3 — A/D converter, input 3.                                                                                                                                                                                                                        |

|                               |                   |                         | 0    | -                     | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                                                                                                                                                     |

| SWDIO/PIO1_3/                 | 39 <u>[5]</u>     | yes                     | I/O  | I; PU                 | SWDIO — Serial wire debug input/output.                                                                                                                                                                                                              |

| AD4/<br>CT32B1_MAT2           |                   |                         | I/O  | -                     | PIO1_3 — General purpose digital input/output pin.                                                                                                                                                                                                   |

| ••••=                         |                   |                         | 1    | -                     | AD4 — A/D converter, input 4.                                                                                                                                                                                                                        |

|                               |                   |                         | 0    | -                     | CT32B1_MAT2 — Match output 2 for 32-bit timer 1.                                                                                                                                                                                                     |

| PIO1_4/AD5/<br>CT32B1_MAT3/   | 40 <u>[5]</u>     | yes                     | I/O  | I; PU                 | <b>PIO1_4</b> — General purpose digital input/output pin.                                                                                                                                                                                            |

| WAKEUP                        |                   |                         | Ι    | -                     | AD5 — A/D converter, input 5.                                                                                                                                                                                                                        |

|                               |                   |                         | 0    | -                     | CT32B1_MAT3 — Match output 3 for 32-bit timer 1.                                                                                                                                                                                                     |

|                               |                   |                         | I    | -                     | <b>WAKEUP</b> — Deep power-down mode wake-up pin with 20 ns glitch filter. This pin must be pulled HIGH externally to enter Deep power-down mode and pulled LOW to exit Deep power-down mode. A LOW-going pulse as short as 50 ns wakes up the part. |

### Table 3. LPC1313/42/43 LQFP48 pin description table ...continued

### 32-bit ARM Cortex-M3 microcontroller

| Table 4. LPC131                               | 1/13/42                  | 2/43 HV                 | QFN33 | pin de                | scription table                                                                                                                                                                                                                                    |

|-----------------------------------------------|--------------------------|-------------------------|-------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                                        | Pin                      | Start<br>Iogic<br>input | Туре  | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                        |

| RESET/PIO0_0 2 <sup>[2]</sup> yes             |                          | <sup>2]</sup> yes I     |       | I; PU                 | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. |

|                                               |                          |                         | I/O   | -                     | <b>PIO0_0</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                 |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2/<br>USB_FTOGGLE | 3 <u>[3]</u>             | yes                     | I/O   | I; PU                 | <b>PIO0_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler or the USB device enumeration (USB on LPC1342/43 only, see description of PIO0_3).                                   |

|                                               |                          |                         | 0     | -                     | CLKOUT — Clock out pin.                                                                                                                                                                                                                            |

|                                               |                          |                         | 0     | -                     | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                   |

|                                               |                          |                         | 0     | -                     | <b>USB_FTOGGLE</b> — USB 1 ms Start-of-Frame signal (LPC1342/43 only).                                                                                                                                                                             |

| PIO0_2/SSEL0/                                 | 8 <u>[3]</u>             | yes                     | I/O   | I; PU                 | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| CT16B0_CAP0                                   |                          |                         | I/O   | -                     | SSEL0 — Slave select for SSP0.                                                                                                                                                                                                                     |

|                                               |                          |                         | I     | -                     | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                  |

| PIO0_3/<br>USB_VBUS                           | 9 <u>[3]</u>             | yes                     | I/O   | I; PU                 | <b>PIO0_3</b> — General purpose digital input/output pin. LPC1342/43 only: A LOW level on this pin during reset starts the ISP command handler, a HIGH level starts the USB device enumeration.                                                    |

|                                               |                          |                         | I     | -                     | <b>USB_VBUS</b> — Monitors the presence of USB bus power (LPC1342/43 only).                                                                                                                                                                        |

| PIO0_4/SCL                                    | 10 <u><sup>[4]</sup></u> | yes                     | I/O   | I; IA                 | PIO0_4 — General purpose digital input/output pin (open-drain).                                                                                                                                                                                    |

|                                               |                          |                         | I/O   | -                     | $\label{eq:scl} \begin{array}{l} \textbf{SCL} - I^2 C \text{-bus clock input/output (open-drain). High-current sink only if} \\ I^2 C \ \text{Fast-mode Plus is selected in the I/O configuration register.} \end{array}$                          |

| PIO0_5/SDA                                    | 11 <u><sup>[4]</sup></u> | yes                     | I/O   | I; IA                 | PIO0_5 — General purpose digital input/output pin (open-drain).                                                                                                                                                                                    |

|                                               |                          |                         | I/O   | -                     | <b>SDA</b> — $I^2C$ -bus data input/output (open-drain). High-current sink only if $I^2C$ Fast-mode Plus is selected in the I/O configuration register.                                                                                            |

| PIO0_6/                                       | 15 <u>[3]</u>            | yes                     | I/O   | I; PU                 | PIO0_6 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| USB_CONNECT/<br>SCK0                          |                          |                         | 0     | -                     | <b>USB_CONNECT</b> — Signal used to switch an external 1.5 k $\Omega$ resistor under software control. Used with the SoftConnect USB feature (LPC1342/43 only).                                                                                    |

|                                               |                          |                         | I/O   | -                     | SCK0 — Serial clock for SSP0.                                                                                                                                                                                                                      |

| PIO0_7/CTS                                    | 16 <u>[3]</u>            | yes                     | I/O   | I; PU                 | <b>PIO0_7</b> — General purpose digital input/output pin (high-current output driver).                                                                                                                                                             |

|                                               |                          |                         | I     | -                     | <b>CTS</b> — Clear To Send input for UART.                                                                                                                                                                                                         |

| PIO0_8/MISO0/                                 | 17 <u>[3]</u>            | yes                     | I/O   | I; PU                 | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| CT16B0_MAT0                                   |                          |                         | I/O   |                       | MISO0 — Master In Slave Out for SSP0.                                                                                                                                                                                                              |

|                                               |                          |                         | 0     | -                     | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                                   |

| PIO0_9/MOSI0/                                 | 18 <u>[3]</u>            | yes                     | I/O   | I; PU                 | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| CT16B0_MAT1/<br>SWO                           |                          |                         | I/O   | -                     | MOSI0 — Master Out Slave In for SSP0.                                                                                                                                                                                                              |

|                                               |                          |                         | 0     | -                     | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                                   |

|                                               |                          |                         | 0     | -                     | <b>SWO</b> — Serial wire trace output.                                                                                                                                                                                                             |

#### Table 4. LPC1311/13/42/43 HVQFN33 pin description table

Product data sheet

32-bit ARM Cortex-M3 microcontroller

# 7. Functional description

### 7.1 Architectural overview

The ARM Cortex-M3 includes three AHB-Lite buses: the system bus, the I-code bus, and the D-code bus (see <u>Figure 1</u>). The I-code and D-code core buses are faster than the system bus and are used similarly to TCM interfaces: one bus dedicated for instruction fetch (I-code) and one bus for data access (D-code). The use of two core buses allows for simultaneous operations if concurrent operations target different devices.

## 7.2 ARM Cortex-M3 processor

The ARM Cortex-M3 is a general purpose, 32-bit microprocessor, which offers high performance and very low power consumption. The ARM Cortex-M3 offers many new features, including a Thumb-2 instruction set, low interrupt latency, hardware multiply and divide, interruptible/continuable multiple load and store instructions, automatic state save and restore for interrupts, tightly integrated interrupt controller, and multiple core buses capable of simultaneous accesses.

Pipeline techniques are employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

The ARM Cortex-M3 processor is described in detail in the *Cortex-M3 Technical Reference Manual* which is available on the official ARM website.

## 7.3 On-chip flash program memory

The LPC1311/13/42/43 contain 32 kB (LPC1313 and LPC1343), 16 kB (LPC1342), or 8 kB (LPC1311) of on-chip flash memory.

## 7.4 On-chip SRAM

The LPC1311/13/42/43 contain a total of 8 kB (LPC1343 and LPC1313) or 4 kB (LPC1342 and LPC1311) on-chip static RAM memory.

### 7.5 Memory map

The LPC1311/13/42/43 incorporate several distinct memory regions. <u>Figure 6</u> shows the overall map of the entire address space from the user program viewpoint following reset. The interrupt vector area supports address remapping.

The AHB peripheral area is 2 MB in size and is divided to allow for up to 128 peripherals. The APB peripheral area is 512 kB in size and is divided to allow for up to 32 peripherals. Each peripheral of either type is allocated 16 kB of space. This allows simplifying the address decoding for each peripheral.

### 32-bit ARM Cortex-M3 microcontroller

The I<sup>2</sup>C-bus is bidirectional for inter-IC control using only two wires: a Serial Clock Line (SCL) and a Serial DAta line (SDA). Each device is recognized by a unique address and can operate as either a receiver-only device (e.g., an LCD driver) or a transmitter with the capability to both receive and send information (such as memory). Transmitters and/or receivers can operate in either master or slave mode, depending on whether the chip has to initiate a data transfer or is only addressed. The I<sup>2</sup>C is a multi-master bus and can be controlled by more than one bus master connected to it.

### 7.12.1 Features

- The I<sup>2</sup>C-bus interface is a standard I<sup>2</sup>C-bus compliant interface with true open-drain pins. The I<sup>2</sup>C-bus interface also supports Fast-mode Plus with bit rates up to 1 Mbit/s.

- Easy to configure as master, slave, or master/slave.

- Programmable clocks allow versatile rate control.

- Bidirectional data transfer between masters and slaves.

- Multi-master bus (no central master).

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus.

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus.

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer.

- The I<sup>2</sup>C-bus can be used for test and diagnostic purposes.

- The I<sup>2</sup>C-bus controller supports multiple address recognition and a bus monitor mode.

## 7.13 10-bit ADC

The LPC1311/13/42/43 contains one ADC. It is a single 10-bit successive approximation ADC with eight channels.

### 7.13.1 Features

- 10-bit successive approximation ADC.

- Input multiplexing among 8 pins.

- Power-down mode.

- Measurement range 0 V to V<sub>DD</sub>.

- 10-bit conversion time  $\ge$  2.44 µs (up to 400 kSamples/s).

- Burst conversion mode for single or multiple inputs.

- Optional conversion on transition of input pin or timer match signal.

- Individual result registers for each ADC channel to reduce interrupt overhead.

### 32-bit ARM Cortex-M3 microcontroller

The vector table may be located anywhere within the bottom 1 GB of Cortex-M3 address space. The vector table must be located on a 256 word boundary.

## 7.20 Emulation and debugging

Debug functions are integrated into the ARM Cortex-M3. Serial wire debug is supported.

32-bit ARM Cortex-M3 microcontroller

# 9. Static characteristics

### Table 7. Static characteristics

$T_{amb} = -40 \degree C$  to +85  $\degree C$ , unless otherwise specified.

|                   | Parameter                               | Conditions                                                                                                    |                            | Min      | Тур <u><sup>[1]</sup></u> | Max | Unit |

|-------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------|----------|---------------------------|-----|------|

| / <sub>DD</sub>   | supply voltage (core and external rail) |                                                                                                               | [2]                        | 2.0      | 3.3                       | 3.6 | V    |

| PC1300            | series (LPC1311/13/42/                  | 43) power consumption                                                                                         |                            |          |                           |     |      |

| <sub>DD</sub> sup | supply current                          | Active mode; V <sub>DD</sub> = 3.3 V;<br>T <sub>amb</sub> = 25 °C; code<br>while(1){}<br>executed from flash; |                            |          |                           |     |      |

|                   |                                         | system clock = 12 MHz                                                                                         | <u>[3][4][5]</u><br>[6][7] | -        | 4                         | -   | mA   |

|                   |                                         | system clock = 72 MHz                                                                                         | [4][5][6]<br>[8][7]        | -        | 17                        | -   | mA   |

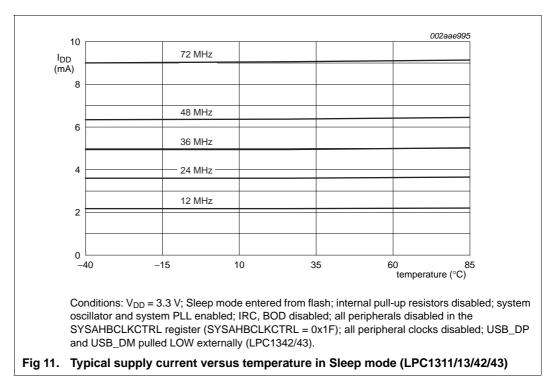

|                   |                                         | Sleep mode;<br>$V_{DD} = 3.3 \text{ V}; \text{ T}_{amb} = 25 \text{ °C};$<br>system clock = 12 MHz            | <u>[3][4][5]</u><br>[6][7] | -        | 2                         | -   | mA   |

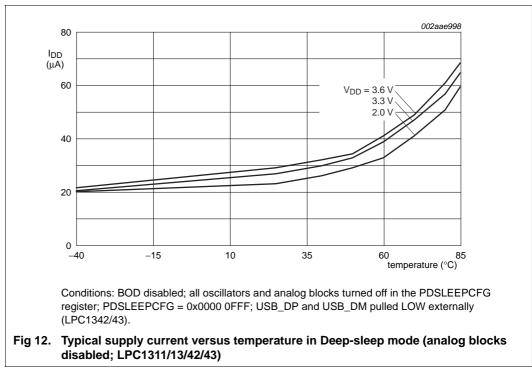

|                   |                                         | Deep-sleep mode; $V_{DD} = 3.3 \text{ V};$<br>$T_{amb} = 25 \text{ °C}$                                       | [4][9][7]                  | -        | 30                        | -   | μA   |

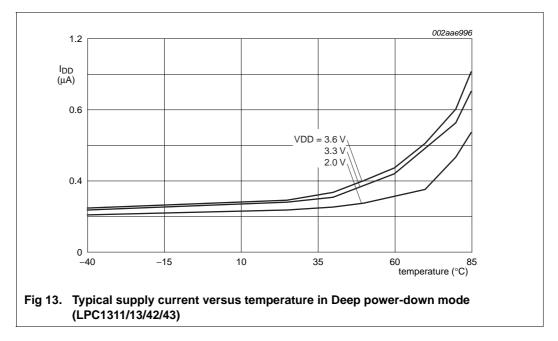

|                   |                                         | Deep power-down mode;<br>V <sub>DD</sub> = 3.3 V; T <sub>amb</sub> = 25 °C                                    | [10]                       | -        | 220                       | -   | nA   |

| PC1300            | L series (LPC1311/01, L                 | PC1313/01) power consumption in I                                                                             | ow-curre                   | ent mode | [11]                      |     |      |

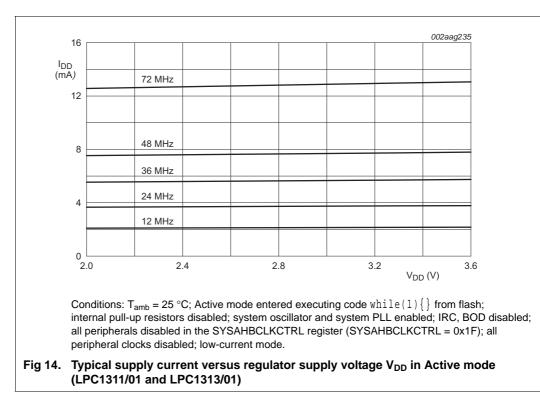

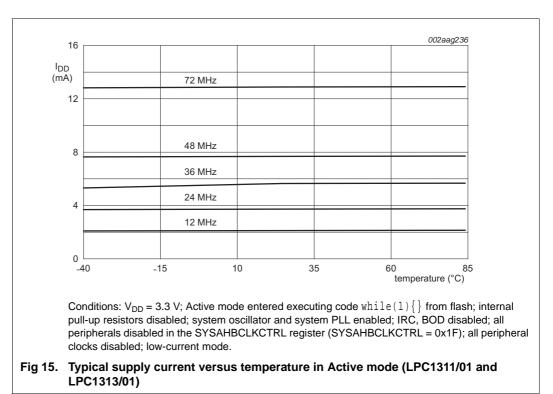

| DD                | supply current                          | Active mode; $V_{DD} = 3.3 V$ ;<br>$T_{amb} = 25 $ °C; code                                                   |                            |          |                           |     |      |

|                   |                                         | while(1){}                                                                                                    |                            |          |                           |     |      |

|                   |                                         | executed from flash;                                                                                          |                            |          |                           |     |      |

|                   |                                         | system clock = 12 MHz                                                                                         | [3][4][5]<br>[6][7]        | -        | 2                         | -   | mA   |

|                   |                                         | system clock = 72 MHz                                                                                         | [4][5][6]<br>[8][7]        | -        | 13                        | -   | mA   |

|                   |                                         | Sleep mode;<br>$V_{DD} = 3.3 \text{ V}; \text{ T}_{amb} = 25 \text{ °C};$<br>system clock = 12 MHz            | <u>[3][4][5]</u><br>[6][7] | -        | 1                         | -   | mA   |

|                   |                                         | Deep-sleep mode; $V_{DD}$ = 3.3 V;<br>T <sub>amb</sub> = 25 °C                                                | <u>[4][9][7]</u>           | -        | 2                         | -   | μA   |

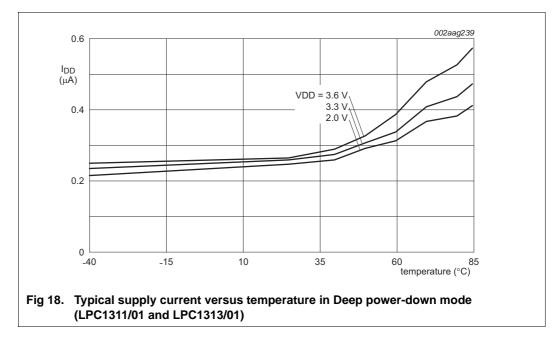

|                   |                                         | Deep power-down mode;<br>$V_{DD} = 3.3 \text{ V}; T_{amb} = 25 \text{ °C}$                                    | [10]                       | -        | 220                       | -   | nA   |

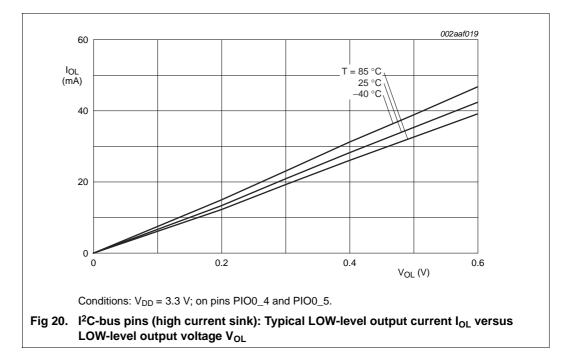

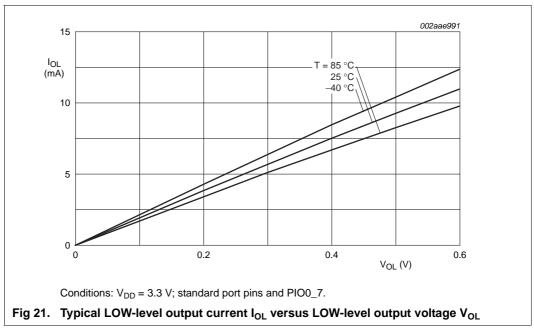

| Standard          | I port pins and RESET p                 | in; see <u>Figure 21, Figure 22, Figure :</u>                                                                 | 23, Figur                  | e 24     |                           |     |      |

| L                 | LOW-level input current                 | V <sub>I</sub> = 0 V; on-chip pull-up resistor disabled                                                       |                            | -        | 0.5                       | 10  | nA   |

| IH                | HIGH-level input<br>current             | $V_I = V_{DD}$ ; on-chip pull-down resistor disabled                                                          |                            | -        | 0.5                       | 10  | nA   |

| OZ                | OFF-state output current                | $V_O = 0 V$ ; $V_O = V_{DD}$ ; on-chip pull-up/down resistors disabled                                        |                            | -        | 0.5                       | 10  | nA   |

| /1                | input voltage                           | pin configured to provide a digital function                                                                  | [12][13]<br>[14]           | 0        | -                         | 5.0 | V    |

|                   |                                         |                                                                                                               |                            |          |                           |     |      |

### 32-bit ARM Cortex-M3 microcontroller

| $I_{amb} = -4$     | O°C to +85 °C, unless of                                                    | nerwise specified.                                         |                |     |                |      |      |

|--------------------|-----------------------------------------------------------------------------|------------------------------------------------------------|----------------|-----|----------------|------|------|

| Symbol             | Parameter                                                                   | Conditions                                                 | М              | lin | Typ <u>[1]</u> | Max  | Unit |

| V <sub>OH</sub>    | HIGH-level output voltage                                                   | driven; for low-/full-speed; $R_L$ of 15 k $\Omega$ to GND | <u>[17]</u> 2. | .8  | -              | 3.5  | V    |

| C <sub>trans</sub> | transceiver capacitance                                                     | pin to GND                                                 | <u>[17]</u> _  |     | -              | 20   | pF   |

| Z <sub>DRV</sub>   | driver output<br>impedance for driver<br>which is not high-speed<br>capable | with 33 $\Omega$ series resistor; steady state drive       | [18][17] 36    | 6   | -              | 44.1 | Ω    |

#### Table 7. Static characteristics ...continued

$T_{amb} = -40 \degree C$  to +85  $\degree C$ , unless otherwise specified

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

[2] For LPC1342 and LPC1343 only: For USB operation 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V. Guaranteed by design.

[3] IRC enabled; system oscillator disabled; system PLL disabled.

[4] I<sub>DD</sub> measurements were performed with all pins configured as GPIO outputs driven LOW and pull-up resistors disabled.

[5] BOD disabled.

[6] All peripherals disabled in the SYSAHBCLKCTRL register. Peripheral clocks to UART, SSP, trace clock, and SysTick timer disabled in the syscon block.

[7] For LPC1342/43: USB\_DP and USB\_DM pulled LOW externally.

- [8] IRC disabled; system oscillator enabled; system PLL enabled.

- [9] All oscillators and analog blocks turned off in the PDSLEEPCFG register; PDSLEEPCFG = 0x0000 0FFF.

- [10] WAKEUP pin pulled HIGH externally. An external pull-up resistor is required on the RESET pin for the Deep power-down mode.

- [11] Low-current mode PWR\_LOW\_CURRENT selected when running the set\_power routine in the power profiles.

[12] Including voltage on outputs in 3-state mode.

- [13] V<sub>DD</sub> supply voltage must be present.

- [14] 3-state outputs go into 3-state mode in Deep power-down mode.

- [15] Allowed as long as the current limit does not exceed the maximum current allowed by the device.

- [16] To V<sub>SS</sub>.

- [17] 3.0 V  $\leq$  V\_{DD}  $\leq$  3.6 V.

- [18] Includes external resistors of 33  $\Omega\pm$  1 % on USB\_DP and USB\_DM.

#### Table 8. ADC static characteristics

$T_{amb} = -40 \degree C$  to +85  $\degree C$  unless otherwise specified; ADC frequency 4.5 MHz,  $V_{DD} = 2.5 V$  to 3.6 V.

| Symbol              | Parameter                           | Conditions | Min      | Тур | Max             | Unit |

|---------------------|-------------------------------------|------------|----------|-----|-----------------|------|

| VIA                 | analog input voltage                |            | 0        | -   | V <sub>DD</sub> | V    |

| C <sub>ia</sub>     | analog input capacitance            |            | -        | -   | 1               | pF   |

| E <sub>D</sub>      | differential linearity error        |            | [1][2] _ | -   | ±1              | LSB  |

| E <sub>L(adj)</sub> | integral non-linearity              |            | [3] _    | -   | ±1.5            | LSB  |

| Eo                  | offset error                        |            | [4] _    | -   | ±3.5            | LSB  |

| E <sub>G</sub>      | gain error                          |            | [5] _    | -   | 0.6             | %    |

| E <sub>T</sub>      | absolute error                      |            | [6] _    | -   | ±4              | LSB  |

| R <sub>vsi</sub>    | voltage source interface resistance |            | -        | -   | 40              | kΩ   |

| R <sub>i</sub>      | input resistance                    |            | [7][8] _ | -   | 2.5             | MΩ   |

[1] The ADC is monotonic, there are no missing codes.

[2] The differential linearity error (E<sub>D</sub>) is the difference between the actual step width and the ideal step width. See Figure 8.

LPC1311 13 42 43

### 32-bit ARM Cortex-M3 microcontroller

32-bit ARM Cortex-M3 microcontroller

# 9.4 Power consumption for LPC1300L series (LPC1311/01 and LPC1313/01)

Remark: Applies to parts LPC1311/01 and LPC1313/01 and all their packages.

Power measurements in Active, Sleep, and Deep-sleep modes were performed under the following conditions (see *LPC13xx user manual*):

- Configure all pins as GPIO with pull-up resistor disabled in the IOCONFIG block.

- Configure GPIO pins as outputs using the GPIOnDIR registers.

- Write 0 to all GPIOnDATA registers to drive the outputs LOW.

### 32-bit ARM Cortex-M3 microcontroller

32-bit ARM Cortex-M3 microcontroller

## 9.5 Peripheral power consumption

The supply current per peripheral is measured as the difference in supply current between the peripheral block enabled and the peripheral block disabled in the SYSAHBCLKCFG or PDRUNCFG (for analog blocks) registers. All other blocks are disabled in both registers and no code is executed. Measured on a typical sample at  $T_{amb} = 25$  °C. Unless noted otherwise, the system oscillator and PLL are running in both measurements.

The supply currents are shown for system clock frequencies of 12 MHz, 48 MHz, and 72 MHz.

| Table 11. | Power consumption for individual analog and digital blocks |

|-----------|------------------------------------------------------------|

|-----------|------------------------------------------------------------|

| Peripheral                             | Typical s | supply cur | rent in mA | ۹.     | Notes                                                                    |

|----------------------------------------|-----------|------------|------------|--------|--------------------------------------------------------------------------|

|                                        | n/a       | 12 MHz     | 48 MHz     | 72 MHz |                                                                          |

| IRC                                    | 0.23      | -          | -          | -      | System oscillator running; PLL off; independent of main clock frequency. |

| System oscillator at 12 MHz            | 0.23      | -          | -          | -      | IRC running; PLL off; independent of main clock frequency.               |

| Watchdog<br>oscillator at<br>500 kHz/2 | 0.002     | -          | -          | -      | System oscillator running; PLL off; independent of main clock frequency. |

| BOD                                    | 0.045     | -          | -          | -      | Independent of main clock frequency.                                     |

| Main or USB PLL                        | -         | 0.26       | 0.34       | 0.48   | •                                                                        |

| ADC                                    | -         | 0.07       | 0.25       | 0.37   | -                                                                        |

| CLKOUT                                 | -         | 0.14       | 0.56       | 0.82   | Main clock divided by 4 in the CLKOUTDIV register.                       |

| CT16B0                                 | -         | 0.01       | 0.05       | 0.08   | -                                                                        |

| CT16B1                                 | -         | 0.01       | 0.04       | 0.06   | •                                                                        |

| CT32B0                                 | -         | 0.01       | 0.05       | 0.07   | •                                                                        |

| CT32B1                                 | -         | 0.01       | 0.04       | 0.06   | -                                                                        |

LPC1311\_13\_42\_43

Product data sheet

### 32-bit ARM Cortex-M3 microcontroller

#### 32-bit ARM Cortex-M3 microcontroller

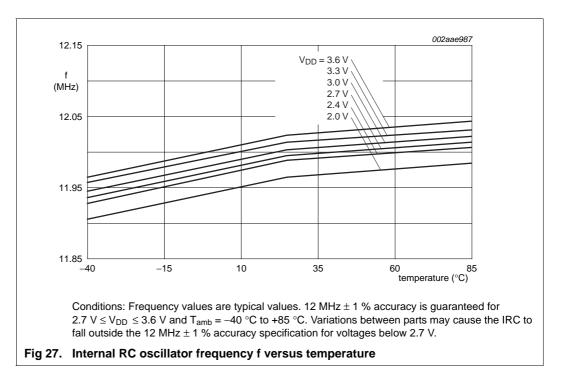

### 10.4 Internal oscillators

#### Table 15. Dynamic characteristics: IRC

$T_{amb} = -40 \circ C$  to +85  $\circ C$ ; 2.7 V  $\leq V_{DD} \leq 3.6 V^{[1]}$ .

| Symbol               | Parameter                        | Conditions | Min   | Typ <u>[2]</u> | Max   | Unit |

|----------------------|----------------------------------|------------|-------|----------------|-------|------|

| f <sub>osc(RC)</sub> | internal RC oscillator frequency | -          | 11.88 | 12             | 12.12 | MHz  |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

#### Table 16. Dynamic characteristics: Watchdog oscillator

| Symbol                | Parameter                     | Conditions                                                 |               | Min | Typ <u>[1]</u> | Max | Unit |

|-----------------------|-------------------------------|------------------------------------------------------------|---------------|-----|----------------|-----|------|

| f <sub>osc(int)</sub> | internal oscillator frequency | DIVSEL = 0x1F, FREQSEL = 0x1 in the WDTOSCCTRL register;   | <u>[2][3]</u> | -   | 7.8            | -   | kHz  |

|                       |                               | DIVSEL = 0x00, FREQSEL = 0xF in the<br>WDTOSCCTRL register | [2][3]        | -   | 1700           | -   | kHz  |

[1] Typical ratings are not guaranteed. The values listed are at nominal supply voltages.

[2] The typical frequency spread over processing and temperature (T<sub>amb</sub> =  $-40 \text{ }^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ) is ±40 %.

[3] See the LPC13xx user manual.

32-bit ARM Cortex-M3 microcontroller

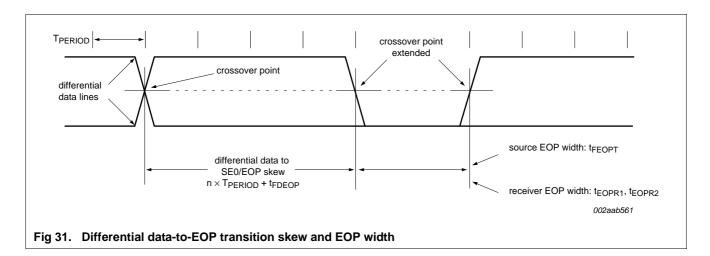

## 10.8 USB interface (LPC1342/43 only)

#### Table 20. Dynamic characteristics: USB pins (full-speed)

$C_L = 50 \text{ pF}$ ;  $R_{pu} = 1.5 \text{ k}\Omega$  on D+ to  $V_{DD}$ , unless otherwise specified. 3.0 V  $\leq V_{DD} \leq$  3.6 V

|                    |                                                             | -                                       |            |       |     |       |      |

|--------------------|-------------------------------------------------------------|-----------------------------------------|------------|-------|-----|-------|------|

| Symbol             | Parameter                                                   | Conditions                              |            | Min   | Тур | Max   | Unit |

| t <sub>r</sub>     | rise time                                                   | 10 % to 90 %                            |            | 8.5   | -   | 13.8  | ns   |

| t <sub>f</sub>     | fall time                                                   | 10 % to 90 %                            |            | 7.7   | -   | 13.7  | ns   |

| t <sub>FRFM</sub>  | differential rise and fall time matching                    | t <sub>r</sub> / t <sub>f</sub>         |            | -     | -   | 109   | %    |

| V <sub>CRS</sub>   | output signal crossover voltage                             |                                         |            | 1.3   | -   | 2.0   | V    |

| t <sub>FEOPT</sub> | source SE0 interval of EOP                                  | see Figure 31                           |            | 160   | -   | 175   | ns   |

| t <sub>FDEOP</sub> | source jitter for differential transition to SE0 transition | see Figure 31                           |            | -2    | -   | +5    | ns   |

| t <sub>JR1</sub>   | receiver jitter to next transition                          |                                         |            | -18.5 | -   | +18.5 | ns   |

| t <sub>JR2</sub>   | receiver jitter for paired transitions                      | 10 % to 90 %                            |            | -9    | -   | +9    | ns   |

| t <sub>EOPR1</sub> | EOP width at receiver                                       | must reject as<br>EOP; see<br>Figure 31 | [1]        | 40    | -   | -     | ns   |

| t <sub>EOPR2</sub> | EOP width at receiver                                       | must accept as<br>EOP; see<br>Figure 31 | <u>[1]</u> | 82    | -   | -     | ns   |

[1] Characterized but not implemented as production test. Guaranteed by design.

32-bit ARM Cortex-M3 microcontroller

# **11. Application information**

## 11.2 XTAL input

The input voltage to the on-chip oscillators is limited to 1.8 V. If the oscillator is driven by a clock in slave mode, it is recommended that the input be coupled through a capacitor with  $C_i = 100 \text{ pF}$ . To limit the input voltage to the specified range, choose an additional capacitor to ground  $C_g$  which attenuates the input voltage by a factor  $C_i/(C_i + C_g)$ . In slave mode, a minimum of 200 mV(RMS) is needed.

### 32-bit ARM Cortex-M3 microcontroller

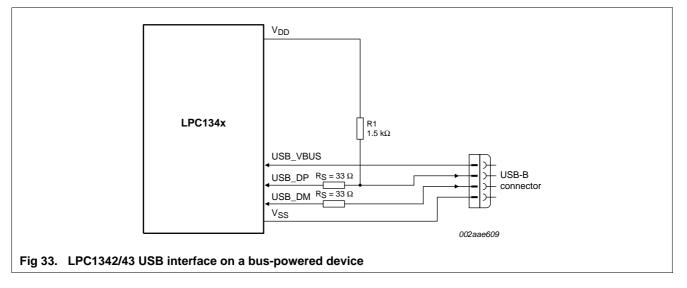

## 11.4 Standard I/O pad configuration

Figure 36 shows the possible pin modes for standard I/O pins with analog input function:

- Digital output driver

- Digital input: Pull-up enabled/disabled

- Digital input: Pull-down enabled/disabled

- Digital input: Repeater mode enabled/disabled

- Analog input

32-bit ARM Cortex-M3 microcontroller

# 14. Abbreviations

| Table 24. | Abbreviations                               |

|-----------|---------------------------------------------|

| Acronym   | Description                                 |

| A/D       | Analog-to-Digital                           |

| ADC       | Analog-to-Digital Converter                 |

| AHB       | Advanced High-performance Bus               |

| AMBA      | Advanced Microcontroller Bus Architecture   |

| APB       | Advanced Peripheral Bus                     |

| BOD       | BrownOut Detection                          |

| EOP       | End Of Packet                               |

| ETM       | Embedded Trace Macrocell                    |

| FIFO      | First-In, First-Out                         |

| GPIO      | General Purpose Input/Output                |

| HID       | Human Interface Device                      |

| I/O       | Input/Output                                |

| LSB       | Least Significant Bit                       |

| MSC       | Mass Storage Class                          |

| PHY       | Physical Layer                              |

| PLL       | Phase-Locked Loop                           |

| SE0       | Single Ended Zero                           |

| SPI       | Serial Peripheral Interface                 |

| SSI       | Serial Synchronous Interface                |

| SSP       | Synchronous Serial Port                     |

| SoF       | Start-of-Frame                              |

| ТСМ       | Tightly-Coupled Memory                      |

| TTL       | Transistor-Transistor Logic                 |

| UART      | Universal Asynchronous Receiver/Transmitter |

| USB       | Universal Serial Bus                        |

|           |                                             |

LPC1311\_13\_42\_43

### 32-bit ARM Cortex-M3 microcontroller

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Non-automotive qualified products** — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b)

# 17. Contact information

whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

# 16.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: salesaddresses@nxp.com