#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 109                                                                     |

| Program Memory Size        | 384KB (384K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 12K x 8                                                                 |

| RAM Size                   | 48K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 40x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 132-UFBGA                                                               |

| Supplier Device Package    | 132-UFBGA (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151qdh6   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

• **Stop** mode without RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, LSE and HSE crystal oscillators are disabled. The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 8  $\mu$ s. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB wakeup.

• **Standby** mode with RTC

Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI RC and HSE crystal oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

• Standby mode without RTC

Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

|                                                           | Functionaliti                     | Functionalities depending on the operating power supply range |                                   |                            |  |  |  |  |  |  |

|-----------------------------------------------------------|-----------------------------------|---------------------------------------------------------------|-----------------------------------|----------------------------|--|--|--|--|--|--|

| Operating power supply range                              | DAC and ADC operation             | USB                                                           | Dynamic voltage<br>scaling range  | I/O operation              |  |  |  |  |  |  |

| V <sub>DD</sub> = V <sub>DDA</sub> = 1.65 to 1.71 V       | Not functional                    | Not functional                                                | Range 2 or<br>Range 3             | Degraded speed performance |  |  |  |  |  |  |

| $V_{DD} = V_{DDA} = 1.71 \text{ to } 1.8 \text{ V}^{(1)}$ | Not functional                    | Not functional                                                | Range 1, Range 2<br>or Range 3    | Degraded speed performance |  |  |  |  |  |  |

| $V_{DD}=V_{DDA}= 1.8 \text{ to } 2.0 \text{ V}^{(1)}$     | Conversion time up<br>to 500 Ksps | Not functional                                                | Range 1, Range 2<br>or<br>Range 3 | Degraded speed performance |  |  |  |  |  |  |

#### Table 3. Functionalities depending on the operating power supply range

|                                   | Functionaliti                     | Functionalities depending on the operating power supply range |                                  |                      |  |  |  |  |  |  |

|-----------------------------------|-----------------------------------|---------------------------------------------------------------|----------------------------------|----------------------|--|--|--|--|--|--|

| Operating power supply range      | DAC and ADC operation             | USB                                                           | Dynamic voltage<br>scaling range | I/O operation        |  |  |  |  |  |  |

| $V_{DD} = V_{DDA} = 2.0$ to 2.4 V | Conversion time up<br>to 500 Ksps | Functional <sup>(2)</sup>                                     | Range 1, Range 2<br>or Range 3   | Full speed operation |  |  |  |  |  |  |

| $V_{DD} = V_{DDA} = 2.4$ to 3.6 V | Conversion time up<br>to 1 Msps   | Functional <sup>(2)</sup>                                     | Range 1, Range 2<br>or Range 3   | Full speed operation |  |  |  |  |  |  |

#### Table 3. Functionalities depending on the operating power supply range (continued)

CPU frequency changes from initial to final must respect "F<sub>CPU</sub> initial < 4\*F<sub>CPU</sub> final" to limit V<sub>CORE</sub> drop due to current consumption peak when frequency increases. It must also respect 5 μs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, the user can switch from 4.2 MHz to 16 MHz, wait 5 μs, then switch from 16 MHz to 32 MHz.

2. Should be USB compliant from I/O voltage standpoint, the minimum  $\rm V_{DD}$  is 3.0 V.

#### Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                                | Dynamic voltage scaling range |

|----------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws)   | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)     | Range 2                       |

| 2.1MHz to 4.2 MHz (1ws)<br>32 kHz to 2.1 MHz (0ws) | Range 3                       |

The operational amplifiers feature:

- Low input bias current

- Low offset voltage

- Low-power mode

- Rail-to-rail input

# 3.14 Ultra-low-power comparators and reference voltage

The STM32L151xD and STM32L152xD devices embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with fixed threshold

- One comparator with rail-to-rail inputs, fast or slow mode. The threshold can be one of the following:

- DAC output

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or a sub-multiple (1/4, 1/2, 3/4)

Both comparators can wake up from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1  $\mu$ A typical).

# 3.15 System configuration controller and routing interface

The system configuration controller provides the capability to remap some alternate functions on different I/O ports.

The highly flexible routing interface allows the application firmware to control the routing of different I/Os to the TIM2, TIM3 and TIM4 timer input captures. It also controls the routing of internal analog signals to ADC1, COMP1 and COMP2 and the internal reference voltage  $V_{\text{REFINT}}$ .

# 3.16 Touch sensing

The STM32L151xD and STM32L152xD devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 34 capacitive sensing channels distributed over 11 analog I/O groups. Both software and timer capacitive sensing acquisition modes are supported.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. The capacitive sensing acquisition only requires few external components to

### 3.18.2 Universal synchronous/asynchronous receiver transmitter (USART)

The three USART and two UART interfaces are able to communicate at speeds of up to 4 Mbit/s. They support IrDA SIR ENDEC and have LIN Master/Slave capability. The three USARTs provide hardware management of the CTS and RTS signals and are ISO 7816 compliant.

All USART/UART interfaces can be served by the DMA controller.

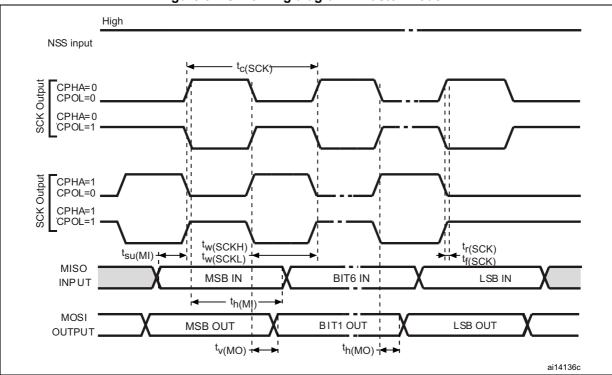

## 3.18.3 Serial peripheral interface (SPI)

Up to three SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The SPIs can be served by the DMA controller.

# 3.18.4 Inter-integrated sound (I<sup>2</sup>S)

Two standard I2S interfaces (multiplexed with SPI2 and SPI3) are available. They can operate in master or slave mode, and can be configured to operate with a 16-/32-bit resolution as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I2S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

The I2Ss can be served by the DMA controller.

#### 3.18.5 SDIO

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 24 MHz in 8-bit mode, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

# 3.18.6 Universal serial bus (USB)

The STM32L151xD and STM32L152xD devices embed a USB device peripheral compatible with the USB full-speed 12 Mbit/s. The USB interface implements a full-speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and supports suspend/resume. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator).

# 3.20 Development support

# 3.20.1 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG JTMS and JTCK pins are shared with SWDAT and SWCLK, respectively, and a specific sequence on the JTMS pin is used to switch between JTAG-DP and SW-DP.

The JTAG port can be permanently disabled with a JTAG fuse.

# 3.20.2 Embedded Trace Macrocell™

The ARM<sup>®</sup> Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32L151xD and STM32L152xD device through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

#### **Pin descriptions**

|   | 1                     | 2             | 3      | 4      | 5     | 6      | 7     | 8     | 9     | 10    | 11     | 12               |        |

|---|-----------------------|---------------|--------|--------|-------|--------|-------|-------|-------|-------|--------|------------------|--------|

| А | (PE3)                 | (PE1)         | (PB8)  | £0070  | (PD7) | PD5    | (PB4) | (PB3) | PA15  | PA14  | PA13   | PA12             |        |

| В | (PE4)                 | (PE2)         | (PB9)  | (PB7)  | (PB6) | (PD6)  | PD4   | (PD3) | (PD1) | PC12  | PC10   | (PA11)           |        |

| С | PC13<br>WKUP2         | PE5           | (PEO)  | (VDD)3 | (PB5) | G14    | G13   | PD2   | (PD0) | PC1)  | (PH2)  | PA10             |        |

| D | PCTA-<br>OSC32        | PE6<br>WKUP3  | (VSS)3 | (PF2)  | (PF1) | (PF0)  | G12   | G10   | PG9   | (PA9) | (PA8)  | PC9              |        |

| E | PC15-<br>OSC32<br>OUT | (LCD          | (VSS)6 | (PF3)  |       |        |       |       | PG5   | PC8   | PC7    | PC6              |        |

| F | PHO<br>OSC IN         | (VSS)5        | (PF4)  | (PF5)  |       | (SS)   | VSS_0 |       | PG3   | (PG4) | vss_2  | (SS_)            |        |

| G |                       | VDD_5         | (PF6)  | (PF7)  |       | VDD_9  |       |       | (PG1) | PG2   |        |                  |        |

| н | PC0                   | NRST          | (VDD_6 | (PF8)  |       |        |       |       | (PG0) | D15   | PD14   | PD13             |        |

| J | (SSA)                 | (PC1)         | PC2    | (PA4)  | (PA7) | (PF9)  | PF12  | PF14  | PF15  | PD12  | PD11   | PD10             |        |

| к |                       | PC3           | (PA2)  | (PA5)  | PC4   | (PF11) | PF13  | (PD9) | (PD8) | PB15  | PB14   | PB13             |        |

| L | (REF)+                | PAO-<br>WKUP1 | (PA3)  | (PA6)  | PC5   | (PB2)  | PE8   | PE10  | PE12  | PB10  | (PB11) | PB12             |        |

| м | (DDA                  | (PA1)         |        |        | РВО   | (PB1)  | (PE7) | (PE9) | PE11  | PE13  | (PE1)  | E15              |        |

|   |                       |               |        |        |       |        |       |       |       |       |        | MS3 <sup>-</sup> | 1072V1 |

### Figure 4. STM32L15xQD UFBGA132 ballout

1. This figure shows the package top view.

|         | F        | Pins    |        |         |                   |                         |                 |                                                  | Pin function                                  | ;                                                  |

|---------|----------|---------|--------|---------|-------------------|-------------------------|-----------------|--------------------------------------------------|-----------------------------------------------|----------------------------------------------------|

| LQFP144 | UFBGA132 | LQFP100 | LQFP64 | WLCSP64 | Pin name          | Pin Type <sup>(1)</sup> | I / O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                           | Additional<br>functions                            |

| -       | J5       | -       | -      | -       | PA7               | I/O                     | FT              | PA7                                              | TIM3_CH2/TIM11_CH1/<br>SPI1_MOSI/<br>LCD_SEG4 | ADC_IN7/<br>COMP1_INP                              |

| -       | M4       | -       | -      | -       | OPAMP2_VI<br>NM   | I                       | тс              | OPAMP2_V<br>INM                                  | -                                             | -                                                  |

| 44      | K5       | 33      | 24     | H6      | PC4               | I/O                     | FT              | PC4                                              | LCD_SEG22                                     | ADC_IN14/<br>COMP1_INP                             |

| 45      | L5       | 34      | 25     | H5      | PC5               | I/O                     | FT              | PC5                                              | LCD_SEG23                                     | ADC_IN15/<br>COMP1_INP                             |

| 46      | M5       | 35      | 26     | H4      | PB0               | I/O                     | тс              | PB0                                              | TIM3_CH3/LCD_SEG5                             | ADC_IN8/<br>COMP1_INP/<br>OPAMP2_VOUT/<br>VREF_OUT |

| 47      | M6       | 36      | 27     | F4      | PB1               | I/O                     | FT              | PB1                                              | TIM3_CH4/LCD_SEG6                             | ADC_IN9/<br>COMP1_INP/<br>VREF_OUT                 |

| 48      | L6       | 37      | 28     | H3      | PB2               | I/O                     | FT              | PB2/<br>BOOT1                                    | BOOT1                                         | ADC_IN0b                                           |

| 49      | K6       | -       | -      | -       | PF11              | I/O                     | FT              | PF11                                             | -                                             | ADC_IN1b                                           |

| 50      | J7       | -       | -      | -       | PF12              | I/O                     | FT              | PF12                                             | FSMC_A6                                       | ADC_IN2b                                           |

| 51      | E3       | -       | -      | -       | V <sub>SS_6</sub> | S                       | -               | V <sub>SS_6</sub>                                | -                                             | -                                                  |

| 52      | H3       | -       | -      | -       | $V_{DD_6}$        | S                       | -               | $V_{DD_6}$                                       | -                                             | -                                                  |

| 53      | K7       | -       | 1      | -       | PF13              | I/O                     | FT              | PF13                                             | FSMC_A7                                       | ADC_IN3b                                           |

| 54      | J8       | -       | -      | -       | PF14              | I/O                     | FT              | PF14                                             | FSMC_A8                                       | ADC_IN6b                                           |

| 55      | J9       | -       | I      | -       | PF15              | I/O                     | FT              | PF15                                             | FSMC_A9                                       | ADC_IN7b                                           |

| 56      | H9       | -       | -      | -       | PG0               | I/O                     | FT              | PG0                                              | FSMC_A10                                      | ADC_IN8b                                           |

| 57      | G9       | -       | -      | -       | PG1               | I/O                     | FT              | PG1                                              | FSMC_A11                                      | ADC_IN9b                                           |

| 58      | M7       | 38      | -      | -       | PE7               | I/O                     | тс              | PE7                                              | FSMC_D4                                       | ADC_IN22/<br>COMP1_INP                             |

| 59      | L7       | 39      | -      | -       | PE8               | I/O                     | тс              | PE8                                              | FSMC_D5                                       | ADC_IN23/<br>COMP1_INP                             |

| 60      | M8       | 40      | -      | -       | PE9               | I/O                     | тс              | PE9                                              | TIM2_CH1_ETR /FSMC_D6                         | ADC_IN24/<br>COMP1_INP                             |

# Table 8. STM32L151xD and STM32L152xD pin definitions (continued)

|           |         |       |          |                | [      | Digital alte | ernate fu | nction numbe | ər      |        |               |          |              |

|-----------|---------|-------|----------|----------------|--------|--------------|-----------|--------------|---------|--------|---------------|----------|--------------|

|           | AFIO0   | AFIO1 | AFIO2    | AFIO3          | AFIO4  | AFIO5        | AFIO6     | AFIO7        | AFIO8   | AFIO11 | AFIO12.       | . AFIO14 | AFIO15       |

| Port name |         |       | •        |                |        | Alt          | ernate fu | unction      |         | •      |               |          |              |

|           | SYSTEM  | TIM2  | TIM3/4/5 | TIM9/<br>10/11 | I2C1/2 | SPI1/2       | SPI3      | USART1/2/3   | UART4/5 | LCD    | FSMC/<br>SDIO | CPRI     | SYSTEM       |

| PD8       | -       | -     | -        | -              | -      | -            | -         | USART3_TX    | -       | SEG28  | D13/DA13      | TIMx_IC1 | EVENT<br>OUT |

| PD9       | -       | -     | -        | -              | -      | -            | -         | USART3_RX    | -       | SEG29  | D14/DA14      | TIMx_IC2 | EVENT<br>OUT |

| PD10      | -       | -     | -        | -              | -      | -            | -         | USART3_CK    | -       | SEG30  | D15/DA15      | TIMx_IC3 | EVENT<br>OUT |

| PD11      | -       | -     | -        | -              | -      | -            | -         | USART3_CTS   | -       | SEG31  | A16           | TIMx_IC4 | EVENT<br>OUT |

| PD12      | -       | -     | TIM4_CH1 | -              | -      | -            | -         | USART3_RTS   | -       | SEG32  | A17           | TIMx_IC1 | EVENT<br>OUT |

| PD13      | -       | -     | TIM4_CH2 | -              | -      | -            | -         | -            | -       | SEG33  | A18           | TIMx_IC2 | EVENT<br>OUT |

| PD14      | -       | -     | TIM4_CH3 | -              | -      | -            | -         | -            | -       | SEG34  | D0/DA0        | TIMx_IC3 | EVENT<br>OUT |

| PD15      | -       | -     | TIM4_CH4 | -              | -      | -            | -         | -            | -       | SEG35  | D1/DA1        | TIMx_IC4 | EVENT<br>OUT |

| PE0       | -       | -     | TIM4_ETR | TIM10_CH1      | -      | -            | -         | -            | -       | SEG36  | NBL0          | TIMx_IC1 | EVENT<br>OUT |

| PE1       | -       | -     | -        | TIM11_CH1      | -      | -            | -         | -            | -       | SEG37  | NBL1          | TIMx_IC2 | EVENT<br>OUT |

| PE2       | TRACECK | -     | TIM3_ETR | -              | -      | -            | -         | -            | -       | SEG 38 | A23           | TIMx_IC3 | EVENT<br>OUT |

| PE3       | TRACED0 | -     | TIM3_CH1 | -              | -      | -            | -         | -            | -       | SEG 39 | A19           | TIMx_IC4 | EVENT<br>OUT |

| PE4       | TRACED1 | -     | TIM3_CH2 | -              | -      | -            | -         | -            | -       | -      | A20           | TIMx_IC1 | EVENT<br>OUT |

| PE5       | TRACED2 | -     | -        | TIM9_CH1       | -      | -            | -         | -            | -       | -      | A21           | TIMx_IC2 | EVENT<br>OUT |

| PE6-WKUP3 | TRACED3 | -     | -        | TIM9_CH2       | -      | -            | -         | -            | -       | -      | -             | TIMx_IC3 | EVENT<br>OUT |

53/154

STM32L151xD STM32L152xD

Pin descriptions

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 10: Voltage characteristics*, *Table 11: Current characteristics*, and *Table 12: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                              | Ratings                                                                         | Min                  | Мах                  | Unit |

|-------------------------------------|---------------------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>    | External main supply voltage (including $V_{DDA}$ and $V_{DD}$ ) <sup>(1)</sup> | -0.3                 | 4.0                  |      |

| V <sub>IN</sub> <sup>(2)</sup>      | Input voltage on five-volt tolerant pin                                         | V <sub>SS</sub> –0.3 | V <sub>DD</sub> +4.0 | V    |

| VIN                                 | Input voltage on any other pin                                                  | V <sub>SS</sub> –0.3 | 4.0                  |      |

| ΔV <sub>DDx</sub>                   | Variations between different V <sub>DD</sub> power pins                         | -                    | 50                   | mV   |

| V <sub>SSX</sub> –V <sub>SS</sub>   | Variations between all different ground pins <sup>(3)</sup>                     | -                    | 50                   |      |

| V <sub>REF+</sub> –V <sub>DDA</sub> | Allowed voltage difference for $V_{REF+} > V_{DDA}$                             | -                    | 0.4                  | V    |

| V <sub>ESD(HBM)</sub>               | Electrostatic discharge voltage<br>(human body model)                           | see Secti            | ion 6.3.12           |      |

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 11* for maximum allowed injected current values.

3. Include  $V_{REF-}$  pin.

#### Table 11. Current characteristics

| Symbol                               | Ratings                                                                                        | Max.  | Unit |  |  |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------------|-------|------|--|--|--|--|

| $I_{VDD(\Sigma)}$                    | $I_{VDD(\Sigma)}$ Total current into sum of all $V_{DD_x}$ power lines (source) <sup>(1)</sup> |       |      |  |  |  |  |

| $I_{VSS(\Sigma)}^{(2)}$              | Total current out of sum of all $V_{SS_x}$ ground lines (sink) <sup>(1)</sup>                  | 100   |      |  |  |  |  |

| I <sub>VDD(PIN)</sub>                | Maximum current into each V <sub>DD_x</sub> power pin (source) <sup>(1)</sup>                  | 70    |      |  |  |  |  |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each VSS_x ground pin (sink) <sup>(1)</sup>                             | -70   |      |  |  |  |  |

|                                      | Output current sunk by any I/O and control pin                                                 | 25    |      |  |  |  |  |

| I <sub>IO</sub>                      | Output current sourced by any I/O and control pin                                              | - 25  | mA   |  |  |  |  |

| 51                                   | Total output current sunk by sum of all IOs and control pins <sup>(2)</sup>                    | 60    |      |  |  |  |  |

| ΣΙ <sub>ΙΟ(ΡΙΝ)</sub>                | Total output current sourced by sum of all IOs and control pins <sup>(2)</sup>                 | -60   |      |  |  |  |  |

| (3)                                  | Injected current on five-volt tolerant I/O <sup>(4)</sup> , RST and B pins                     | -5/+0 |      |  |  |  |  |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on any other pin <sup>(5)</sup>                                               | ± 5   |      |  |  |  |  |

| ΣΙ <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>                        | ± 25  |      |  |  |  |  |

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

3. Negative injection disturbs the analog performance of the device. See note in Section 6.3.19.

| Symbol               | Parameter                                                 | Conditions                                                              |                                                    | f <sub>HCLK</sub><br>[MHz] | Тур  | Max<br>(1) | Unit |

|----------------------|-----------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------|----------------------------|------|------------|------|

|                      |                                                           |                                                                         | Range3,                                            | 1                          | 290  | 500        |      |

|                      |                                                           |                                                                         | V <sub>CORE</sub> =1.2 V                           | 2                          | 505  | 750        | μA   |

|                      |                                                           |                                                                         | VOS[1:0]=11                                        | 4                          | 955  | 1200       |      |

|                      |                                                           | f <sub>HSE</sub> = f <sub>HCLK</sub> up to 16MHz,                       | Range2,                                            | 4                          | 1.15 | 1.6        |      |

|                      |                                                           | included $f_{HSE} = f_{HCLK}/2$ above<br>16 MHz (PLL ON) <sup>(2)</sup> |                                                    | 8                          | 2.3  | 2.9        | mA   |

|                      | Supply current in<br>Run mode code<br>executed from Flash | 16 MHz (PLL ON) <sup>(2)</sup>                                          | VOS[1:0]=10                                        | 16                         | 4.25 | 5.2        |      |

|                      |                                                           |                                                                         | Range1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0]=01 | 8                          | 2.65 | 3.5        |      |

| I <sub>DD (Run</sub> |                                                           |                                                                         |                                                    | 16                         | 5.35 | 6.5        |      |

| from                 |                                                           |                                                                         |                                                    | 32                         | 10.5 | 12         |      |

| Flash)               |                                                           |                                                                         | Range2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0]=10 | 16                         | 4.35 | 5.2        |      |

|                      |                                                           | HSI clock source (16 MHz)                                               | Range1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0]=01 | 32                         | 10.5 | 12.3       |      |

|                      |                                                           | MSI clock, 65 kHZ                                                       | Range3,                                            | 0.065                      | 46   | 130        |      |

|                      |                                                           | MSI clock, 524 kHZ                                                      | V <sub>CORE</sub> =1.2 V                           | 0.524                      | 160  | 250        | μA   |

|                      |                                                           | MSI clock, 4.2 MHZ                                                      | VOS[1:0]=11                                        | 4.2                        | 965  | 1200       |      |

#### Table 17. Current consumption in Run mode, code with data processing running from Flash

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol                            | Parameter         | Conditions                                                          |                                                    | f <sub>HCLK</sub> | Тур   | Max  | Unit |

|-----------------------------------|-------------------|---------------------------------------------------------------------|----------------------------------------------------|-------------------|-------|------|------|

|                                   |                   |                                                                     | Range3,                                            | 1                 | 230   | 470  |      |

|                                   |                   |                                                                     | V <sub>CORE</sub> =1.2 V                           | 2                 | 415   | 780  | μA   |

|                                   |                   |                                                                     | VOS[1:0]=11                                        | 4                 | 800   | 1200 |      |

|                                   |                   | f <sub>HSE</sub> = f <sub>HCLK</sub> up to 16 MHz,                  | Range2,                                            | 4                 | 0.935 | 1.5  |      |

|                                   |                   | included $f_{HSE} = f_{HCLK}/2$ above 16MHz (PLL ON) <sup>(1)</sup> | V <sub>CORE</sub> =1.5 V                           | 8                 | 1.9   | 3    | mA   |

|                                   | ave aute of frame | 16MHz (PLL ON) <sup>(1)</sup>                                       | VOS[1:0]=10                                        | 16                | 3.75  | 5    |      |

|                                   |                   |                                                                     | Range1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0]=01 | 8                 | 2.25  | 3.5  |      |

|                                   |                   |                                                                     |                                                    | 16                | 4.45  | 5.55 |      |

| I <sub>DD (Run</sub><br>from RAM) |                   |                                                                     |                                                    | 32                | 9.05  | 10.9 |      |

| ,                                 |                   |                                                                     | Range2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0]=10 | 16                | 3.75  | 4.8  |      |

|                                   |                   | HSI clock source (16 MHz)                                           | Range1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0]=01 | 32                | 8.95  | 11.7 |      |

|                                   |                   | MSI clock, 65 kHZ                                                   | Range3,                                            | 0.065             | 43.5  | 100  |      |

|                                   |                   | MSI clock, 524 kHZ                                                  | V <sub>CORE</sub> =1.2 V                           | 0.524             | 135   | 215  | μA   |

|                                   |                   | MSI clock, 4.2 MHZ                                                  | VOS[1:0]=11                                        | 4.2               | 835   | 1100 |      |

# Table 18. Current consumption in Run mode, code with data processing running from RAM

1. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Typical consumption, V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C |                    |                                                              |                                                              |                                                              |                               |                      |

|----------------------------------------------------------------------|--------------------|--------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-------------------------------|----------------------|

| Peripheral                                                           |                    | Range 1,<br>V <sub>CORE</sub> =<br>1.8 V<br>VOS[1:0] =<br>01 | Range 2,<br>V <sub>CORE</sub> =<br>1.5 V<br>VOS[1:0] =<br>10 | Range 3,<br>V <sub>CORE</sub> =<br>1.2 V<br>VOS[1:0] =<br>11 | Low-power<br>sleep and<br>run | Unit                 |

|                                                                      | SYSCFG &<br>RI     | 3.5                                                          | 2.9                                                          | 2.4                                                          | 2.9                           |                      |

|                                                                      | TIM9               | 9.0                                                          | 7.4                                                          | 5.8                                                          | 7.4                           |                      |

|                                                                      | TIM10              | 7.1                                                          | 5.8                                                          | 4.6                                                          | 5.8                           |                      |

| APB2                                                                 | TIM11              | 6.5                                                          | 5.3                                                          | 4.3                                                          | 5.3                           |                      |

|                                                                      | ADC <sup>(2)</sup> | 11.0                                                         | 9.1                                                          | 7.2                                                          | 9.1                           |                      |

|                                                                      | SDIO               | 28.4                                                         | 24.2                                                         | 19.1                                                         | 24.2                          |                      |

|                                                                      | SPI1               | 5.1                                                          | 4.2                                                          | 3.3                                                          | 4.2                           |                      |

|                                                                      | USART1             | 9.4                                                          | 7.8                                                          | 6.1                                                          | 7.8                           |                      |

|                                                                      | GPIOA              | 7.3                                                          | 6.1                                                          | 4.8                                                          | 6.1                           |                      |

|                                                                      | GPIOB              | 7.5                                                          | 6.1                                                          | 4.8                                                          | 6.1                           |                      |

|                                                                      | GPIOC              | 8.2                                                          | 6.8                                                          | 5.3                                                          | 6.8                           | µA/MHz<br>(fusuu)    |

|                                                                      | GPIOD              | 8.7                                                          | 7.1                                                          | 5.7                                                          | 7.1                           | (f <sub>HCLK</sub> ) |

|                                                                      | GPIOE              | 7.6                                                          | 6.2                                                          | 4.9                                                          | 6.2                           |                      |

|                                                                      | GPIOF              | 7.7                                                          | 6.3                                                          | 5.0                                                          | 6.3                           |                      |

| AHB                                                                  | GPIOG              | 8.4                                                          | 7.0                                                          | 5.4                                                          | 7.0                           |                      |

|                                                                      | GPIOH              | 1.8                                                          | 1.3                                                          | 1.1                                                          | 1.3                           |                      |

|                                                                      | CRC                | 0.8                                                          | 0.6                                                          | 0.4                                                          | 0.6                           |                      |

|                                                                      | FLASH              | 26.3                                                         | 19.3                                                         | 18.3                                                         | _(3)                          |                      |

|                                                                      | DMA1               | 19.0                                                         | 16.0                                                         | 12.8                                                         | 16.0                          |                      |

|                                                                      | DMA2               | 17.0                                                         | 14.5                                                         | 11.5                                                         | 14.5                          |                      |

|                                                                      | FSMC               | 16.0                                                         | 13.4                                                         | 10.6                                                         | 13.4                          |                      |

| All enabled                                                          |                    | 310                                                          | 246                                                          | 217                                                          | 226.7                         |                      |

Table 24. Peripheral current consumption<sup>(1)</sup> (continued)

| Symbol                              | Parameter                                                                                                 | Conditions                                                  | Min | Тур | Мах                                | Unit  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|------------------------------------|-------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency                                                                                      | -                                                           | 1   |     | 24                                 | MHz   |

| R <sub>F</sub>                      | Feedback resistor                                                                                         | -                                                           | -   | 200 | -                                  | kΩ    |

| С                                   | Recommended load<br>capacitance versus<br>equivalent serial<br>resistance of the crystal<br>$(R_S)^{(3)}$ | R <sub>S</sub> = 30 Ω                                       | -   | 20  | -                                  | pF    |

| I <sub>HSE</sub>                    | HSE driving current                                                                                       | $V_{DD}$ = 3.3 V,<br>$V_{IN}$ = $V_{SS}$ with 30 pF<br>load | -   | -   | 3                                  | mA    |

| I                                   | HSE oscillator power                                                                                      | C = 20 pF<br>f <sub>OSC</sub> = 16 MHz                      | -   | -   | 2.5 (startup)<br>0.7 (stabilized)  | mA    |

| I <sub>DD(HSE)</sub>                | consumption                                                                                               | C = 10 pF<br>f <sub>OSC</sub> = 16 MHz                      | -   | -   | 2.5 (startup)<br>0.46 (stabilized) |       |

| 9 <sub>m</sub>                      | Oscillator<br>transconductance                                                                            | Startup                                                     | 3.5 | -   | -                                  | mA /V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                                                                              | V <sub>DD</sub> is stabilized                               | -   | 1   | -                                  | ms    |

Table 28. HSE oscillator characteristics<sup>(1)(2)</sup>

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by characterization results.

The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 16*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

| Symbol                       | Parameter                                  | Min                   | Max | Unit |

|------------------------------|--------------------------------------------|-----------------------|-----|------|

| t <sub>w(CLK)</sub>          | FSMC_CLK period                            | 2*T <sub>HCLK</sub>   | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>    | FSMC_CLK low to FSMC_NEx low (x = 02)      | -                     | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>    | FSMC_CLK low to FSMC_NEx high (x = 02)     | 0                     | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>   | FSMC_CLK low to FSMC_NADV low              | -                     | 0   | ns   |

| t <sub>d(CLKL-NADVH)</sub>   | FSMC_CLK low to FSMC_NADV high             | 0                     | -   | ns   |

| t <sub>d(CLKL-AV)</sub>      | FSMC_CLK low to FSMC_Ax valid (x = 1625)   | -                     | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>     | FSMC_CLK low to FSMC_Ax invalid (x = 1625) | T <sub>HCLK</sub> + 4 | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>    | FSMC_CLK low to FSMC_NWE low               | -                     | 0   | ns   |

| t <sub>d(CLKL-NWEH)</sub>    | FSMC_CLK low to FSMC_NWE high              | 1                     | -   | ns   |

| t <sub>d(CLKL-ADIV)</sub>    | FSMC_CLK low to FSMC_AD[15:0] invalid      | 5                     | -   | ns   |

| t <sub>d(CLKL-DATA)</sub>    | FSMC_A/D[15:0] valid after FSMC_CLK low    | -                     | 6   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high      | 6                     | -   | ns   |

| t <sub>h(CLKH-NWAITV)</sub>  | FSMC_NWAIT valid after FSMC_CLK high       | 0                     | -   | ns   |

| t <sub>d(CLKL-NBLH)</sub>    | FSMC_CLK low to FSMC_NBL high              | 1                     | -   | ns   |

Table 42. Synchronous multiplexed PSRAM write timings<sup>(1)</sup>

1. C<sub>L</sub> = 30 pF.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

|                             |                                    |                          |                                                        | Max vs. |                              |                              |      |

|-----------------------------|------------------------------------|--------------------------|--------------------------------------------------------|---------|------------------------------|------------------------------|------|

| Symbol                      | Parameter                          | Conditions               | tions Monitored 4 MH<br>frequency band voltag<br>range |         | 16 MHz<br>voltage<br>range 2 | 32 MHz<br>voltage<br>range 1 | Unit |

|                             |                                    | V <sub>DD</sub> = 3.3 V, | 0.1 to 30 MHz                                          | 3       | -6                           | -5                           |      |

| 6                           | Peak level                         |                          | 30 to 130 MHz                                          | 18      | 4                            | -7                           | dBµV |

| S <sub>EMI</sub> Peak level | LQFP100 package compliant with IEC | 130 MHz to 1GHz          | 15                                                     | 5       | -7                           |                              |      |

|                             |                                    | 61967-2                  | SAE EMI Level                                          | 2.5     | 2                            | 1                            | -    |

Table 46. EMI characteristics

# 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol                | Ratings                                                     | Conditions                                            | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------------|-------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic<br>discharge voltage<br>(human body model)    | $T_A = +25 \text{ °C}$ , conforming<br>to JESD22-A114 | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic<br>discharge voltage<br>(charge device model) | $T_A = +25 \text{ °C}$ , conforming<br>to JESD22-C101 | 111   | 500                             | V    |

Table 47. ESD absolute maximum ratings

1. Guaranteed by characterization results.

Figure 31. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

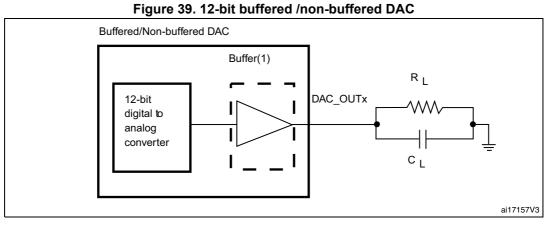

- 4. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

- 5. Difference between the value measured at Code (0x800) and the ideal value =  $V_{REF+}/2$ .

- 6. Difference between the value measured at Code (0x001) and the ideal value.

- 7. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{DDA} 0.2$ ) V when buffer is ON.

- 8. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

# 6.3.21 Operational amplifier characteristics

| Symbol               | Parameter            |                           | Condition <sup>(1)</sup> | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit  |  |

|----------------------|----------------------|---------------------------|--------------------------|--------------------|-----|--------------------|-------|--|

| CMIR                 | Common mode inpu     | ut range                  | -                        | 0                  | -   | V <sub>DD</sub>    |       |  |

|                      | Input offset voltage | Maximum calibration range | -                        | -                  | -   | ±15                | m)/   |  |

| VI <sub>OFFSET</sub> | input onset voltage  | After offset calibration  | -                        | -                  | -   | ±1.5               | mV    |  |

| 43.71                | Input offset voltage | Normal mode               | -                        | -                  | -   | ±40                | µV/°C |  |

| $\Delta VI_{OFFSET}$ | drift                | Low-power mode            | -                        | -                  | -   | ±80                |       |  |

| -                    | Input current bias   | Dedicated input           |                          | -                  | -   | 1                  |       |  |

| I <sub>IB</sub>      |                      | General purpose input     | 75 °C                    | -                  | -   | 10                 | nA    |  |

|                      |                      | Normal mode               | -                        | -                  | -   | 500                |       |  |

| ILOAD                | Drive current        | Low-power mode            | -                        | -                  | -   | 100                | μA    |  |

|                      | Orana                | Normal mode               | No load,                 | -                  | 100 | 220                |       |  |

| I <sub>DD</sub>      | Consumption          | Low-power mode            | quiescent mode           | _                  | 30  | 60                 | μA    |  |

|                      | Common mode          | Normal mode               | -                        | -                  | -85 | -                  | dD    |  |

| CMRR                 | rejection ration     | Low-power mode            | -                        | -                  | -90 | -                  | dB    |  |

#### Table 68. Operational amplifier characteristics

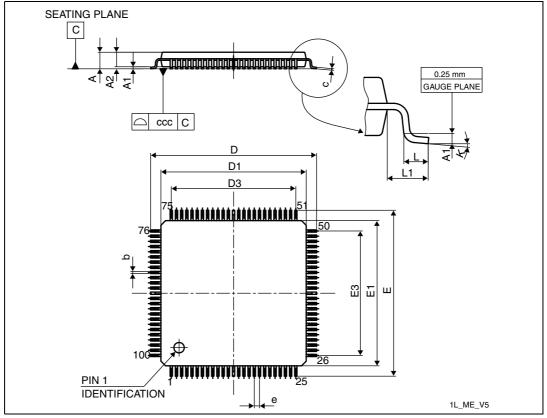

# 7.2 LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package information

Figure 43. LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 75. LQPF100, 14 x 14 mm, | 100-pin low-profile quad flat package mechanical |

|--------------------------------|--------------------------------------------------|

|                                | data                                             |

|        |             |        | uala   |                       |        |        |  |

|--------|-------------|--------|--------|-----------------------|--------|--------|--|

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |

| Symbol | Min         | Тур    | Max    | Min                   | Тур    | Max    |  |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |  |

| D      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| D3     | -           | 12.000 | -      | -                     | 0.4724 | -      |  |

| Е      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

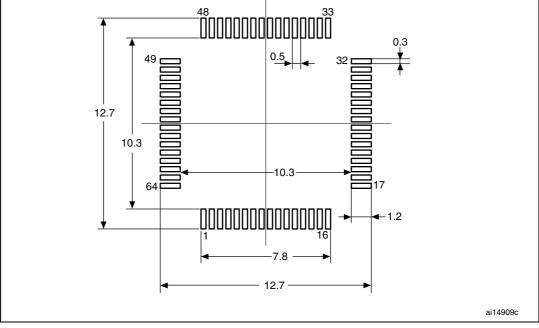

| Table 76. LQFP64, 10 x 10 mm 64-pin low-profile quad flat package mechanical data |

|-----------------------------------------------------------------------------------|

| (continued)                                                                       |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Мах    |

| E3     | -           | 7.500 | -     | -                     | 0.2953 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| К      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

# Table 77. UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid arraypackage mechanical data (continued)

| Symbol |     | millimeters |       | inches <sup>(1)</sup> |     |        |

|--------|-----|-------------|-------|-----------------------|-----|--------|

| Symbol | Min | Тур         | Max   | Min                   | Тур | Max    |

| ddd    | -   | -           | 0.080 | -                     | -   | 0.0031 |

| eee    | -   | -           | 0.150 | -                     | -   | 0.0059 |

| fff    | -   | -           | 0.050 | -                     | -   | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

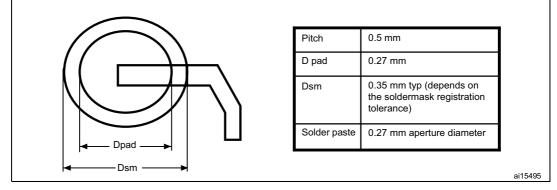

# Figure 50. UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid array package recommended footprint