Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 384KB (384K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 12K x 8                                                                 |

| RAM Size                   | 48K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 21x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151rdt6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 6.3.2                                                                  | Embedded reset and power control block characteristics         | 63    |  |  |  |

|------|------------------------------------------------------------------------|----------------------------------------------------------------|-------|--|--|--|

|      | 6.3.3                                                                  | Embedded internal reference voltage                            | 65    |  |  |  |

|      | 6.3.4                                                                  | Supply current characteristics                                 | 66    |  |  |  |

|      | 6.3.5                                                                  | Wakeup time from low-power mode                                | 77    |  |  |  |

|      | 6.3.6                                                                  | External clock source characteristics                          | 78    |  |  |  |

|      | 6.3.7                                                                  | Internal clock source characteristics                          | 84    |  |  |  |

|      | 6.3.8                                                                  | PLL characteristics                                            | 87    |  |  |  |

|      | 6.3.9                                                                  | Memory characteristics                                         | 87    |  |  |  |

|      | 6.3.10                                                                 | FSMC characteristics                                           | 89    |  |  |  |

|      | 6.3.11                                                                 | EMC characteristics                                            | . 101 |  |  |  |

|      | 6.3.12                                                                 | Electrical sensitivity characteristics                         | . 102 |  |  |  |

|      | 6.3.13                                                                 | I/O current injection characteristics                          | . 103 |  |  |  |

|      | 6.3.14                                                                 | I/O port characteristics                                       | . 104 |  |  |  |

|      | 6.3.15                                                                 | NRST pin characteristics                                       | . 107 |  |  |  |

|      | 6.3.16                                                                 | TIM timer characteristics                                      | . 108 |  |  |  |

|      | 6.3.17                                                                 | Communications interfaces                                      | . 109 |  |  |  |

|      | 6.3.18                                                                 | SDIO characteristics                                           | . 117 |  |  |  |

|      | 6.3.19                                                                 | 12-bit ADC characteristics                                     | . 118 |  |  |  |

|      | 6.3.20                                                                 | DAC electrical specifications                                  | . 123 |  |  |  |

|      | 6.3.21                                                                 | Operational amplifier characteristics                          | . 125 |  |  |  |

|      | 6.3.22                                                                 | Temperature sensor characteristics                             | . 127 |  |  |  |

|      | 6.3.23                                                                 | Comparator                                                     | . 127 |  |  |  |

|      | 6.3.24                                                                 | LCD controller                                                 | . 129 |  |  |  |

| Pack | age info                                                               | ormation                                                       | . 130 |  |  |  |

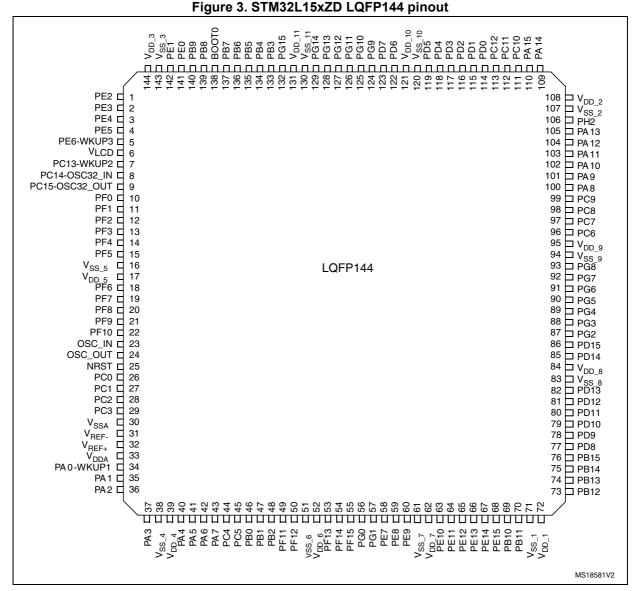

| 7.1  |                                                                        | 44, 20 x 20 mm, 144-pin low-profile quad flat package tion     | . 130 |  |  |  |

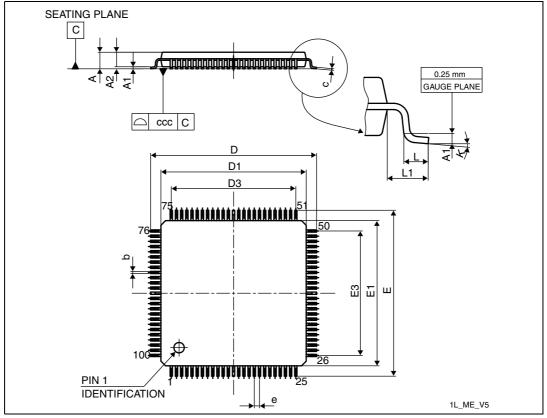

| 7.2  | LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package information |                                                                |       |  |  |  |

| 7.3  |                                                                        | 4, 10 x 10 mm, 64-pin low-profile quad flat package tion       | . 136 |  |  |  |

| 7.4  |                                                                        | 132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid       | . 139 |  |  |  |

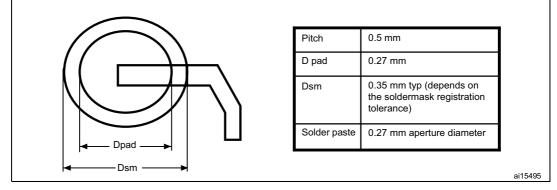

| 7.5  | WLCSF                                                                  | P64, 0.4 mm pitch wafer level chip scale package information . | . 142 |  |  |  |

| 7.6  | Therma                                                                 | Il characteristics                                             | . 145 |  |  |  |

|      | 7.6.1                                                                  | Reference document                                             | . 146 |  |  |  |

|      |                                                                        |                                                                |       |  |  |  |

7

| Figure 46.<br>Figure 47. | LQFP64, 10 x 10 mm, 64-pin low-profile quad flat package outline                      | 36 |

|--------------------------|---------------------------------------------------------------------------------------|----|

|                          | recommended footprint1                                                                | 37 |

| Figure 48.               | LQFP64 10 x 10 mm, 64-pin low-profile quad flat package top view example 1            | 38 |

| Figure 49.               | UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid array package outline 1 | 39 |

| Figure 50.               | UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid array package           |    |

|                          | recommended footprint1                                                                | 40 |

| Figure 51.               | UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid array package           |    |

|                          | top view example                                                                      | 41 |

| Figure 52.               | WLCSP64, 0.4 mm pitch wafer level chip scale package outline                          | 42 |

| Figure 53.               | WLCSP64, 0.4 mm pitch wafer level chip scale package                                  |    |

|                          | recommended footprint1                                                                | 43 |

| Figure 54.               | WLCSP64, 0.4 mm pitch wafer level chip scale package top view example                 | 44 |

| Figure 55.               | Thermal resistance suffix 6                                                           | 46 |

| Figure 56.               | Thermal resistance suffix 7   1                                                       | 46 |

#### 2.2.3 Common system strategy.

To offer flexibility and optimize performance, the STM8L15xxx, STM32L15xxx and STM32L162xx family uses a common architecture:

- Same power supply range from 1.65 V to 3.6 V

- Architecture optimized to reach ultra-low consumption both in low-power modes and Run mode

- Fast startup strategy from low-power modes

- Flexible system clock

- Ultrasafe reset: same reset strategy including power-on reset, power-down reset, brownout reset and programmable voltage detector

#### 2.2.4 Features

ST ultra-low-power continuum also lies in feature compatibility:

- More than 15 packages with pin count from 20 to 144 pins and size down to 3 x 3 mm

- Memory density ranging from 2 to 512 Kbytes

• **Stop** mode without RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, LSE and HSE crystal oscillators are disabled. The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 8  $\mu$ s. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB wakeup.

• **Standby** mode with RTC

Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI RC and HSE crystal oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

• Standby mode without RTC

Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

|                                                           | Functionalities depending on the operating power supply range |                |                                   |                            |  |  |

|-----------------------------------------------------------|---------------------------------------------------------------|----------------|-----------------------------------|----------------------------|--|--|

| Operating power supply range                              | DAC and ADC operation                                         | USB            | Dynamic voltage<br>scaling range  | I/O operation              |  |  |

| V <sub>DD</sub> = V <sub>DDA</sub> = 1.65 to 1.71 V       | Not functional                                                | Not functional | Range 2 or<br>Range 3             | Degraded speed performance |  |  |

| $V_{DD} = V_{DDA} = 1.71 \text{ to } 1.8 \text{ V}^{(1)}$ | Not functional                                                | Not functional | Range 1, Range 2<br>or Range 3    | Degraded speed performance |  |  |

| $V_{DD}=V_{DDA}= 1.8 \text{ to } 2.0 \text{ V}^{(1)}$     | Conversion time up<br>to 500 Ksps                             | Not functional | Range 1, Range 2<br>or<br>Range 3 | Degraded speed performance |  |  |

#### Table 3. Functionalities depending on the operating power supply range

### 3.5 Low-power real-time clock and backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Dedicated registers contain the sub-second, second, minute, hour (12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day of the month are made automatically. The RTC provides two programmable alarms and programmable periodic interrupts with wakeup from Stop and Standby modes.

The programmable wakeup time ranges from 120 µs to 36 hours.

The RTC can be calibrated with an external 512 Hz output, and a digital compensation circuit helps reduce drift due to crystal deviation.

The RTC can also be automatically corrected with a 50/60Hz stable powerline.

The RTC calendar can be updated on the fly down to sub second precision, which enables network system synchronization.

A time stamp can record an external event occurrence, and generates an interrupt.

There are thirty-two 32-bit backup registers provided to store 128 bytes of user application data. They are cleared in case of tamper detection.

Three pins can be used to detect tamper events. A change on one of these pins can reset backup register and generate an interrupt. To prevent false tamper event, like ESD event, these three tamper inputs can be digitally filtered.

## **3.6 GPIOs (general-purpose inputs/outputs)**

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions, and can be individually remapped using dedicated AFIO registers. All GPIOs are high current capable. The alternate function configuration of I/Os can be locked if needed following a specific sequence in order to avoid spurious writing to the I/O registers. The I/O controller is connected to the AHB with a toggling speed of up to 16 MHz.

#### External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 24 edge detector lines used to generate interrupt/event requests. Each line can be individually configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 115 GPIOs can be connected to the 16 external interrupt lines. The 8 other lines are connected to RTC, PVD, USB, comparator events or capacitive sensing acquisition.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, SDIO, general-purpose timers, DAC and ADC.

## 3.10 LCD (liquid crystal display)

The LCD drives up to 8 common terminals and 44 segment terminals to drive up to 320 pixels.

- Internal step-up converter to guarantee functionality and contrast control irrespective of V<sub>DD</sub>. This converter can be deactivated, in which case the V<sub>LCD</sub> pin is used to provide the voltage to the LCD

- Supports static, 1/2, 1/3, 1/4 and 1/8 duty

- Supports static, 1/2, 1/3 and 1/4 bias

- Phase inversion to reduce power consumption and EMI

- Up to 8 pixels can be programmed to blink

- Unneeded segments and common pins can be used as general I/O pins

- LCD RAM can be updated at any time owing to a double-buffer

- The LCD controller can operate in Stop mode

### 3.11 ADC (analog-to-digital converter)

A 12-bit analog-to-digital converters is embedded into STM32L151xD and STM32L152xD devices with up to 40 external channels, performing conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs with up to 28 external channels in a group.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all scanned channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start triggers, to allow the application to synchronize A/D conversions and timers. An injection mode allows high priority conversions to be done by interrupting a scan mode which runs in as a background task.

The ADC includes a specific low-power mode. The converter is able to operate at maximum speed even if the CPU is operating at a very low frequency and has an auto-shutdown function. The ADC's runtime and analog front-end current consumption are thus minimized whatever the MCU operating mode.

#### 3.11.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\text{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies

DocID022027 Rev 11

## 4 Pin descriptions

1. This figure shows the package top view.

|         | P        | Pins    |        |         |                   |                         |                 |                                                  | Pin functions                                                      |                                      |  |

|---------|----------|---------|--------|---------|-------------------|-------------------------|-----------------|--------------------------------------------------|--------------------------------------------------------------------|--------------------------------------|--|

| LQFP144 | UFBGA132 | LQFP100 | LQFP64 | WLCSP64 | Pin name          | Pin Type <sup>(1)</sup> | I / O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                                                | Additional<br>functions              |  |

| 61      | -        | -       | -      | -       | V <sub>SS_7</sub> | S                       | -               | V <sub>SS_7</sub>                                | -                                                                  | -                                    |  |

| 62      | -        | I       | -      | -       | V <sub>DD_7</sub> | S                       | -               | V <sub>DD_7</sub>                                | -                                                                  | -                                    |  |

| 63      | L8       | 41      | -      | -       | PE10              | I/O                     | тс              | PE10                                             | TIM2_CH2/FSMC_D7                                                   | ADC_IN25/<br>COMP1_INP               |  |

| 64      | M9       | 42      | -      | -       | PE11              | I/O                     | FT              | PE11                                             | TIM2_CH3/FSMC_D8                                                   | -                                    |  |

| 65      | L9       | 43      | -      | -       | PE12              | I/O                     | FT              | PE12                                             | TIM2_CH4/SPI1_NSS<br>/FSMC_D9                                      | -                                    |  |

| 66      | M10      | 44      | -      | -       | PE13              | I/O                     | FT              | PE13                                             | SPI1_SCK/FSMC_D10                                                  | -                                    |  |

| 67      | M11      | 45      | -      | -       | PE14              | I/O                     | FT              | PE14                                             | SPI1_MISO/FSMC_D11                                                 | -                                    |  |

| 68      | M12      | 46      | -      | -       | PE15              | I/O                     | FT              | PE15                                             | SPI1_MOSI/FSMC_D12                                                 | -                                    |  |

| 69      | L10      | 47      | 29     | G3      | PB10              | I/O                     | FT              | PB10                                             | TIM2_CH3/I2C2_SCL/<br>USART3_TX/<br>LCD_SEG10                      | -                                    |  |

| 70      | L11      | 48      | 30     | F3      | PB11              | I/O                     | FT              | PB11                                             | TIM2_CH4/ I2C2_SDA/<br>USART3_RX/ LCD_SEG11                        | -                                    |  |

| 71      | F12      | 49      | 31     | H2      | V <sub>SS_1</sub> | S                       | -               | V <sub>SS_1</sub>                                | -                                                                  | -                                    |  |

| 72      | G12      | 50      | 32     | H1      | $V_{DD_1}$        | S                       | -               | V <sub>DD_1</sub>                                | -                                                                  | -                                    |  |

| 73      | L12      | 51      | 33     | G2      | PB12              | I/O                     | FT              | PB12                                             | TIM10_CH1/I2C2_SMBA/<br>SPI2_NSS/ I2S2_WS/<br>USART3_CK/ LCD_SEG12 | ADC_IN18/<br>COMP1_INP               |  |

| 74      | K12      | 52      | 34     | G1      | PB13              | I/O                     | FT              | PB13                                             | TIM9_CH1/SPI2_SCK/<br>I2S2_CK/<br>USART3_CTS/<br>LCD_SEG13         | ADC_IN19/<br>COMP1_INP               |  |

| 75      | K11      | 53      | 35     | F2      | PB14              | I/O                     | FT              | PB14                                             | TIM9_CH2/SPI2_MISO/<br>USART3_RTS/<br>LCD_SEG14                    | ADC_IN20/<br>COMP1_INP               |  |

| 76      | K10      | 54      | 36     | F1      | PB15              | I/O                     | FT              | PB15                                             | TIM11_CH1/SPI2_MOSI/<br>I2S2_SD/<br>LCD_SEG15                      | ADC_IN21/<br>COMP1_INP/<br>RTC_REFIN |  |

| 77      | K9       | 55      | -      | -       | PD8               | I/O                     | FT              | PD8                                              | USART3_TX/LCD_SEG28/<br>FSMC_D13                                   | -                                    |  |

| 78      | K8       | 56      | -      | -       | PD9               | I/O                     | FT              | PD9                                              | USART3_RX/LCD_SEG29/<br>FSMC_D14                                   | -                                    |  |

#### Table 8. STM32L151xD and STM32L152xD pin definitions (continued)

2

#### **Alternate functions**

|           |        |                    |          |                | [      | Digital alte | ernate fui          | nction numb | er      |          |               |          |              |

|-----------|--------|--------------------|----------|----------------|--------|--------------|---------------------|-------------|---------|----------|---------------|----------|--------------|

|           | AFIO0  | AFIO1              | AFIO2    | AFIO3          | AFIO4  | AFIO5        | AFIO6               | AFIO7       | AFIO8.  | . AFIO11 | AFIO12.       | AFIO14   | AFIO15       |

| Port name |        | Alternate function |          |                |        |              |                     |             |         |          |               |          |              |

|           | SYSTEM | TIM2               | TIM3/4/5 | TIM9/<br>10/11 | I2C1/2 | SPI1/2       | SPI3                | USART1/2/3  | UART4/5 | LCD      | FSMC/<br>SDIO | CPRI     | SYSTEM       |

| BOOT0     | ΒΟΟΤΟ  | -                  | -        | -              | -      | -            | -                   | -           | -       | -        | -             | -        | EVENT<br>OUT |

| NRST      | NRST   | -                  | -        | -              | -      | -            | -                   | -           | -       | -        | -             | -        | -            |

| PA0-WKUP1 | -      | TIM2_CH1_ETR       | TIM5_CH1 | -              | -      | -            | -                   | USART2_CTS  | -       | -        | -             | TIMx_IC1 | EVENT<br>OUT |

| PA1       | -      | TIM2_CH2           | TIM5_CH2 | -              | -      | -            | -                   | USART2_RTS  | -       | SEG0     | -             | TIMx_IC2 | EVENT<br>OUT |

| PA2       | -      | TIM2_CH3           | TIM5_CH3 | TIM9_CH1       | -      | -            | -                   | USART2_TX   | -       | SEG1     | -             | TIMx_IC3 | EVENT<br>OUT |

| PA3       | -      | TIM2_CH4           | TIM5_CH4 | TIM9_CH2       | -      | -            | -                   | USART2_RX   | -       | SEG2     | -             | TIMx_IC4 | EVENT<br>OUT |

| PA4       | -      | -                  | -        | -              | -      | SPI1_NSS     | SPI3_NSS<br>I2S3_WS | USART2_CK   | -       | -        | -             | TIMx_IC1 | EVENT<br>OUT |

| PA5       | -      | TIM2_CH1_ETR       | -        | -              | -      | SPI1_SCK     | -                   | -           | -       | -        | -             | TIMx_IC2 | EVENT<br>OUT |

| PA6       | -      | -                  | TIM3_CH1 | TIM10_CH1      | -      | SPI1_MISO    | -                   | -           | -       | SEG3     | -             | TIMx_IC3 | EVENT<br>OUT |

| PA7       | -      | -                  | TIM3_CH2 | TIM11_CH1      | -      | SPI1_MOSI    | -                   | -           | -       | SEG4     | -             | TIMx_IC4 | EVENT<br>OUT |

| PA8       | мсо    | -                  | -        | -              | -      | -            | -                   | USART1_CK   | -       | СОМО     | -             | TIMx_IC1 | EVENT<br>OUT |

| PA9       | -      | -                  | -        | -              | -      | -            | -                   | USART1_TX   | -       | COM1     | -             | TIMx_IC2 | EVENT<br>OUT |

| PA10      | -      | -                  | -        | -              | -      | -            | -                   | USART1_RX   | -       | COM2     | -             | TIMx_IC3 | EVENT<br>OUT |

| PA11      | -      | -                  | -        | -              | -      | SPI1_MISO    |                     | USART1_CTS  | -       | -        | -             | TIMx_IC4 | EVENT<br>OUT |

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 10: Voltage characteristics*, *Table 11: Current characteristics*, and *Table 12: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                                                      | Ratings                                                                         | Min                  | Мах                  | Unit |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>                                            | External main supply voltage (including $V_{DDA}$ and $V_{DD}$ ) <sup>(1)</sup> | -0.3                 | 4.0                  |      |

| V <sub>IN</sub> <sup>(2)</sup>                                              | Input voltage on five-volt tolerant pin                                         | V <sub>SS</sub> –0.3 | V <sub>DD</sub> +4.0 | V    |

| VIN                                                                         | Input voltage on any other pin                                                  | V <sub>SS</sub> –0.3 | 4.0                  |      |

| ΔV <sub>DDx</sub>                                                           | Variations between different V <sub>DD</sub> power pins                         | -                    | 50                   | mV   |

| V <sub>SSX</sub> –V <sub>SS</sub>                                           | Variations between all different ground pins <sup>(3)</sup>                     | -                    | 50                   |      |

| V <sub>REF+</sub> –V <sub>DDA</sub>                                         | Allowed voltage difference for $V_{REF+} > V_{DDA}$                             | -                    | 0.4                  | V    |

| V <sub>ESD(HBM)</sub> Electrostatic discharge voltage<br>(human body model) |                                                                                 | see Secti            | ion 6.3.12           |      |

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 11* for maximum allowed injected current values.

3. Include  $V_{REF-}$  pin.

#### Table 11. Current characteristics

| Symbol                               | Ratings                                                                        | Max. | Unit |

|--------------------------------------|--------------------------------------------------------------------------------|------|------|

| $I_{VDD(\Sigma)}$                    | Total current into sum of all $V_{DD_x}$ power lines (source) <sup>(1)</sup>   | 100  |      |

| $I_{VSS(\Sigma)}^{(2)}$              | Total current out of sum of all $V_{SS_x}$ ground lines (sink) <sup>(1)</sup>  | 100  |      |

| I <sub>VDD(PIN)</sub>                | Maximum current into each V <sub>DD_x</sub> power pin (source) <sup>(1)</sup>  | 70   |      |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each VSS_x ground pin (sink) <sup>(1)</sup>             | -70  |      |

|                                      | Output current sunk by any I/O and control pin                                 | 25   |      |

| I <sub>IO</sub>                      | Output current sourced by any I/O and control pin                              | - 25 | mA   |

| 51                                   | Total output current sunk by sum of all IOs and control pins <sup>(2)</sup>    | 60   |      |

| ΣΙ <sub>ΙΟ(ΡΙΝ)</sub>                | Total output current sourced by sum of all IOs and control pins <sup>(2)</sup> | -60  |      |

| (3)                                  | Injected current on five-volt tolerant I/O <sup>(4)</sup> , RST and B pins     |      |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on any other pin <sup>(5)</sup>                               | ± 5  |      |

| ΣΙ <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>        | ± 25 |      |

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

3. Negative injection disturbs the analog performance of the device. See note in Section 6.3.19.

| Symbol                            | Parameter                                                  | Conditions                                                          | f <sub>HCLK</sub>                                  | Тур   | Max   | Unit |    |

|-----------------------------------|------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------|-------|-------|------|----|

|                                   |                                                            |                                                                     | Range3,                                            | 1     | 230   | 470  |    |

|                                   |                                                            |                                                                     | V <sub>CORE</sub> =1.2 V                           | 2     | 415   | 780  | μA |

|                                   |                                                            |                                                                     | VOS[1:0]=11                                        | 4     | 800   | 1200 |    |

|                                   |                                                            | f <sub>HSE</sub> = f <sub>HCLK</sub> up to 16 MHz,                  | Range2,                                            | 4     | 0.935 | 1.5  |    |

|                                   |                                                            | included $f_{HSE} = f_{HCLK}/2$ above 16MHz (PLL ON) <sup>(1)</sup> | V <sub>CORE</sub> =1.5 V                           | 8     | 1.9   | 3    |    |

|                                   | Supply current in<br>Run mode code<br>executed from<br>RAM | 16MHz (PLL ON) <sup>(1)</sup>                                       | VOS[1:0]=10                                        | 16    | 3.75  | 5    | mA |

|                                   |                                                            |                                                                     | Range1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0]=01 | 8     | 2.25  | 3.5  |    |

|                                   |                                                            |                                                                     |                                                    | 16    | 4.45  | 5.55 |    |

| I <sub>DD (Run</sub><br>from RAM) |                                                            |                                                                     |                                                    | 32    | 9.05  | 10.9 |    |

|                                   |                                                            | HSI clock source (16 MHz)                                           | Range2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0]=10 | 16    | 3.75  | 4.8  |    |

|                                   |                                                            |                                                                     | Range1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0]=01 | 32    | 8.95  | 11.7 |    |

|                                   |                                                            | MSI clock, 65 kHZ                                                   | Range3,                                            | 0.065 | 43.5  | 100  |    |

|                                   |                                                            | MSI clock, 524 kHZ                                                  | V <sub>CORE</sub> =1.2 V                           | 0.524 | 135   | 215  | μA |

|                                   |                                                            | MSI clock, 4.2 MHZ                                                  | VOS[1:0]=11                                        | 4.2   | 835   | 1100 |    |

#### Table 18. Current consumption in Run mode, code with data processing running from RAM

1. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol               | Parameter                                                                            | Conditions                                                        | Тур  | Max <sup>(1)</sup> | Unit |  |

|----------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------|------|--------------------|------|--|

| t <sub>WUSLEEP</sub> | Wakeup from Sleep mode                                                               | f <sub>HCLK</sub> = 32 MHz                                        | 0.4  | -                  |      |  |

| twusleep_lp          | Wakeup from Low-power sleep                                                          | f <sub>HCLK</sub> = 262 kHz<br>Flash enabled                      | 46   | -                  |      |  |

|                      | mode, f <sub>HCLK</sub> = 262 kHz                                                    | f <sub>HCLK</sub> = 262 kHz<br>Flash switched OFF                 | 46   | -                  |      |  |

|                      | Wakeup from Stop mode,<br>regulator in Run mode<br>ULP bit = 1 and FWU bit = 1       | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 8.2  | -                  |      |  |

|                      |                                                                                      | $f_{HCLK} = f_{MSI} = 4.2 \text{ MHz}$<br>Voltage range 1 and 2   | 7.7  | 8.9                |      |  |

|                      |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 3 | 8.2  | 13.1               | μs   |  |

| t <sub>WUSTOP</sub>  | Wakeup from Stop mode,<br>regulator in low-power mode<br>ULP bit = 1 and FWU bit = 1 | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 10.2 | 13.4               |      |  |

|                      |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                   | 16   | 20                 |      |  |

|                      |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                    | 31   | 37                 |      |  |

|                      |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                    | 57   | 66                 |      |  |

|                      |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                    | 112  | 123                |      |  |

|                      |                                                                                      | f <sub>HCLK</sub> = MSI = 65 kHz                                  | 221  | 236                |      |  |

| t                    | Wakeup from Standby mode<br>ULP bit = 1 and FWU bit = 1                              | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 58   | 104                |      |  |

| <sup>t</sup> wustdby | Wakeup from Standby mode<br>FWU bit = 0                                              | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 2.6  | 3.25               | ms   |  |

Table 25. Low-power mode wakeup timings

1. Guaranteed by characterization, unless otherwise specified

#### 6.3.6 External clock source characteristics

.

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.13*. However, the recommended clock input waveform is shown in *Figure 14*.

| Table 26 | High-speed | external | user clock | characteristics <sup>(1)</sup> |

|----------|------------|----------|------------|--------------------------------|

|          |            |          |            |                                |

| Symbol               | Parameter                  | Conditions                  | Min | Тур | Мах | Unit |

|----------------------|----------------------------|-----------------------------|-----|-----|-----|------|

| £                    | User external clock source | CSS is on or<br>PLL is used | 1   | 8   | 32  | MHz  |

| <sup>T</sup> HSE_ext | frequency                  | CSS is off, PLL<br>not used | 0   | 8   | 32  | MHz  |

| Symbol                              | Parameter                                                                                                 | Conditions                                                  | Min | Тур | Мах                                | Unit  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|------------------------------------|-------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency                                                                                      | -                                                           | 1   |     | 24                                 | MHz   |

| R <sub>F</sub>                      | Feedback resistor                                                                                         | -                                                           | -   | 200 | -                                  | kΩ    |

| С                                   | Recommended load<br>capacitance versus<br>equivalent serial<br>resistance of the crystal<br>$(R_S)^{(3)}$ | R <sub>S</sub> = 30 Ω                                       | -   | 20  | -                                  | pF    |

| I <sub>HSE</sub>                    | HSE driving current                                                                                       | $V_{DD}$ = 3.3 V,<br>$V_{IN}$ = $V_{SS}$ with 30 pF<br>load | -   | -   | 3                                  | mA    |

| I <sub>DD(HSE)</sub>                | HSE oscillator power consumption                                                                          | C = 20 pF<br>f <sub>OSC</sub> = 16 MHz                      | -   | -   | 2.5 (startup)<br>0.7 (stabilized)  | mA    |

|                                     |                                                                                                           | C = 10 pF<br>f <sub>OSC</sub> = 16 MHz                      | -   | -   | 2.5 (startup)<br>0.46 (stabilized) |       |

| 9 <sub>m</sub>                      | Oscillator<br>transconductance                                                                            | Startup                                                     | 3.5 | -   | -                                  | mA /V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                                                                              | V <sub>DD</sub> is stabilized                               | -   | 1   | -                                  | ms    |

Table 28. HSE oscillator characteristics<sup>(1)(2)</sup>

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by characterization results.

The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

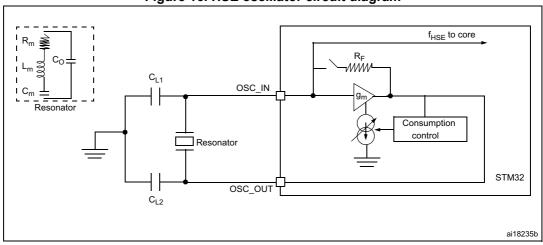

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 16*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

Figure 16. HSE oscillator circuit diagram

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 29*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                | Parameter                                                                                     | Conditions                            | Min   | Тур    | Max | Unit |

|-----------------------|-----------------------------------------------------------------------------------------------|---------------------------------------|-------|--------|-----|------|

| f <sub>LSE</sub>      | Low speed external oscillator<br>frequency                                                    | -                                     | -     | 32.768 | -   | kHz  |

| R <sub>F</sub>        | Feedback resistor -                                                                           |                                       | -     | 1.2    | -   | MΩ   |

| C <sup>(2)</sup>      | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 kΩ                | -     | 8      | -   | pF   |

| I <sub>LSE</sub>      | LSE driving current                                                                           | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$ | -     | -      | 1.1 | μA   |

|                       |                                                                                               | V <sub>DD</sub> = 1.8 V               | -     | 450    | -   |      |

| I <sub>DD (LSE)</sub> | LSE oscillator current<br>consumption                                                         | V <sub>DD</sub> = 3.0 V               | - 600 | -      | nA  |      |

|                       |                                                                                               | V <sub>DD</sub> = 3.6V                | -     | 750    | -   |      |

| 9 <sub>m</sub>        | Oscillator transconductance                                                                   | -                                     | 3     | -      | -   | µA/V |

| $t_{SU(LSE)}^{(4)}$   | Startup time                                                                                  | $V_{DD}$ is stabilized                | -     | 1      | -   | S    |

| Table 29. LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz) <sup>(</sup> | r characteristics (f <sub>l SE</sub> = 32.768 kHz) <sup>(1)</sup> | le 29. LSE oscillato |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------|

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------|

1. Guaranteed by characterization results.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value for example MSIV-TIN32.768kHz. Refer to crystal manufacturer for more details.

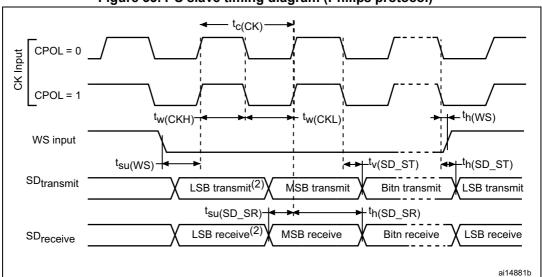

ODD bit value, digital contribution leads to a min of (I2SDIV/(2\*I2SDIV+ODD) and a max of (I2SDIV+ODD)/(2\*I2SDIV+ODD). Fs max is supported for each mode/condition.

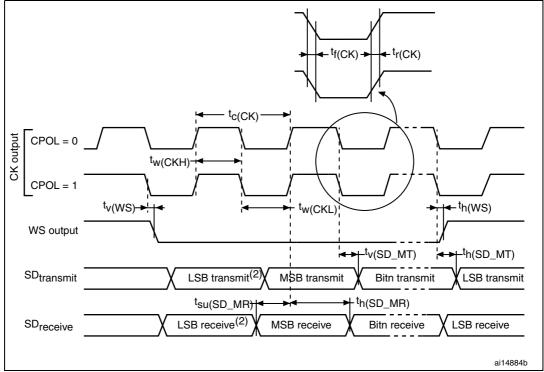

Figure 33. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels: 0.3 × V\_{DD} and 0.7 × V\_{DD}.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

Figure 34. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Guaranteed by characterization results.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

| Symbol                          | Parameter                                          | Conditions                                             | Min  | Тур                                                            | Max     | Unit               |

|---------------------------------|----------------------------------------------------|--------------------------------------------------------|------|----------------------------------------------------------------|---------|--------------------|

|                                 |                                                    | Direct channels<br>2.4 V ⊴V <sub>DDA</sub> ≤3.6 V      | 0.25 |                                                                |         |                    |

| t <sub>S</sub> <sup>(5)</sup>   |                                                    | Multiplexed channels<br>2.4 V ⊴V <sub>DDA</sub> ≤3.6 V | 0.56 | -                                                              | -       |                    |

|                                 | Sampling time                                      | Direct channels<br>1.8 V ⊴V <sub>DDA</sub> ⊴2.4 V      | 0.56 | -                                                              | -       | μs                 |

|                                 |                                                    | Multiplexed channels<br>1.8 V ⊴V <sub>DDA</sub> ⊴2.4 V | 1    |                                                                |         |                    |

|                                 |                                                    | -                                                      | 4    | - 24.75<br>sampling phase) +1<br>(e approximation)<br>- 16<br> | 384     | 1/f <sub>ADC</sub> |

|                                 | Total conversion time                              | f <sub>ADC</sub> = 16 MHz                              | 1    | -                                                              | 24.75   | μs                 |

| t <sub>CONV</sub>               | Total conversion time<br>(including sampling time) | -                                                      |      |                                                                |         | 1/f <sub>ADC</sub> |

| C                               | Internal sample and hold                           | Direct channels                                        | -    | 16                                                             | -       | pF                 |

| C <sub>ADC</sub> ca             | capacitor                                          | Multiplexed channels                                   | -    | 10                                                             | -       |                    |

| f                               | External trigger frequency                         | 12-bit conversions                                     | -    | -                                                              | Tconv+1 | 1/f <sub>ADC</sub> |

| f <sub>TRIG</sub>               | Regular sequencer                                  | 6/8/10-bit conversions                                 | -    | -                                                              | Tconv   | 1/f <sub>ADC</sub> |

| £                               | External trigger frequency                         | 12-bit conversions                                     | -    | -                                                              | Tconv+2 | 1/f <sub>ADC</sub> |

| f <sub>TRIG</sub>               | Injected sequencer                                 | 6/8/10-bit conversions                                 | -    | -                                                              | Tconv+1 | 1/f <sub>ADC</sub> |

| R <sub>AIN</sub> <sup>(6)</sup> | Signal source impedance                            |                                                        | -    | -                                                              | 50      | kΩ                 |

| +                               | Injection trigger conversion                       | f <sub>ADC</sub> = 16 MHz                              | 219  | -                                                              | 281     | ns                 |

| t <sub>lat</sub>                | latency                                            | -                                                      | 3.5  | -                                                              | 4.5     | 1/f <sub>ADC</sub> |

| t                               | Regular trigger conversion                         | f <sub>ADC</sub> = 16 MHz                              | 156  | -                                                              | 219     | ns                 |

| t <sub>latr</sub>               | latency                                            | -                                                      | 2.5  | -                                                              | 3.5     | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub>               | Power-up time                                      | -                                                      | -    | -                                                              | 3.5     | μs                 |

#### Table 64. ADC characteristics (continued)

1. The Vref+ input can be grounded if neither the ADC nor the DAC are used (this allows to shut down an external voltage reference).

2. The current consumption through VREF is composed of two parameters:

- one constant (max 300 µA)

- one variable (max 400  $\mu A$ ), only during sampling time + 2 first conversion pulses

So, peak consumption is 300+400 = 700  $\mu A$  and average consumption is 300 + [(4 sampling + 2) /16] x 400 = 450  $\mu A$  at 1Msps

V<sub>REF+</sub> can be internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> can be internally connected to V<sub>SSA</sub>, depending on the package. Refer to Section 4: Pin descriptions for further details.

4.  $V_{SSA}$  or  $V_{REF-}$  must be tied to ground.

5. Minimum sampling time is reached for an external input impedance limited to a value as defined in *Table 66: Maximum source impedance RAIN max*.

6. External impedance has another high value limitation when using short sampling time as defined in *Table 66: Maximum source impedance RAIN max*.

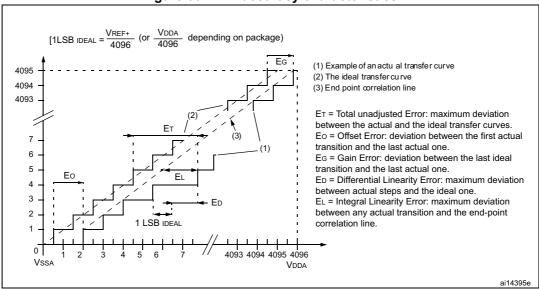

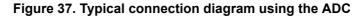

#### Figure 36. ADC accuracy characteristics

- 1. Refer to Table 66: Maximum source impedance RAIN max for the value of  $R_{AIN}$  and Table 64: ADC characteristics for the value of  $C_{ADC}$ .

- C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

## 6.3.20 DAC electrical specifications

Data guaranteed by design, unless otherwise specified.

| Symbol                              | Parameter                                             | Conditions                                                                     | Min | Тур              | Мах                         | Unit |  |

|-------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------|-----|------------------|-----------------------------|------|--|

| V <sub>DDA</sub>                    | Analog supply voltage                                 | -                                                                              | 1.8 | -                | 3.6                         |      |  |

| V <sub>REF+</sub>                   | Reference supply voltage                              | $V_{REF^+}$ must always be below $V_{DDA}$                                     | 1.8 | -                | 3.6                         | V    |  |

| V <sub>REF-</sub>                   | Lower reference voltage                               | -                                                                              |     | V <sub>SSA</sub> |                             |      |  |

| Current consumption on              |                                                       | No load, middle code (0x800)                                                   | -   | 130              | 220                         |      |  |

| I <sub>DDVREF+</sub> <sup>(1)</sup> | V <sub>REF+</sub> supply<br>V <sub>REF+</sub> = 3.3 V | No load, worst code (0x000)                                                    | -   | 220              | 350                         |      |  |

| . (1)                               | Current consumption on                                | No load, middle code (0x800)                                                   | -   | 210              | 320                         | μA   |  |

| I <sub>DDA</sub> <sup>(1)</sup>     | V <sub>DDA</sub> supply<br>V <sub>DDA</sub> = 3.3 V   | No load, worst code (0xF1C)                                                    | -   | 320              | 520                         | 1    |  |

| $R_L^{(2)}$                         | Resistive load                                        | DAC output buffer ON                                                           |     | -                | -                           | kΩ   |  |

| C <sub>L</sub> <sup>(2)</sup>       | Capacitive load                                       |                                                                                |     | -                | 50                          | pF   |  |

| R <sub>O</sub>                      | Output impedance                                      |                                                                                |     | 16               | 20                          | kΩ   |  |

| N.                                  | Voltage on DAC_OUT<br>output                          | DAC output buffer ON                                                           | 0.2 | -                | V <sub>DDA</sub> – 0.2      | v    |  |

| V <sub>DAC_OUT</sub>                |                                                       | DAC output buffer OFF                                                          | 0.5 | -                | V <sub>REF+</sub> –<br>1LSB | mV   |  |

| DNL <sup>(1)</sup>                  | Differential non                                      | $C_{L} \le 50 \text{ pF}, R_{L} \ge 5 \text{ k}\Omega$<br>DAC output buffer ON | -   | 1.5              | 3                           |      |  |

|                                     | linearity <sup>(3)</sup>                              | No R <sub>L</sub> , C <sub>L</sub> $\leq$ 50 pF<br>DAC output buffer OFF       | -   | 1.5              | 3                           |      |  |

| INL <sup>(1)</sup>                  | Integral non linearity <sup>(4)</sup>                 | $C_{L} \le 50 \text{ pF}, R_{L} \ge 5 \text{ k}\Omega$<br>DAC output buffer ON | -   | 2                | 4                           |      |  |

|                                     | Integral non linearity <sup>(4)</sup>                 | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                    | -   | 2                | 4                           | LSB  |  |

| Offset <sup>(1)</sup>               | Offset error at code                                  | $C_{L} \le 50 \text{ pF}, R_{L} \ge 5 \text{ k}\Omega$<br>DAC output buffer ON | -   | ±10              | ±25                         |      |  |

|                                     | 0x800 <sup>(5)</sup>                                  | No R <sub>L</sub> , C <sub>L</sub> $\leq$ 50 pF<br>DAC output buffer OFF       | -   | ±5               | ±8                          |      |  |

| Offset1 <sup>(1)</sup>              | Offset error at code 0x001 <sup>(6)</sup>             | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                    | -   | ±1.5             | ±5                          |      |  |

# 7.2 LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package information

Figure 43. LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 75. LQPF100, 14 x 14 mm, | 100-pin low-profile quad flat package mechanical |

|--------------------------------|--------------------------------------------------|

|                                | data                                             |

|        | uala   |             |        |        |        |        |  |  |

|--------|--------|-------------|--------|--------|--------|--------|--|--|

| Symbol |        | millimeters |        |        |        |        |  |  |

| Symbol | Min    | Тур         | Max    | Min    | Тур    | Max    |  |  |

| А      | -      | -           | 1.600  | -      | -      | 0.0630 |  |  |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -      | 0.0059 |  |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551 | 0.0571 |  |  |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087 | 0.0106 |  |  |

| С      | 0.090  | -           | 0.200  | 0.0035 | -      | 0.0079 |  |  |

| D      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299 | 0.6378 |  |  |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512 | 0.5591 |  |  |

| D3     | -      | 12.000      | -      | -      | 0.4724 | -      |  |  |

| Е      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299 | 0.6378 |  |  |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512 | 0.5591 |  |  |

## Table 77. UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid arraypackage mechanical data (continued)

| Symbol |     | millimeters |       |     | inches <sup>(1)</sup> |        |  |

|--------|-----|-------------|-------|-----|-----------------------|--------|--|

| Symbol | Min | Тур         | Max   | Min | Тур                   | Max    |  |

| ddd    | -   | -           | 0.080 | -   | -                     | 0.0031 |  |

| eee    | -   | -           | 0.150 | -   | -                     | 0.0059 |  |

| fff    | -   | -           | 0.050 | -   | -                     | 0.0020 |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

## Figure 50. UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid array package recommended footprint