Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 384KB (384K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 12K x 8                                                                 |

| RAM Size                   | 48K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 21x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151rdt7   |

|   | 3.16  | Touch s  | sensing                                                                | . 29 |

|---|-------|----------|------------------------------------------------------------------------|------|

|   | 3.17  | Timers   | and watchdogs                                                          | . 30 |

|   |       | 3.17.1   | General-purpose timers (TIM2, TIM3, TIM4, TIM5, TIM9, TIM10 and TIM11) | . 30 |

|   |       | 3.17.2   | Basic timers (TIM6 and TIM7)                                           | . 31 |

|   |       | 3.17.3   | SysTick timer                                                          | . 31 |

|   |       | 3.17.4   | Independent watchdog (IWDG)                                            | . 31 |

|   |       | 3.17.5   | Window watchdog (WWDG)                                                 | . 31 |

|   | 3.18  | Commi    | unication interfaces                                                   | . 31 |

|   |       | 3.18.1   | I <sup>2</sup> C bus                                                   | . 31 |

|   |       | 3.18.2   | Universal synchronous/asynchronous receiver transmitter (USART) .      | . 32 |

|   |       | 3.18.3   | Serial peripheral interface (SPI)                                      | . 32 |

|   |       | 3.18.4   | Inter-integrated sound (I2S)                                           | . 32 |

|   |       | 3.18.5   | SDIO                                                                   | . 32 |

|   |       | 3.18.6   | Universal serial bus (USB)                                             | . 32 |

|   | 3.19  | CRC (c   | cyclic redundancy check) calculation unit                              | . 33 |

|   | 3.20  | Develo   | pment support                                                          | . 34 |

|   |       | 3.20.1   | Serial wire JTAG debug port (SWJ-DP)                                   | . 34 |

|   |       | 3.20.2   | Embedded Trace Macrocell™                                              | . 34 |

|   |       |          |                                                                        |      |

| 4 | Pin d | lescript | ions                                                                   | 35   |

| _ | Mana  |          |                                                                        |      |

| 5 | wem   | ory map  | oping                                                                  | . 57 |

| 6 | Elect | rical ch | aracteristics                                                          | . 58 |

|   | 6.1   | Parame   | eter conditions                                                        | . 58 |

|   |       | 6.1.1    | Minimum and maximum values                                             | . 58 |

|   |       | 6.1.2    | Typical values                                                         | . 58 |

|   |       | 6.1.3    | Typical curves                                                         | . 58 |

|   |       | 6.1.4    | Loading capacitor                                                      | . 58 |

|   |       | 6.1.5    | Pin input voltage                                                      | . 58 |

|   |       | 6.1.6    | Power supply scheme                                                    | . 59 |

|   |       | 6.1.7    | Optional LCD power supply scheme                                       | . 60 |

|   |       | 6.1.8    | Current consumption measurement                                        | . 60 |

|   | 6.2   | Absolu   | te maximum ratings                                                     | 61   |

|   | 6.3   | Operati  | ing conditions                                                         | 62   |

|   |       | 6.3.1    | General operating conditions                                           | . 62 |

|   |       |          | · -                                                                    |      |

| Table 47. | ESD absolute maximum ratings                                                    | . 102 |

|-----------|---------------------------------------------------------------------------------|-------|

| Table 48. | Electrical sensitivities                                                        |       |

| Table 49. | I/O current injection susceptibility                                            |       |

| Table 50. | I/O static characteristics                                                      |       |

| Table 51. | Output voltage characteristics                                                  |       |

| Table 52. | I/O AC characteristics                                                          |       |

| Table 53. | NRST pin characteristics                                                        |       |

| Table 54. | TIMx characteristics                                                            |       |

| Table 55. | I <sup>2</sup> C characteristics                                                |       |

| Table 56. | SCL frequency (f <sub>PCL K1</sub> = 32 MHz, V <sub>DD</sub> = VDD_I2C = 3.3 V) |       |

| Table 57. | SPI characteristics                                                             |       |

| Table 58. | USB startup time                                                                |       |

| Table 59. | USB DC electrical characteristics                                               |       |

| Table 60. | USB: full speed electrical characteristics                                      | . 114 |

| Table 61. | I2S characteristics                                                             | . 115 |

| Table 62. | SDIO characteristics                                                            | . 117 |

| Table 63. | ADC clock frequency                                                             | . 118 |

| Table 64. | ADC characteristics                                                             |       |

| Table 65. | ADC accuracy                                                                    | . 120 |

| Table 66. | Maximum source impedance R <sub>AIN</sub> max                                   |       |

| Table 67. | DAC characteristics                                                             | . 123 |

| Table 68. | Operational amplifier characteristics                                           | . 125 |

| Table 69. | Temperature sensor calibration values                                           | . 127 |

| Table 70. | Temperature sensor characteristics                                              | . 127 |

| Table 71. | Comparator 1 characteristics                                                    | . 127 |

| Table 72. | Comparator 2 characteristics                                                    | . 128 |

| Table 73. | LCD controller characteristics                                                  | . 129 |

| Table 74. | LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package mechanical data      | . 131 |

| Table 75. | LQPF100, 14 x 14 mm, 100-pin low-profile quad flat package mechanical data      | . 133 |

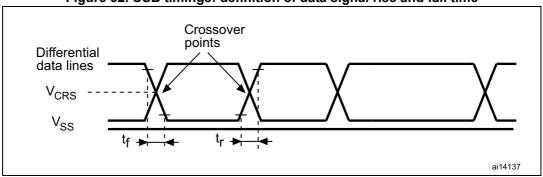

| Table 76. | LQFP64, 10 x 10 mm 64-pin low-profile quad flat package mechanical data         | . 136 |

| Table 77. | UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid array             |       |

|           | package mechanical data                                                         |       |

| Table 78. | WLCSP64, 0.4 mm pitch wafer level chip scale package mechanical data            |       |

| Table 79. | WLCSP64, 0.4 mm pitch package recommended PCB design rules                      |       |

| Table 80. | Thermal characteristics                                                         |       |

| Table 81. | Ordering information scheme                                                     |       |

| Table 82. | Document revision history                                                       | . 148 |

# **List of figures**

| Figure 1.  | Ultra-low-power STM32L151xD and STM32L152xD block diagram                      | 15  |

|------------|--------------------------------------------------------------------------------|-----|

| Figure 2.  | Clock tree                                                                     |     |

| Figure 3.  | STM32L15xZD LQFP144 pinout                                                     | 35  |

| Figure 4.  | STM32L15xQD UFBGA132 ballout                                                   |     |

| Figure 5.  | STM32L15xVD LQFP100 pinout                                                     | 37  |

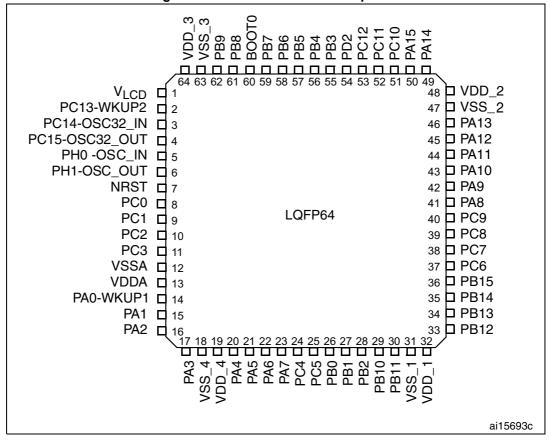

| Figure 6.  | STM32L15xRD LQFP64 pinout                                                      | 38  |

| Figure 7.  | STM32L15xRD WLCSP64 ballout                                                    | 39  |

| Figure 8.  | Memory map                                                                     | 57  |

| Figure 9.  | Pin loading conditions                                                         | 58  |

| Figure 10. | Pin input voltage                                                              |     |

| Figure 11. | Power supply scheme                                                            |     |

| Figure 12. | Optional LCD power supply scheme                                               |     |

| Figure 13. | Current consumption measurement scheme                                         |     |

| Figure 14. | High-speed external clock source AC timing diagram                             |     |

| Figure 15. | Low-speed external clock source AC timing diagram                              |     |

| Figure 16. | HSE oscillator circuit diagram                                                 |     |

| Figure 17. | Typical application with a 32.768 kHz crystal                                  |     |

| Figure 18. | Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms                     |     |

| Figure 19. | Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms                    |     |

| Figure 20. | Asynchronous multiplexed PSRAM/NOR read waveforms                              |     |

| Figure 21. | Asynchronous multiplexed PSRAM/NOR write waveforms                             |     |

| Figure 22. | Synchronous multiplexed NOR/PSRAM read timings                                 |     |

| Figure 23. | Synchronous multiplexed PSRAM write timings                                    |     |

| Figure 24. | Synchronous non-multiplexed NOR/PSRAM read timings                             |     |

| Figure 25. | Synchronous non-multiplexed PSRAM write timings                                |     |

| Figure 26. | I/O AC characteristics definition                                              |     |

| Figure 27. | Recommended NRST pin protection                                                |     |

| Figure 28. | I <sup>2</sup> C bus AC waveforms and measurement circuit                      |     |

| Figure 29. | SPI timing diagram - slave mode and CPHA = 0                                   | 112 |

| Figure 30. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                    | 112 |

| Figure 31. | SPI timing diagram - master mode <sup>(1)</sup>                                | 113 |

| Figure 32. | USB timings: definition of data signal rise and fall time                      | 114 |

| Figure 33. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>        | 116 |

| Figure 34. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>       | 116 |

| Figure 35. | SDIO timings                                                                   | 117 |

| Figure 36. | ADC accuracy characteristics                                                   | 121 |

| Figure 37. | Typical connection diagram using the ADC                                       | 121 |

| Figure 38. | Maximum dynamic current consumption on V <sub>REF+</sub> supply pin during ADC |     |

| _          | conversion                                                                     |     |

| Figure 39. | 12-bit buffered /non-buffered DAC                                              | 125 |

| Figure 40. | LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package outline             | 130 |

| Figure 41. | LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package                     |     |

| _          | recommended footprint                                                          | 132 |

| Figure 42. | LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package top view example    |     |

| Figure 43. | LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package outline             | 133 |

| Figure 44. | LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package                     |     |

| -          | recommended footprint                                                          | 134 |

| Figure 45  | LOFP100 14 x 14 mm 100-pin low-profile guad flat package top view example      | 135 |

### 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32L151xD and STM32L152xD ultra-low-power ARM<sup>®</sup> Cortex<sup>®</sup>-M3 based microcontroller product line.

The STM32L151xD and STM32L152xD microcontrollers feature 384 Kbytes of Flash memory.

The ultra-low-power STM32L151xD and STM32L152xD family includes devices in 5 different package types: from 64 pins to 144 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the ultra-low-power STM32L151xD and STM32L152xD microcontroller family suitable for a wide range of applications:

- Medical and handheld equipment

- Application control and user interface

- PC peripherals, gaming, GPS and sport equipment

- Alarm systems, wired and wireless sensors, video intercom

- Utility metering

This STM32L151xD and STM32L152xD datasheet should be read in conjunction with the STM32L1xxxx reference manual (RM0038). The application note "Getting started with STM32L1xxxx hardware development" (AN3216) gives a hardware implementation overview. Both documents are available from the STMicroelectronics website www.st.com.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core please refer to the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 technical reference manual, available from the www.arm.com website. *Figure 1* shows the general block diagram of the device family.

## 2 Description

The ultra-low-power STM32L151xD and STM32L152xD devices incorporate the connectivity power of the universal serial bus (USB) with the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC core operating at a frequency of 32 MHz (33.3 DMIPS), a memory protection unit (MPU), high-speed embedded memories (Flash memory up to 384 Kbytes and RAM up to 48 Kbytes), a flexible static memory controller (FSMC) interface (for devices with packages of 100 pins and more) and an extensive range of enhanced I/Os and peripherals connected to two APB buses.

The STM32L151xD and STM32L152xD devices offer three operational amplifiers, one 12-bit ADC, two DACs, two ultra-low-power comparators, one general-purpose 32-bit timer, six general-purpose 16-bit timers and two basic timers, which can be used as time bases.

Moreover, the STM32L151xD and STM32L152xD devices contain standard and advanced communication interfaces: up to two I2Cs, three SPIs, two I2S, one SDIO, three USARTs, two UARTs, and an USB. The STM32L151xD and STM32L152xD devices offer up to 34 capacitive sensing channels to simply add a touch sensing functionality to any application.

They also include a real-time clock and a set of backup registers that remain powered in Standby mode.

Finally, the integrated LCD controller (except STM32L151xD devices) has a built-in LCD voltage generator that allows to drive up to 8 multiplexed LCDs with the contrast independent of the supply voltage.

The ultra-low-power STM32L151xD and STM32L152xD devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +85  $^{\circ}$ C and -40 to +105  $^{\circ}$ C temperature ranges. A comprehensive set of power-saving modes allows the design of low-power applications.

Table 3. Functionalities depending on the operating power supply range (continued)

|                                                  | Functionalities depending on the operating power supply range |                           |                                |                      |  |  |  |  |  |

|--------------------------------------------------|---------------------------------------------------------------|---------------------------|--------------------------------|----------------------|--|--|--|--|--|

| Operating power supply range                     | DAC and ADC operation                                         | USB                       | Dynamic voltage scaling range  | I/O operation        |  |  |  |  |  |

| V <sub>DD</sub> =V <sub>DDA</sub> = 2.0 to 2.4 V | Conversion time up to 500 Ksps                                | Functional <sup>(2)</sup> | Range 1, Range 2<br>or Range 3 | Full speed operation |  |  |  |  |  |

| V <sub>DD</sub> =V <sub>DDA</sub> = 2.4 to 3.6 V | Conversion time up to 1 Msps                                  | Functional <sup>(2)</sup> | Range 1, Range 2<br>or Range 3 | Full speed operation |  |  |  |  |  |

CPU frequency changes from initial to final must respect "F<sub>CPU</sub> initial < 4\*F<sub>CPU</sub> final" to limit V<sub>CORE</sub> drop due to current consumption peak when frequency increases. It must also respect 5 μs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, the user can switch from 4.2 MHz to 16 MHz, wait 5 μs, then switch from 16 MHz to 32 MHz.

Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                                | Dynamic voltage scaling range |

|----------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws)   | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)     | Range 2                       |

| 2.1MHz to 4.2 MHz (1ws)<br>32 kHz to 2.1 MHz (0ws) | Range 3                       |

<sup>2.</sup> Should be USB compliant from I/O voltage standpoint, the minimum  $\rm V_{\rm DD}$  is 3.0 V.

### 3.4 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

- **Safe clock switching**: clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management**: to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- System clock source: three different clock sources can be used to drive the master clock SYSCLK:

- 1-24 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz).

When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

- Auxiliary clock source: two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog.

The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

- RTC and LCD clock sources: the LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

- **USB clock source:** the embedded PLL has a dedicated 48 MHz clock output to supply the USB interface.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 2 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

- Clock-out capability (MCO: microcontroller clock output): it outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

### 3.7 Memories

The STM32L151xD and STM32L152xD devices have the following features:

- 48 Kbytes of embedded RAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 384 Kbytes of embedded Flash program memory

- 12 Kbytes of data EEPROM

- Options bytes

Flash program and data EEPROM are divided into two banks, this enables writing in one bank while running code or reading data in the other bank.

The options bytes are used to write-protect or read-out protect the memory (with 4 Kbytes granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (ARM Cortex-M3 JTAG and serial wire) and boot in RAM selection disabled (JTAG fuse)

The whole non-volatile memory embeds the error correction code (ECC) feature.

### 3.8 FSMC (flexible static memory controller)

The FSMC supports the following modes: SRAM, PSRAM, NOR/OneNAND Flash.

Functionality overview:

- Up to 26 bit address bus

- Up to 16-bit data bus

- Write FIFO

- Burst mode

- Code execution from external memory

- Four chip select signals

- Up to 32 MHz external access

# 3.9 DMA (direct memory access)

The flexible 12-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

5/

from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode. See *Table 69: Temperature sensor calibration values*.

### 3.11.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (when no external voltage, VREF+, is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode. See *Table 15: Embedded internal reference voltage calibration values*.

### 3.12 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in non-inverting configuration.

This dual digital Interface supports the following features:

- Two DAC converters: one for each output channel

- 8-bit or 12-bit monotonic output

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channels, independent or simultaneous conversions

- DMA capability for each channel (including the underrun interrupt)

- External triggers for conversion

- Input reference voltage V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32L151xD and STM32L152xD devices. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

# 3.13 Operational amplifier

The STM32L151xD and STM32L152xD devices embed three operational amplifiers with external or internal follower routing capability (or even amplifier and filter capability with external components). When one operational amplifier is selected, one external ADC channel is used to enable output measurement.

577

Figure 6. STM32L15xRD LQFP64 pinout

1. This figure shows the package top view.

57/

# 747

### **Alternate functions**

### Table 9. Alternate function input/output

|           |        |                    |          |                |        | Digital alte | ernate fui          | nction numbe | ər      |          |               |          |              |

|-----------|--------|--------------------|----------|----------------|--------|--------------|---------------------|--------------|---------|----------|---------------|----------|--------------|

|           | AFIO0  | AFIO1              | AFIO2    | AFIO3          | AFIO4  | AFIO5        | AFIO6               | AFIO7        | AFIO8 . | . AFIO11 | AFIO12 .      | AFIO14   | AFIO15       |

| Port name |        | Alternate function |          |                |        |              |                     |              |         |          |               |          |              |

|           | SYSTEM | TIM2               | TIM3/4/5 | TIM9/<br>10/11 | I2C1/2 | SPI1/2       | SPI3                | USART1/2/3   | UART4/5 | LCD      | FSMC/<br>SDIO | CPRI     | SYSTEM       |

| воото     | воото  | -                  | -        | -              | -      | -            | -                   | -            | -       | -        | -             | -        | EVENT<br>OUT |

| NRST      | NRST   | -                  | -        | -              | -      | -            | -                   | -            | -       | -        | -             | -        | -            |

| PA0-WKUP1 | -      | TIM2_CH1_ETR       | TIM5_CH1 | -              | -      | -            | -                   | USART2_CTS   | -       | -        | -             | TIMx_IC1 | EVENT<br>OUT |

| PA1       | -      | TIM2_CH2           | TIM5_CH2 | -              | -      | -            | -                   | USART2_RTS   | -       | SEG0     | -             | TIMx_IC2 | EVENT<br>OUT |

| PA2       | -      | TIM2_CH3           | TIM5_CH3 | TIM9_CH1       | -      | -            | -                   | USART2_TX    | -       | SEG1     | -             | TIMx_IC3 | EVENT<br>OUT |

| PA3       | -      | TIM2_CH4           | TIM5_CH4 | TIM9_CH2       | -      | -            | -                   | USART2_RX    | -       | SEG2     | -             | TIMx_IC4 | EVENT<br>OUT |

| PA4       | -      | -                  | -        | -              | -      | SPI1_NSS     | SPI3_NSS<br>I2S3_WS | USART2_CK    | -       | -        | -             | TIMx_IC1 | EVENT<br>OUT |

| PA5       | -      | TIM2_CH1_ETR       | -        | -,             | -      | SPI1_SCK     | -                   | -            | -       | -        | -             | TIMx_IC2 | EVENT<br>OUT |

| PA6       | -      | -                  | TIM3_CH1 | TIM10_CH1      | -      | SPI1_MISO    | -                   | -            | -       | SEG3     | -             | TIMx_IC3 | EVENT<br>OUT |

| PA7       | -      | -                  | TIM3_CH2 | TIM11_CH1      | -      | SPI1_MOSI    | -                   | -            | -       | SEG4     | -             | TIMx_IC4 | EVENT<br>OUT |

| PA8       | мсо    | -                  | -        | -              | -      | -            | -                   | USART1_CK    | -       | СОМО     | -             | TIMx_IC1 | EVENT<br>OUT |

| PA9       | -      | -                  | -        | -              | -      | -            | -                   | USART1_TX    | -       | COM1     | -             | TIMx_IC2 | EVENT<br>OUT |

| PA10      | -      | -                  | -        | -              | -      | -            | -                   | USART1_RX    | -       | COM2     | -             | TIMx_IC3 | EVENT<br>OUT |

| PA11      | -      | -                  | -        | -              | -      | SPI1_MISO    |                     | USART1_CTS   | -       | -        | -             | TIMx_IC4 | EVENT<br>OUT |

### 6.1.6 Power supply scheme

Standby-power circuitry (LSE,RTC,Wake-up logic, RTC backup registers) OUT Ю GP I/Os Logic Kernel logic (CPU, Digital & Memories) Regulator N × 100 nF ·  $1 \times 4.7 \, \mu F$  $V_{\text{DDA}}$ V<sub>REF</sub> Analog: OSC,PLL,COMP, 100 nF + 1 μF ADC/ 100 nF  $V_{REF}$ DAC  $V_{\text{SSA}}$ N - number of  $V_{\text{DD}}\!/V_{\text{SS}}$  pairs MS32461V3

Figure 11. Power supply scheme

### 6.3.3 Embedded internal reference voltage

The parameters given in *Table 16* are based on characterization results, unless otherwise specified.

Table 15. Embedded internal reference voltage calibration values

| Calibration value name | Description                                                                   | Memory address            |

|------------------------|-------------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at temperature of 30 °C ±5 °C V <sub>DDA</sub> = 3 V ±10 mV | 0x1FF8 00F8 - 0x1FF8 00F9 |

Table 16. Embedded internal reference voltage

| Symbol                                  | Parameter                                                                                 | Conditions                                                                        | Min   | Тур   | Max   | Unit               |

|-----------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------|-------|-------|--------------------|

| V <sub>REFINT out</sub> (1)             | Internal reference voltage                                                                | – 40 °C < T <sub>J</sub> < +110 °C                                                | 1.202 | 1.224 | 1.242 | V                  |

| I <sub>REFINT</sub>                     | Internal reference current consumption                                                    | -                                                                                 | -     | 1.4   | 2.3   | μΑ                 |

| T <sub>VREFINT</sub>                    | Internal reference startup time                                                           | -                                                                                 | -     | 2     | 3     | ms                 |

| V <sub>VREF_MEAS</sub>                  | V <sub>DDA</sub> and V <sub>REF+</sub> voltage during V <sub>REFINT</sub> factory measure | -                                                                                 | 2.99  | 3     | 3.01  | V                  |

| A <sub>VREF_MEAS</sub>                  | Accuracy of factory-measured V <sub>REF</sub> value <sup>(2)</sup>                        | Including uncertainties due to ADC and V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | ı     | ±5    | mV                 |

| T <sub>Coeff</sub> <sup>(3)</sup>       | Temperature coefficient                                                                   | -40 °C < T <sub>J</sub> < +110 °C                                                 | -     | 25    | 100   | ppm/°              |

| A <sub>Coeff</sub> <sup>(3)</sup>       | Long-term stability                                                                       | 1000 hours, T= 25 °C                                                              | -     | -     | 1000  | ppm                |

| V <sub>DDCoeff</sub> <sup>(3)</sup>     | Voltage coefficient                                                                       | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                  | -     | -     | 2000  | ppm/V              |

| T <sub>S_vrefint</sub> <sup>(3)</sup>   | ADC sampling time when reading the internal reference voltage                             | -                                                                                 | 4     | -     | -     | μs                 |

| T <sub>ADC_BUF</sub> <sup>(3) (4)</sup> | Startup time of reference voltage buffer for ADC                                          | -                                                                                 | -     | -     | 10    | μs                 |

| I <sub>BUF_ADC</sub> <sup>(3)</sup>     | Consumption of reference voltage buffer for ADC                                           | -                                                                                 | -     | 13.5  | 25    | μA                 |

| I <sub>VREF_OUT</sub> (3)               | VREF_OUT output current (5)                                                               | -                                                                                 | -     | -     | 1     | μA                 |

| C <sub>VREF_OUT</sub> <sup>(3)</sup>    | VREF_OUT output load                                                                      | -                                                                                 | -     | -     | 50    | pF                 |

| I <sub>LPBUF</sub> <sup>(3)</sup>       | Consumption of reference voltage buffer for VREF_OUT and COMP                             | -                                                                                 | -     | 730   | 1200  | nA                 |

| V <sub>REFINT_DIV1</sub> (3)            | 1/4 reference voltage                                                                     | -                                                                                 | 24    | 25    | 26    | %                  |

| V <sub>REFINT_DIV2</sub> (3)            | 1/2 reference voltage                                                                     | -                                                                                 | 49    | 50    | 51    | V <sub>REFIN</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(3)</sup> | 3/4 reference voltage                                                                     | -                                                                                 | 74    | 75    | 76    | Т                  |

<sup>1.</sup> Guaranteed by test in production.

<sup>4.</sup> Shortest sampling time can be determined in the application by multiple iterations.

<sup>2.</sup> The internal  $V_{\mathsf{REF}}$  value is individually measured in production and stored in dedicated EEPROM bytes.

<sup>3.</sup> Guaranteed by characterization results.

Table 44. Synchronous non-multiplexed PSRAM write timings<sup>(1)</sup> (continued)

| Symbol                       | Parameter                                  | Min | Max | Unit |

|------------------------------|--------------------------------------------|-----|-----|------|

| t <sub>d(CLKL-NWEH)</sub>    | FSMC_CLK low to FSMC_NWE high              | 5   | -   | ns   |

| t <sub>d(CLKL-DATA)</sub>    | FSMC_D[15:0] valid data after FSMC_CLK low | -   | 7   | ns   |

| t <sub>d(CLKL-NBLH)</sub>    | FSMC_CLK low to FSMC_NBL high              | 3   | -   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high      | 6   | -   | ns   |

| t <sub>h(CLKH-NWAITV)</sub>  | FSMC_NWAIT valid after FSMC_CLK high       | 0   | -   | ns   |

<sup>1.</sup> C<sub>L</sub> = 30 pF.

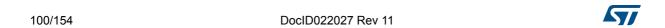

#### **USB** characteristics

The USB interface is USB-IF certified (full speed).

Table 58. USB startup time

| Symbol                              | Parameter                    | Max | Unit |

|-------------------------------------|------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1   | μs   |

<sup>1.</sup> Guaranteed by design.

Table 59. USB DC electrical characteristics

| Symbol                         | Parameter                       | Conditions                               | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |  |  |  |

|--------------------------------|---------------------------------|------------------------------------------|---------------------|---------------------|------|--|--|--|

| Input leve                     | Input levels                    |                                          |                     |                     |      |  |  |  |

| V <sub>DD</sub>                | USB operating voltage           | -                                        | 3.0                 | 3.6                 | V    |  |  |  |

| V <sub>DI</sub> <sup>(2)</sup> | Differential input sensitivity  | I(USB_DP, USB_DM)                        | 0.2                 | -                   |      |  |  |  |

| V <sub>CM</sub> <sup>(2)</sup> | Differential common mode range  | Includes V <sub>DI</sub> range           | 0.8                 | 2.5                 | V    |  |  |  |

| V <sub>SE</sub> <sup>(2)</sup> | Single ended receiver threshold | -                                        | 1.3                 | 2.0                 |      |  |  |  |

| Output lev                     | vels                            |                                          |                     |                     |      |  |  |  |

| V <sub>OL</sub> <sup>(3)</sup> | Static output level low         | $R_L$ of 1.5 k $\Omega$ to 3.6 $V^{(4)}$ | -                   | 0.3                 | V    |  |  |  |

| V <sub>OH</sub> <sup>(3)</sup> | Static output level high        | $R_L$ of 15 k $\Omega$ to $V_{SS}^{(4)}$ | 2.8                 | 3.6                 | ]    |  |  |  |

- 1. All the voltages are measured from the local ground potential.

- 2. Guaranteed by characterization results.

- 3. Guaranteed by test in production.

- 4.  $R_L$  is the load connected on the USB drivers.

Figure 32. USB timings: definition of data signal rise and fall time

Table 60. USB: full speed electrical characteristics

| Driver characteristics <sup>(1)</sup> |                                         |                        |   |    |    |  |

|---------------------------------------|-----------------------------------------|------------------------|---|----|----|--|

| Symbol                                | Symbol Parameter Conditions Min Max Uni |                        |   |    |    |  |

| t <sub>r</sub>                        | Rise time <sup>(2)</sup>                | C <sub>L</sub> = 50 pF | 4 | 20 | ns |  |

| t <sub>f</sub>                        | Fall Time <sup>(2)</sup>                | C <sub>L</sub> = 50 pF | 4 | 20 | ns |  |

### **6.3.22** Temperature sensor characteristics

Table 69. Temperature sensor calibration values

| Calibration value name | Description                                                                           | Memory address            |

|------------------------|---------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at temperature of 30 °C ±5 °C V <sub>DDA</sub> = 3 V ±10 mV  | 0x1FF8 00FA - 0x1FF8 00FB |

| TS_CAL2                | TS ADC raw data acquired at temperature of 110 °C ±5 °C V <sub>DDA</sub> = 3 V ±10 mV | 0x1FF8 00FE - 0x1FF8 00FF |

Table 70. Temperature sensor characteristics

| Symbol                             | Parameter                                      | Min  | Тур   | Max       | Unit  |

|------------------------------------|------------------------------------------------|------|-------|-----------|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature  | -    | ±1    | <u>+2</u> | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                  | 1.48 | 1.61  | 1.75      | mV/°C |

| V <sub>110</sub>                   | Voltage at 110°C ±5°C <sup>(2)</sup>           | 612  | 626.8 | 641.5     | mV    |

| I <sub>DDA(TEMP)</sub> (3)         | Current consumption                            | -    | 3.4   | 6         | μΑ    |

| t <sub>START</sub> (3)             | Startup time                                   | -    | -     | 10        |       |

| T <sub>S_temp</sub> <sup>(3)</sup> | ADC sampling time when reading the temperature | 4    | -     | -         | μs    |

- 1. Guaranteed by characterization results.

- 2. Measured at  $V_{DD}$  = 3 V ±10 mV. V110 ADC conversion result is stored in the TS\_CAL2 byte.

- 3. Guaranteed by design.

### 6.3.23 Comparator

**Table 71. Comparator 1 characteristics**

| Symbol                   | Parameter                                                      | Conditions                                                                                             | Min <sup>(1)</sup> | Тур    | Max <sup>(1)</sup> | Unit      |

|--------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------|--------|--------------------|-----------|

| $V_{DDA}$                | Analog supply voltage                                          | -                                                                                                      | 1.65               |        | 3.6                | V         |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                        | -                                                                                                      | -                  | 400    | -                  | kΩ        |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                         | -                                                                                                      | -                  | 10     | -                  | K22       |

| V <sub>IN</sub>          | Comparator 1 input voltage range                               | -                                                                                                      | 0.6                | -      | $V_{DDA}$          | V         |

| t <sub>START</sub>       | Comparator startup time                                        | -                                                                                                      | -                  | 7      | 10                 |           |

| td                       | Propagation delay <sup>(2)</sup>                               | -                                                                                                      | -                  | - 3 10 |                    | μs        |

| Voffset                  | Comparator offset                                              | -                                                                                                      | -                  | ±3     | ±10                | mV        |

| d <sub>Voffset</sub> /dt | Comparator offset variation in worst voltage stress conditions | $V_{DDA} = 3.6 \text{ V}$ $V_{IN+} = 0 \text{ V}$ $V_{IN-} = V_{REFINT}$ $T_A = 25 ^{\circ} \text{ C}$ | 0                  | 1.5    | 10                 | mV/1000 h |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                             | -                                                                                                      | -                  | 160    | 260                | nA        |

Table 75. LQPF100, 14 x 14 mm, 100-pin low-profile quad flat package mechanical data (continued)

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

|        | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| E3     | -     | 12.000      | -     | -      | 0.4724                | -      |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |

| L      | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |

| L1     | -     | 1.000       | -     | -      | 0.0394                | -      |

| k      | 0.0°  | 3.5°        | 7.0°  | 0.0°   | 3.5°                  | 7.0°   |

| ccc    | -     | -           | 0.080 | -      | -                     | 0.0031 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 44. LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package recommended footprint

1. Dimensions are in millimeters.

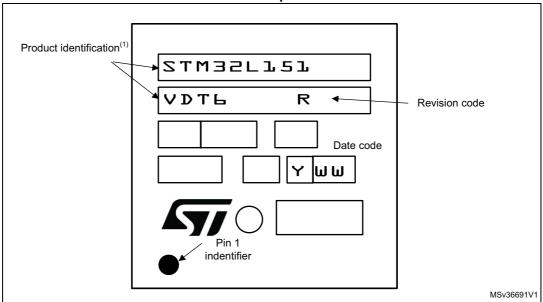

### Marking of engineering samples

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 45. LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package top view example

<sup>1.</sup> Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity

Table 82. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                    |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 3        | Added WLCSP64 package.  Section 3: Functional overview: changed '128 kHz' to '131 kHz' in section "Low power run mode".                                                                                                                                                                    |

|             |          | Section 3.17.1: General-purpose timers (TIM2, TIM3, TIM4, TIM5, TIM9, TIM10 and TIM11): changed 'six' to 'seven' synchronizable general-purpose timers.                                                                                                                                    |

| 18-Apr-2012 |          | Table 14: STM32L15xxD pin definitions on page 52: updated name of reference manual in footnote 5.                                                                                                                                                                                          |

|             |          | I2C updated: footnote 3. from Table 58                                                                                                                                                                                                                                                     |

|             |          | Note about I2C clock updated: footnote 2. from <i>Table 58</i> modified.  Note [non-robust] updated: footnote 2. from <i>Table 68</i> modified.  GPIOs high current capability updated: <i>Section 3.6: GPIOs (general-purpose inputs/outputs)</i> 'except for analog inputs' was removed. |

|             |          | Changed maximum number of touch sensing channels to 34, and updated <i>Table 4: Ultra-low-power STM32L15xxD device features and peripheral counts</i> .                                                                                                                                    |

|             |          | Updated Section 3.10: ADC (analog-to-digital converter) to add Section 3.10.1: Temperature sensor and Section 3.10.2: Internal voltage reference (VREFINT).                                                                                                                                |

|             |          | Removed caution note below Figure 8: Power supply scheme.                                                                                                                                                                                                                                  |

|             |          | Added note below Table 4: STM32L15xQD STM32L162QD UFBGA132 ballout.                                                                                                                                                                                                                        |

|             |          | Modified <i>Table 8: STM32L15xRDSTM32L162RD WLCSP64 ballout</i> to match top view.                                                                                                                                                                                                         |

| 15-Jun-2012 | 2012 4   | Changed FSMC_LBAR into FSMC_NADV, and I2C1_SMBAI into I2C1_SMBA in <i>Table 14: STM32L15xxD pin definitions</i> .                                                                                                                                                                          |

|             |          | Modified PB10/11/12 for AFIO4 ction, and replaced LBAR by NADV for AFIO12 in <i>Table 19: ction input/output</i> .                                                                                                                                                                         |

|             |          | Updated <i>Table 22: Typical and maximum current consumptions in Stop mode</i> and added <i>Note 6.</i> Updated <i>Table 23: Typical and maximum current consumptions in Standby mode.</i> Updated t <sub>WUSTOP</sub> in <i>Table :</i> .                                                 |

|             |          | Updated Table 27: Peripheral current consumption.                                                                                                                                                                                                                                          |

|             |          | Updated <i>Table 60: SPI characteristics</i> , added <i>Note 1</i> and <i>Note 3</i> , and applied <i>Note 2</i> to $t_{r(SCK)}$ , $t_{f(SCK)}$ , $t_{w(SCKH)}$ , $t_{w(SCKL)}$ , $t_{su(MI)}$ , $t_{su(SI)}$ , $t_{h(MI)}$ , and $t_{h(SI)}$ .                                            |

|             |          | Updated I <sub>DD</sub> maximum value in <i>Table 38: Flash memory and data EEPROM characteristics</i> .                                                                                                                                                                                   |

Table 82. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25-Oct-2012 | 5        | Updated Features Updated Figure 1: Ultra-low-power STM32L162xC block diagram Added Table 4: Functionalities depending on the working mode (from Run/active down to standby), and Table 3: ange depending on dynamic voltage scaling Updated Figure 3: STM32L162VC LQFP100 pinout Updated Table 14: STM32L15xxD pin definitions Added Note 2 in Table 15: Embedded reset and power control block characteristics Replaced TBD values in Table 30: Low-speed external user clock characteristics, Table 38: Flash memory and data EEPROM characteristics and Table 55: I/O AC characteristics Added Table 61: I2S characteristics, Figure 29: I2S slave timing diagram (Philips protocol)(1) and Figure 30: I2S master timing diagram (Philips protocol)(1) Added Table 62: SDIO characteristics Added Figure 31: SDIO timings Updated Section 6.3.9: FSMC characteristics Updated Table 72: Temperature sensor characteristics Added Figure 40: Thermal resistance |

| 01-Feb-2013 | 6        | Removed AHB1/AHB2 and corrected typo on APB1/APB2 in Figure 1: Ultra-low-power STM32L162xC block diagram  Updated "OP amp" line in Table 4: Functionalities depending on the working mode (from Run/active down to standby)  Added IWDG and WWDG rows in Table 4: Functionalities depending on the working mode (from Run/active down to standby)  Added OneNAND support in Section 3.8: FSMC (flexible static memory controller)  The comment "HSE = 16 MHz(2) (PLL ON for fHCLK above 16 MHz)" replaced by "fHSE = fHCLK up to 16 MHz included, fHSE = fHCLK/2 above 16 MHz (PLL ON)(2)" in table Table 19: Current consumption in Sleep mode  Updated Stop mode current to 1.5 µA in Ultra low power platform  Replaced BGA132 by UFBGA132 in Table 4: Ultra-low-power STM32L15xxD device features and peripheral counts  Replaced BGA132 by UFBGA132 in Figure 4: STM32L15xQD STM32L162QD UFBGA132 ballout  Updated entire Section 7: Package characteristics |