#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 109                                                                          |

| Program Memory Size        | 384KB (384K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 12K x 8                                                                      |

| RAM Size                   | 48K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 40x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

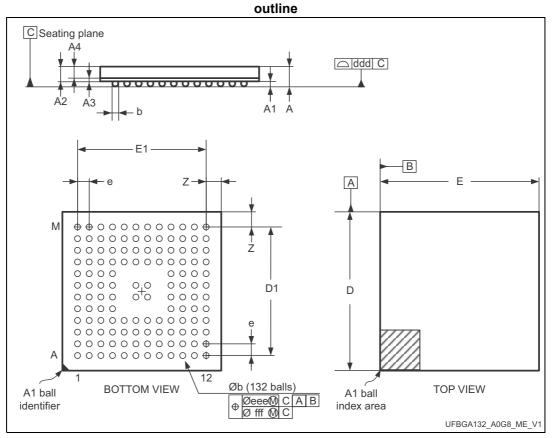

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 132-UFBGA                                                                    |

| Supplier Device Package    | 132-UFBGA (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l152qdh6        |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

• **Stop** mode without RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, LSE and HSE crystal oscillators are disabled. The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 8  $\mu$ s. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB wakeup.

• **Standby** mode with RTC

Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI RC and HSE crystal oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

• Standby mode without RTC

Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

|                                                                    | Functionalities depending on the operating power supply rar |                |                                   |                            |  |  |

|--------------------------------------------------------------------|-------------------------------------------------------------|----------------|-----------------------------------|----------------------------|--|--|

| Operating power supply range                                       | DAC and ADC<br>operation USB                                |                | Dynamic voltage<br>scaling range  | I/O operation              |  |  |

| V <sub>DD</sub> = V <sub>DDA</sub> = 1.65 to 1.71 V                | Not functional                                              | Not functional | Range 2 or<br>Range 3             | Degraded speed performance |  |  |

| $V_{DD} = V_{DDA} = 1.71 \text{ to } 1.8 \text{ V}^{(1)}$          | Not functional                                              | Not functional | Range 1, Range 2<br>or Range 3    | Degraded speed performance |  |  |

| $V_{DD}=V_{DDA}=$ 1.8 to 2.0 V <sup>(1)</sup> Conversion to 500 Ks |                                                             | Not functional | Range 1, Range 2<br>or<br>Range 3 | Degraded speed performance |  |  |

#### Table 3. Functionalities depending on the operating power supply range

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, SDIO, general-purpose timers, DAC and ADC.

# 3.10 LCD (liquid crystal display)

The LCD drives up to 8 common terminals and 44 segment terminals to drive up to 320 pixels.

- Internal step-up converter to guarantee functionality and contrast control irrespective of V<sub>DD</sub>. This converter can be deactivated, in which case the V<sub>LCD</sub> pin is used to provide the voltage to the LCD

- Supports static, 1/2, 1/3, 1/4 and 1/8 duty

- Supports static, 1/2, 1/3 and 1/4 bias

- Phase inversion to reduce power consumption and EMI

- Up to 8 pixels can be programmed to blink

- Unneeded segments and common pins can be used as general I/O pins

- LCD RAM can be updated at any time owing to a double-buffer

- The LCD controller can operate in Stop mode

# 3.11 ADC (analog-to-digital converter)

A 12-bit analog-to-digital converters is embedded into STM32L151xD and STM32L152xD devices with up to 40 external channels, performing conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs with up to 28 external channels in a group.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all scanned channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start triggers, to allow the application to synchronize A/D conversions and timers. An injection mode allows high priority conversions to be done by interrupting a scan mode which runs in as a background task.

The ADC includes a specific low-power mode. The converter is able to operate at maximum speed even if the CPU is operating at a very low frequency and has an auto-shutdown function. The ADC's runtime and analog front-end current consumption are thus minimized whatever the MCU operating mode.

#### 3.11.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\text{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies

DocID022027 Rev 11

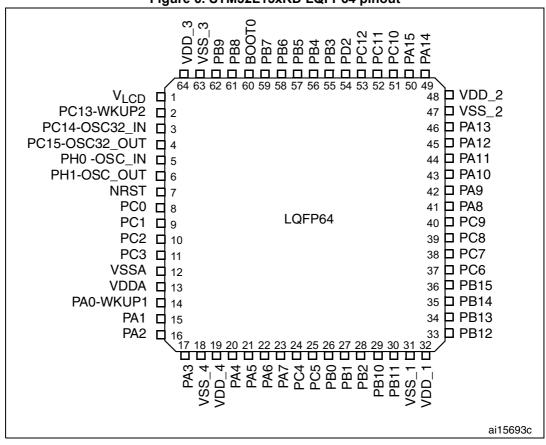

Figure 6. STM32L15xRD LQFP64 pinout

1. This figure shows the package top view.

#### STM32L151xD STM32L152xD

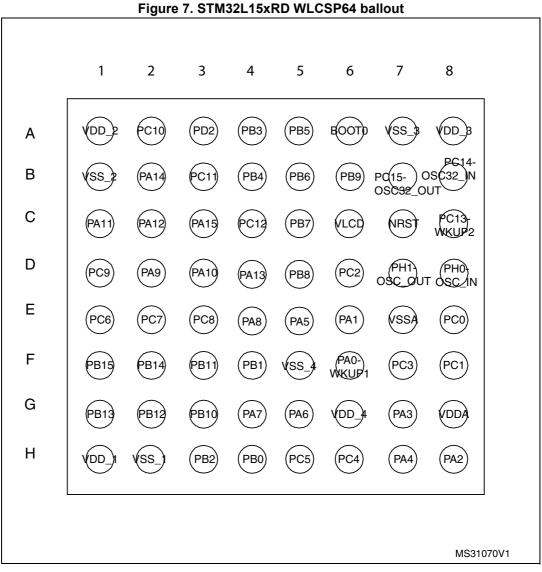

1. This figure shows the package top view.

#### Table 7. Legend/abbreviations used in the pinout table

| Name          | Abbreviation | Definition                                                                                                                            |  |  |  |  |

|---------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin name      |              | Inless otherwise specified in brackets below the pin name, the pin function luring and after reset is the same as the actual pin name |  |  |  |  |

|               | S            | Supply pin                                                                                                                            |  |  |  |  |

| Pin type      | I            | Input only pin                                                                                                                        |  |  |  |  |

|               | I/O          | Input / output pin                                                                                                                    |  |  |  |  |

|               | FT           | 5 V tolerant I/O                                                                                                                      |  |  |  |  |

| I/O structure | TC           | Standard 3.3 V I/O                                                                                                                    |  |  |  |  |

| I/O structure | В            | Dedicated BOOT0 pin                                                                                                                   |  |  |  |  |

|               | RST          | Bidirectional reset pin with embedded weak pull-up resistor                                                                           |  |  |  |  |

|           |        |          |          |                | ſ         | Digital alto         | ernate fui | nction numbe | ər      |        |               |          |              |

|-----------|--------|----------|----------|----------------|-----------|----------------------|------------|--------------|---------|--------|---------------|----------|--------------|

|           | AFIO0  | AFIO1    | AFIO2    | AFIO3          | AFIO4     | AFIO5                | AFIO6      | AFIO7        | AFIO8   | AFIO11 | AFIO12        | AFIO14   | AFIO15       |

| Port name |        |          | 1        | 1              |           | Alt                  | ternate fu | Inction      | L L     | 1      | J – I         | l        |              |

|           | SYSTEM | TIM2     | TIM3/4/5 | TIM9/<br>10/11 | I2C1/2    | SPI1/2               | SPI3       | USART1/2/3   | UART4/5 | LCD    | FSMC/<br>SDIO | CPRI     | SYSTEM       |

| PB11      | -      | TIM2_CH4 | -        | -              | I2C2_SDA  | -                    | -          | USART3_RX    | -       | SEG11  | -             | -        | EVENT<br>OUT |

| PB12      | -      | -        | -        | TIM10_CH1      | I2C2_SMBA | SPI2_NSS<br>I2S2_WS  | -          | USART3_CK    | -       | SEG12  | -             | -        | EVENT<br>OUT |

| PB13      | -      | -        | -        | TIM9_CH1       | -         | SPI2_SCK<br>I2S2_CK  | -          | USART3_CTS   | -       | SEG13  | -             | -        | EVENT<br>OUT |

| PB14      | -      | -        | -        | TIM9_CH2       | -         | SPI2_MISO            | -          | USART3_RTS   | -       | SEG14  | -             | -        | EVENT<br>OUT |

| PB15      | -      | -        | -        | TIM11_CH1      | -         | SPI2_MOSI<br>I2S2_SD | -          | -            | -       | SEG15  | -             | -        | EVENT<br>OUT |

| PC0       | -      | -        | -        | -              | -         |                      | -          | -            | -       | SEG18  | -             | TIMx_IC1 | EVENT<br>OUT |

| PC1       | -      | -        | -        | -              | -         | -                    | -          | -            | -       | SEG19  | -             | TIMx_IC2 | EVENT<br>OUT |

| PC2       | -      | -        | -        | -              | -         | -                    | -          | -            | -       | SEG20  | -             | TIMx_IC3 | EVENT<br>OUT |

| PC3       | -      | -        | -        | -              | -         | -                    | -          | -            | -       | SEG21  | -             | TIMx_IC4 | EVENT<br>OUT |

| PC4       | -      | -        | -        | -              | -         | -                    | -          | -            | -       | SEG22  | -             | TIMx_IC1 | EVENT<br>OUT |

| PC5       | -      | -        | -        | -              | -         | -                    | -          | -            | -       | SEG23  | -             | TIMx_IC2 | EVENT<br>OUT |

| PC6       | -      | -        | TIM3_CH1 | -              | -         | I2S2_MCK             | -          | -            | -       | SEG24  | SDIO_D6       | TIMx_IC3 | EVENT<br>OUT |

| PC7       | -      | -        | TIM3_CH2 | -              | -         | -                    | I2S3_MCK   | -            | -       | SEG25  | SDIO_D7       | TIMx_IC4 | EVENT<br>OUT |

| PC8       | -      | -        | ТІМ3_СНЗ | -              | -         | -                    | -          | -            | -       | SEG26  | SDIO_D0       | TIMx_IC1 | EVENT<br>OUT |

| PC9       | -      | -        | TIM3_CH4 | -              | -         | -                    | -          | -            | -       | SEG27  | SDIO_D1       | TIMx_IC2 | EVENT<br>OUT |

# 6 Electrical characteristics

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.6 V (for the 1.65 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

### 6.1.4 Loading capacitor

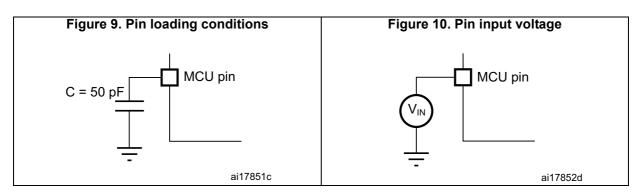

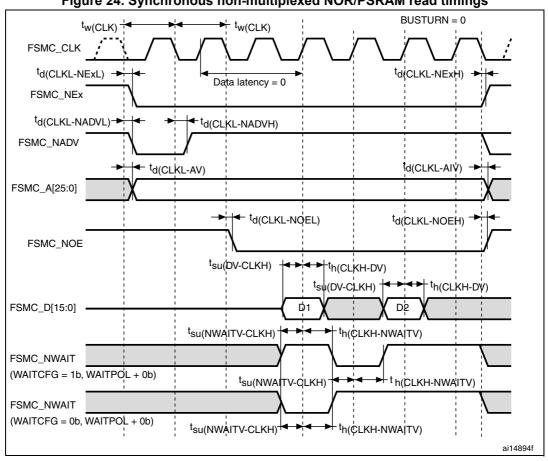

The loading conditions used for pin parameter measurement are shown in *Figure 9*.

### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 10*.

| Symbol                 | Parameter                          | Conditior                                                                                                                                     | IS                                    | f <sub>HCLK</sub> | Тур  | Max<br>(1) | Unit |

|------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------|------|------------|------|

|                        |                                    |                                                                                                                                               | Range3,                               | 1                 | 58   | 220        |      |

|                        |                                    |                                                                                                                                               | Vcore=1.2 V                           | 2                 | 96   | 300        |      |

|                        |                                    |                                                                                                                                               | VOS[1:0]=11                           | 4                 | 170  | 380        |      |

|                        |                                    | f <sub>HSE</sub> = f <sub>HCLK</sub> up to 16 MHz,                                                                                            | Range2,                               | 4                 | 210  | 500        |      |

|                        |                                    | included f <sub>HSE</sub> = f <sub>HCLK</sub> /2                                                                                              | Vcore=1.5 V                           | 8                 | 400  | 700        |      |

|                        |                                    | above 16 MHz (PLL ON) <sup>(2)</sup>                                                                                                          | VOS[1:0]=10                           | 16                | 810  | 1100       |      |

|                        | Supply surrent in                  |                                                                                                                                               | Range1,                               | 8                 | 485  | 800        |      |

|                        | Supply current in Sleep mode, code |                                                                                                                                               | Vcore=1.8 V                           | 16                | 955  | 1250       |      |

|                        | executed from<br>RAM, Flash        |                                                                                                                                               | VOS[1:0]=01                           | 32                | 2100 | 2700       |      |

| s                      | switched OFF                       | HSI clock source (16 MHz)                                                                                                                     | Range2,<br>Vcore=1.5 V<br>VOS[1:0]=10 | 16                | 835  | 1100       |      |

|                        |                                    |                                                                                                                                               | Range1,<br>Vcore=1.8 V<br>VOS[1:0]=01 | 32                | 2100 | 2700       |      |

|                        |                                    | MSI clock, 65 kHZ                                                                                                                             | Range3,                               | 0.065             | 18.5 | 72         | - μΑ |

|                        |                                    | MSI clock, 524 kHZ                                                                                                                            | Vcore=1.2 V                           | 0.524             | 37   | 92         |      |

|                        |                                    | MSI clock, 4.2 MHZ                                                                                                                            | VOS[1:0]=11                           | 4.2               | 180  | 273        |      |

| I <sub>DD(SLEEP)</sub> |                                    | f <sub>HSE</sub> = f <sub>HCLK</sub> up to 16 MHz,<br>included f <sub>HSE</sub> = f <sub>HCLK</sub> /2<br>above 16MHz (PLL ON) <sup>(2)</sup> | Range3,<br>Vcore=1.2 V<br>VOS[1:0]=11 | 1                 | 75   | 250        |      |

|                        |                                    |                                                                                                                                               |                                       | 2                 | 115  | 300        |      |

|                        | Supply current in                  |                                                                                                                                               |                                       | 4                 | 200  | 380        |      |

|                        |                                    |                                                                                                                                               | Range2,<br>Vcore=1.5 V<br>VOS[1:0]=10 | 4                 | 230  | 500        |      |

|                        |                                    |                                                                                                                                               |                                       | 8                 | 430  | 700        |      |

|                        |                                    |                                                                                                                                               |                                       | 16                | 840  | 1120       |      |

|                        |                                    |                                                                                                                                               | Range1,<br>Vcore=1.8 V                | 8                 | 500  | 800        |      |

|                        |                                    |                                                                                                                                               |                                       | 16                | 980  | 1300       |      |

|                        | Sleep mode, Flash switched ON      |                                                                                                                                               | VOS[1:0]=01                           | 32                | 2100 | 2700       |      |

|                        | SWITCHED ON                        | HSI clock source (16 MHz)                                                                                                                     | Range2,<br>Vcore=1.5 V<br>VOS[1:0]=10 | 16                | 860  | 1160       |      |

|                        |                                    |                                                                                                                                               | Range1,<br>Vcore=1.8 V<br>VOS[1:0]=01 | 32                | 2150 | 2800       |      |

|                        |                                    | MSI clock, 65 kHZ                                                                                                                             | Range3,                               | 0.065             | 33,5 | 90         |      |

|                        |                                    | MSI clock, 524 kHZ                                                                                                                            | Vcore=1.2 V                           | 0.524             | 53   | 110        |      |

|                        |                                    | MSI clock, 4.2 MHZ                                                                                                                            | VOS[1:0]=11                           | 4.2               | 200  | 290        |      |

|  | Table 19 | Current co | nsumption i | n Sleep mode |

|--|----------|------------|-------------|--------------|

|--|----------|------------|-------------|--------------|

1. Guaranteed by characterization results, unless otherwise specified.

#### 2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register)

| Symbol                                                                            | Parameter                                          |                                                   | Conditions                                      |                                                  |                        | Max <sup>(1)</sup> | Unit |  |

|-----------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------|-------------------------------------------------|--------------------------------------------------|------------------------|--------------------|------|--|

|                                                                                   |                                                    |                                                   |                                                 | $T_A$ = -40 °C to 25 °C                          | 11                     | 14                 |      |  |

|                                                                                   |                                                    |                                                   | MSI clock, 65 kHz                               | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz  | T <sub>A</sub> = 85 °C | 26                 | 32   |  |

|                                                                                   |                                                    | All<br>peripherals                                | HOLK                                            | T <sub>A</sub> = 105 °C                          | 53                     | 72                 |      |  |

|                                                                                   |                                                    | OFF, code                                         |                                                 | T <sub>A</sub> =-40 °C to 25 °C                  | 18                     | 21                 |      |  |

|                                                                                   |                                                    | executed<br>from RAM,                             | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz | T <sub>A</sub> = 85 °C                           | 33                     | 40                 |      |  |

| Supply<br>I <sub>DD (LP</sub> current in<br><sub>Run)</sub> Low-power<br>run mode | Flash<br>switched                                  | HOLK COMIL                                        | T <sub>A</sub> = 105 °C                         | 60                                               | 78                     |                    |      |  |

|                                                                                   | OFF, V <sub>DD</sub>                               |                                                   | $T_A$ = -40 °C to 25 °C                         | 36                                               | 41                     |                    |      |  |

|                                                                                   | from 1.65 V<br>to 3.6 V                            | MSI clock, 131 kHz<br>f <sub>HCLK</sub> = 131 kHz | T <sub>A</sub> = 55 °C                          | 39                                               | 44                     |                    |      |  |

|                                                                                   |                                                    |                                                   | T <sub>A</sub> = 85 °C                          | 50                                               | 58                     |                    |      |  |

|                                                                                   |                                                    |                                                   | T <sub>A</sub> = 105 °C                         | 78                                               | 95                     |                    |      |  |

|                                                                                   |                                                    | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz   | $T_A$ = -40 °C to 25 °C                         | 36                                               | 40.5                   |                    |      |  |

|                                                                                   |                                                    |                                                   | T <sub>A</sub> = 85 °C                          | 53                                               | 60                     | μA                 |      |  |

|                                                                                   |                                                    | All<br>peripherals<br>OFF, code<br>executed       | HOLK                                            | T <sub>A</sub> = 105 °C                          | 81                     | 100                | -    |  |

|                                                                                   |                                                    |                                                   | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$          | 44                     | 49                 |      |  |

|                                                                                   |                                                    |                                                   |                                                 | T <sub>A</sub> = 85 °C                           | 61                     | 67                 |      |  |

|                                                                                   |                                                    | from Flash,<br>V <sub>DD</sub> from               | HOLK COMP                                       | T <sub>A</sub> = 105 °C                          | 89                     | 107                |      |  |

|                                                                                   |                                                    | 1.65 V to                                         |                                                 | $T_A = -40 \ ^\circ C \text{ to } 25 \ ^\circ C$ | 64                     | 71                 |      |  |

|                                                                                   |                                                    | 3.6 V                                             | MSI clock, 131 kHz                              | T <sub>A</sub> = 55 °C                           | 68                     | 73                 |      |  |

|                                                                                   |                                                    | f <sub>HCLK</sub> = 131 kHz                       | T <sub>A</sub> = 85 °C                          | 80                                               | 88                     |                    |      |  |

|                                                                                   |                                                    |                                                   |                                                 | T <sub>A</sub> = 105 °C                          | 101                    | 110                |      |  |

| I <sub>DD</sub> max<br>(LP Run)                                                   | Max allowed<br>current in<br>Low-power<br>run mode | V <sub>DD</sub> from<br>1.65 V to<br>3.6 V        | -                                               | -                                                | -                      | 200                |      |  |

| <b>T</b>  | • • •               |               |              |

|-----------|---------------------|---------------|--------------|

| Table 20. | Current consumption | on in Low-pow | ver run mode |

1. Guaranteed by characterization results, unless otherwise specified.

|                                              |                                     |            |             | -   | -                  |      |

|----------------------------------------------|-------------------------------------|------------|-------------|-----|--------------------|------|

| Symbol                                       | Parameter                           | Conditions | Min         | Тур | Мах                | Unit |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage |            | $0.7V_{DD}$ | -   | V <sub>DD</sub>    | V    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage  |            | $V_{SS}$    | -   | $0.3V_{\text{DD}}$ |      |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time             |            | 12          | -   | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time            |            | -           | -   | 20                 | 115  |

| C <sub>in(HSE)</sub>                         | OSC_IN input capacitance            |            | -           | 2.6 | -                  | pF   |

Table 26. High-speed external user clock characteristics<sup>(1)</sup> (continued)

1. Guaranteed by design.

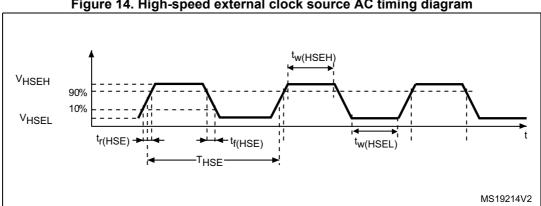

Figure 14. High-speed external clock source AC timing diagram

| Symbol                              | Parameter                                                                                                 | Conditions                                                  | Min | Тур | Мах                                | Unit  |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|------------------------------------|-------|--|

| f <sub>OSC_IN</sub>                 | Oscillator frequency                                                                                      | -                                                           | 1   |     | 24                                 | MHz   |  |

| R <sub>F</sub>                      | Feedback resistor                                                                                         | -                                                           | -   | 200 | -                                  | kΩ    |  |

| С                                   | Recommended load<br>capacitance versus<br>equivalent serial<br>resistance of the crystal<br>$(R_S)^{(3)}$ | R <sub>S</sub> = 30 Ω                                       | -   | 20  | -                                  | pF    |  |

| I <sub>HSE</sub>                    | HSE driving current                                                                                       | $V_{DD}$ = 3.3 V,<br>$V_{IN}$ = $V_{SS}$ with 30 pF<br>load | -   | -   | 3                                  | mA    |  |

| 1                                   | HSE oscillator power                                                                                      | C = 20 pF<br>f <sub>OSC</sub> = 16 MHz                      | -   | -   | 2.5 (startup)<br>0.7 (stabilized)  | ٣٨    |  |

| IDD(HSE)                            | consumption                                                                                               | C = 10 pF<br>f <sub>OSC</sub> = 16 MHz                      | -   | -   | 2.5 (startup)<br>0.46 (stabilized) | mA    |  |

| 9 <sub>m</sub>                      | Oscillator<br>transconductance                                                                            | Startup                                                     | 3.5 | -   | -                                  | mA /V |  |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                                                                              | V <sub>DD</sub> is stabilized                               | -   | 1   | -                                  | ms    |  |

Table 28. HSE oscillator characteristics<sup>(1)(2)</sup>

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by characterization results.

The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 16*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

### 6.3.7 Internal clock source characteristics

The parameters given in *Table 30* are derived from tests performed under the conditions summarized in *Table 13*.

#### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                                               | Conditions                                                           |                   | Тур  | Max              | Unit |

|-------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------|-------------------|------|------------------|------|

| f <sub>HSI</sub>                    | Frequency                                               | V <sub>DD</sub> = 3.0 V                                              |                   | 16   | -                | MHz  |

| TRIM <sup>(1)(2)</sup>              | HSI user-trimmed                                        | Trimming code is not a multiple of 16                                | -                 | ±0.4 | 0.7              | %    |

| TRIM                                |                                                         | Trimming code is a multiple of 16                                    | -                 | -    | ±1.5             | %    |

|                                     |                                                         | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 25 °C                     | -1 <sup>(3)</sup> | -    | 1 <sup>(3)</sup> | %    |

|                                     | Accuracy of the<br>factory-calibrated<br>HSI oscillator | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 0 to 55 °C                | -1.5              | -    | 1.5              | %    |

| ACC <sub>HSI</sub> <sup>(2)</sup>   |                                                         | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 70 °C                              | -2                | -    | 2                | %    |

|                                     |                                                         | $V_{DDA}$ = 3.0 V, $T_{A}$ = -10 to 85 °C                            | -2.5              | -    | 2                | %    |

|                                     |                                                         | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = -10 to 105 °C             | -4                | -    | 2                | %    |

|                                     |                                                         | V <sub>DDA</sub> = 1.65 V to 3.6 V<br>T <sub>A</sub> = -40 to 105 °C | -4                | -    | 3                | %    |

| t <sub>SU(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>startup time                          | -                                                                    | -                 | 3.7  | 6                | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>power consumption                     | -                                                                    | -                 | 100  | 140              | μA   |

| Table 30. HSI oscillator | characteristics |

|--------------------------|-----------------|

|--------------------------|-----------------|

1. The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

2. Guaranteed by characterization results.

3. Guaranteed by test in production.

## Low-speed internal (LSI) RC oscillator

#### Table 31. LSI oscillator characteristics

| Symbol                              | Parameter                                                                | Min | Тур | Мах | Unit |

|-------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                                            | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift $0^{\circ}C \leq T_{A} \leq 105^{\circ}C$ | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                              | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                                         | -   | 400 | 510 | nA   |

1. Guaranteed by test in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design.

| Table 50. Asynchronous non-induplexed SICAMIN SICAMINON write timings |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter                                                             | Min                                                                                                                                                                                                                                                                                                                                                                                  | Мах                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| FSMC_NE low time                                                      | 2*T <sub>HCLK</sub> -3                                                                                                                                                                                                                                                                                                                                                               | 2*T <sub>HCLK</sub> +2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| FSMC_NEx low to FSMC_NWE low                                          | 0.5                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| FSMC_NWE low time                                                     | T <sub>HCLK</sub> - 2                                                                                                                                                                                                                                                                                                                                                                | T <sub>HCLK</sub> + 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| FSMC_NWE high to FSMC_NE high hold time                               | T <sub>HCLK</sub> - 2.5                                                                                                                                                                                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| FSMC_NEx low to FSMC_A valid                                          | -                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Address hold time after FSMC_NWE high                                 | T <sub>HCLK</sub> - 2.5                                                                                                                                                                                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| FSMC_NEx low to FSMC_BL valid                                         | -                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| FSMC_BL hold time after FSMC_NWE high                                 | T <sub>HCLK</sub> - 4                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| FSMC_NEx low to Data valid                                            | -                                                                                                                                                                                                                                                                                                                                                                                    | T <sub>HCLK</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Data hold time after FSMC_NWE high                                    | me after FSMC_NWE high T <sub>HCLK</sub> - 2.5 -                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                                                                       | Parameter         FSMC_NE low time         FSMC_NEx low to FSMC_NWE low         FSMC_NWE low time         FSMC_NWE low time         FSMC_NWE low to FSMC_NE high hold time         FSMC_NEx low to FSMC_A valid         Address hold time after FSMC_NWE high         FSMC_NEx low to FSMC_BL valid         FSMC_BL hold time after FSMC_NWE high         FSMC_NEx low to Data valid | Parameter       Min         FSMC_NE low time       2*T <sub>HCLK</sub> -3         FSMC_NEx low to FSMC_NWE low       0.5         FSMC_NWE low time       T <sub>HCLK</sub> -2         FSMC_NWE low time       T <sub>HCLK</sub> -2.5         FSMC_NWE high to FSMC_NE high hold time       -         Address hold time after FSMC_NWE high       T <sub>HCLK</sub> -2.5         FSMC_NEx low to FSMC_A valid       -         FSMC_NEx low to FSMC_BL valid       -         FSMC_BL hold time after FSMC_NWE high       T <sub>HCLK</sub> -4         FSMC_NEx low to Data valid       - | ParameterMinMaxFSMC_NE low time2*T <sub>HCLK</sub> -32*T <sub>HCLK</sub> +2FSMC_NEx low to FSMC_NWE low0.51FSMC_NWE low timeT <sub>HCLK</sub> -2T <sub>HCLK</sub> +3FSMC_NWE low timeT <sub>HCLK</sub> -2.5-FSMC_NWE high to FSMC_NE high hold timeT <sub>HCLK</sub> -2.5-FSMC_NEx low to FSMC_A valid-0Address hold time after FSMC_NWE highT <sub>HCLK</sub> -2.5-FSMC_NEx low to FSMC_BL valid-0FSMC_BL hold time after FSMC_NWE highT <sub>HCLK</sub> -4-FSMC_NEx low to Data valid-T <sub>HCLK</sub> -4 |  |  |  |

Table 38. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings<sup>(1)</sup>

1. C<sub>L</sub> = 30 pF.

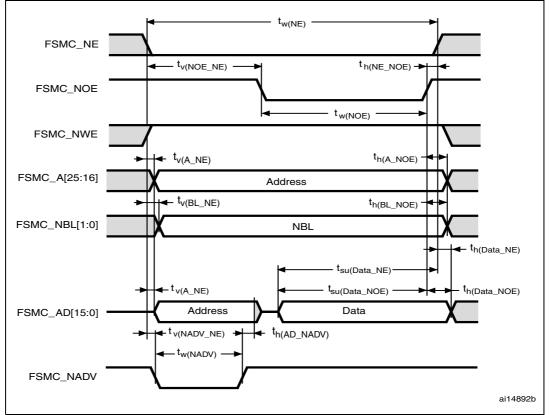

Figure 24. Synchronous non-multiplexed NOR/PSRAM read timings

| Table 43. Synchronous non-multiplexed NOR/PSRAM read timings <sup>(1)</sup> |

|-----------------------------------------------------------------------------|

|-----------------------------------------------------------------------------|

| Symbol                     | Parameter                                       | Min                          | Max                   | Unit |

|----------------------------|-------------------------------------------------|------------------------------|-----------------------|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                                 | 2*T <sub>HCLK</sub> -<br>0.5 | -                     | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x = 02)           | -                            | 0                     | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x = 02)          | 0                            | -                     | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low                   | -                            | 3                     | ns   |

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high                  | 3.5                          | -                     | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x = 1625)        | -                            | 0                     | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x = 1625)      | 0                            | -                     | ns   |

| t <sub>d(CLKL-NOEL)</sub>  | FSMC_CLK low to FSMC_NOE low                    | -                            | T <sub>HCLK</sub> + 1 | ns   |

| t <sub>d(CLKL-NOEH)</sub>  | FSMC_CLK low to FSMC_NOE high                   | 2.5                          | -                     | ns   |

| t <sub>su(DV-CLKH)</sub>   | FSMC_D[15:0] valid data before FSMC_CLK<br>high | 4                            | _                     | ns   |

| t <sub>h(CLKH-DV)</sub>    | FSMC_D[15:0] valid data after FSMC_CLK high     | 4                            | -                     | ns   |

### 6.3.15 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 53*)

Unless otherwise specified, the parameters given in *Table 53* are derived from tests performed under the conditions summarized in *Table 13*.

| Symbol                                | Parameter                                          | Conditions                                                   | Min                 | Тур                               | Max                 | Unit |

|---------------------------------------|----------------------------------------------------|--------------------------------------------------------------|---------------------|-----------------------------------|---------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup>  | NRST input low level voltage                       | -                                                            | -                   | -                                 | 0.3 V <sub>DD</sub> |      |

| V <sub>IH(NRST)</sub> <sup>(1)</sup>  | NRST input high<br>level voltage                   | -                                                            | 0.7 V <sub>DD</sub> | -                                 | -                   | V    |

| V                                     | NRST output low                                    | I <sub>OL</sub> = 2 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V    | -                   | -                                 | 0.4                 | v    |

| V <sub>OL(NRST)</sub> <sup>(1)</sup>  | level voltage                                      | I <sub>OL</sub> = 1.5 mA<br>1.65 V < V <sub>DD</sub> < 2.7 V | -                   | -                                 | 0.4                 |      |

| V <sub>hys(NRST)</sub> <sup>(1)</sup> | NRST Schmitt trigger voltage hysteresis            | -                                                            | -                   | 10%V <sub>DD</sub> <sup>(2)</sup> | -                   | mV   |

| R <sub>PU</sub>                       | Weak pull-up<br>equivalent resistor <sup>(3)</sup> | $V_{IN} = V_{SS}$                                            | 30                  | 45                                | 60                  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>   | NRST input filtered pulse                          | -                                                            | -                   | -                                 | 50                  | ns   |

| V <sub>NF(NRST)</sub> <sup>(3)</sup>  | NRST input not<br>filtered pulse                   | -                                                            | 350                 | -                                 | -                   | ns   |

Table 53. NRST pin characteristics

1. Guaranteed by design.

2. With a minimum of 200 mV.

3. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is around 10%.

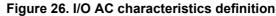

Figure 29. SPI timing diagram - slave mode and CPHA = 0

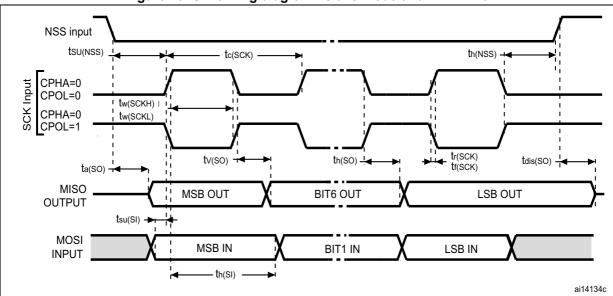

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}.}$

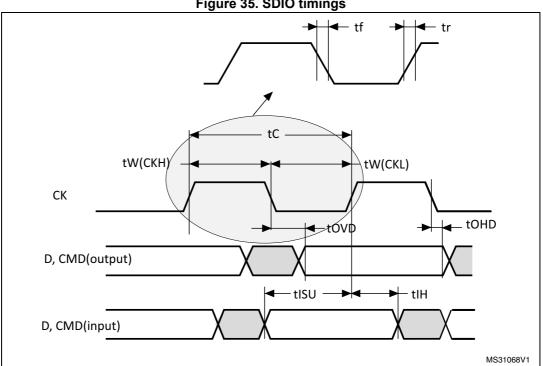

#### 6.3.18 **SDIO characteristics**

| Symbol                                               | Parameter                                                      | Conditions | Min                  | Max | Unit |  |  |  |

|------------------------------------------------------|----------------------------------------------------------------|------------|----------------------|-----|------|--|--|--|

| f <sub>PP</sub>                                      | Clock frequency in data transfer mode                          | 0          | 24                   | MHz |      |  |  |  |

| t <sub>W(CKL)</sub>                                  | Clock low time, f <sub>PP</sub> = 24 MHz                       | CL ≤30 pF  | 20 <sup>(2)</sup>    | -   |      |  |  |  |

| t <sub>W(CKH)</sub>                                  | Clock high time, f <sub>PP</sub> = 24 MHz                      | CL ≤30 pF  | 18 <sup>(2)</sup>    | -   |      |  |  |  |

| t <sub>r</sub>                                       | Clock rise time, $f_{PP}$ = 24 MHz CL $\leq$ 30                |            | -                    | 5   | ns   |  |  |  |

| t <sub>f</sub>                                       | Clock fall time, $f_{PP}$ = 24 MHz CL $\leq$ 30 pF -           |            |                      |     |      |  |  |  |

|                                                      | CMD, D inputs (referenced to CK) in SD default mode            |            |                      |     |      |  |  |  |

|                                                      | -                                                              |            | From 2.8<br>to 3.6 V | -   | -    |  |  |  |

| t <sub>ISU</sub>                                     | Input setup time, f <sub>PP</sub> = 24 MHz                     | CL ≤30 pF  | 2                    | -   | 20   |  |  |  |

| t <sub>IH</sub>                                      | Input hold time, f <sub>PP</sub> = 24 MHz                      | CL ≦30 pF  | 1.6                  | -   | ns   |  |  |  |

| CMD, D outputs (referenced to CK) in SD default mode |                                                                |            |                      |     |      |  |  |  |

| t <sub>OVD</sub>                                     | Output valid default time, $f_{PP}$ = 24 MHzCL $\leq$ 30 pF014 |            |                      |     | ne   |  |  |  |

| t <sub>OHD</sub>                                     | Output hold default time, f <sub>PP</sub> = 24 MHz             | CL ≤30 pF  | 0                    | -   | ns   |  |  |  |

#### Table 62. SDIO characteristics<sup>(1)</sup>

1. Guaranteed by characterization results.

2. Values measured with a threshold level equal to  $V_{\mbox{\scriptsize DD}}/2.$

#### Figure 35. SDIO timings

#### **Electrical characteristics**

| Symbol | Parameter                            | Test conditions                                                                                                                                  | Min <sup>(3)</sup> | Тур | Max <sup>(3)</sup> | Unit |

|--------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

| ET     | Total unadjusted error               |                                                                                                                                                  | -                  | 2   | 4                  |      |

| EO     | Offset error                         | $2.4 \text{ V} \leq \text{V}_{\text{DDA}} \leq 3.6 \text{ V}$                                                                                    | -                  | 1   | 2                  |      |

| EG     | Gain error                           | 2.4 V ≤V <sub>REF+</sub> ≤ 3.6 V<br>f <sub>ADC</sub> = 8 MHz, R <sub>AIN</sub> = 50 Ω                                                            | -                  | 1.5 | 3.5                | LSB  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 °C                                                                                                                            | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                                                                                  | -                  | 1.7 | 3                  |      |

| ENOB   | Effective number of bits             |                                                                                                                                                  | 9.2                | 10  | -                  | bits |

| SINAD  | Signal-to-noise and distortion ratio | 2.4 V ≤V <sub>DDA</sub> ≤ 3.6 V<br>V <sub>DDA</sub> = V <sub>REF+</sub><br>f <sub>ADC</sub> = 16 MHz, R <sub>AIN</sub> = 50 Ω                    | 57.5               | 62  | -                  |      |

| SNR    | Signal-to-noise ratio                | T <sub>A</sub> = -40 to 105 ° C                                                                                                                  | 57.5               | 62  | -                  | dB   |

| THD    | Total harmonic distortion            | F <sub>input</sub> =10kHz                                                                                                                        | -                  | -70 | -65                |      |

| ENOB   | Effective number of bits             |                                                                                                                                                  | 9.2                | 10  | -                  | bits |

| SINAD  | Signal-to-noise and distortion ratio | 1.8 V $\leq$ V <sub>DDA</sub> $\leq$ 2.4 V<br>V <sub>DDA</sub> = V <sub>REF+</sub><br>f <sub>ADC</sub> = 8 MHz or 4 MHz, R <sub>AIN</sub> = 50 Ω | 57.5               | 62  | -                  |      |

| SNR    | Signal-to-noise ratio                | T <sub>A</sub> = -40 to 105 ° C                                                                                                                  | 57.5               | 62  | -                  | dB   |

| THD    | Total harmonic distortion            | - F <sub>input</sub> =10kHz                                                                                                                      | -                  | -70 | -65                |      |

| ET     | Total unadjusted error               |                                                                                                                                                  | -                  | 4   | 6.5                |      |

| EO     | Offset error                         | $2.4 \text{ V} \leq \text{V}_{\text{DDA}} \leq 3.6 \text{ V}$                                                                                    | -                  | 2   | 4                  |      |

| EG     | Gain error                           | 1.8 V ≤V <sub>REF+</sub> ≤ 2.4 V<br>f <sub>ADC</sub> = 4 MHz, R <sub>AIN</sub> = 50 Ω                                                            | -                  | 4   | 6                  | LSB  |