#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | ARM7®                                                                        |

| Core Size                  | 16/32-Bit                                                                    |

| Speed                      | 55MHz                                                                        |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                   |

| Number of I/O              | 62                                                                           |

| Program Memory Size        | 512KB (512K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                                |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-LQFP                                                                     |

| Supplier Device Package    | 100-LQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7xc512b-aur |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- + Fully Static Operation: Up to 55 MHz at 1.65V and 85  $\,$  C Worst Case Conditions

- Available in 100-lead LQFP Green and 100-ball TFBGA Green Packages

# 1. Description

Atmel's AT91SAM7XC512/256/128 is a member of a series of highly integrated Flash microcontrollers based on the 32-bit ARM RISC processor. It features 512/256/128 Kbyte high-speed Flash and 128/64/32 Kbyte SRAM, a large set of peripherals, including an 802.3 Ethernet MAC, a CAN controller, an AES 128 Encryption accelerator and a Triple Data Encryption System. A complete set of system functions minimizes the number of external components.

The embedded Flash memory can be programmed in-system via the JTAG-ICE interface or via a parallel interface on a production programmer prior to mounting. Built-in lock bits and a security bit protect the firmware from accidental overwrite and preserve its confidentiality.

The AT91SAM7XC512/256/128 system controller includes a reset controller capable of managing the power-on sequence of the microcontroller and the complete system. Correct device operation can be monitored by a built-in brownout detector and a watchdog running off an integrated RC oscillator.

By combining the ARM7TDMI processor with on-chip Flash and SRAM, and a wide range of peripheral functions, including USART, SPI, CAN Controller, Ethernet MAC, AES 128 accelerator, TDES, Timer Counter, RTT and Analog-to-Digital Converters on a monolithic chip, the AT91SAM7XC512/256/128 is a powerful device that provides a flexible, cost-effective solution to many embedded control applications requiring secure communication over, for example, Ethernet, CAN wired and Zigbee<sup>™</sup> wireless networks.

# 1.1 Configuration Summary of the AT91SAM7XC512/256/128

The AT91SAM7XC512, AT91SAM7XC256 and AT91SAM7XC128 differ only in memory sizes. Table 1-1 summarizes the configurations of the two devices.

| Device        | Flash      | Flash Organization | SRAM       | AES               | TDES |

|---------------|------------|--------------------|------------|-------------------|------|

| AT91SAM7XC512 | 512K bytes | dual plane         | 128K bytes | 1 AES 256/192/128 | 1    |

| AT91SAM7XC256 | 256K bytes | single plane       | 64K bytes  | 1 AES 128         | 1    |

| AT91SAM7XC128 | 128K bytes | single plane       | 32K bytes  | 1 AES 128         | 1    |

**Table 1-1.**Configuration Summary

# 4.2 100-lead LQFP Pinout

**Table 4-1.**Pinout in 100-lead LQFP Package

| 1  | ADVREF     |   | 26 |   |

|----|------------|---|----|---|

| 2  | GND        |   | 27 |   |

| 3  | AD4        |   | 28 |   |

| 4  | AD5        |   | 29 |   |

| 5  | AD6        |   | 30 |   |

| 6  | AD7        |   | 31 |   |

| 7  | VDDOUT     |   | 32 |   |

| 8  | VDDIN      |   | 33 |   |

| 9  | PB27/AD0   | 1 | 34 |   |

| 10 | PB28/AD1   |   | 35 |   |

| 11 | PB29/AD2   |   | 36 |   |

| 12 | PB30/AD3   |   | 37 |   |

| 13 | PA8/PGMM0  |   | 38 |   |

| 14 | PA9/PGMM1  |   | 39 |   |

| 15 | VDDCORE    |   | 40 |   |

| 16 | GND        |   | 41 |   |

| 17 | VDDIO      |   | 42 |   |

| 18 | PA10/PGMM2 |   | 43 |   |

| 19 | PA11/PGMM3 |   | 44 |   |

| 20 | PA12/PGMD0 |   | 45 |   |

| 21 | PA13/PGMD1 | 1 | 46 |   |

| 22 | PA14/PGMD2 | 1 | 47 |   |

| 23 | PA15/PGMD3 |   | 48 |   |

| 24 | PA16/PGMD4 | 1 | 49 |   |

| 25 | PA17/PGMD5 |   | 50 |   |

|    | •          | • |    | • |

| 26 | PA18/PGMD6  |

|----|-------------|

| 27 | PB9         |

| 28 | PB8         |

| 29 | PB14        |

| 30 | PB13        |

| 31 | PB6         |

| 32 | GND         |

| 33 | VDDIO       |

| 34 | PB5         |

| 35 | PB15        |

| 36 | PB17        |

| 37 | VDDCORE     |

| 38 | PB7         |

| 39 | PB12        |

| 40 | PB0         |

| 41 | PB1         |

| 42 | PB2         |

| 43 | PB3         |

| 44 | PB10        |

| 45 | PB11        |

| 46 | PA19/PGMD7  |

| 47 | PA20/PGMD8  |

| 48 | VDDIO       |

| 49 | PA21/PGMD9  |

| 50 | PA22/PGMD10 |

| 51 | TDI         |

|----|-------------|

| 52 | GND         |

| 53 | PB16        |

| 54 | PB4         |

| 55 | PA23/PGMD11 |

| 56 | PA24/PGMD12 |

| 57 | NRST        |

| 58 | TST         |

| 59 | PA25/PGMD13 |

| 60 | PA26/PGMD14 |

| 61 | VDDIO       |

| 62 | VDDCORE     |

| 63 | PB18        |

| 64 | PB19        |

| 65 | PB20        |

| 66 | PB21        |

| 67 | PB22        |

| 68 | GND         |

| 69 | PB23        |

| 70 | PB24        |

| 71 | PB25        |

| 72 | PB26        |

| 73 | PA27/PGMD15 |

| 74 | PA28        |

| 75 | PA29        |

|    |             |

| 76  | TDO           |

|-----|---------------|

| 77  | JTAGSEL       |

| 78  | TMS           |

| 79  | TCK           |

| 80  | PA30          |

| 81  | PA0/PGMEN0    |

| 82  | PA1/PGMEN1    |

| 83  | GND           |

| 84  | VDDIO         |

| 85  | PA3           |

| 86  | PA2           |

| 87  | VDDCORE       |

| 88  | PA4/PGMNCMD   |

| 89  | PA5/PGMRDY    |

| 90  | PA6/PGMNOE    |

| 91  | PA7/PGMNVALID |

| 92  | ERASE         |

| 93  | DDM           |

| 94  | DDP           |

| 95  | VDDFLASH      |

| 96  | GND           |

| 97  | XIN/PGMCK     |

| 98  | XOUT          |

| 99  | PLLRC         |

| 100 | VDDPLL        |

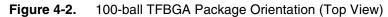

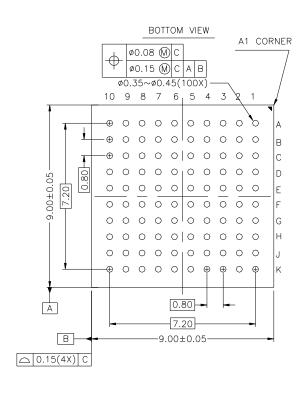

# 4.3 100-ball TFBGA Package Outline

Figure 4-2 shows the orientation of the 100-ball TFBGA package. A detailed mechanical description is given in the Mechanical Characteristics section of the full datasheet.

# 4.4 100-ball TFBGA Pinout

Table 4-2.

Pinout in 100-ball TFBGA Package

| Pin | Signal Name   |

|-----|-------------|-----|-------------|-----|-------------|-----|---------------|

| A1  | PA22/PGMD10 | C6  | PB17        | F1  | PB21        | H6  | PA7/PGMNVALID |

| A2  | PA21/PGMD9  | C7  | PB13        | F2  | PB23        | H7  | PA9/PGMM1     |

| A3  | PA20/PGMD8  | C8  | PA13/PGMD1  | F3  | PB25        | H8  | PA8/PGMM0     |

| A4  | PB1         | C9  | PA12/PGMD0  | F4  | PB26        | H9  | PB29/AD2      |

| A5  | PB7         | C10 | PA15/PGMD3  | F5  | TCK         | H10 | PLLRC         |

| A6  | PB5         | D1  | PA23/PGMD11 | F6  | PA6/PGMNOE  | J1  | PA29          |

| A7  | PB8         | D2  | PA24/PGMD12 | F7  | ERASE       | J2  | PA30          |

| A8  | PB9         | D3  | NRST        | F8  | VDDCORE     | J3  | PA0/PGMEN0    |

| A9  | PA18/PGMD6  | D4  | TST         | F9  | GND         | J4  | PA1/PGMEN1    |

| A10 | VDDIO       | D5  | PB19        | F10 | VDDIN       | J5  | VDDFLASH      |

| B1  | TDI         | D6  | PB6         | G1  | PB22        | J6  | GND           |

| B2  | PA19/PGMD7  | D7  | PA10/PGMM2  | G2  | PB24        | J7  | XIN/PGMCK     |

| B3  | PB11        | D8  | VDDIO       | G3  | PA27/PGMD15 | J8  | XOUT          |

| B4  | PB2         | D9  | PB27/AD0    | G4  | TDO         | J9  | GND           |

| B5  | PB12        | D10 | PA11/PGMM3  | G5  | PA2         | J10 | VDDPLL        |

| B6  | PB15        | E1  | PA25/PGMD13 | G6  | PA5/PGMRDY  | K1  | VDDCORE       |

| B7  | PB14        | E2  | PA26/PGMD14 | G7  | VDDCORE     | K2  | VDDCORE       |

| B8  | PA14/PGMD2  | E3  | PB18        | G8  | GND         | K3  | DDP           |

| B9  | PA16/PGMD4  | E4  | PB20        | G9  | PB30/AD3    | K4  | DDM           |

| B10 | PA17/PGMD5  | E5  | TMS         | G10 | VDDOUT      | K5  | GND           |

| C1  | PB16        | E6  | GND         | H1  | VDDCORE     | K6  | AD7           |

| C2  | PB4         | E7  | VDDIO       | H2  | PA28        | K7  | AD6           |

| C3  | PB10        | E8  | PB28/AD1    | H3  | JTAGSEL     | K8  | AD5           |

| C4  | PB3         | E9  | VDDIO       | H4  | PA3         | K9  | AD4           |

| C5  | PB0         | E10 | GND         | H5  | PA4/PGMNCMD | K10 | ADVREF        |

# 6. I/O Lines Considerations

## 6.1 JTAG Port Pins

TMS, TDI and TCK are schmitt trigger inputs and are not 5-V tolerant. TMS, TDI and TCK do not integrate a pull-up resistor.

TDO is an output, driven at up to VDDIO, and has no pull-up resistor.

The JTAGSEL pin is used to select the JTAG boundary scan when asserted at a high level. The JTAGSEL pin integrates a permanent pull-down resistor of about 15 k $\Omega$

To eliminate any risk of spuriously entering the JTAG boundary scan mode due to noise on JTAGSEL, it should be tied externally to GND if boundary scan is not used, or pulled down with an external low-value resistor (such as 1 k $\Omega$ ).

## 6.2 Test Pin

The TST pin is used for manufacturing test or fast programming mode of the AT91SAM7XC512/256/128 when asserted high. The TST pin integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND.

To eliminate any risk of entering the test mode due to noise on the TST pin, it should be tied to GND if the FFPI is not used, or pulled down with an external low-value resistor (such as 1 k $\Omega$ ).

To enter fast programming mode, the TST pin and the PA0 and PA1 pins should be tied high and PA2 tied to low.

Driving the TST pin at a high level while PA0 or PA1 is driven at 0 leads to unpredictable results.

### 6.3 Reset Pin

The NRST pin is bidirectional with an open drain output buffer. It is handled by the on-chip reset controller and can be driven low to provide a reset signal to the external components or asserted low externally to reset the microcontroller. There is no constraint on the length of the reset pulse, and the reset controller can guarantee a minimum pulse length. This allows connection of a simple push-button on the NRST pin as system user reset, and the use of the signal NRST to reset all the components of the system.

The NRST pin integrates a permanent pull-up resistor to VDDIO.

### 6.4 ERASE Pin

The ERASE pin is used to re-initialize the Flash content and some of its NVM bits. It integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND.

To eliminate any risk of erasing the Flash due to noise on the ERASE pin, it shoul be tied externally to GND, which prevents erasing the Flash from the application, or pulled down with an external low-value resistor (such as  $1 \text{ k}\Omega$ ).

This pin is debounced by the RC oscillator to improve the glitch tolerance. Minimum debouncing time is 200 ms.

## 6.5 PIO Controller Lines

All the I/O lines, PA0 to PA30 and PB0 to PB30, are 5V-tolerant and all integrate a programmable pull-up resistor. Programming of this pull-up resistor is performed independently for each I/O line through the PIO controllers.

# 7. Processor and Architecture

# 7.1 ARM7TDMI Processor

- RISC processor based on ARMv4T Von Neumann architecture

- Runs at up to 55 MHz, providing 0.9 MIPS/MHz

- Two instruction sets

- ARM® high-performance 32-bit instruction set

- Thumb<sup>®</sup> high code density 16-bit instruction set

- Three-stage pipeline architecture

- Instruction Fetch (F)

- Instruction Decode (D)

- Execute (E)

# 7.2 Debug and Test Features

- Integrated embedded in-circuit emulator

- Two watchpoint units

- Test access port accessible through a JTAG protocol

- Debug communication channel

- Debug Unit

- Two-pin UART

- Debug communication channel interrupt handling

- Chip ID Register

- IEEE1149.1 JTAG Boundary-scan on all digital pins

## 7.3 Memory Controller

- Programmable Bus Arbiter

- Handles requests from the ARM7TDMI, the Ethernet MAC and the Peripheral DMA Controller

- · Address decoder provides selection signals for

- Three internal 1 Mbyte memory areas

- One 256 Mbyte embedded peripheral area

- Abort Status Registers

- Source, Type and all parameters of the access leading to an abort are saved

- Facilitates debug by detection of bad pointers

- Misalignment Detector

- Alignment checking of all data accesses

- Abort generation in case of misalignment

- Remap Command

- Remaps the SRAM in place of the embedded non-volatile memory

- Allows handling of dynamic exception vectors

# 8. Memory

# 8.1 AT91SAM7XC512

- 512 Kbytes of dual-plane Flash Memory

- 2 contiguous banks of 1024 pages of 256 bytes

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 write cycles, 10-year data retention capability

- 32 lock bits, protecting 32 sectors of 64 pages

- Protection Mode to secure contents of the Flash

- 128 Kbytes of Fast SRAM

- Single-cycle access at full speed

# 8.2 AT91SAM7XC256

- 256 Kbytes of Flash Memory

- 1024 pages of 256 bytes

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 write cycles, 10-year data retention capability

- 16 lock bits, each protecting 16 sectors of 64 pages

- Protection Mode to secure contents of the Flash

- 64 Kbytes of Fast SRAM

- Single-cycle access at full speed

# 8.3 AT91SAM7XC128

- 128 Kbytes of Flash Memory

- 512 pages of 256 bytes

- Fast access time, 30 MHz single-cycle access in Worst Case conditions

- Page programming time: 6 ms, including page auto-erase

- Page programming without auto-erase: 3 ms

- Full chip erase time: 15 ms

- 10,000 write cycles, 10-year data retention capability

- 8 lock bits, each protecting 8 sectors of 64 pages

- Protection Mode to secure contents of the Flash

- 32 Kbytes of Fast SRAM

- Single-cycle access at full speed

|            | 0x0000 0000                | Flash Before Remap<br>SRAM After Remap |  | 1 M Bytes   |

|------------|----------------------------|----------------------------------------|--|-------------|

|            | 0x0010 0000                | Internal FLASH                         |  | 1 M Bytes   |

| 256M Bytes | 0x0020 0000                | Internal SRAM                          |  | 1 M Bytes   |

|            | 0x0030 0000<br>0x003F FFFF | Internal ROM                           |  | 1 M Bytes   |

|            | 0x0040 0000                | Undefined Areas<br>(Abort)             |  | 252 M Bytes |

|            | 0x0FFF FFFF                |                                        |  | ۲           |

**Figure 8-3.** Internal Memory Mapping with GPNVM Bit 2 = 1

### 8.5 Embedded Flash

#### 8.5.1 Flash Overview

- The Flash of the AT91SAM7XC512 is organized in two banks (dual plane) 0f 1254 pages of 256 bytes. The 524, 288 bytes are organized in 32-bit words.

- The Flash of the AT91SAM7XC256 is organized in 1024 pages of 256 bytes (single plane). It reads as 65,536 32-bit words.

- The Flash of the AT91SAM7XC128 is organized in 512 pages of 256 bytes (single plane). It reads as 32,768 32-bit words.

The Flash contains a 256-byte write buffer, accessible through a 32-bit interface.

The Flash benefits from the integration of a power reset cell and from the brownout detector. This prevents code corruption during power supply changes, even in the worst conditions.

When Flash is not used (read or write access), it is automatically placed into standby mode.

#### 8.5.2 Embedded Flash Controller

The Embedded Flash Controller (EFC) manages accesses performed by the masters of the system. It enables reading the Flash and writing the write buffer. It also contains a User Interface, mapped within the Memory Controller on the APB. The User Interface allows:

- programming of the access parameters of the Flash (number of wait states, timings, etc.)

- starting commands such as full erase, page erase, page program, NVM bit set, NVM bit clear, etc.

- getting the end status of the last command

- getting error status

- programming interrupts on the end of the last commands or on errors

The Embedded Flash Controller also provides a dual 32-bit Prefetch Buffer that optimizes 16-bit access to the Flash. This is particularly efficient when the processor is running in Thumb mode.

Two EFCs are embedded in the AT91SAM7XC512 to control each bank of 256 KBytes. Dualplane organization allows concurrent read and program functionality. Read from one memory

plane may be performed even while program or erase functions are being executed in the other memory plane.

One EFC is embedded in the AT91SAM7XC256/128 to control the single plane of 256/128 KBytes.

#### 8.5.3 Lock Regions

#### 8.5.3.1 AT91SAM7XC512

Two Embedded Flash Controllers each manage 16 lock bits to protect 16 regions of the flash against inadvertent flash erasing or programming commands. The AT91SAM7XC512 contains 32 lock regions and each lock region contains 64 pages of 256 bytes. Each lock region has a size of 16 Kbytes.

If a locked-region's erase or program command occurs, the command is aborted and the EFC trigs an interrupt.

The 32 NVM bits are software programmable through both of the EFC User Interfaces. The command "Set Lock Bit" enables the protection. The command "Clear Lock Bit" unlocks the lock region.

Asserting the ERASE pin clears the lock bits, thus unlocking the entire Flash.

#### 8.5.3.2 AT91SAM7XC256

The Embedded Flash Controller manages 16 lock bits to protect 16 regions of the flash against inadvertent flash erasing or programming commands. The AT91SAM7XC256 contains 16 lock regions and each lock region contains 64 pages of 256 bytes. Each lock region has a size of 16 Kbytes.

If a locked-region's erase or program command occurs, the command is aborted and the EFC trigs an interrupt.

The 16 NVM bits are software programmable through the EFC User Interface. The command "Set Lock Bit" enables the protection. The command "Clear Lock Bit" unlocks the lock region.

Asserting the ERASE pin clears the lock bits, thus unlocking the entire Flash.

#### 8.5.3.3 AT91SAM7XC128

The Embedded Flash Controller manages 8 lock bits to protect 8 regions of the flash against inadvertent flash erasing or programming commands. The AT91SAM7XC128 contains 8 lock regions and each lock region contains 64 pages of 256 bytes. Each lock region has a size of 16 Kbytes.

If a locked-region's erase or program command occurs, the command is aborted and the EFC trigs an interrupt.

The 8 NVM bits are software programmable through the EFC User Interface. The command "Set Lock Bit" enables the protection. The command "Clear Lock Bit" unlocks the lock region.

Asserting the ERASE pin clears the lock bits, thus unlocking the entire Flash.

#### 8.5.4 Security Bit Feature

The AT91SAM7XC512/256/128 features a security bit, based on a specific NVM-Bit. When the security is enabled, any access to the Flash, either through the ICE interface or through the Fast

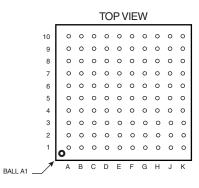

#### Figure 9-1. System Controller Block Diagram

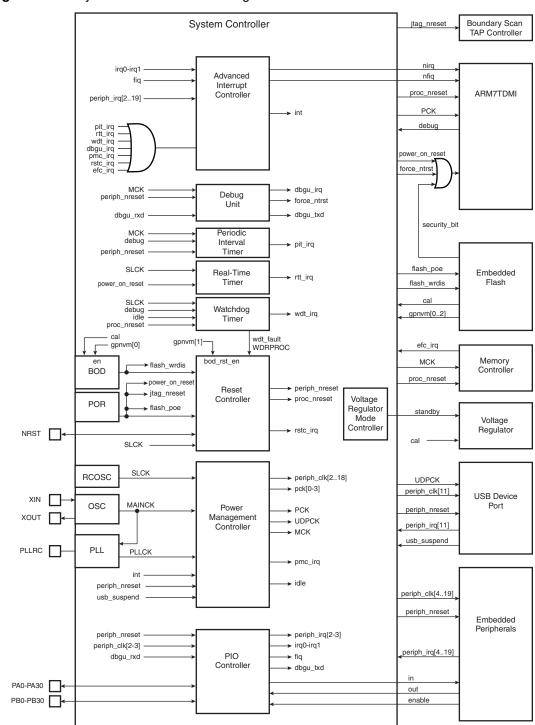

# 9.2 Clock Generator

The Clock Generator embeds one low-power RC Oscillator, one Main Oscillator and one PLL with the following characteristics:

- RC Oscillator ranges between 22 KHz and 42 KHz

- Main Oscillator frequency ranges between 3 and 20 MHz

- Main Oscillator can be bypassed

- PLL output ranges between 80 and 200 MHz

It provides SLCK, MAINCK and PLLCK.

Figure 9-2. Clock Generator Block Diagram

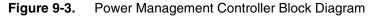

# 9.3 Power Management Controller

The Power Management Controller uses the Clock Generator outputs to provide:

- the Processor Clock PCK

- the Master Clock MCK

- the USB Clock UDPCK

- all the peripheral clocks, independently controllable

- · four programmable clock outputs

The Master Clock (MCK) is programmable from a few hundred Hz to the maximum operating frequency of the device.

The Processor Clock (PCK) switches off when entering processor idle mode, thus allowing reduced power consumption while waiting for an interrupt.

## 9.4 Advanced Interrupt Controller

- · Controls the interrupt lines (nIRQ and nFIQ) of an ARM Processor

- · Individually maskable and vectored interrupt sources

- Source 0 is reserved for the Fast Interrupt Input (FIQ)

- Source 1 is reserved for system peripherals (RTT, PIT, EFC, PMC, DBGU, etc.)

- Other sources control the peripheral interrupts or external interrupts

- Programmable edge-triggered or level-sensitive internal sources

- Programmable positive/negative edge-triggered or high/low level-sensitive external sources

- 8-level Priority Controller

- Drives the normal interrupt nIRQ of the processor

- Handles priority of the interrupt sources

• Programmable 16-bit prescaler for SLCK accuracy compensation

### 9.9 PIO Controllers

- Two PIO Controllers, each controlling 31 I/O lines

- Fully programmable through set/clear registers

- Multiplexing of two peripheral functions per I/O line

- For each I/O line (whether assigned to a peripheral or used as general-purpose I/O)

- Input change interrupt

- Half a clock period glitch filter

- Multi-drive option enables driving in open drain

- Programmable pull-up on each I/O line

- Pin data status register, supplies visibility of the level on the pin at any time

- Synchronous output, provides Set and Clear of several I/O lines in a single write

### 9.10 Voltage Regulator Controller

The purpose of this controller is to select the Power Mode of the Voltage Regulator between Normal Mode (bit 0 is cleared) or Standby Mode (bit 0 is set).

## 10.3 Peripheral Multiplexing on PIO Lines

The AT91SAM7XC512/256/128 features two PIO controllers, PIOA and PIOB, that multiplex the I/O lines of the peripheral set.

Each PIO Controller controls 31 lines. Each line can be assigned to one of two peripheral functions, A or B. Some of them can also be multiplexed with the analog inputs of the ADC Controller.

Table 10-2 on page 34 and Table 10-3 on page 35 defines how the I/O lines of the peripherals A, B or the analog inputs are multiplexed on the PIO Controller A and PIO Controller B. The two columns "Function" and "Comments" have been inserted for the user's own comments; they may be used to track how pins are defined in an application.

Note that some peripheral functions that are output only, may be duplicated in the table.

At reset, all I/O lines are automatically configured as input with the programmable pull-up enabled, so that the device is maintained in a static state as soon as a reset is detected.

# 10.5 PIO Controller B Multiplexing

|          | PIO Co       | ontroller B  |          | Application U | sage     |

|----------|--------------|--------------|----------|---------------|----------|

| I/O Line | Peripheral A | Peripheral B | Comments | Function      | Comments |

| PB0      | ETXCK/EREFCK | PCK0         |          |               |          |

| PB1      | ETXEN        |              |          |               |          |

| PB2      | ETX0         |              |          |               |          |

| PB3      | ETX1         |              |          |               |          |

| PB4      | ECRS         |              |          |               |          |

| PB5      | ERX0         |              |          |               |          |

| PB6      | ERX1         |              |          |               |          |

| PB7      | ERXER        |              |          |               |          |

| PB8      | EMDC         |              |          |               |          |

| PB9      | EMDIO        |              |          |               |          |

| PB10     | ETX2         | SPI1_NPCS1   |          |               |          |

| PB11     | ETX3         | SPI1_NPCS2   |          |               |          |

| PB12     | ETXER        | TCLK0        |          |               |          |

| PB13     | ERX2         | SPI0_NPCS1   |          |               |          |

| PB14     | ERX3         | SPI0_NPCS2   |          |               |          |

| PB15     | ERXDV/ECRSDV |              |          |               |          |

| PB16     | ECOL         | SPI1_NPCS3   |          |               |          |

| PB17     | ERXCK        | SPI0_NPCS3   |          |               |          |

| PB18     | EF100        | ADTRG        |          |               |          |

| PB19     | PWM0         | TCLK1        |          |               |          |

| PB20     | PWM1         | PCK0         |          |               |          |

| PB21     | PWM2         | PCK1         |          |               |          |

| PB22     | PWM3         | PCK2         |          |               |          |

| PB23     | TIOA0        | DCD1         |          |               |          |

| PB24     | TIOB0        | DSR1         |          |               |          |

| PB25     | TIOA1        | DTR1         |          |               |          |

| PB26     | TIOB1        | RI1          |          |               |          |

| PB27     | TIOA2        | PWM0         | AD0      |               |          |

| PB28     | TIOB2        | PWM1         | AD1      |               |          |

| PB29     | PCK1         | PWM2         | AD2      |               |          |

| PB30     | PCK2         | PWM3         | AD3      |               |          |

Table 10-3. Multiplexing on PIO Controller B

- Automatic wakeup on trigger and back to sleep mode after conversions of all enabled channels

- Four of eight analog inputs shared with digital signals

# 11. Package Drawings

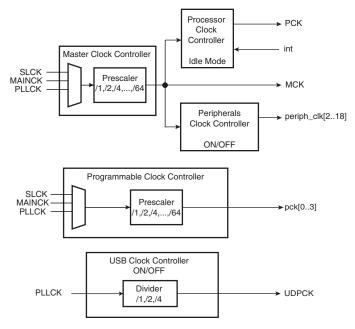

# Figure 11-1. LQFP Package Drawing

|        |      | Millimeter |                | Inch      |           |       |  |

|--------|------|------------|----------------|-----------|-----------|-------|--|

| Symbol | Min  | Nom        | Max            | Min       | Nom       | Max   |  |

| A      |      |            | 1.60           |           |           | 0.63  |  |

| A1     | 0.05 |            | 0.15           | 0.002     |           | 0.006 |  |

| A2     | 1.35 | 1.40       | 1.45           | 0.053     | 0.055     | 0.057 |  |

| D      |      | 16.00 BSC  |                |           | 0.630 BSC | I     |  |

| D1     |      | 14.00 BSC  |                |           | 0.551 BSC |       |  |

| E      |      | 16.00 BSC  |                |           | 0.630 BSC |       |  |

| E1     |      | 14.00 BSC  |                |           | 0.551 BSC |       |  |

| R2     | 0.08 |            | 0.20           | 0.003     |           | 0.008 |  |

| R1     | 0.08 |            |                | 0.003     |           |       |  |

| Q      | 0.   | 3.5.       | 7.             | 0.        | 3.5.      | 7∙    |  |

| θ1     | 0.   |            |                | 0.        |           |       |  |

| θ2     | 11.  | 12·        | 13·            | 11.       | 12·       | 13·   |  |

| θ3     | 11.  | 12·        | 13·            | 11.       | 12·       | 13·   |  |

| С      | 0.09 |            | 0.20           | 0.004     |           | 0.008 |  |

| L      | 0.45 | 0.60       | 0.75           | 0.018     | 0.024     | 0.030 |  |

| L1     |      | 1.00 REF   |                | 0.039 REF |           |       |  |

| S      | 0.20 |            |                | 0.008     |           |       |  |

| b      | 0.17 | 0.20       | 0.27           | 0.007     | 0.008     | 0.011 |  |

| е      |      | 0.50 BSC   |                |           | 0.020 BSC |       |  |

| D2     |      | 12.00      |                |           | 0.472     |       |  |

| E2     |      | 12.00      |                |           | 0.472     |       |  |

|        |      | Toleranc   | es of Form and | Position  |           |       |  |

| aaa    |      | 0.20       |                |           | 0.008     |       |  |

| bbb    | 0.20 |            |                | 0.008     |           |       |  |

| CCC    |      | 0.08       |                |           | 0.003     |       |  |

| ddd    |      | 0.08       |                |           | 0.003     |       |  |

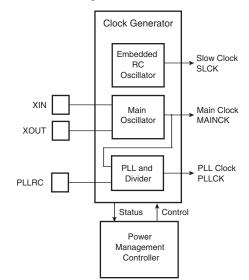

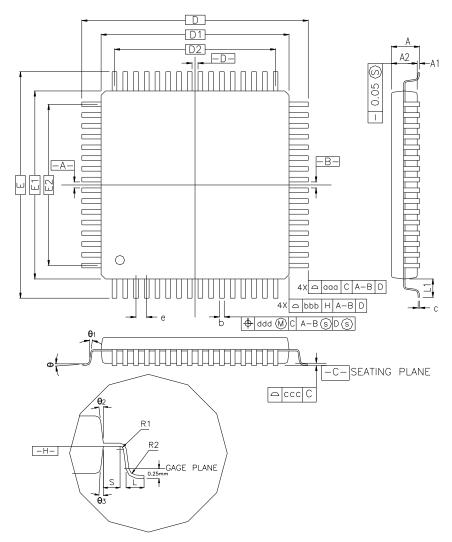

### Figure 11-2. 100-TFBGA Package Drawing

| Ball Pitch          | 0.80 |

|---------------------|------|

| Substrate Thickness | 0.21 |

| Ball Diameter       | 0.4  |

| Mold Thickness      | 0.53 |

All dimensions are in mm

#### Headquarters

*Atmel Corporation* 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon Hong Kong Tel: (852) 2245-6100 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

#### Web Site

www.atmel.com www.atmel.com/AT91SAM www.atmel.com/lproducts/ASIC

Literature Requests www.atmel.com/literature **Technical Support** AT91SAM Support Atmel techincal support Sales Contacts www.atmel.com/contacts/

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNTIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2008 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, Atmel logo and combinations thereof, DataFlash<sup>®</sup>, SAM-BA<sup>®</sup> and others, are registered trademarks of Atmel Corporation or its subsidiaries. Windows<sup>®</sup> and others, are registered trademarks of Microsoft Corporation in the US and/or other countries. ARM<sup>®</sup>, the ARM Powered<sup>®</sup> logo and others, are registered trademarks or trademarks of ARM Limited. Other terms and product names may be the trademarks of others.