Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status                | Active                                                                                                             |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Core Processor                | ARM® Cortex®-M7                                                                                                    |

| Core Size                     | 32-Bit Single-Core                                                                                                 |

| Speed                         | 480MHz                                                                                                             |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I²C, IrDA, LINbus, MDIO, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                                  |

| Number of I/O                 | 140                                                                                                                |

| Program Memory Size           | 2MB (2M x 8)                                                                                                       |

| Program Memory Type           | FLASH                                                                                                              |

| EEPROM Size                   | -                                                                                                                  |

| RAM Size                      | 1M x 8                                                                                                             |

| Voltage - Supply<br>(Vcc/Vdd) | 1.62V ~ 3.6V                                                                                                       |

| Data Converters               | A/D 36x16b; D/A 2x12b                                                                                              |

| Oscillator Type               | Internal                                                                                                           |

| Operating<br>Temperature      | -40°C ~ 85°C (TA)                                                                                                  |

| Mounting Type                 | Surface Mount                                                                                                      |

| Package / Case                | 201-UFBGA                                                                                                          |

| Supplier Device<br>Package    | 176+25UFBGA (10x10)                                                                                                |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32h743iik6                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

STM32H743xl devices operate in the –40 to +85 °C temperature range from a 1.62 to 3.6 V power supply. The supply voltage can drop down to 1.62 V by using an external power supervisor (see Section 3.5.2: Power supply supervisor) and connecting the PDR\_ON pin to  $V_{SS}$ . Otherwise the supply voltage must stay above 1.71 V with the embedded power voltage detector enabled.

Dedicated supply inputs for USB (OTG\_FS and OTG\_HS) are available on all packages except LQFP100 to allow a greater power supply choice.

A comprehensive set of power-saving modes allows the design of low-power applications.

STM32H743xI devices are offered in 8 packages ranging from 100 pins to 240 pins/balls. The set of included peripherals changes with the device chosen.

These features make STM32H743xI microcontrollers suitable for a wide range of applications:

- Motor drive and application control

- Medical equipment

- Industrial applications: PLC, inverters, circuit breakers

- Printers, and scanners

- Alarm systems, video intercom, and HVAC

- Home audio appliances

- Mobile applications, Internet of Things

- Wearable devices: smart watches.

*Figure 1* shows the general block diagram of the device family.

| Pe                   | eripherals                  | STM32H<br>743VI | STM32H<br>743ZI | STM32H<br>743AI | STM32H<br>743II | STM32H<br>743BI | STM32H<br>743XI |  |  |  |

|----------------------|-----------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--|--|--|

| Flash m              | emory in Kbytes             | 2048            |                 |                 |                 |                 |                 |  |  |  |

|                      | SRAM mapped onto<br>AXI bus |                 |                 | 512             |                 |                 |                 |  |  |  |

| SRAM in              | SRAM1 (D2 domain)           |                 |                 | 128             |                 |                 |                 |  |  |  |

| Kbytes               | SRAM2 (D2 domain)           |                 |                 | 128             |                 |                 |                 |  |  |  |

|                      | SRAM3 (D2 domain)           | 32              |                 |                 |                 |                 |                 |  |  |  |

|                      | SRAM4 (D3 domain)           | 64              |                 |                 |                 |                 |                 |  |  |  |

| TCM RAM in<br>Kbytes | ITCM RAM<br>(instruction)   |                 |                 |                 |                 |                 |                 |  |  |  |

| Royles               | DTCM RAM (data)             |                 |                 | 128             |                 |                 |                 |  |  |  |

| Backup               | SRAM (Kbytes)               |                 |                 | 4               |                 |                 |                 |  |  |  |

|                      | FMC                         | Yes             |                 |                 |                 |                 |                 |  |  |  |

| (                    | Quad-SPI                    | Yes             |                 |                 |                 |                 |                 |  |  |  |

|                      | Ethernet                    | Yes             |                 |                 |                 |                 |                 |  |  |  |

#### Table 2. STM32H743xl features and peripheral counts

The  $V_{\mbox{CORE}}$  domain is split into the following power domains that can be independently switch off.

- D1 domain containing some peripherals and the Cortex<sup>®</sup>-M7 core.

- D2 domain containing a large part of the peripherals.

- D3 domain containing some peripherals and the system control.

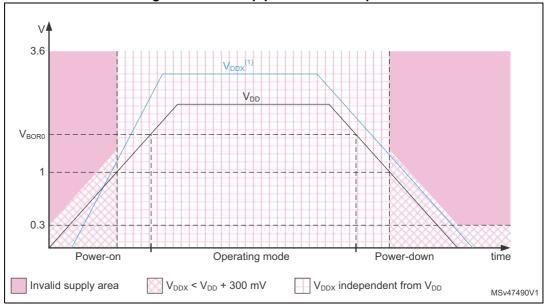

During power-up and power-down phases, the following power sequence requirements must be respected (see *Figure 2*):

- When  $V_{DD}$  is below 1 V, other power supplies ( $V_{DDA}$ ,  $V_{DD33USB}$ ,  $V_{DD50USB}$ ) must remain below  $V_{DD}$  + 300 mV.

- When V<sub>DD</sub> is above 1 V, all power supplies are independent.

During the power-down phase,  $V_{DD}$  can temporarily become lower than other supplies only if the energy provided to the microcontroller remains below 1 mJ. This allows external decoupling capacitors to be discharged with different time constants during the power-down transient phase.

Figure 2. Power-up/power-down sequence

1.  $V_{DDx}$  refers to any power supply among  $V_{DDA}$ ,  $V_{DD33USB}$ ,  $V_{DD50USB}$ .

## 3.7 Reset and clock controller (RCC)

The clock and reset controller is located in D3 domain. The RCC manages the generation of all the clocks, as well as the clock gating and the control of the system and peripheral resets. It provides a high flexibility in the choice of clock sources and allows to apply clock ratios to improve the power consumption. In addition, on some communication peripherals that are capable to work with two different clock domains (either a bus interface clock or a kernel peripheral clock), the system frequency can be changed without modifying the baudrate.

## 3.7.1 Clock management

The devices embed four internal oscillators, two oscillators with external crystal or resonator, two internal oscillators with fast startup time and three PLLs.

The RCC receives the following clock source inputs:

- Internal oscillators:

- 64 MHz HSI clock

- 48 MHz RC oscillator

- 4 MHz CSI clock

- 32 kHz LSI clock

- External oscillators:

- 4-48 MHz HSE clock

- 32.768 kHz LSE clock

The RCC provides three PLLs: one for system clock, two for kernel clocks.

The system starts on the HSI clock. The user application can then select the clock configuration.

#### 3.7.2 System reset sources

Power-on reset initializes all registers while system reset reinitializes the system except for the debug, part of the RCC and power controller status registers, as well as the backup power domain.

A system reset is generated in the following cases:

- Power-on reset (pwr\_por\_rst)

- Brownout reset

- Low level on NRST pin (external reset)

- Window watchdog

- Independent watchdog

- Software reset

- Low-power mode security reset

- Exit from Standby

## 3.25 LCD-TFT controller

The LCD-TFT display controller provides a 24-bit parallel digital RGB (Red, Green, Blue) and delivers all signals to interface directly to a broad range of LCD and TFT panels up to XGA (1024x768) resolution with the following features:

- 2 display layers with dedicated FIFO (64x64-bit)

- Color Look-Up table (CLUT) up to 256 colors (256x24-bit) per layer

- Up to 8 input color formats selectable per layer

- Flexible blending between two layers using alpha value (per pixel or constant)

- Flexible programmable parameters for each layer

- Color keying (transparency color)

- Up to 4 programmable interrupt events

- AXI master interface with burst of 16 words

## 3.26 JPEG Codec (JPEG)

The JPEG Codec can encode and decode a JPEG stream as defined in the **ISO/IEC 10918-1** specification. It provides an fast and simple hardware compressor and decompressor of JPEG images with full management of JPEG headers.

The JPEG codec main features are as follows:

- 8-bit/channel pixel depths

- Single clock per pixel encoding and decoding

- Support for JPEG header generation and parsing

- Up to four programmable quantization tables

- Fully programmable Huffman tables (two AC and two DC)

- Fully programmable minimum coded unit (MCU)

- Encode/decode support (non simultaneous)

- Single clock Huffman coding and decoding

- Two-channel interface: Pixel/Compress In, Pixel/Compressed Out

- Support for single greyscale component

- Ability to enable/disable header processing

- Fully synchronous design

- Configuration for High-speed decode mode

## 3.27 Random number generator (RNG)

All devices embed an RNG that delivers 32-bit random numbers generated by an integrated analog circuit.

## 3.28 Timers and watchdogs

The devices include one high-resolution timer, two advanced-control timers, ten generalpurpose timers, two basic timers, five low-power timers, two watchdogs and a SysTick timer.

## 3.28.4 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

TIM6 and TIM7 support independent DMA request generation.

#### 3.28.5 Low-power timers (LPTIM1, LPTIM2, LPTIM3, LPTIM4, LPTIM5)

The low-power timers have an independent clock and is running also in Stop mode if it is clocked by LSE, LSI or an external clock. It is able to wakeup the devices from Stop mode.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous / One-shot mode

- Selectable software / hardware input trigger

- Selectable clock source:

- Internal clock source: LSE, LSI, HSI or APB clock

- External clock source over LPTIM input (working even with no internal clock source running, used by the Pulse Counter Application)

- Programmable digital glitch filter

- Encoder mode

#### 3.28.6 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

#### 3.28.7 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in Debug mode.

#### 3.28.8 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

|         |          |         | Pin/ba   | all nam     |         |         |                   |                                          |          |               |       | continueuy                                                                                                                                                                     |                                           |

|---------|----------|---------|----------|-------------|---------|---------|-------------------|------------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| LQFP100 | TFBGA100 | LQFP144 | UFBGA169 | UFBGA176+25 | LQFP176 | LQFP208 | TFBGA240 +25      | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                                            | Additional<br>functions                   |

| -       | -        | -       | K3       | H4          | 45      | 48      | P3                | PH4                                      | I/O      | FT_fa         | -     | I2C2_SCL, LCD_G5,<br>OTG_HS_ULPI_NXT,<br>LCD_G4, EVENTOUT                                                                                                                      | ADC3_INN14,<br>ADC3_INP15                 |

| -       | -        | -       | L3       | J4          | 46      | 49      | P4                | PH5                                      | I/O      | FT_fa         | -     | I2C2_SDA, SPI5_NSS,<br>FMC_SDNWE,<br>EVENTOUT                                                                                                                                  | ADC3_INN15,<br>ADC3_INP16                 |

| 25      | K2       | 37      | N3       | R2          | 47      | 50      | U2                | PA3                                      | I/O      | FT_<br>ha     | -     | TIM2_CH4, TIM5_CH4,<br>LPTIM5_OUT,<br>TIM15_CH2,<br>USART2_RX, LCD_B2,<br>OTG_HS_ULPI_D0,<br>ETH_MII_COL, LCD_B5,<br>EVENTOUT                                                  | ADC12_INP15                               |

| 26      | -        | 38      | G2       | K6          | -       | 51      | F2 <sup>(4)</sup> | VSS                                      | S        | -             | -     | -                                                                                                                                                                              | -                                         |

| -       | -        | -       | I        | L4          | 48      | -       | -                 | VSS                                      | S        | -             | -     | -                                                                                                                                                                              | -                                         |

| 27      | -        | 39      | -        | K4          | 49      | 52      | G5                | VDD                                      | S        | -             | -     | -                                                                                                                                                                              | -                                         |

| 28      | G3       | 40      | H6       | N4          | 50      | 53      | U3                | PA4                                      | I/O      | TT_a          | -     | TIM5_ETR,<br>SPI1_NSS/I2S1_WS,<br>SPI3_NSS/I2S3_WS,<br>USART2_CK, SPI6_NSS,<br>OTG_HS_SOF,<br>DCMI_HSYNC,<br>LCD_VSYNC,<br>EVENTOUT                                            | ADC12_INP18,<br>DAC1_OUT1                 |

| 29      | H3       | 41      | L4       | P4          | 51      | 54      | Т3                | PA5                                      | I/O      | TT_<br>ha     | -     | TIM2_CH1/TIM2_ETR,<br>TIM8_CH1N,<br>SPI1_SCK/I2S1_CK,<br>SPI6_SCK,<br>OTG_HS_ULPI_CK,<br>LCD_R4, EVENTOUT                                                                      | ADC12_INN18,<br>ADC12_INP19,<br>DAC1_OUT2 |

| 30      | J3       | 42      | K5       | P3          | 52      | 55      | R3                | PA6                                      | I/O      | FT_a          | -     | TIM1_BKIN, TIM3_CH1,<br>TIM8_BKIN,<br>SPI1_MISO/I2S1_SDI,<br>SPI6_MISO, TIM13_CH1,<br>TIM8_BKIN_COMP12,<br>MDIOS_MDC,<br>TIM1_BKIN_COMP12,<br>DCMI_PIXCLK, LCD_G2,<br>EVENTOUT | ADC12_INP3                                |

Table 8. STM32H743xl pin/ball definition (continued)

|         |          |         | Pin/ba   | all nam     | е       |         |              |                                          |          |               |       |                                                                                                               |                            |

|---------|----------|---------|----------|-------------|---------|---------|--------------|------------------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------|----------------------------|

| LQFP100 | TFBGA100 | LQFP144 | UFBGA169 | UFBGA176+25 | LQFP176 | LQFP208 | TFBGA240 +25 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                           | Additional<br>functions    |

| 38      | J5       | 59      | H8       | P8          | 69      | 80      | Т9           | PE8                                      | I/O      | TT_<br>ha     | -     | TIM1_CH1N,<br>DFSDM_CKIN2,<br>UART7_TX,<br>QUADSPI_BK2_IO1,<br>FMC_D5/FMC_DA5,<br>COMP_2_OUT,<br>EVENTOUT     | OPAMP2_<br>VINM            |

| 39      | K5       | 60      | J8       | P9          | 70      | 81      | P9           | PE9                                      | I/O      | TT_<br>ha     | -     | TIM1_CH1,<br>DFSDM_CKOUT,<br>UART7_RTS,<br>QUADSPI_BK2_IO2,<br>FMC_D6/FMC_DA6,<br>EVENTOUT                    | OPAMP2_VINP,<br>COMP_2_INP |

| -       | -        | 61      | C12      | M9          | 71      | 82      | J17          | VSS                                      | S        | -             | -     | -                                                                                                             | -                          |

| -       | -        | 62      | C13      | N9          | 72      | 83      | J13          | VDD                                      | S        | -             | -     | -                                                                                                             | -                          |

| 40      | G6       | 63      | M8       | R9          | 73      | 84      | N9           | PE10                                     | I/O      | FT_<br>ha     | -     | TIM1_CH2N,<br>DFSDM_DATIN4,<br>UART7_CTS,<br>QUADSPI_BK2_IO3,<br>FMC_D7/FMC_DA7,<br>EVENTOUT                  | COMP_2_INM                 |

| 41      | H6       | 64      | N8       | P10         | 74      | 85      | P10          | PE11                                     | I/O      | FT_<br>ha     | -     | TIM1_CH2,<br>DFSDM_CKIN4,<br>SPI4_NSS, SAI2_SD_B,<br>FMC_D8/FMC_DA8,<br>LCD_G3, EVENTOUT                      | COMP_2_INP                 |

| 42      | J6       | 65      | L8       | R10         | 75      | 86      | R10          | PE12                                     | I/O      | FT_h          | -     | TIM1_CH3N,<br>DFSDM_DATIN5,<br>SPI4_SCK,<br>SAI2_SCK_B,<br>FMC_D9/FMC_DA9,<br>COMP_1_OUT, LCD_B4,<br>EVENTOUT | -                          |

| 43      | K6       | 66      | K8       | N11         | 76      | 87      | T10          | PE13                                     | I/O      | FT_h          | -     | TIM1_CH3,<br>DFSDM_CKIN5,<br>SPI4_MISO, SAI2_FS_B,<br>FMC_D10/FMC_DA10,<br>COMP_2_OUT, LCD_DE,<br>EVENTOUT    | -                          |

| -       | -        | -       | L12      | F7          | -       | -       | K15          | VSS                                      | S        | -             | -     | -                                                                                                             | -                          |

| -       | -        | -       | H13      | -           | -       | -       | K13          | VDD                                      | S        | -             | -     | -                                                                                                             | -                          |

Table 8. STM32H743xl pin/ball definition (continued)

|         | 44 G7 67 J9 P11 77 84 |         |            |             |         |         |              |                                          |          |               |       |                                                                                                                                                                                     |                         |

|---------|-----------------------|---------|------------|-------------|---------|---------|--------------|------------------------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | TFBGA100              | LQFP144 | UFBGA169   | UFBGA176+25 | LQFP176 | LQFP208 | TFBGA240 +25 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                                                 | Additional<br>functions |

| 44      | G7                    | 67      | <b>1</b> 9 | P11         | 77      | 88      | U10          | PE14                                     | I/O      | FT_h          | -     | TIM1_CH4, SPI4_MOSI,<br>SAI2_MCK_B,<br>FMC_D11/FMC_DA11,<br>LCD_CLK, EVENTOUT                                                                                                       | -                       |

| 45      | H7                    | 68      | N9         | R11         | 78      | 89      | R11          | PE15                                     | I/O      | FT_h          | -     | TIM1_BKIN,<br>HDMITIM1_BKIN,<br>FMC_D12/FMC_DA12,<br>TIM1_BKIN_COMP12,<br>LCD_R7, EVENTOUT                                                                                          | -                       |

| 46      | J7                    | 69      | L9         | R12         | 79      | 90      | P11          | PB10                                     | I/O      | FT_f          | -     | TIM2_CH3,<br>HRTIM_SCOUT,<br>LPTIM2_IN1, I2C2_SCL,<br>SPI2_SCK/I2S2_CK,<br>DFSDM_DATIN7,<br>USART3_TX,<br>QUADSPI_BK1_NCS,<br>OTG_HS_ULPI_D3,<br>ETH_MII_RX_ER,<br>LCD_G4, EVENTOUT | -                       |

| 47      | К7                    | 70      | M9         | R13         | 80      | 91      | P12          | PB11                                     | I/O      | FT_f          | -     | TIM2_CH4,<br>HRTIM_SCIN,<br>LPTIM2_ETR,<br>I2C2_SDA,<br>DFSDM_CKIN7,<br>USART3_RX,<br>OTG_HS_ULPI_D4,<br>ETH_MII_TX_EN/ETH_R<br>MII_TX_EN, LCD_G5,<br>EVENTOUT                      | -                       |

| 48      | F8                    | 71      | N10        | M10         | 81      | 92      | U11          | VCAPVCA<br>P                             | S        | -             | -     | -                                                                                                                                                                                   | -                       |

| 49      | E4                    | -       | -          | K7          | -       | 93      | L15          | VSS                                      | S        | -             | -     | -                                                                                                                                                                                   | -                       |

| -       | -                     | -       | M10        | -           | -       | -       | U12          | VDDLDO                                   | S        | -             | -     | -                                                                                                                                                                                   | -                       |

| 50      | -                     | 72      | M1         | N10         | 82      | 94      | L13          | VDD                                      | S        | -             | -     | -                                                                                                                                                                                   | -                       |

| -       | -                     | -       | -          | -           | -       | 95      | R12          | PJ5                                      | I/O      | FT            | -     | LCD_R6, EVENTOUT                                                                                                                                                                    | -                       |

| -       | -                     | -       | -          | M11         | 83      | 96      | T11          | PH6                                      | I/O      | FT            | -     | TIM12_CH1,<br>I2C2_SMBA, SPI5_SCK,<br>ETH_MII_RXD2,<br>FMC_SDNE1, DCMI_D8,<br>EVENTOUT                                                                                              | -                       |

| -       | -                     | -       | -          | N12         | 84      | 97      | U13          | PH7                                      | I/O      | FT_fa         | -     | I2C3_SCL, SPI5_MISO,<br>ETH_MII_RXD3,<br>FMC_SDCKE1,<br>DCMI_D9, EVENTOUT                                                                                                           | -                       |

Table 8. STM32H743xl pin/ball definition (continued)

|         |          |         | Pin/ba   | all nam     |         |         |              |                                          |          |               |       | oontinueuy                                                                                                                                |                         |

|---------|----------|---------|----------|-------------|---------|---------|--------------|------------------------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | TFBGA100 | LQFP144 | UFBGA169 | UFBGA176+25 | LQFP176 | LQFP208 | TFBGA240 +25 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                       | Additional<br>functions |

| 97      | D4       | 141     | D5       | A4          | 169     | 200     | C4           | PE0                                      | I/O      | FT_h          | -     | LPTIM1_ETR,<br>TIM4_ETR,<br>HRTIM_SCIN,<br>LPTIM2_ETR,<br>UART8_RX,<br>FDCAN1_RXFD_MODE,<br>SAI2_MCK_A,<br>FMC_NBL0, DCMI_D2,<br>EVENTOUT | -                       |

| 98      | C4       | 142     | D4       | A3          | 170     | 201     | B4           | PE1                                      | I/O      | FT_h          | -     | LPTIM1_IN2,<br>HRTIM_SCOUT,<br>UART8_TX,<br>FDCAN1_TXFD_MODE,<br>FMC_NBL1, DCMI_D3,<br>EVENTOUT                                           | -                       |

| -       | -        | -       | -        | -           | -       | -       | A7           | VCAP                                     | S        | -             | -     | -                                                                                                                                         | -                       |

| 99      | -        | -       | -        | D5          | -       | 202     | -            | VSS                                      | S        | -             | -     | -                                                                                                                                         | -                       |

| -       | F7       | 143     | C4       | C6          | 171     | 203     | E7           | PDR_ON                                   | S        | -             | -     | -                                                                                                                                         | -                       |

| -       | F4       | -       | B4       | -           | -       | -       | A6           | VDDLDO                                   | S        | -             | -     | -                                                                                                                                         | -                       |

| 100     | -        | 144     | -        | C5          | 172     | 204     | -            | VDD                                      | S        | -             | -     | -                                                                                                                                         | -                       |

| -       | -        | -       | -        | D4          | 173     | 205     | A4           | Pl4                                      | I/O      | FT_h          | -     | TIM8_BKIN,<br>SAI2_MCK_A,<br>TIM8_BKIN_COMP12,<br>FMC_NBL2, DCMI_D5,<br>LCD_B4, EVENTOUT                                                  | -                       |

| -       | -        | -       | -        | C4          | 174     | 206     | A3           | PI5                                      | I/O      | FT_h          | -     | TIM8_CH1,<br>SAI2_SCK_A,<br>FMC_NBL3,<br>DCMI_VSYNC, LCD_B5,<br>EVENTOUT                                                                  | -                       |

| -       | -        | -       | A4       | C3          | 175     | 207     | A2           | Pl6                                      | I/O      | FT_h          | -     | TIM8_CH2, SAI2_SD_A,<br>FMC_D28, DCMI_D6,<br>LCD_B6, EVENTOUT                                                                             | -                       |

| -       | -        | -       | E2       | C2          | 176     | 208     | В3           | PI7                                      | I/O      | FT_h          | -     | TIM8_CH3, SAI2_FS_A,<br>FMC_D29, DCMI_D7,<br>LCD_B7, EVENTOUT                                                                             | -                       |

| -       | -        | -       | -        | H9          | -       | -       | -            | VSS                                      | S        | -             | -     | -                                                                                                                                         | -                       |

| -       | -        | -       | -        | K9          | -       | -       | -            | VSS                                      | S        | -             | -     | -                                                                                                                                         | -                       |

| -       | -        | -       | -        | K10         | -       | -       | -            | VSS                                      | S        | -             | -     | -                                                                                                                                         | -                       |

Table 8. STM32H743xI pin/ball definition (continued)

1. When this pin/ball was previously configured as an oscillator, the oscillator function is kept during and after a reset. This is valid for all resets except for power-on reset.

2. This ball should remain floating.

90/231

# DS12110 Rev 5

|        |      |         |                                    |                                 |                                                       |                                                          | Table                      | 15. Port                                   | G altern                                       | ate func                                                    | tions                                                                         |                                                                    |                                                                     |                                                     |                            |               |               |

|--------|------|---------|------------------------------------|---------------------------------|-------------------------------------------------------|----------------------------------------------------------|----------------------------|--------------------------------------------|------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------|----------------------------|---------------|---------------|

|        |      | AF0     | AF1                                | AF2                             | AF3                                                   | AF4                                                      | AF5                        | AF6                                        | AF7                                            | AF8                                                         | AF9                                                                           | AF10                                                               | AF11                                                                | AF12                                                | AF13                       | AF14          | AF15          |

|        | Port | SYS     | TIM1/2/16/1<br>7/LPTIM1/<br>HRTIM1 | SAI1/TIM3/<br>4/5/12/<br>HRTIM1 | LPUART/<br>TIM8/<br>LPTIM2/3/4<br>/5/HRTIM1/<br>DFSDM | I2C1/2/3/4/<br>USART1/<br>TIM15/<br>LPTIM2/<br>DFSDM/CEC | SPI1/2/3/4/<br>5/6/CEC     | SPI2/3/SAI1<br>/3/I2C4/<br>UART4/<br>DFSDM | SPI2/3/6/<br>USART1/2/<br>3/6/UART7/<br>SDMMC1 | SPI6/SAI2/<br>4/UART4/5/<br>8/LPUART/<br>SDMMC1/<br>SPDIFRX | SAI4/<br>FDCAN1/2/<br>TIM13/14/<br>QUADSPI/<br>FMC/<br>SDMMC2/<br>LCD/SPDIFRX | SAI2/4/TIM8/<br>QUADSPI/<br>SDMMC2/<br>OTG1_HS/<br>OTG2_FS/<br>LCD | I2C4/UART7<br>/SWPMI1/<br>TIM1/8/<br>DFSDM/<br>SDMMC2/<br>MDIOS/ETH | TIM1/8/FMC<br>/SDMMC1/<br>MDIOS/<br>OTG1_FS/<br>LCD | TIM1/<br>DCMI/LCD<br>/COMP | UART5/<br>LCD | SYS           |

|        | PG0  | -       | -                                  | -                               | -                                                     | -                                                        | -                          | -                                          | -                                              | -                                                           | -                                                                             | -                                                                  | -                                                                   | FMC_A10                                             | -                          | -             | EVENT<br>-OUT |

|        | PG1  | -       | -                                  | -                               | -                                                     | -                                                        | -                          | -                                          | -                                              | -                                                           | -                                                                             | -                                                                  | -                                                                   | FMC_A11                                             | -                          | -             | EVENT<br>-OUT |

|        | PG2  | -       | -                                  | -                               | TIM8_BKIN                                             | -                                                        | -                          | -                                          | -                                              | -                                                           | -                                                                             | -                                                                  | TIM8_BKIN_<br>COMP12                                                | FMC_A12                                             | -                          | -             | EVENT<br>-OUT |

|        | PG3  | -       | -                                  | -                               | TIM8_<br>BKIN2                                        | -                                                        | -                          | -                                          | -                                              | -                                                           | -                                                                             | -                                                                  | TIM8_BKIN2<br>_COMP12                                               | FMC_A13                                             | -                          | -             | EVENT<br>-OUT |

|        | PG4  | -       | TIM1_BKIN<br>2                     | -                               | -                                                     | -                                                        | -                          | -                                          | -                                              | -                                                           | -                                                                             | -                                                                  | TIM1_BKIN2<br>_COMP12                                               | FMC_A14/<br>FMC_BA0                                 | -                          | -             | EVENT<br>-OUT |

|        | PG5  | -       | TIM1_ETR                           | -                               | -                                                     | -                                                        | -                          | -                                          | -                                              | -                                                           | -                                                                             | -                                                                  | -                                                                   | FMC_A15/<br>FMC_BA1                                 | -                          | -             | EVENT<br>-OUT |

|        | PG6  | -       | TIM17_<br>BKIN                     | HRTIM_<br>CHE1                  | -                                                     | -                                                        | -                          | -                                          | -                                              | -                                                           | -                                                                             | QUADSPI_<br>BK1_NCS                                                | -                                                                   | FMC_NE3                                             | DCMI_D1<br>2               | LCD_R<br>7    | EVENT<br>-OUT |

| Port G |      | -       | -                                  | HRTIM_<br>CHE2                  | -                                                     | -                                                        | -                          | SAI1_<br>MCLK_A                            | USART6_<br>CK                                  | -                                                           | -                                                                             | -                                                                  | -                                                                   | FMC_INT                                             | DCMI_D1<br>3               | LCD_<br>CLK   | EVENT<br>-OUT |

| đ      | PG8  | -       | -                                  | -                               | TIM8_ETR                                              | -                                                        | SPI6_NSS                   | -                                          | USART6_<br>RTS                                 | SPDIFRX_<br>IN2                                             | -                                                                             | -                                                                  | ETH_PPS_<br>OUT                                                     | FMC_<br>SDCLK                                       | -                          | LCD_<br>G7    | EVENT<br>-OUT |

|        | PG9  | -       | -                                  | -                               | -                                                     | -                                                        | SPI1_<br>MISO/I2S1<br>_SDI | -                                          | USART6_<br>RX                                  | SPDIFRX_<br>IN3                                             | QUADSPI_BK<br>2_IO2                                                           | SAI2_FS_B                                                          | -                                                                   | FMC_NE2/<br>FMC_NCE                                 | DCMI_<br>VSYNC             | -             | EVENT<br>-OUT |

|        | PG10 | -       | -                                  | HRTIM_<br>FLT5                  | -                                                     | -                                                        | SPI1_NSS/<br>I2S1_WS       | -                                          | -                                              | -                                                           | LCD_G3                                                                        | SAI2_SD_B                                                          | -                                                                   | FMC_NE3                                             | DCMI_D2                    | LCD_B<br>2    | EVENT<br>-OUT |

|        | PG11 | -       | -                                  | HRTIM_<br>EEV4                  | -                                                     | -                                                        | SPI1_SCK/<br>I2S1_CK       | -                                          | -                                              | SPDIFRX_<br>IN0                                             | -                                                                             | SDMMC2_D2                                                          | ETH_MII_<br>TX_EN/<br>ETH_RMII_<br>TX_EN                            | -                                                   | DCMI_D3                    | LCD_B<br>3    | EVENT<br>-OUT |

|        | PG12 | -       | LPTIM1_IN1                         | HRTIM_<br>EEV5                  | -                                                     | -                                                        | SPI6_<br>MISO              |                                            | USART6_<br>RTS                                 | SPDIFRX_<br>IN1                                             | LCD_B4                                                                        | -                                                                  | ETH_MII_<br>TXD1/ETH_<br>RMII_TXD1                                  | FMC_NE4                                             | -                          | LCD_<br>B1    | EVENT<br>-OUT |

|        | PG13 | TRACED0 | LPTIM1_<br>OUT                     | HRTIM_<br>EEV10                 | -                                                     | -                                                        | SPI6_SCK                   | -                                          | USART6_<br>CTS_NSS                             | -                                                           | -                                                                             | -                                                                  | ETH_MII_<br>TXD0/ETH_<br>RMII_TXD0                                  | FMC_A24                                             | -                          | LCD_<br>R0    | EVENT<br>-OUT |

Pin descriptions

|      | able 38. Peripheral |      | I <sub>DD</sub> (Typ) |      |        |

|------|---------------------|------|-----------------------|------|--------|

| P    | eripheral           | VOS1 | VOS2                  | VOS3 | – Unit |

|      | TIM1                | 5.1  | 4.8                   | 4.3  |        |

|      | TIM8                | 5.4  | 4.9                   | 4.6  |        |

|      | USART1 registers    | 2.7  | 2.6                   | 2.5  |        |

|      | USART1 kernel       | 0.1  | 0.1                   | 0.1  |        |

|      | USART6 registers    | 2.6  | 2.5                   | 2.5  |        |

|      | USART6 kernel       | 0.1  | 0.1                   | 0.1  |        |

|      | SPI1 registers      | 1.8  | 1.6                   | 1.6  |        |

|      | SPI1 kernel         | 1    | 0.8                   | 0.6  |        |

|      | SPI4 registers      | 1.6  | 1.5                   | 1.5  |        |

|      | SPI4 kernel         | 0.5  | 0.4                   | 0.4  |        |

|      | TIM15               | 3.1  | 2.8                   | 2.7  |        |

|      | TIM16               | 2.4  | 2.1                   | 2.1  |        |

| APB2 | TIM17               | 2.2  | 2                     | 1.9  | µA/MHz |

|      | SPI5 registers      | 1.8  | 1.7                   | 1.7  |        |

|      | SPI5 kernel         | 0.6  | 0.5                   | 0.3  |        |

|      | SAI1 registers      | 1.5  | 1.4                   | 1.4  |        |

|      | SAI1 kernel         | 2    | 1.7                   | 1.5  |        |

|      | SAI2 registers      | 1.5  | 1.5                   | 1.3  |        |

|      | SAI2 kernel         | 2.2  | 1.9                   | 1.8  |        |

|      | SAI3 registers      | 1.8  | 1.6                   | 1.6  |        |

|      | SAI3 kernel         | 2.5  | 2.3                   | 2.1  |        |

|      | DFSDM1 registers    | 6    | 5.4                   | 5.2  | 1      |

|      | DFSDM1 kernel       | 0.9  | 0.8                   | 0.7  | 1      |

|      | HRTIM               | 40   | 37                    | 35   | 1      |

|      | Bridge APB2         | 0.1  | 0.1                   | 0.1  |        |

| Table 38 Pr | eripheral current | consumption in | Run mode     | (continued) |

|-------------|-------------------|----------------|--------------|-------------|

|             |                   | consumption in | INUIT ITTOUE | (continueu) |

|      |                      |      | I <sub>DD</sub> (Typ) | <b>、</b> |        |

|------|----------------------|------|-----------------------|----------|--------|

| Р    | eripheral            | VOS1 | VOS2                  | VOS3     | Unit   |

|      | SYSCFG               | 1    | 0.7                   | 0.7      |        |

|      | LPUART1<br>registers | 1.1  | 1.1                   | 1.1      |        |

|      | LPUART1 kernel       | 2.6  | 2.4                   | 2.1      |        |

|      | SPI6 registers       | 1.6  | 1.5                   | 1.4      |        |

|      | SPI6 kernel          | 0.2  | 0.2                   | 0.2      |        |

|      | I2C4 registers       | 0.1  | 0.1                   | 0.1      |        |

|      | I2C4 kernel          | 2.4  | 2.1                   | 2        |        |

|      | LPTIM2 registers     | 0.5  | 0.5                   | 0.5      |        |

|      | LPTIM2 kernel        | 2.3  | 2.1                   | 1.8      |        |

|      | LPTIM3 registers     | 0.5  | 0.5                   | 0.5      |        |

| APB4 | LPTIM3 kernel        | 2    | 2.1                   | 1.5      | µA/MHz |

|      | LPTIM4 registers     | 0.5  | 0.5                   | 0.5      |        |

|      | LPTIM4 kernel        | 2    | 2                     | 1.9      |        |

|      | LPTIM5 registers     | 0.5  | 0.5                   | 0.5      |        |

|      | LPTIM5 kernel        | 2    | 1.8                   | 1.5      |        |

|      | COMP1/2              | 0.7  | 0.5                   | 0.5      |        |

|      | VREFBUF              | 0.6  | 0.4                   | 0.4      |        |

|      | RTC                  | 1.2  | 1.1                   | 1.1      |        |

|      | SAI4 registers       | 1.6  | 1.5                   | 1.4      |        |

|      | SAI4 kernel          | 1.3  | 1.3                   | 1.2      |        |

|      | Bridge APB4          | 0.1  | 0.1                   | 0.1      |        |

Table 38. Peripheral current consumption in Run mode (continued)

#### Table 39. Peripheral current consumption in Stop, Standby and VBAT mode

| Symbol          | Parameter                     | Conditions | Тур  | Unit |

|-----------------|-------------------------------|------------|------|------|

| Gymbol          | i arameter                    | Conditions | 3 V  | Onic |

|                 | RTC+LSE low drive             | -          | 2.32 |      |

| I <sub>DD</sub> | RTC+LSE medium-<br>low drive  | -          | 2.4  | μA   |

|                 | RTC+LSE medium-<br>high drive | -          | 2.7  | μ    |

|                 | RTC+LSE High drive            | -          | 3    |      |

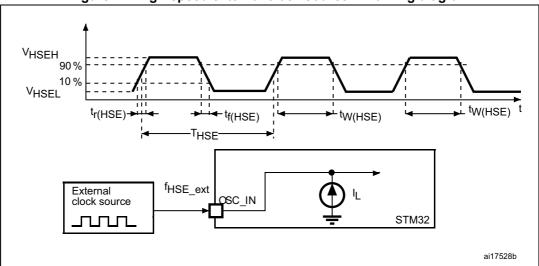

## 6.3.8 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard I/O.

The external clock signal has to respect the *Table 59: I/O static characteristics*. However, the recommended clock input waveform is shown in *Figure 17*.

| Symbol                                                    | Parameter                            | Min                | Тур | Max                | Unit |

|-----------------------------------------------------------|--------------------------------------|--------------------|-----|--------------------|------|

| f <sub>HSE_ext</sub>                                      | User external clock source frequency | 4                  | 25  | 50                 | MHz  |

| V <sub>SW</sub><br>(V <sub>HSEH</sub> -V <sub>HSEL)</sub> | OSC_IN amplitude                     | 0.7V <sub>DD</sub> | -   | V <sub>DD</sub>    | v    |

| V <sub>DC</sub>                                           | OSC_IN input voltage                 | $V_{SS}$           | -   | 0.3V <sub>SS</sub> |      |

| t <sub>W(HSE)</sub>                                       | OSC_IN high or low time              | 7                  | -   | -                  | ns   |

Table 41. High-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design.

| Symbol                     | Parameter                                  | Min                           | Мах | Unit |

|----------------------------|--------------------------------------------|-------------------------------|-----|------|

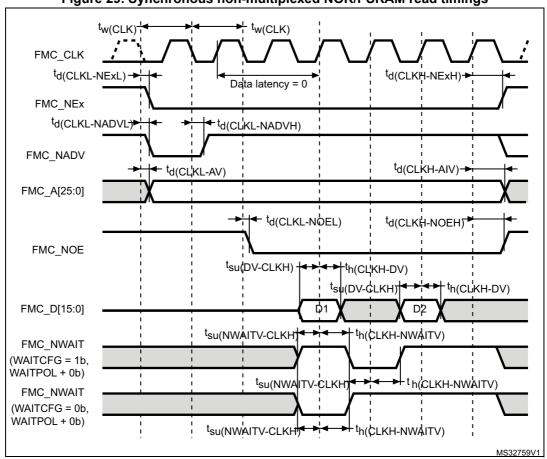

| t <sub>w(CLK)</sub>        | FMC_CLK period                             | 2T <sub>fmc_ker_ck</sub> – 1  | -   |      |

| t <sub>(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)          | -                             | 2   |      |

| t <sub>d(CLKH-NExH)</sub>  | FMC_CLK high to FMC_NEx high (x= 02)       | T <sub>fmc_ker_ck</sub> + 0.5 | -   |      |

| t <sub>d(CLKL-NADVL)</sub> | FMC_CLK low to FMC_NADV low                | -                             | 0.5 |      |

| t <sub>d(CLKL-NADVH)</sub> | FMC_CLK low to FMC_NADV high               | 0                             | -   |      |

| t <sub>d(CLKL-AV)</sub>    | FMC_CLK low to FMC_Ax valid (x=1625)       | -                             | 2   |      |

| t <sub>d(CLKH-AIV)</sub>   | FMC_CLK high to FMC_Ax invalid (x=1625)    | T <sub>fmc_ker_ck</sub>       | -   | ns   |

| t <sub>d(CLKL-NOEL)</sub>  | FMC_CLK low to FMC_NOE low                 | -                             | 1.5 |      |

| t <sub>d(CLKH-NOEH)</sub>  | FMC_CLK high to FMC_NOE high               | T <sub>fmc_ker_ck</sub> + 0.5 | -   |      |

| t <sub>su(DV-CLKH)</sub>   | FMC_D[15:0] valid data before FMC_CLK high | 2                             | -   |      |

| t <sub>h(CLKH-DV)</sub>    | FMC_D[15:0] valid data after FMC_CLK high  | 1                             | -   |      |

| t <sub>(NWAIT-CLKH)</sub>  | FMC_NWAIT valid before FMC_CLK high        | 2                             | -   |      |

| t <sub>h(CLKH-NWAIT)</sub> | FMC_NWAIT valid after FMC_CLK high         | 2                             | -   |      |

1. Guaranteed by characterization results.

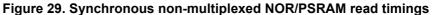

#### General PCB design guidelines

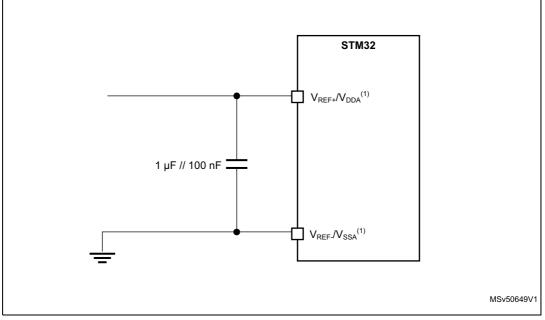

Power supply decoupling should be performed as shown in *Figure 41* or *Figure 42*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 100 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

Figure 41. Power supply and reference decoupling (V<sub>REF+</sub> not connected to V<sub>DDA</sub>)

1. V<sub>REF+</sub> input is available on all package whereas the V<sub>REF-</sub> s available only on UFBGA176+25 and TFBGA240+25. When V<sub>REF-</sub> is not available, it is internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

1. V<sub>REF+</sub> input is available on all package whereas the V<sub>REF-</sub> s available only on UFBGA176+25 and TFBGA240+25. When V<sub>REF-</sub> is not available, it is internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

# 6.3.24 V<sub>BAT</sub> monitoring characteristics

| Table 92. | VDAT  | monitoring | characteristics |

|-----------|-------|------------|-----------------|

|           | • BAI | monitoring | onunuotoristios |

| Symbol                             | Parameter                                      |     | Тур | Max | Unit |

|------------------------------------|------------------------------------------------|-----|-----|-----|------|

| R                                  | Resistor bridge for V <sub>BAT</sub>           | -   | 26  | -   | KΩ   |

| Q                                  | Ratio on V <sub>BAT</sub> measurement          |     | 4   | -   | -    |

| Er <sup>(1)</sup>                  | Error on Q                                     | -10 | -   | +10 | %    |

| t <sub>S_vbat</sub> <sup>(1)</sup> | ADC sampling time when reading $V_{BAT}$ input | 9   | -   | -   | μs   |

1. Guaranteed by design.

| Symbol          | Parameter Condition       |                    | Min | Тур | Мах | Unit |  |  |

|-----------------|---------------------------|--------------------|-----|-----|-----|------|--|--|

| R <sub>BC</sub> | Battery charging resistor | VBRS in PWR_CR3= 0 | -   | 5   | -   | ΚΩ   |  |  |

|                 |                           | VBRS in PWR_CR3= 1 |     | 1.5 | -   | K77  |  |  |

## Table 93. $V_{BAT}$ charging characteristics

## 6.3.25 Voltage booster for analog switch

| Symbol                 | Parameter            | Condition                        | Min  | Тур | Max | Unit |

|------------------------|----------------------|----------------------------------|------|-----|-----|------|

| V <sub>DD</sub>        | Supply voltage       | -                                | 1.62 | 2-6 | 3.6 | V    |

| t <sub>SU(BOOST)</sub> | Booster startup time | -                                | -    | -   | 50  | μs   |

| 1                      | Poostor consumption  | 1.62 V ≤ V <sub>DD</sub> ≤ 2.7 V | -    | -   | 125 |      |

| I <sub>DD(BOOST)</sub> | Booster consumption  | 2.7 V < V <sub>DD</sub> < 3.6 V  | -    | -   | 250 | μA   |

1. Guaranteed by characterization results.

| Symbol                  | Parameter              | Conditions             |                             | Min | Тур | Мах  | Unit |

|-------------------------|------------------------|------------------------|-----------------------------|-----|-----|------|------|

|                         | Voltage noise density  | at<br>1 KHz            | output loaded<br>with 4 kΩ  | -   | 140 | -    | nV/√ |

| en                      | Voltage noise density  | at<br>10 KHz           |                             | -   | 55  | -    | Hz   |

|                         | OPAMP consumption from | Normal<br>mode         | no Load,                    | -   | 570 | 1000 |      |

| I <sub>DDA(OPAMP)</sub> | V <sub>DDA</sub>       | High-<br>speed<br>mode | quiescent mode,<br>follower | -   | 610 | 1200 | μA   |

Table 96. OPAMP characteristics<sup>(1)</sup> (continued)

1. Guaranteed by design, unless otherwise specified.

2.  $R_{LOAD}$  is the resistive load connected to VSSA or to VDDA.

3. R2 is the internal resistance between the OPAMP output and th OPAMP inverting input. R1 is the internal resistance between the OPAMP inverting input and ground. PGA gain = 1 + R2/R1.

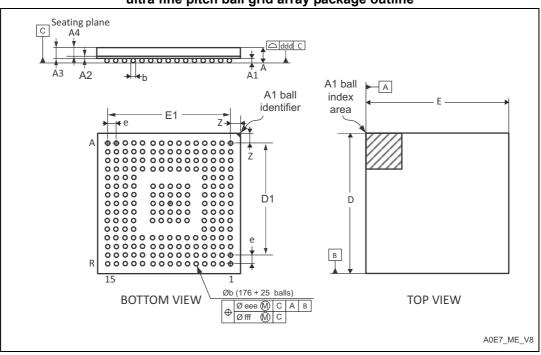

# 7.7 UFBGA176+25 package information

Figure 81. UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

| Table 123. UFBGA176+25 - ball, 10 x 10 mm, 0.65 mm pitch, |

|-----------------------------------------------------------|

| ultra fine pitch ball grid array package mechanical data  |

| Cumhal |       | millimeters |        | inches <sup>(1)</sup> |        |        |

|--------|-------|-------------|--------|-----------------------|--------|--------|

| Symbol | Min.  | Тур.        | Max.   | Min.                  | Тур.   | Max.   |

| А      | -     | -           | 0.600  | -                     | -      | 0.0236 |

| A1     | -     | -           | 0.110  | -                     | -      | 0.0043 |

| A2     | -     | 0.130       | -      | -                     | 0.0051 | -      |

| A3     | -     | 0.450       | -      | -                     | 0.0177 | -      |

| A4     | -     | 0.320       | -      | -                     | 0.0126 | -      |

| b      | 0.240 | 0.290       | 0.340  | 0.0094                | 0.0114 | 0.0134 |

| D      | 9.850 | 10.000      | 10.150 | 0.3878                | 0.3937 | 0.3996 |

| D1     | -     | 9.100       | -      | -                     | 0.3583 | -      |

| E      | 9.850 | 10.000      | 10.150 | 0.3878                | 0.3937 | 0.3996 |

| E1     | -     | 9.100       | -      | -                     | 0.3583 | -      |

| е      | -     | 0.650       | -      | -                     | 0.0256 | -      |

| Z      | -     | 0.450       | -      | -                     | 0.0177 | -      |

| ddd    | -     | -           | 0.080  | -                     | -      | 0.0031 |

| Date        | Revision      | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |               | Updated typical and maximum current consumption in <i>Table 36:</i><br><i>Typical and maximum current consumption in Standby mode</i><br>and <i>Table 37: Typical and maximum current consumption in</i><br><i>VBAT mode</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 18-May-2018 | 4 (continued) | <ul> <li>Added note to f<sub>LSI</sub> in <i>Table 48: LSI oscillator characteristics</i>.</li> <li>Updated <i>Figure 21: VIL/VIH for all I/Os except BOOT0</i>.</li> <li>Added note in <i>Table 82: Quad-SPI characteristics in SDR mode</i>, <i>Table 83: Quad SPI characteristics in DDR mode</i> and <i>Table 84: Dynamics characteristics: Delay Block characteristics</i>.</li> <li>Section 6.3.20: 16-bit ADC characteristics: updated THD conditions in <i>Table 86: ADC accuracy</i>; removed formula to compute R<sub>AIN</sub>.</li> <li>Changed decoupling capacitor value to 100 nF in <i>Section : General PCB design guidelines.</i>*</li> <li>Added note in <i>Table 87: DAC characteristics, Table 94: Voltage booster for analog switch characteristics and Table 97: DFSDM measured timing 1.62-3.6 V, Table 114: Dynamics characteristics: SWD characteristics.</i></li> <li>Updated <i>Figure 73: LQFP144 marking example (package top view)</i> and <i>Figure 80: LQFP208 marking example (package top view)</i>.</li> <li>Updated TFBGA240+25 package information to final mechanical data.</li> </ul> |

| 13-Jul-2018 | 5             | <ul> <li>Added description of power-up and power-down phases in Section 3.5.1: Power supply scheme.</li> <li>Removed ETH_TX_ER from Table 8: STM32H743xl pin/ball definition and Table 9: Port A alternate functions to Table 19: Port K alternate functions.</li> <li>Added note related to decoupling capacitor tolerance below Figure 14: Power supply scheme.</li> <li>Added note 2. related to CEXT in Table 24: VCAP operating conditions.</li> <li>Updated Table 45: HSI48 oscillator characteristics, Table 46: HSI oscillator characteristics and Table 47: CSI oscillator characteristics.</li> <li>Renamed Table 49 into "PLL characteristics (wide VCO frequency range)" and updated note 2 Added Table 50: PLL characteristics (medium VCO frequency range).</li> <li>Updated T<sub>coeff</sub> in Table 89: VREFBUF characteristics.</li> <li>Updated Table 96: OPAMP characteristics.</li> </ul>                                                                                                                                                                                                               |

| Table 129 | . Document | revision | history |

|-----------|------------|----------|---------|

|-----------|------------|----------|---------|

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics – All rights reserved

DS12110 Rev 5