Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                       |                                                                                                                    |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Product Status                | Active                                                                                                             |

| Core Processor                | ARM® Cortex®-M7                                                                                                    |

| Core Size                     | 32-Bit Single-Core                                                                                                 |

| Speed                         | 480MHz                                                                                                             |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I²C, IrDA, LINbus, MDIO, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                                  |

| Number of I/O                 | 140                                                                                                                |

| Program Memory Size           | 2MB (2M x 8)                                                                                                       |

| Program Memory Type           | FLASH                                                                                                              |

| EEPROM Size                   | -                                                                                                                  |

| RAM Size                      | 1M x 8                                                                                                             |

| Voltage - Supply<br>(Vcc/Vdd) | 1.62V ~ 3.6V                                                                                                       |

| Data Converters               | A/D 36x16b; D/A 2x12b                                                                                              |

| Oscillator Type               | Internal                                                                                                           |

| Operating<br>Temperature      | -40°C ~ 85°C (TA)                                                                                                  |

| Mounting Type                 | Surface Mount                                                                                                      |

| Package / Case                | 176-LQFP                                                                                                           |

| Supplier Device<br>Package    | 176-LQFP (24x24)                                                                                                   |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32h743iit6                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.3 Memories

## 3.3.1 Embedded Flash memory

The STM32H743xI devices embed up to 2 Mbytes of Flash memory that can be used for storing programs and data.

The Flash memory is organized as 266-bit Flash words memory that can be used for storing both code and data constants. Each word consists of:

- One Flash word (8 words, 32 bytes or 256 bits)

- 10 ECC bits.

The Flash memory is divided into two independent banks. Each bank is organized as follows:

- A 1-Mbyte user Flash memory block containing eight user sectors of 128 Kbytes(4 K Flash words)

- 128 Kbytes of System Flash memory from which the device can boot

- 2 Kbytes (64 Flash words) of user option bytes for user configuration

## 3.3.2 Embedded SRAM

All devices feature:

- 512 Kbytes of AXI-SRAM mapped onto AXI bus on D1 domain.

- SRAM1 mapped on D2 domain: 128 Kbytes

- SRAM2 mapped on D2 domain: 128 Kbytes

- SRAM3 mapped on D2 domain: 32 Kbytes

- SRAM4 mapped on D3 domain: 64 Kbytes

- 4 Kbytes of backup SRAM

The content of this area is protected against possible unwanted write accesses, and is retained in Standby or  $V_{BAT}$  mode.

RAM mapped to TCM interface (ITCM and DTCM):

Both ITCM and DTCM RAMs are 0 wait state memories. either They can be accessed either from the CPU or the MDMA (even in Sleep mode) through a specific AHB slave of the CPU(AHBP):

- 64 Kbytes of ITCM-RAM (instruction RAM)

This RAM is connected to ITCM 64-bit interface designed for execution of critical real-times routines by the CPU.

- 128 Kbytes of DTCM-RAM (2x 64-Kbyte DTCM-RAMs on 2x32-bit DTCM ports) The DTCM-RAM could be used for critical real-time data, such as interrupt service routines or stack/heap memory. Both DTCM-RAMs can be used in parallel (for load/store operations) thanks to the Cortex<sup>®</sup>-M7 dual issue capability.

The MDMA can be used to load code or data in ITCM or DTCM RAMs.

The  $V_{\mbox{CORE}}$  domain is split into the following power domains that can be independently switch off.

- D1 domain containing some peripherals and the Cortex<sup>®</sup>-M7 core.

- D2 domain containing a large part of the peripherals.

- D3 domain containing some peripherals and the system control.

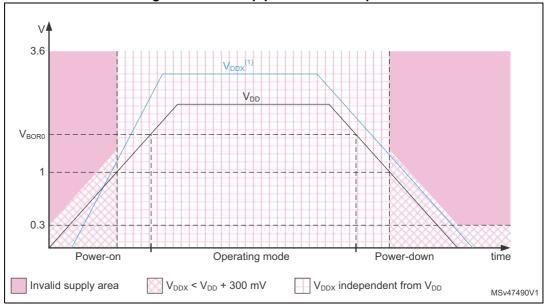

During power-up and power-down phases, the following power sequence requirements must be respected (see *Figure 2*):

- When  $V_{DD}$  is below 1 V, other power supplies ( $V_{DDA}$ ,  $V_{DD33USB}$ ,  $V_{DD50USB}$ ) must remain below  $V_{DD}$  + 300 mV.

- When V<sub>DD</sub> is above 1 V, all power supplies are independent.

During the power-down phase,  $V_{DD}$  can temporarily become lower than other supplies only if the energy provided to the microcontroller remains below 1 mJ. This allows external decoupling capacitors to be discharged with different time constants during the power-down transient phase.

Figure 2. Power-up/power-down sequence

1.  $V_{DDx}$  refers to any power supply among  $V_{DDA}$ ,  $V_{DD33USB}$ ,  $V_{DD50USB}$ .

## 3.5.2 Power supply supervisor

The devices have an integrated power-on reset (POR)/ power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry:

- Power-on reset (POR)

The POR supervisor monitors V<sub>DD</sub> power supply and compares it to a fixed threshold.

The devices remain in Reset mode when V<sub>DD</sub> is below this threshold,

- Power-down reset (PDR)

The PDR supervisor monitors V<sub>DD</sub> power supply. A reset is generated when V<sub>DD</sub> drops below a fixed threshold.

The PDR supervisor can be enabled/disabled through PDR\_ON pin.

Brownout reset (BOR)

The BOR supervisor monitors  $V_{DD}$  power supply. Three BOR thresholds (from 2.1 to 2.7 V) can be configured through option bytes. A reset is generated when  $V_{DD}$  drops below this threshold.

## 3.5.3 Voltage regulator

The same voltage regulator supplies the 3 power domains (D1, D2 and D3). D1 and D2 can be independently switched off.

Voltage regulator output can be adjusted according to application needs through 5 power supply levels:

- Run mode (VOS1 to VOS3)

- Scale 1: high performance

- Scale 2: medium performance and consumption

- Scale 3: optimized performance and low-power consumption

- Stop mode (SVOS3 to SVOS5)

- Scale 3: peripheral with wakeup from Stop mode capabilities (UART, SPI, I2C, LPTIM) are operational

- Scale 4 and 5 where the peripheral with wakeup from Stop mode is disabled The peripheral functionality is disabled but wakeup from Stop mode is possible through GPIO or asynchronous interrupt.

## 3.25 LCD-TFT controller

The LCD-TFT display controller provides a 24-bit parallel digital RGB (Red, Green, Blue) and delivers all signals to interface directly to a broad range of LCD and TFT panels up to XGA (1024x768) resolution with the following features:

- 2 display layers with dedicated FIFO (64x64-bit)

- Color Look-Up table (CLUT) up to 256 colors (256x24-bit) per layer

- Up to 8 input color formats selectable per layer

- Flexible blending between two layers using alpha value (per pixel or constant)

- Flexible programmable parameters for each layer

- Color keying (transparency color)

- Up to 4 programmable interrupt events

- AXI master interface with burst of 16 words

## 3.26 JPEG Codec (JPEG)

The JPEG Codec can encode and decode a JPEG stream as defined in the **ISO/IEC 10918-1** specification. It provides an fast and simple hardware compressor and decompressor of JPEG images with full management of JPEG headers.

The JPEG codec main features are as follows:

- 8-bit/channel pixel depths

- Single clock per pixel encoding and decoding

- Support for JPEG header generation and parsing

- Up to four programmable quantization tables

- Fully programmable Huffman tables (two AC and two DC)

- Fully programmable minimum coded unit (MCU)

- Encode/decode support (non simultaneous)

- Single clock Huffman coding and decoding

- Two-channel interface: Pixel/Compress In, Pixel/Compressed Out

- Support for single greyscale component

- Ability to enable/disable header processing

- Fully synchronous design

- Configuration for High-speed decode mode

## 3.27 Random number generator (RNG)

All devices embed an RNG that delivers 32-bit random numbers generated by an integrated analog circuit.

## 3.28 Timers and watchdogs

The devices include one high-resolution timer, two advanced-control timers, ten generalpurpose timers, two basic timers, five low-power timers, two watchdogs and a SysTick timer.

## 3.28.2 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (Edge- or Center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

TIM1 and TIM8 support independent DMA request generation.

### 3.28.3 General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32H743xI devices (see *Table 5* for differences).

### • TIM2, TIM3, TIM4, TIM5

The devices include 4 full-featured general-purpose timers: TIM2, TIM3, TIM4 and TIM5. TIM2 and TIM5 are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler while TIM3 and TIM4 are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. All timers feature 4 independent channels for input capture/output compare, PWM or One-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

TIM2, TIM3, TIM4 and TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

### • TIM12, TIM13, TIM14, TIM15, TIM16, TIM17

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM13, TIM14, TIM16 and TIM17 feature one independent channel, whereas TIM12 and TIM15 have two independent channels for input capture/output compare, PWM or One-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers or used as simple timebases.

All USART have a clock domain independent from the CPU clock, allowing the USARTx to wake up the MCU from Stop mode. The wakeup from Stop mode is programmable and can be done on:

- Start bit detection

- Any received data frame

- A specific programmed data frame

- Specific TXFIFO/RXFIFO status when FIFO mode is enabled.

All USART interfaces can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>              | USART1/2/3/6 | UART4/5/7/8 |

|--------------------------------------------------|--------------|-------------|

| Hardware flow control for modem                  | Х            | Х           |

| Continuous communication using DMA               | Х            | х           |

| Multiprocessor communication                     | Х            | Х           |

| Synchronous mode (Master/Slave)                  | Х            | -           |

| Smartcard mode                                   | Х            | -           |

| Single-wire Half-duplex communication            | Х            | Х           |

| IrDA SIR ENDEC block                             | Х            | Х           |

| LIN mode                                         | Х            | Х           |

| Dual clock domain and wakeup from low power mode | Х            | х           |

| Receiver timeout interrupt                       | Х            | Х           |

| Modbus communication                             | Х            | Х           |

| Auto baud rate detection                         | Х            | х           |

| Driver Enable                                    | Х            | Х           |

| USART data length                                | 7, 8 an      | d 9 bits    |

| Tx/Rx FIFO                                       | Х            | Х           |

| Tx/Rx FIFO size                                  | 1            | 6           |

### Table 6. USART features

1. X = supported.

# 3.32 Low-power universal asynchronous receiver transmitter (LPUART)

The device embeds one Low-Power UART (LPUART1). The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUARTs embed a Transmit FIFO (TXFIFO) and a Receive FIFO (RXFIFO). FIFO mode is enabled by software and is disabled by default.

\_

## 3.37 Management Data Input/Output (MDIO) slaves

The devices embed an MDIO slave interface it includes the following features:

- 32 MDIO Registers addresses, each of which is managed using separate input and output data registers:

- 32 x 16-bit firmware read/write, MDIO read-only output data registers

- 32 x 16-bit firmware read-only, MDIO write-only input data registers

- Configurable slave (port) address

- Independently maskable interrupts/events:

- MDIO Register write

- MDIO Register read

- MDIO protocol error

- Able to operate in and wake up from Stop mode

## 3.38 SD/SDIO/MMC card host interfaces (SDMMC)

Two SDMMC host interfaces are available. They support *MultiMediaCard System Specification Version 4.51* in three different databus modes: 1 bit (default), 4 bits and 8 bits.

Both interfaces support the *SD memory card specifications version 4.1.* and the *SDIO card specification version 4.0.* in two different databus modes: 1 bit (default) and 4 bits.

Each SDMMC host interface supports only one SD/SDIO/MMC card at any one time and a stack of MMC Version 4.51 or previous.

The SDMMC host interface embeds a dedicated DMA controller allowing high-speed transfers between the interface and the SRAM.

## 3.39 Controller area network (FDCAN1, FDCAN2)

The controller area network (CAN) subsystem consists of two CAN modules, a shared message RAM memory and a clock calibration unit.

Both CAN modules (FDCAN1 and FDCAN2) are compliant with ISO 11898-1 (CAN protocol specification version 2.0 part A, B) and CAN FD protocol specification version 1.0.

FDCAN1 supports time triggered CAN (TTCAN) specified in ISO 11898-4, including event synchronized time-triggered communication, global system time, and clock drift compensation. The FDCAN1 contains additional registers, specific to the time triggered feature. The CAN FD option can be used together with event-triggered and time-triggered CAN communication.

A 10-Kbyte message RAM memory implements filters, receive FIFOs, receive buffers, transmit event FIFOs, transmit buffers (and triggers for TTCAN). This message RAM is shared between the two FDCAN1 and FDCAN2 modules.

The common clock calibration unit is optional. It can be used to generate a calibrated clock for both FDCAN1 and FDCAN2 from the HSI internal RC oscillator and the PLL, by evaluating CAN messages received by the FDCAN1.

|         |          |         | Pin/ba   | all nam     | e       |         |              |                                          |          |               |       |                                                                                                                                                                           |                                 |

|---------|----------|---------|----------|-------------|---------|---------|--------------|------------------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| LQFP100 | TFBGA100 | LQFP144 | UFBGA169 | UFBGA176+25 | LQFP176 | LQFP208 | TFBGA240 +25 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                                       | Additional<br>functions         |

| 1       | A3       | 1       | A2       | A2          | 1       | 1       | C3           | PE2                                      | I/O      | FT_h          | -     | TRACECLK, SAI1_CK1,<br>SPI4_SCK,<br>SAI1_MCLK_A,<br>SAI4_MCLK_A,<br>QUADSPI_BK1_IO2,<br>SAI4_CK1,<br>ETH_MII_TXD3,<br>FMC_A23, EVENTOUT                                   | -                               |

| 2       | В3       | 2       | B2       | A1          | 2       | 2       | D3           | PE3                                      | I/O      | FT_h          | -     | TRACED0, TIM15_BKIN,<br>SAI1_SD_B, SAI4_SD_B,<br>FMC_A19, EVENTOUT                                                                                                        | -                               |

| 3       | C3       | 3       | A1       | B1          | 3       | 3       | D2           | PE4                                      | I/O      | FT_h          | -     | TRACED1, SAI1_D2,<br>DFSDM_DATIN3,<br>TIM15_CH1N,<br>SPI4_NSS, SAI1_FS_A,<br>SAI4_FS_A, SAI4_D2,<br>FMC_A20, DCMI_D4,<br>LCD_B0, EVENTOUT                                 | -                               |

| 4       | D3       | 4       | C3       | B2          | 4       | 4       | D1           | PE5                                      | I/O      | FT_h          | -     | TRACED2, SAI1_CK2,<br>DFSDM_CKIN3,<br>TIM15_CH1, SPI4_MISO,<br>SAI1_SCK_A,<br>SAI4_SCK_A, SAI4_CK2,<br>FMC_A21, DCMI_D6,<br>LCD_G0, EVENTOUT                              | -                               |

| 5       | E3       | 5       | C2       | В3          | 5       | 5       | E5           | PE6                                      | I/O      | FT_h          | -     | TRACED3, TIM1_BKIN2,<br>SAI1_D1, TIM15_CH2,<br>SPI4_MOSI, SAI1_SD_A,<br>SAI4_SD_A, SAI4_D1,<br>SAI2_MCK_B,<br>TIM1_BKIN2_COMP12,<br>FMC_A22, DCMI_D7,<br>LCD_G1, EVENTOUT | -                               |

| -       | -        | -       | M4       | H10         | -       | -       | A1           | VSS                                      | S        | -             | -     | -                                                                                                                                                                         | -                               |

| -       | -        | -       | A3       | -           | -       | -       | -            | VDD                                      | S        | -             | -     | -                                                                                                                                                                         | -                               |

| 6       | B2       | 6       | E3       | C1          | 6       | 6       | B1           | VBAT                                     | S        | -             | -     | -                                                                                                                                                                         | -                               |

| -       | -        | -       | -        | J6          | -       | -       | B2           | VSS                                      | -        | -             | -     | -                                                                                                                                                                         | -                               |

| -       | -        | -       | -        | D2          | 7       | 7       | E4           | PI8                                      | I/O      | FT            | -     | EVENTOUT                                                                                                                                                                  | RTC_TAMP_2/<br>RTC_TS/<br>WKUP3 |

| 7       | A2       | 7       | D3       | D1          | 8       | 8       | E3           | PC13                                     | I/O      | FT            | -     | EVENTOUT                                                                                                                                                                  | RTC_TAMP_1/<br>RTC_TS/<br>WKUP2 |

| -       | -        | -       | -        | J7          | -       | -       | B6           | VSS                                      | -        | -             | -     | -                                                                                                                                                                         | -                               |

Table 8. STM32H743xI pin/ball definition

STM32H743xI

DS12110 Rev 5

577

85/231

|      |         |                                    |                                 |                                                       |                                                          | Table '                    | 11. Port (                                 | C alterna                                      | ate funct                                                   | tions                                                                             |                                                                        |                                                                             |                                                     |                            |               |              |

|------|---------|------------------------------------|---------------------------------|-------------------------------------------------------|----------------------------------------------------------|----------------------------|--------------------------------------------|------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------|----------------------------|---------------|--------------|

|      | AF0     | AF1                                | AF2                             | AF3                                                   | AF4                                                      | AF5                        | AF6                                        | AF7                                            | AF8                                                         | AF9                                                                               | AF10                                                                   | AF11                                                                        | AF12                                                | AF13                       | AF14          | AF15         |

| Port | SYS     | TIM1/2/16/1<br>7/LPTIM1/<br>HRTIM1 | SAI1/TIM3/<br>4/5/12/<br>HRTIM1 | LPUART/<br>TIM8/<br>LPTIM2/3/4<br>/5/HRTIM1/<br>DFSDM | I2C1/2/3/4/<br>USART1/<br>TIM15/<br>LPTIM2/<br>DFSDM/CEC | SPI1/2/3/4/<br>5/6/CEC     | SPI2/3/SAI1<br>/3/I2C4/<br>UART4/<br>DFSDM | SPI2/3/6/<br>USART1/2/<br>3/6/UART7/<br>SDMMC1 | SPI6/SAI2/<br>4/UART4/5/<br>8/LPUART/<br>SDMMC1/<br>SPDIFRX | SAI4/<br>FDCAN1/2/<br>TIM13/14/<br>QUADSPI/<br>FMC/<br>SDMMC2/<br>LCD/<br>SPDIFRX | SAI2/4/<br>TIM8/<br>QUADSPI/<br>SDMMC2/<br>OTG1_HS/<br>OTG2_FS/<br>LCD | I2C4/<br>UART7/<br>SWPMI1/<br>TIM1/8/<br>DFSDM/<br>SDMMC2/<br>MDIOS/<br>ETH | TIM1/8/FMC<br>/SDMMC1/<br>MDIOS/<br>OTG1_FS/<br>LCD | TIM1/DCMI<br>/LCD/<br>COMP | UART5/<br>LCD | SYS          |

| PC0  | -       | -                                  | -                               | DFSDM_<br>CKIN0                                       | -                                                        | -                          | DFSDM_<br>DATIN4                           | -                                              | SAI2_FS_B                                                   | -                                                                                 | OTG_HS_<br>ULPI_STP                                                    | -                                                                           | FMC_<br>SDNWE                                       | -                          | LCD_R5        | EVEN<br>OUT  |

| PC1  | TRACED0 | -                                  | SAI1_D1                         | DFSDM_<br>DATIN0                                      | DFSDM_<br>CKIN4                                          | SPI2_<br>MOSI/I2S2<br>_SDO | SAI1_SD_A                                  | -                                              | SAI4_SD_<br>A                                               | SDMMC2_<br>CK                                                                     | SAI4_D1                                                                | ETH_MDC                                                                     | MDIOS_<br>MDC                                       | -                          | -             | EVENT<br>OUT |

| PC2  | -       | -                                  | -                               | DFSDM_<br>CKIN1                                       | -                                                        | SPI2_<br>MISO/I2S2<br>_SDI | DFSDM_CK<br>OUT                            | -                                              | -                                                           | -                                                                                 | OTG_HS_<br>ULPI_DIR                                                    | ETH_MII_<br>TXD2                                                            | FMC_SDNE<br>0                                       | -                          | -             | EVEN<br>OUT  |

| PC3  | -       | -                                  | -                               | DFSDM_<br>DATIN1                                      | -                                                        | SPI2_<br>MOSI/I2S2<br>_SDO | -                                          | -                                              | -                                                           | -                                                                                 | OTG_HS_<br>ULPI_NXT                                                    | ETH_MII_<br>TX_CLK                                                          | FMC_SDCK<br>E0                                      | -                          | -             | EVEN<br>OUT  |

| PC4  | -       | -                                  | -                               | DFSDM_<br>CKIN2                                       | -                                                        | I2S1_MCK                   | -                                          | -                                              | -                                                           | SPDIFRX_<br>IN2                                                                   | -                                                                      | ETH_MII_<br>RXD0/ETH_<br>RMII_RXD0                                          | FMC_SDNE<br>0                                       | -                          | -             | EVEN<br>OUT  |

| PC5  | -       | -                                  | SAI1_D3                         | DFSDM_<br>DATIN2                                      | -                                                        | -                          | -                                          | -                                              |                                                             | SPDIFRX_<br>IN3                                                                   | SAI4_D3                                                                | ETH_MII_<br>RXD1/ETH_<br>RMII_RXD1                                          | FMC_SDCK<br>E0                                      | COMP_1_<br>OUT             | -             | EVEN<br>OUT  |

| PC6  | -       | HRTIM_CH<br>A1                     | TIM3_CH1                        | TIM8_CH1                                              | DFSDM_<br>CKIN3                                          | I2S2_MCK                   | -                                          | USART6_<br>TX                                  | SDMMC1_<br>D0DIR                                            | FMC_<br>NWAIT                                                                     | SDMMC2_<br>D6                                                          | -                                                                           | SDMMC1_<br>D6                                       | DCMI_D0                    | LCD_<br>HSYNC | EVEN<br>OUT  |

| PC7  | TRGIO   | HRTIM_CH<br>A2                     | TIM3_CH2                        | TIM8_CH2                                              | DFSDM_<br>DATIN3                                         | -                          | I2S3_MCK                                   | USART6_<br>RX                                  | SDMMC1_<br>D123DIR                                          | FMC_NE1                                                                           | SDMMC2_<br>D7                                                          | SWPMI_TX                                                                    | SDMMC1_<br>D7                                       | DCMI_D1                    | LCD_G6        | EVEN<br>OUT  |

| PC8  | TRACED1 | HRTIM_CH<br>B1                     | TIM3_CH3                        | TIM8_CH3                                              | -                                                        | -                          | -                                          | USART6_<br>CK                                  | UART5_<br>RTS                                               | FMC_NE2/<br>FMC_NCE                                                               | -                                                                      | SWPMI_RX                                                                    | SDMMC1_<br>D0                                       | DCMI_D2                    | -             | EVEN<br>OUT  |

| PC9  | MCO2    | -                                  | TIM3_CH4                        | TIM8_CH4                                              | I2C3_SDA                                                 | I2S_CKIN                   | -                                          | -                                              | UART5_<br>CTS                                               | QUADSPI_<br>BK1_IO0                                                               | LCD_G3                                                                 | SWPMI_<br>SUSPEND                                                           | SDMMC1_<br>D1                                       | DCMI_D3                    | LCD_B2        | EVEN<br>OUT  |

| PC10 | -       | -                                  | HRTIM_<br>EEV1                  | DFSDM_<br>CKIN5                                       | -                                                        | -                          | SPI3_SCK/<br>I2S3_CK                       | USART3_<br>TX                                  | UART4_TX                                                    | QUADSPI_<br>BK1_IO1                                                               | -                                                                      | -                                                                           | SDMMC1_<br>D2                                       | DCMI_D8                    | LCD_R2        | EVEN<br>OUT  |

| PC11 | -       | -                                  | HRTIM_<br>FLT2                  | DFSDM_<br>DATIN5                                      | -                                                        | -                          | SPI3_MISO/<br>I2S3_SDI                     | USART3_<br>RX                                  | UART4_RX                                                    | QUADSPI_<br>BK2_NCS                                                               | -                                                                      | -                                                                           | SDMMC1_<br>D3                                       | DCMI_D4                    | -             | EVEN<br>OUT  |

| PC12 | TRACED3 | -                                  | HRTIM_<br>EEV2                  | -                                                     | -                                                        | -                          | SPI3_MOSI/<br>I2S3_SDO                     | USART3_<br>CK                                  | UART5_TX                                                    | -                                                                                 | -                                                                      | -                                                                           | SDMMC1_<br>CK                                       | DCMI_D9                    | -             | EVEN<br>OUT  |

| PC13 | -       | -                                  | -                               | -                                                     | -                                                        | -                          | -                                          | -                                              | -                                                           | -                                                                                 | -                                                                      | -                                                                           | -                                                   | -                          | -             | EVEN<br>OUT  |

Pin descriptions

| Symbol                   | Parameter             | Conditions | Min | Тур | Max | Unit         |  |

|--------------------------|-----------------------|------------|-----|-----|-----|--------------|--|

| V <sub>REFINT_DIV1</sub> | 1/4 reference voltage | -          | -   | 25  | -   |              |  |

| V <sub>REFINT_DIV2</sub> | 1/2 reference voltage | -          | -   | 50  | -   | %<br>Vreeint |  |

| V <sub>REFINT_DIV3</sub> | 3/4 reference voltage | -          | -   | 75  | -   | VREFINT      |  |

Table 27. Embedded reference voltage (continued)

1. The shortest sampling time for the application can be determined by multiple iterations.

2. Guaranteed by design.

| Table 28. | Internal | reference | voltage | calibration values | s |

|-----------|----------|-----------|---------|--------------------|---|

|           | meena    | 101010100 | vonago  |                    | • |

| Symbol          | Parameter                                                    | Memory address      |

|-----------------|--------------------------------------------------------------|---------------------|

| $V_{REFIN}$ CAL | Raw data acquired at temperature of 30 °C, $V_{DDA}$ = 3.3 V | 1FF1E860 - 1FF1E861 |

## 6.3.6 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 15: Current consumption measurement scheme*.

All the run-mode current consumption measurements given in this section are performed with a CoreMark code.

### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in analog input mode.

- All peripherals are disabled except when explicitly mentioned.

- The Flash memory access time is adjusted with the minimum wait states number, depending on the f<sub>ACLK</sub> frequency (refer to the table "Number of wait states according to CPU clock (f<sub>rcc c ck</sub>) frequency and V<sub>CORE</sub> range" available in the reference manual).

- When the peripherals are enabled, the AHB clock frequency is the CPU frequency divided by 2 and the APB clock frequency is AHB clock frequency divided by 2.

The parameters given in *Table 29* to *Table 37* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

### On-chip peripheral current consumption

The MCU is placed under the following conditions:

- At startup, all I/O pins are in analog input configuration.

- All peripherals are disabled unless otherwise mentioned.

- The I/O compensation cell is enabled.

- $f_{rcc\_c\_ck}$  is the CPU clock.  $f_{PCLK} = f_{rcc\_c\_ck}/4$ , and  $f_{HCLK} = f_{rcc\_c\_ck}/2$ .

- The given value is calculated by measuring the difference of current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- $f_{rcc\_c\_ck} = 400 \text{ MHz} \text{ (Scale 1), } f_{rcc\_c\_ck} = 300 \text{ MHz} \text{ (Scale 2),} \\ f_{rcc\_c\_ck} = 200 \text{ MHz} \text{ (Scale 3)}$

- The ambient operating temperature is 25  $^\circ$ C and V<sub>DD</sub>=3.3 V.

| Symbol                  | Parameter                   | Conditions                     | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------------|-----------------------------|--------------------------------|--------------------|-----|--------------------|------|

|                         |                             | Program/erase parallelism x 8  | -                  | 290 | 580 <sup>(2)</sup> |      |

| +                       | Word (266 bits) programming | Program/erase parallelism x 16 | -                  | 180 | 360                |      |

| t <sub>prog</sub>       | time                        | Program/erase parallelism x 32 | -                  | 130 | 260                | μs   |

|                         |                             | Program/erase parallelism x 64 | -                  | 100 | 200                |      |

|                         |                             | Program/erase parallelism x 8  | -                  | 2   | 4                  |      |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time  | Program/erase parallelism x 16 | -                  | 1.8 | 3.6                |      |

|                         |                             | Program/erase parallelism x 32 | -                  |     |                    |      |

|                         | Mass erase time             | Program/erase parallelism x 8  | -                  | 13  | 26                 | s    |

| +                       |                             | Program/erase parallelism x 16 | -                  | 8   | 16                 |      |

| t <sub>ME</sub>         |                             | Program/erase parallelism x 32 | -                  | 6   | 12                 |      |

|                         |                             | Program/erase parallelism x 64 | -                  | 5   | 10                 |      |

|                         |                             | Program parallelism x 8        |                    |     |                    |      |

| V                       | Brogramming voltage         | Program parallelism x 16       | 1.62               | -   | 3.6                | V    |

| V <sub>prog</sub>       | Programming voltage         | Program parallelism x 32       |                    |     |                    | v    |

|                         |                             | Program parallelism x 64       | 1.8                | -   | 3.6                |      |

| Table 52. Flash memory programming | (single bank configuration nDBANK=1) |

|------------------------------------|--------------------------------------|

|                                    |                                      |

1. Guaranteed by characterization results.

2. The maximum programming time is measured after 10K erase operations.

| Querra ha a l    | Devenuetor     | Conditions                                 | Value              | Unit    |  |

|------------------|----------------|--------------------------------------------|--------------------|---------|--|

| Symbol           | Parameter      | Conditions                                 | Min <sup>(1)</sup> | Unit    |  |

| N <sub>END</sub> | Endurance      | $T_J = -40$ to +125 °C (6 suffix versions) | 10                 | kcycles |  |

| +                | Data retention | 1 kcycle at T <sub>A</sub> = 85 °C         | 30                 | Years   |  |

| <sup>t</sup> RET |                | 10 kcycles at T <sub>A</sub> = 55 °C       | 20                 | Teals   |  |

## Table 53. Flash memory endurance and data retention

1. Guaranteed by characterization results.

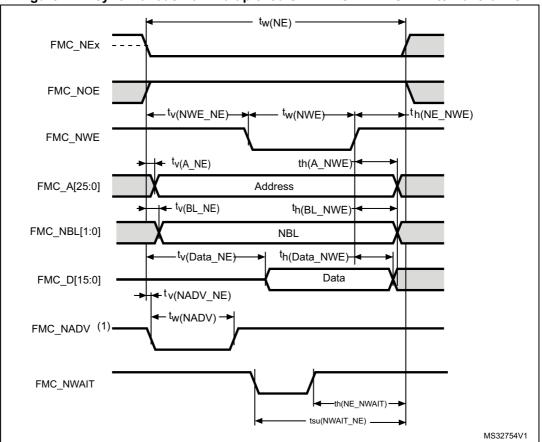

Figure 24. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

| Table 66. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings <sup>(1)</sup> |

|------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------|

| Symbol                   | Parameter                                                | Min                           | Max                           | Unit |

|--------------------------|----------------------------------------------------------|-------------------------------|-------------------------------|------|

| t <sub>w(NE)</sub>       | FMC_NE low time                                          | 3T <sub>fmc_ker_ck</sub> − 1  | 3T <sub>fmc_ker_ck</sub>      |      |

| t <sub>v(NWE_NE)</sub>   | FMC_NEx low to FMC_NWE low                               | T <sub>fmc_ker_ck</sub>       | T <sub>fmc_ker_ck</sub> + 1   |      |

| t <sub>w(NWE)</sub>      | FMC_NWE low time                                         | T <sub>fmc_ker_ck</sub> - 0.5 | T <sub>fmc_ker_ck</sub> + 0.5 |      |

| t <sub>h(NE_NWE)</sub>   | FMC_NWE high to FMC_NE high hold time                    | T <sub>fmc_ker_ck</sub>       | -                             |      |

| t <sub>v(A_NE)</sub>     | FMC_NEx low to FMC_A valid -                             |                               | 2                             |      |

| t <sub>h(A_NWE)</sub>    | Address hold time after FMC_NWE high T <sub>fmc_ke</sub> |                               | -                             | 20   |

| t <sub>v(BL_NE)</sub>    | FMC_NEx low to FMC_BL valid                              | -                             | 0.5                           | ns   |

| t <sub>h(BL_NWE)</sub>   | FMC_BL hold time after FMC_NWE high                      | T <sub>fmc_ker_ck</sub> - 0.5 | -                             |      |

| t <sub>v(Data_NE)</sub>  | Data to FMC_NEx low to Data valid                        | -                             | T <sub>fmc_ker_ck</sub> + 2.5 |      |

| t <sub>h(Data_NWE)</sub> | Data hold time after FMC_NWE high                        | T <sub>fmc_ker_ck</sub> +0.5  | -                             |      |

| t <sub>v(NADV_NE)</sub>  | FMC_NEx low to FMC_NADV low                              | -                             | 0                             |      |

| t <sub>w(NADV)</sub>     | FMC_NADV low time                                        | -                             | T <sub>fmc_ker_ck</sub> + 1   |      |

1. Guaranteed by characterization results.

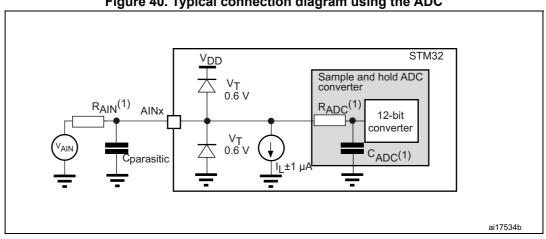

Figure 40. Typical connection diagram using the ADC

- Refer to *Table 85* for the values of  $R_{AIN}$ ,  $R_{ADC}$  and  $C_{ADC}$ . 1.

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 5 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced. 2.

## 6.3.21 DAC electrical characteristics

| Symbol                             | Parameter                                                                                                                                                                                                | Cond                                      | Min                              | Тур                | Max              | Unit                      |    |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------|--------------------|------------------|---------------------------|----|

| V <sub>DDA</sub>                   | Analog supply voltage                                                                                                                                                                                    | -                                         |                                  | 1.8                | 3.3              | 3.6                       |    |

| V <sub>REF+</sub>                  | Positive reference voltage                                                                                                                                                                               | -                                         |                                  | 1.80               | -                | V <sub>DDA</sub>          | v  |

| V <sub>REF-</sub>                  | Negative reference voltage                                                                                                                                                                               | -                                         |                                  | -                  | V <sub>SSA</sub> | -                         |    |

| RL                                 | Resistive Load                                                                                                                                                                                           | DAC output                                | connected to<br>V <sub>SSA</sub> | 5                  | -                | -                         | kΩ |

|                                    |                                                                                                                                                                                                          | buffer ON                                 | connected to<br>V <sub>DDA</sub> | 25                 | -                | -                         |    |

| $R_0^{(2)}$                        | Output Impedance                                                                                                                                                                                         | DAC output                                | t buffer OFF                     | 10.3               | 13               | 16                        |    |

|                                    | Output impedance sample                                                                                                                                                                                  | DAC output<br>buffer ON                   | V <sub>DD</sub> = 2.7 V          | -                  | -                | 1.6                       | kΩ |

| R <sub>BON</sub>                   | and hold mode, output<br>buffer ON                                                                                                                                                                       |                                           | V <sub>DD</sub> = 2.0 V          | -                  | -                | 2.6                       |    |

| R <sub>BOFF</sub>                  | Output impedance sample<br>and hold mode, output<br>buffer OFF                                                                                                                                           | DAC output<br>buffer OFF                  | V <sub>DD</sub> = 2.7 V          | -                  | -                | 17.8                      | kΩ |

|                                    |                                                                                                                                                                                                          |                                           | V <sub>DD</sub> = 2.0 V          | -                  | -                | 18.7                      |    |

| C <sub>L</sub> <sup>(2)</sup>      |                                                                                                                                                                                                          | DAC output buffer OFF                     |                                  | -                  | -                | 50                        | pF |

| C <sub>SH</sub> <sup>(2)</sup>     | Capacitive Load Sample and Hold mode                                                                                                                                                                     |                                           | Hold mode                        | -                  | 0.1              | 1                         | μF |

| V <sub>DAC_OUT</sub>               | Voltage on DAC_OUT                                                                                                                                                                                       | DAC output buffer ON                      |                                  | 0.2                | -                | V <sub>REF+</sub><br>-0.2 | v  |

|                                    | ouipui                                                                                                                                                                                                   | DAC output buffer OFF                     |                                  | 0                  | -                | $V_{REF^+}$               |    |

| tSETTLING                          | Settling time (full scale: for<br>a 12-bit code transition<br>between the lowest and<br>the highest input codes<br>when DAC_OUT reaches<br>the final value of ±0.5LSB,<br>±1LSB, ±2LSB, ±4LSB,<br>±8LSB) | Normal mode, D<br>OFF, ±1LS               | -                                | 1.7 <sup>(2)</sup> | 2 <sup>(2)</sup> | μs                        |    |

| t <sub>WAKEUP</sub> <sup>(3)</sup> | Wakeup time from off<br>state (setting the Enx bit in<br>the DAC Control register)<br>until the ±1LSB final value                                                                                        | Normal mode, D<br>ON, C <sub>L</sub> ≤ 50 | -                                | 5                  | 7.5              | μs                        |    |

| V <sub>offset</sub> <sup>(2)</sup> | Middle code offset for 1                                                                                                                                                                                 | V <sub>REF+</sub> = 3.6 V                 |                                  | -                  | 850              | -                         | μV |

| ⊻offset` ′                         | trim code step                                                                                                                                                                                           | V <sub>REF+</sub> = 1.8 V                 |                                  | -                  | 425              | -                         | μν |

| Table 87. | DAC | characteristics <sup>(1)</sup> |

|-----------|-----|--------------------------------|

|-----------|-----|--------------------------------|

| Symbol                  | Parameter              | Conditions             |                             | Min | Тур | Мах  | Unit       |

|-------------------------|------------------------|------------------------|-----------------------------|-----|-----|------|------------|

| en                      | Voltage noise density  | at<br>1 KHz            | output loaded               | -   | 140 | -    | nV/√<br>Hz |

|                         |                        | at<br>10 KHz           | with 4 kΩ                   | -   | 55  | -    |            |

| I <sub>DDA(OPAMP)</sub> | OPAMP consumption from | Normal<br>mode         | no Load,                    | -   | 570 | 1000 |            |

|                         | V <sub>DDA</sub>       | High-<br>speed<br>mode | quiescent mode,<br>follower | -   | 610 | 1200 | μA         |

Table 96. OPAMP characteristics<sup>(1)</sup> (continued)

1. Guaranteed by design, unless otherwise specified.

2.  $R_{LOAD}$  is the resistive load connected to VSSA or to VDDA.

3. R2 is the internal resistance between the OPAMP output and th OPAMP inverting input. R1 is the internal resistance between the OPAMP inverting input and ground. PGA gain = 1 + R2/R1.

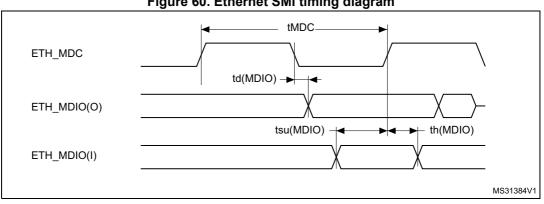

Figure 60. Ethernet SMI timing diagram

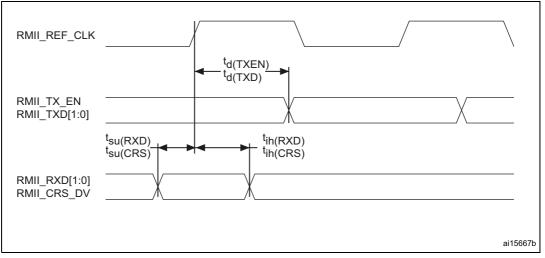

Table 112 gives the list of Ethernet MAC signals for the RMII and Figure 61 shows the corresponding timing diagram.

| Symbol               | Parameter                        | Min | Тур | Мах  | Unit |

|----------------------|----------------------------------|-----|-----|------|------|

| t <sub>su(RXD)</sub> | Receive data setup time          | 2   | -   | -    |      |

| t <sub>ih(RXD)</sub> | Receive data hold time           | 3   | -   | -    |      |

| t <sub>su(CRS)</sub> | Carrier sense setup time         | 2.5 | -   | -    | ns   |

| t <sub>ih(CRS)</sub> | Carrier sense hold time          | 2   | -   | -    | 115  |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time | 4   | 4.5 | 7    |      |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | 7   | 7.5 | 11.5 |      |

Table 112. Dynamics characteristics: Ethernet MAC signals for RMII<sup>(1)</sup>

1. Guaranteed by characterization results.

Table 113 gives the list of Ethernet MAC signals for MII and Figure 62 shows the corresponding timing diagram.

| 9···· ··· · · · · · · · · · · · · · · · |             |       |       |                       |        |        |  |

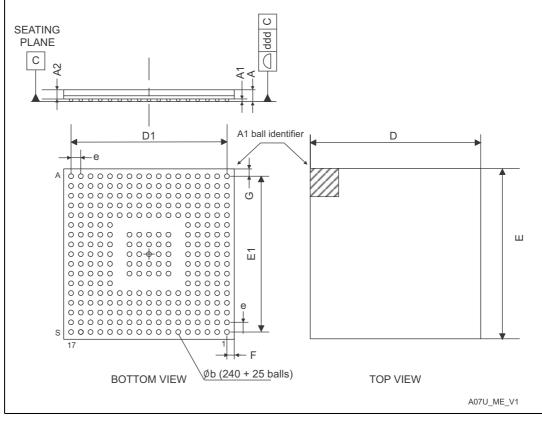

|-----------------------------------------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol                                  | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|                                         | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |  |

| F                                       | 0.450       | 0.500 | 0.550 | 0.0177                | 0.0197 | 0.0217 |  |

| ddd                                     | -           | -     | 0.100 | -                     | -      | 0.0039 |  |

| eee                                     | -           | -     | 0.150 | -                     | -      | 0.0059 |  |

| fff                                     | -           | -     | 0.050 | -                     | -      | 0.0020 |  |

## Table 120. UFBGA169 - 169-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ballgrid array package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

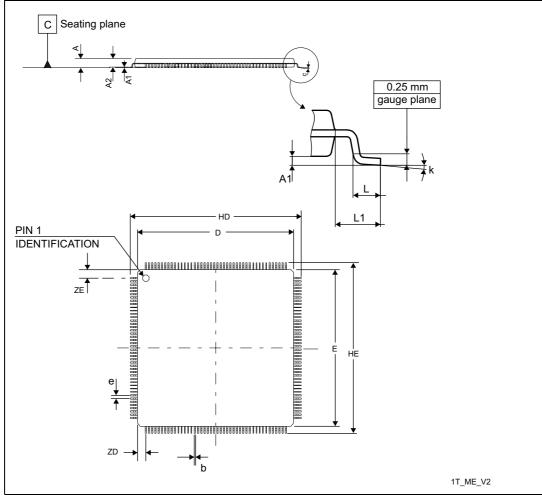

## 7.5 LQFP176 package information

### Figure 75. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline

1. Drawing is not to scale.

DS12110 Rev 5

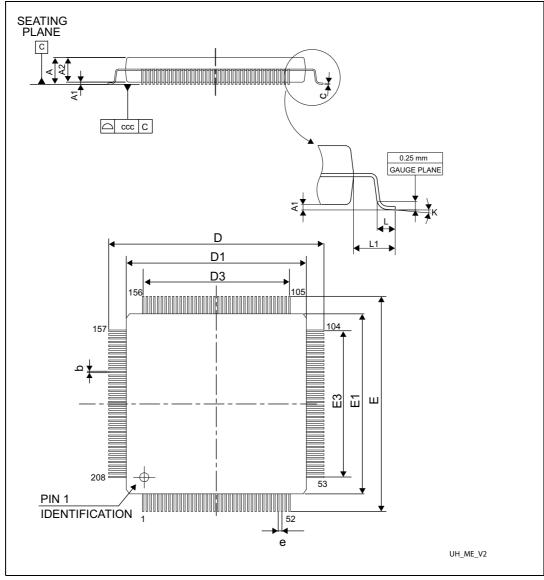

## 7.6 LQFP208 package information

Figure 78. LQFP208 - 208-pin, 28 x 28 mm low-profile quad flat package outline

1. Drawing is not to scale.

## 7.8 **TFBGA240+25** package information

Figure 84. TFBGA - 240+25 ball, 14x14 mm, 0.8 mm pitch, fine pitch ball grid array package outline

1. Dimensions are expressed in millimeters.