#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | C1665V2                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20MHz                                                                           |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                        |

| Peripherals                | PWM, WDT                                                                        |

| Number of I/O              | 79                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.7V                                                                    |

| Data Converters            | -                                                                               |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | PG-TQFP-100-16                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc164n-16f20f-bb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1                                                                                                                               | Summary of Features 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2                                                                                                          | General Device Information       4         Introduction       4         Pin Configuration and Definition       5                                                                                                                                                                                                                                                                                                                                                                      |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16 | Functional Description14Memory Subsystem and Organization15External Bus Controller17Central Processing Unit (CPU)18Interrupt System20On-Chip Debug Support (OCDS)25Capture/Compare Units (CAPCOM1/2)26The Capture/Compare Unit CAPCOM629General Purpose Timer (GPT12E) Unit30Real Time Clock33Asynchronous/Synchronous Serial Interfaces (ASC0/ASC1)36High Speed Synchronous Serial Channels (SSC0/SSC1)36Watchdog Timer37Parallel Ports37Power Management40Instruction Set Summary41 |

| <b>4</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5                                                                                     | Electrical Parameters43Absolute Maximum Ratings43Package Properties43Operating Conditions44Parameter Interpretation45DC Parameters46                                                                                                                                                                                                                                                                                                                                                  |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4                                                                                            | Timing Parameters52Definition of Internal Timing52External Clock Drive XTAL155Testing Waveforms56AC Characteristics57                                                                                                                                                                                                                                                                                                                                                                 |

| 6                                                                                                                               | <b>Packaging</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Table 2   Pin Definitions and Functions |             |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-----------------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbo<br>I                              | Pin<br>Num. | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| RSTIN                                   | 1           | 1              | Reset Input with Schmitt-Trigger characteristics. A low level<br>at this pin while the oscillator is running resets the XC164N.<br>A spike filter suppresses input pulses <10 ns. Input pulses<br>>100 ns safely pass the filter. The minimum duration for a<br>safe recognition should be 100 ns + 2 CPU clock cycles.<br><i>Note: The reset duration must be sufficient to let the<br/>hardware configuration signals settle.</i><br><u>External circuitry must guarantee low level at the<br/>RSTIN pin at least until both power supply voltages<br/>have reached the operating range.</u> |  |

| P20.12                                  | 2           | 10             | For details, please refer to the description of P20.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| NMI                                     | 3           | 1              | Non-Maskable Interrupt Input. A high to low transition at this<br>pin causes the CPU to vector to the NMI trap routine. When<br>the PWRDN (power down) instruction is executed, the NMI<br>pin must be low in order to force the XC164N into power<br>down mode. If NMI is high, when PWRDN is executed, the<br>part will continue to run in normal mode.<br>If not used, pin NMI should be pulled high externally.                                                                                                                                                                            |  |

| P0H.0-<br>P0H.3                         | 47          | Ю              | For details, please refer to the description of <b>PORT0</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Table 2        | Pi          | n Definit      | finitions and Functions (cont'd)                                                  |                                                                                                                                                                                                                                                                   |  |  |  |  |

|----------------|-------------|----------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbo<br>I     | Pin<br>Num. | Input<br>Outp. | Function                                                                          | Function                                                                                                                                                                                                                                                          |  |  |  |  |

| P9             |             | IO             | programm<br>state) or or<br>driver). The<br>or special)                           | Port 9 is a 6-bit bidirectional I/O port. Each pin can be<br>programmed for input (output driver in high-impedance<br>state) or output (configurable as push/pull or open drain<br>driver). The input threshold of Port 9 is selectable (standard<br>or special). |  |  |  |  |

| P9.0           | 10          | I/O            | CC16IO                                                                            | ing Port 9 pins also serve for alternate functions:<br>CAPCOM2: CC16 Capture Inp./Compare Outp.,                                                                                                                                                                  |  |  |  |  |

| P9.1           | 11          | I<br>I/O       | EX7IN<br>CC17IO                                                                   | Fast External Interrupt 7 Input (alternate pin B) CAPCOM2: CC17 Capture Inp./Compare Outp.,                                                                                                                                                                       |  |  |  |  |

| P9.2           | 12          | I<br>I/O       | EX6IN<br>CC18IO                                                                   | Fast External Interrupt 6 Input (alternate pin B) CAPCOM2: CC18 Capture Inp./Compare Outp.,                                                                                                                                                                       |  |  |  |  |

| P9.3           | 13          | I<br>I/O       | EX7IN<br>CC19IO                                                                   | Fast External Interrupt 7 Input (alternate pin A) CAPCOM2: CC19 Capture Inp./Compare Outp.,                                                                                                                                                                       |  |  |  |  |

| P9.4<br>P9.5   | 14<br>15    | <br> /O<br> /O | EX6IN<br>CC20IO<br>CC21IO                                                         | Fast External Interrupt 6 Input (alternate pin A)<br>CAPCOM2: CC20 Capture Inp./Compare Outp.<br>CAPCOM2: CC21 Capture Inp./Compare Outp.                                                                                                                         |  |  |  |  |

| P5             |             | I              | Port 5 is a 14-bit input-only port.<br>Some pins of Port 5 serve as timer inputs: |                                                                                                                                                                                                                                                                   |  |  |  |  |

| P5.0           | 18          | I              | No Alterna                                                                        | te Function beside General Purpose Input                                                                                                                                                                                                                          |  |  |  |  |

| P5.1           | 19          | I              |                                                                                   | te Function beside General Purpose Input                                                                                                                                                                                                                          |  |  |  |  |

| P5.2           | 20          |                |                                                                                   | te Function beside General Purpose Input                                                                                                                                                                                                                          |  |  |  |  |

| P5.3           | 21          |                |                                                                                   | te Function beside General Purpose Input                                                                                                                                                                                                                          |  |  |  |  |

| P5.4           | 22          |                |                                                                                   | te Function beside General Purpose Input                                                                                                                                                                                                                          |  |  |  |  |

| P5.5<br>P5.10  | 23<br>24    |                | T6EUD<br>T5EUD                                                                    | GPT2 Timer T6 Ext. Up/Down Ctrl. Inp.<br>GPT2 Timer T5 Ext. Up/Down Ctrl. Inp.                                                                                                                                                                                    |  |  |  |  |

| P5.10<br>P5.11 | 24<br>25    |                |                                                                                   |                                                                                                                                                                                                                                                                   |  |  |  |  |

| P5.6           | 26          |                |                                                                                   |                                                                                                                                                                                                                                                                   |  |  |  |  |

| P5.7           | 27          |                | T6IN                                                                              | GPT2 Timer T6 Count/Gate Input                                                                                                                                                                                                                                    |  |  |  |  |

| P5.12          | 30          | 1              | T5IN                                                                              | GPT2 Timer T5 Count/Gate Input                                                                                                                                                                                                                                    |  |  |  |  |

| P5.13          | 31          | 1              | T4EUD                                                                             | GPT1 Timer T4 Ext. Up/Down Ctrl. Inp.                                                                                                                                                                                                                             |  |  |  |  |

| P5.14          | 32          | I              | T2EUD                                                                             | GPT1 Timer T2 Ext. Up/Down Ctrl. Inp.                                                                                                                                                                                                                             |  |  |  |  |

| P5.15          | 33          | Ι              |                                                                                   |                                                                                                                                                                                                                                                                   |  |  |  |  |

#### ., ., . : 4 : ----. . .. , -

| Table 2    | Pi          | n Definit      | tions and F                                                                                                                                                                                                                                                                                                                                                                                      | u <b>nctions</b> (cont'd)                                                                   |  |  |

|------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|

| Symbo<br>I | Pin<br>Num. | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |  |  |

| P4         |             | IO             | Port 4 is an 8-bit bidirectional I/O port. Each pin can be<br>programmed for input (output driver in high-impedance<br>state) or output (configurable as push/pull or open drain<br>driver). The input threshold of Port 4 is selectable (standard<br>or special).<br>Port 4 can be used to output the segment address lines, the<br>optional chip select lines, and for serial interface lines: |                                                                                             |  |  |

| P4.0       | 53          | 0<br>0         | <u>A16</u><br>CS3                                                                                                                                                                                                                                                                                                                                                                                | Least Significant Segment Address Line,<br>Chip Select 3 Output                             |  |  |

| P4.1       | 54          | 0<br>0         | <u>A17</u><br>CS2                                                                                                                                                                                                                                                                                                                                                                                | Segment Address Line,<br>Chip Select 2 Output                                               |  |  |

| P4.2       | 55          | 0<br>0         | A18<br>CS1                                                                                                                                                                                                                                                                                                                                                                                       | Segment Address Line,<br>Chip Select 1 Output                                               |  |  |

| P4.3       | 56          | 0<br>0         | <u>A19</u><br>CS0                                                                                                                                                                                                                                                                                                                                                                                | Segment Address Line,<br>Chip Select 0 Output                                               |  |  |

| P4.4       | 57          | 0              | A20                                                                                                                                                                                                                                                                                                                                                                                              | Segment Address Line,                                                                       |  |  |

| P4.5       | 58          | I<br>O         | EX5IN<br>A21                                                                                                                                                                                                                                                                                                                                                                                     | Fast External Interrupt 5 Input (alternate pin B)<br>Segment Address Line,                  |  |  |

| P4.6       | 59          | I<br>O         | EX4IN<br>A22                                                                                                                                                                                                                                                                                                                                                                                     | Fast External Interrupt 4 Input (alternate pin B)<br>Segment Address Line,                  |  |  |

| P4.7       | 60          | I<br>O         | EX5IN<br>A23                                                                                                                                                                                                                                                                                                                                                                                     | Fast External Interrupt 5 Input (alternate pin A)<br>Most Significant Segment Address Line, |  |  |

|            |             | I              | EX4IN                                                                                                                                                                                                                                                                                                                                                                                            | Fast External Interrupt 4 Input (alternate pin A)                                           |  |  |

| Table 2    | Pi          | n Definit      | ions and Functions (cont'd)                    |                                                                               |  |  |

|------------|-------------|----------------|------------------------------------------------|-------------------------------------------------------------------------------|--|--|

| Symbo<br>I | Pin<br>Num. | Input<br>Outp. | Function                                       |                                                                               |  |  |

| PORT1      |             | IO             | continued                                      |                                                                               |  |  |

| (cont'd)   |             |                |                                                |                                                                               |  |  |

| P1H.0      | 89          | I              |                                                | CAPCOM6: Position 0 Input,                                                    |  |  |

|            |             | I              |                                                | Fast External Interrupt 0 Input (default pin),                                |  |  |

|            |             | I/O            |                                                | CAPCOM2: CC23 Capture Inp./Compare Outp.                                      |  |  |

| P1H.1      | 90          |                |                                                | CAPCOM6: Position 1 Input,                                                    |  |  |

|            |             |                |                                                | Fast External Interrupt 1 Input (default pin),                                |  |  |

| DALLO      | <b>A</b> 4  | I/O            |                                                | SSC1 Master-Receive/Slave-Transmit In/Out.                                    |  |  |

| P1H.2      | 91          |                |                                                | CAPCOM6: Position 2 Input,                                                    |  |  |

|            |             | <br> /O        |                                                | Fast External Interrupt 2 Input (default pin),                                |  |  |

| P1H.3      | 92          |                |                                                | SSC1 Master-Transmit/Slave-Receive Out/Inp.<br>CAPCOM2: Timer T7 Count Input, |  |  |

| г іп.э     | 92          | 1/O            |                                                | SSC1 Master Clock Output / Slave Clock Input,                                 |  |  |

|            |             | 1/0            |                                                | Fast External Interrupt 3 Input (default pin),                                |  |  |

|            |             |                |                                                | Fast External Interrupt 0 Input (alternate pin A)                             |  |  |

| P1H.4      | 93          | 1/0            |                                                | CAPCOM2: CC24 Capture Inp./Compare Outp.,                                     |  |  |

|            | 00          | 1              |                                                | Fast External Interrupt 4 Input (default pin)                                 |  |  |

| P1H.5      | 94          | I/O            |                                                | CAPCOM2: CC25 Capture Inp./Compare Outp.,                                     |  |  |

|            |             | 1              |                                                | Fast External Interrupt 5 Input (default pin)                                 |  |  |

| P1H.6      | 95          | I/O            |                                                | CAPCOM2: CC26 Capture Inp./Compare Outp.,                                     |  |  |

|            |             | I              | EX6IN                                          | Fast External Interrupt 6 Input (default pin)                                 |  |  |

| P1H.7      | 96          | I/O            | CC27IO                                         | CAPCOM2: CC27 Capture Inp./Compare Outp.,                                     |  |  |

|            |             | 1              | EX7IN                                          | Fast External Interrupt 7 Input (default pin)                                 |  |  |

| XTAL2      | 99          | 0              | XTAL2:                                         | Output of the oscillator amplifier circuit                                    |  |  |

| XTAL1      | 100         | 1              | XTAL1:                                         | Input to the oscillator amplifier and input to                                |  |  |

|            |             |                | 1                                              | the internal clock generator                                                  |  |  |

|            |             |                | To clock the                                   | device from an external source, drive XTAL1,                                  |  |  |

|            |             |                | -                                              | g XTAL2 unconnected. Minimum and maximum                                      |  |  |

|            |             |                | -                                              | rise/fall times specified in the AC                                           |  |  |

|            |             |                | Characterist                                   | ics must be observed.                                                         |  |  |

| res        | 28          | -              | pin is reserv                                  | pin is reserved and connected to $V_{\rm DDP}$                                |  |  |

| res        | 29          | -              | pin is reserv                                  | ed and connected to $V_{SSP}$                                                 |  |  |

| $V_{DDI}$  | 35, 97      | -              | Digital Core Supply Voltage (On-Chip Modules): |                                                                               |  |  |

|            |             |                | +2.5 V during normal operation and idle mode.  |                                                                               |  |  |

|            |             |                | Please refer                                   | to the Operating Conditions                                                   |  |  |

| Table 2       | Table 2Pin Definitions and Functions (cont'd) |                |                                                                                                                                                                                                     |  |  |  |  |

|---------------|-----------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbo<br>I    | Pin<br>Num.                                   | Input<br>Outp. | Function                                                                                                                                                                                            |  |  |  |  |

| $V_{DDP}$     | 9, 17,<br>38, 61,<br>87                       | -              | Digital Pad Supply Voltage (Pin Output Drivers):<br>+5 V during normal operation and idle mode.<br>Please refer to the <b>Operating Conditions</b>                                                  |  |  |  |  |

| $V_{\rm SSI}$ | 34, 98                                        | -              | Digital Ground.                                                                                                                                                                                     |  |  |  |  |

| $V_{\rm SSP}$ | 8, 16,<br>37,62,<br>88                        | -              | Connect decoupling capacitors to adjacent $V_{\rm DD}/V_{\rm SS}$ pin pairs<br>as close as possible to the pins.<br>All $V_{\rm SS}$ pins must be connected to the ground-line or ground-<br>plane. |  |  |  |  |

## 3.2 External Bus Controller

All of the external memory accesses are performed by a particular on-chip External Bus Controller (EBC). It can be programmed either to Single Chip Mode when no external memory is required, or to one of four different external memory access modes<sup>1</sup>), which are as follows:

- 16 ... 24-bit Addresses, 16-bit Data, Demultiplexed

- 16 ... 24-bit Addresses, 16-bit Data, Multiplexed

- 16 ... 24-bit Addresses, 8-bit Data, Multiplexed

- 16 ... 24-bit Addresses, 8-bit Data, Demultiplexed

In the demultiplexed bus modes, addresses are output on PORT1 and data is input/output on PORT0 or P0L, respectively. In the multiplexed bus modes both addresses and data use PORT0 for input/output. The high order address (segment) lines use Port 4. The number of active segment address lines is selectable, restricting the external address space to 8 Mbytes ... 64 Kbytes. This is required when interface lines are assigned to Port 4.

Up to 4 external  $\overline{CS}$  signals (3 windows plus default) can be generated in order to save external glue logic. External modules can directly be connected to the common address/data bus and their individual select lines.

Important timing characteristics of the external bus interface have been made programmable (via registers TCONCSx/FCONCSx) to allow the user the adaption of a wide range of different types of memories and external peripherals.

In addition, up to 4 independent address windows may be defined (via registers ADDRSELx) which control the access to different resources with different bus characteristics. These address windows are arranged hierarchically where window 4 overrides window 3, and window 2 overrides window 1. All accesses to locations not covered by these 4 address windows are controlled by TCONCS0/FCONCS0. The currently active window can generate a chip select signal.

The external bus timing is related to the rising edge of the reference clock output CLKOUT. The external bus protocol is compatible with that of the standard C166 Family.

The EBC also controls accesses to resources connected to the on-chip LXBus. The LXBus is an internal representation of the external bus and allows accessing integrated peripherals and modules in the same way as external components.

<sup>1)</sup> Bus modes are switched dynamically if several address windows with different mode settings are used.

#### 3.4 Interrupt System

With an interrupt response time of typically 8 CPU clocks (in case of internal program execution), the XC164N is capable of reacting very fast to the occurrence of non-deterministic events.

The architecture of the XC164N supports several mechanisms for fast and flexible response to service requests that can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to being serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

In contrast to a standard interrupt service where the current program execution is suspended and a branch to the interrupt vector table is performed, just one cycle is 'stolen' from the current CPU activity to perform a PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source, or the destination pointer, or both. An individual PEC transfer counter is implicitly decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source related vector location. PEC services are very well suited, for example, for supporting the transmission or reception of blocks of data. The XC164N has 8 PEC channels each of which offers such fast interrupt-driven data transfer capabilities.

A separate control register which contains an interrupt request flag, an interrupt enable flag and an interrupt priority bitfield exists for each of the possible interrupt nodes. Via its related register, each node can be programmed to one of sixteen interrupt priority levels. Once having been accepted by the CPU, an interrupt service can only be interrupted by a higher prioritized service request. For the standard interrupt processing, each of the possible interrupt nodes has a dedicated vector location.

Fast external interrupt inputs are provided to service external interrupts with high precision requirements. These fast interrupt inputs feature programmable edge detection (rising edge, falling edge, or both edges).

Software interrupts are supported by means of the 'TRAP' instruction in combination with an individual trap (interrupt) number.

**Table 4** shows all of the possible XC164N interrupt sources and the corresponding hardware-related interrupt flags, vectors, vector locations and trap (interrupt) numbers.

Note: Interrupt nodes which are not assigned to peripherals (unassigned nodes), may be used to generate software controlled interrupt requests by setting the respective interrupt request bit (xIR).

#### Table 4XC164N Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| CAPCOM6 Timer T13                             | CCU6_T13IC          | xx'0138 <sub>H</sub>             | 4E <sub>H</sub> / 78 <sub>D</sub> |

| CAPCOM6 Emergency                             | CCU6_EIC            | xx'013C <sub>H</sub>             | 4F <sub>H</sub> / 79 <sub>D</sub> |

| CAPCOM6                                       | CCU6_IC             | xx'0140 <sub>H</sub>             | 50 <sub>H</sub> / 80 <sub>D</sub> |

| SSC1 Transmit                                 | SSC1_TIC            | xx'0144 <sub>H</sub>             | 51 <sub>H</sub> / 81 <sub>D</sub> |

| SSC1 Receive                                  | SSC1_RIC            | xx'0148 <sub>H</sub>             | 52 <sub>H</sub> / 82 <sub>D</sub> |

| SSC1 Error                                    | SSC1_EIC            | xx'014C <sub>H</sub>             | 53 <sub>H</sub> / 83 <sub>D</sub> |

| Unassigned node                               |                     | xx'0150 <sub>H</sub>             | 54 <sub>H</sub> / 84 <sub>D</sub> |

| Unassigned node                               |                     | xx'0154 <sub>H</sub>             | 55 <sub>H</sub> / 85 <sub>D</sub> |

| Unassigned node                               |                     | xx'0158 <sub>H</sub>             | 56 <sub>H</sub> / 86 <sub>D</sub> |

| Unassigned node                               |                     | xx'015C <sub>H</sub>             | 57 <sub>H</sub> / 87 <sub>D</sub> |

| Unassigned node                               |                     | xx'0164 <sub>H</sub>             | 59 <sub>H</sub> / 89 <sub>D</sub> |

| Unassigned node                               |                     | xx'0168 <sub>H</sub>             | 5A <sub>H</sub> / 90 <sub>D</sub> |

| Unassigned node                               |                     | xx'016C <sub>H</sub>             | 5B <sub>H</sub> / 91 <sub>D</sub> |

| Unassigned node                               |                     | xx'0170 <sub>H</sub>             | 5C <sub>H</sub> / 92 <sub>D</sub> |

| Unassigned node                               |                     | xx'0174 <sub>H</sub>             | 5D <sub>H</sub> / 93 <sub>D</sub> |

| Unassigned node                               |                     | xx'0100 <sub>H</sub>             | 40 <sub>H</sub> / 64 <sub>D</sub> |

| Unassigned node                               |                     | xx'0104 <sub>H</sub>             | 41 <sub>H</sub> / 65 <sub>D</sub> |

| Unassigned node                               |                     | xx'012C <sub>H</sub>             | 4B <sub>H</sub> / 75 <sub>D</sub> |

| Unassigned node                               |                     | xx'00FC <sub>H</sub>             | 3F <sub>H</sub> / 63 <sub>D</sub> |

| Unassigned node                               |                     | xx'0160 <sub>H</sub>             | 58 <sub>H</sub> / 88 <sub>D</sub> |

Register VECSEG defines the segment where the vector table is located to. Bitfield VECSC in register CPUCON1 defines the distance between two adjacent vectors. This table represents the default setting, with a distance of 4 (two words) between two vectors.

2) The interrupt nodes assigned to ASC1 are only available in derivatives including the ASC1. Otherwise, they are unassigned nodes.

The XC164N also provides an excellent mechanism to identify and to process exceptions or error conditions that arise during run-time, so-called 'Hardware Traps'. Hardware traps cause immediate non-maskable system reaction which is similar to a standard interrupt service (branching to a dedicated vector table location). The occurence of a hardware trap is additionally signified by an individual bit in the trap flag register (TFR). Except when another higher prioritized trap service is in progress, a hardware trap will interrupt any actual program execution. In turn, hardware trap services can normally not be interrupted by standard or PEC interrupts.

**Table 5** shows all of the possible exceptions or error conditions that can arise during runtime:

| Exception Condition                                                                                                                                                               | Trap<br>Flag                        | Trap<br>Vector                            | Vector<br>Location <sup>1)</sup>                                                             | Trap<br>Number                                                           | Trap<br>Priority           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------|

| Reset Functions:<br>– Hardware Reset<br>– Software Reset<br>– W-dog Timer Overflow                                                                                                | -                                   | RESET<br>RESET<br>RESET                   | xx'0000 <sub>H</sub><br>xx'0000 <sub>H</sub><br>xx'0000 <sub>H</sub>                         | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub>                    | <br>   <br>                |

| Class A Hardware Traps:<br>– Non-Maskable Interrupt<br>– Stack Overflow<br>– Stack Underflow<br>– Software Break                                                                  | NMI<br>STKOF<br>STKUF<br>SOFTBRK    | NMITRAP<br>STOTRAP<br>STUTRAP<br>SBRKTRAP | xx'0008 <sub>H</sub><br>xx'0010 <sub>H</sub><br>xx'0018 <sub>H</sub><br>xx'0020 <sub>H</sub> | 02 <sub>H</sub><br>04 <sub>H</sub><br>06 <sub>H</sub><br>08 <sub>H</sub> | <br>  <br>                 |

| <ul> <li>Class B Hardware Traps:</li> <li>Undefined Opcode</li> <li>PMI Access Error</li> <li>Protected Instruction<br/>Fault</li> <li>Illegal Word Operand<br/>Access</li> </ul> | UNDOPC<br>PACER<br>PRTFLT<br>ILLOPA | BTRAP<br>BTRAP<br>BTRAP<br>BTRAP          | xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub> | OA <sub>H</sub><br>OA <sub>H</sub><br>OA <sub>H</sub><br>OA <sub>H</sub> | <br> <br> <br>             |

| Reserved                                                                                                                                                                          | _                                   | -                                         | [2C <sub>H</sub> –<br>3C <sub>H</sub> ]                                                      | [0B <sub>H</sub> –<br>0F <sub>H</sub> ]                                  | -                          |

| Software Traps <ul> <li>TRAP Instruction</li> </ul>                                                                                                                               | _                                   | -                                         | Any<br>[ $xx'0000_H - xx'01FC_H$ ]<br>in steps<br>of $4_H$                                   | Any<br>[00 <sub>н</sub> –<br>7F <sub>н</sub> ]                           | Current<br>CPU<br>Priority |

#### Table 5Hardware Trap Summary

1) Register VECSEG defines the segment where the vector table is located to.

# 3.5 On-Chip Debug Support (OCDS)

The On-Chip Debug Support system provides a broad range of debug and emulation features built into the XC164N. The user software running on the XC164N can thus be debugged within the target system environment.

The OCDS is controlled by an external debugging device via the debug interface, consisting of the IEEE-1149-conforming JTAG port and a break interface. The debugger controls the OCDS via a set of dedicated registers accessible via the JTAG interface. Additionally, the OCDS system can be controlled by the CPU, e.g. by a monitor program. An injection interface allows the execution of OCDS-generated instructions by the CPU.

Multiple breakpoints can be triggered by on-chip hardware, by software, or by an external trigger input. Single stepping is supported as well as the injection of arbitrary instructions and read/write access to the complete internal address space. A breakpoint trigger can be answered with a CPU-halt, a monitor call, a data transfer, or/and the activation of an external signal.

Tracing data can be obtained via the JTAG interface or via the external bus interface for increased performance.

The debug interface uses a set of 6 interface signals (4 JTAG lines, 2 break lines) to communicate with external circuitry. These interface signals are realized as alternate functions on Port 3 pins.

Complete system emulation is supported by the New Emulation Technology (NET) interface. Via this full-featured emulation interface (including internal buses, control, status, and pad signals) the XC164N chip can be connected to a NET carrier chip.

The use of the XC164N production chip together with the carrier chip provides superior emulation behavior, because the emulation system shows exactly the same functionality as the production chip (use of the identical silicon).

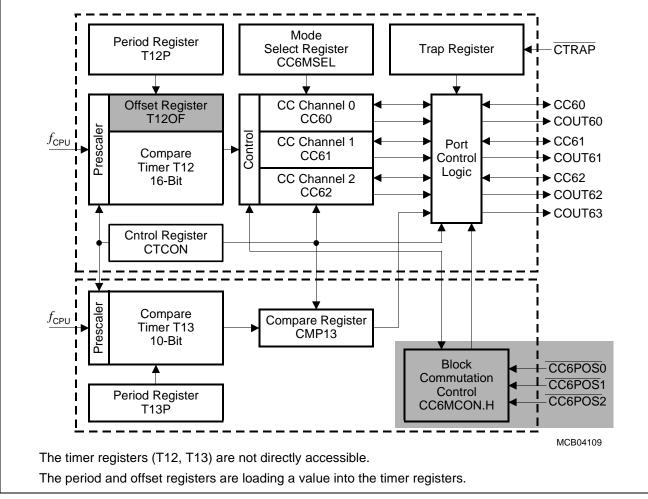

# 3.7 The Capture/Compare Unit CAPCOM6

The CAPCOM6 unit supports generation and control of timing sequences on up to three 16-bit capture/compare channels plus one independent 10-bit compare channel.

In compare mode the CAPCOM6 unit provides two output signals per channel which have inverted polarity and non-overlapping pulse transitions (deadtime control). The compare channel can generate a single PWM output signal and is further used to modulate the capture/compare output signals.

In capture mode the contents of compare timer T12 is stored in the capture registers upon a signal transition at pins CCx.

Compare timers T12 (16-bit) and T13 (10-bit) are free running timers which are clocked by the prescaled system clock.

### Figure 6 CAPCOM6 Block Diagram

For motor control applications both subunits may generate versatile multichannel PWM signals which are basically either controlled by compare timer T12 or by a typical hall sensor pattern at the interrupt inputs (block commutation).

## 3.16 Instruction Set Summary

Table 8 lists the instructions of the XC164N in a condensed way.

The various addressing modes that can be used with a specific instruction, the operation of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "Instruction Set Manual".

This document also provides a detailled description of each instruction.

| Mnemonic             | Description                                                                                          | Bytes |

|----------------------|------------------------------------------------------------------------------------------------------|-------|

| ADD(B)               | Add word (byte) operands                                                                             | 2/4   |

| ADDC(B)              | Add word (byte) operands with Carry                                                                  | 2/4   |

| SUB(B)               | Subtract word (byte) operands                                                                        | 2/4   |

| SUBC(B)              | Subtract word (byte) operands with Carry                                                             | 2/4   |

| MUL(U)               | (Un)Signed multiply direct GPR by direct GPR (16-16-bit)                                             | 2     |

| DIV(U)               | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                            | 2     |

| DIVL(U)              | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                            | 2     |

| CPL(B)               | Complement direct word (byte) GPR                                                                    | 2     |

| NEG(B)               | Negate direct word (byte) GPR                                                                        | 2     |

| AND(B)               | Bitwise AND, (word/byte operands)                                                                    | 2/4   |

| (X)OR(B)             | Bitwise (exclusive)OR, (word/byte operands)                                                          | 2/4   |

| BCLR / BSET          | Clear/Set direct bit                                                                                 | 2     |

| BMOV(N)              | Move (negated) direct bit to direct bit                                                              | 4     |

| BAND / BOR /<br>BXOR | AND/OR/XOR direct bit with direct bit                                                                | 4     |

| BCMP                 | Compare direct bit to direct bit                                                                     | 4     |

| BFLDH / BFLDL        | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data        | 4     |

| CMP(B)               | Compare word (byte) operands                                                                         | 2/4   |

| CMPD1/2              | Compare word data to GPR and decrement GPR by 1/2                                                    | 2/4   |

| CMPI1/2              | Compare word data to GPR and increment GPR by 1/2                                                    | 2/4   |

| PRIOR                | Determine number of shift cycles to normalize direct<br>word GPR and store result in direct word GPR | 2     |

| SHL / SHR            | Shift left/right direct word GPR                                                                     | 2     |

| ROL / ROR            | Rotate left/right direct word GPR                                                                    | 2     |

| ASHR                 | Arithmetic (sign bit) shift right direct word GPR                                                    | 2     |

| MOV(B)               | Move word (byte) data                                                                                | 2/4   |

| MOVBS/Z              | Move byte operand to word op. with sign/zero extension                                               | 2/4   |

#### Table 8 Instruction Set Summary

## 4.3 Operating Conditions

The following operating conditions must not be exceeded to ensure correct operation of the XC164N. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

| Parameter                                 | Symbol              | Limit | Values                 | Unit | Notes                                            |

|-------------------------------------------|---------------------|-------|------------------------|------|--------------------------------------------------|

|                                           |                     | min.  | max.                   |      |                                                  |

| Digital supply voltage for the core       | V <sub>DDI</sub>    | 2.35  | 2.7                    | V    | Active mode,<br>$f_{CPU} = f_{CPUmax}^{1)}$      |

| Digital supply voltage for IO pads        | $V_{DDP}$           | 4.4   | 5.5                    | V    | Active mode                                      |

| Supply Voltage Difference                 | $\Delta V_{\rm DD}$ | -0.5  | -                      | V    | $V_{\rm DDP}$ - $V_{\rm DDI}^{4)}$               |

| Digital ground voltage                    | V <sub>SS</sub>     |       | 0                      | V    | Reference voltage                                |

| Overload current                          | I <sub>OV</sub>     | -5    | 5                      | mA   | Per IO pin <sup>5)6)</sup>                       |

|                                           |                     | -2    | 5                      | mA   | Per analog input pin <sup>5)6)</sup>             |

| Overload current coupling                 | K <sub>OVA</sub>    | _     | 1.0 × 10 <sup>-4</sup> | _    | <i>I</i> <sub>OV</sub> > 0                       |

| factor for analog inputs <sup>7)</sup>    |                     | _     | 1.5 × 10 <sup>-3</sup> | -    | <i>I</i> <sub>OV</sub> < 0                       |

| Overload current coupling                 | K <sub>OVD</sub>    | -     | 5.0 × 10 <sup>-3</sup> | -    | <i>I</i> <sub>OV</sub> > 0                       |

| factor for digital I/O pins <sup>7)</sup> |                     | -     | 1.0 × 10 <sup>-2</sup> | -    | <i>I</i> <sub>OV</sub> < 0                       |

| Absolute sum of overload currents         | $\Sigma  I_{OV} $   | _     | 50                     | mA   | 6)                                               |

| External Load<br>Capacitance              | CL                  | _     | 50                     | pF   | Pin drivers in <b>default</b> mode <sup>8)</sup> |

| Ambient temperature                       | T <sub>A</sub>      | 0     | 70                     | °C   | SAB-XC164N                                       |

|                                           |                     | -40   | 85                     | °C   | SAF-XC164N                                       |

|                                           |                     | -40   | 125                    | °C   | SAK-XC164N                                       |

| Table 11 | Operating | Condition | Parameters |

|----------|-----------|-----------|------------|

|          | J         |           |            |

1)  $f_{CPUmax} = 40 \text{ MHz}$  for devices marked ...40F,  $f_{CPUmax} = 20 \text{ MHz}$  for devices marked ...20F.

2) External circuitry must guarantee low level at the RSTIN pin at least until both power supply voltages have reached the operating level.

3) The specified voltage range is allowed for operation. The range limits may be reached under extreme operating conditions. However, specified parameters, such as leakage currents, refer to the standard operating voltage range of  $V_{\text{DDP}}$  = 4.75 V to 5.25 V.

4) This limitation must be fulfilled under all operating conditions including power-ramp-up, power-ramp-down, and power-save modes.

### 4.5 DC Parameters

#### **DC Characteristics**

(Operating Conditions apply)<sup>1)</sup>

| Parameter                                          | Symbol            |         | Limit Values                  |                               | Unit | Test Condition                                                      |  |

|----------------------------------------------------|-------------------|---------|-------------------------------|-------------------------------|------|---------------------------------------------------------------------|--|

|                                                    |                   |         | min.                          | max.                          |      |                                                                     |  |

| Input low voltage TTL<br>(all except XTAL1)        | $V_{IL}$          | SR      | -0.5                          | 0.2×V <sub>DDP</sub><br>- 0.1 | V    | -                                                                   |  |

| Input low voltage XTAL1                            | $V_{ILC}$         | SR      | -0.5                          | $0.3 	imes V_{ m DDI}$        | V    | -                                                                   |  |

| Input low voltage<br>(Special Threshold)           | V <sub>ILS</sub>  | SR      | -0.5                          | $0.45 \times V_{\text{DDP}}$  | V    | 2)                                                                  |  |

| Input high voltage TTL<br>(all except XTAL1)       | $V_{IH}$          | SR      | 0.2×V <sub>DDP</sub><br>+ 0.9 | V <sub>DDP</sub><br>+ 0.5     | V    | -                                                                   |  |

| Input high voltage XTAL1                           | V <sub>IHC</sub>  | SR      | $0.7 \times V_{ m DDI}$       | V <sub>DDI</sub><br>+ 0.5     | V    | _                                                                   |  |

| Input high voltage<br>(Special Threshold)          | V <sub>IHS</sub>  | SR      | 0.8×V <sub>DDP</sub><br>- 0.2 | V <sub>DDP</sub><br>+ 0.5     | V    | 2)                                                                  |  |

| Input Hysteresis<br>(Special Threshold)            | HYS               |         | $0.04 \times V_{\text{DDP}}$  | _                             | V    | $V_{\text{DDP}}$ in [V],<br>Series resis-<br>tance = 0 $\Omega^{2}$ |  |

| Output low voltage                                 | $V_{OL}$          | CC      | _                             | 1.0                           | V    | $I_{\rm OL} \leq I_{\rm OLmax}^{3)}$                                |  |

|                                                    |                   |         | -                             | 0.45                          | V    | $I_{\rm OL} \leq I_{\rm OLnom}^{3) 4)$                              |  |

| Output high voltage <sup>5)</sup>                  | V <sub>OH</sub>   | CC      | V <sub>DDP</sub><br>- 1.0     | -                             | V    | $I_{\rm OH} \ge I_{\rm OHmax}^{3)}$                                 |  |

|                                                    |                   |         | V <sub>DDP</sub><br>- 0.45    | _                             | V    | $I_{\text{OH}} \ge I_{\text{OHnom}}^{3) 4}$                         |  |

| Input leakage current<br>(Port 5) <sup>6)</sup>    | I <sub>OZ1</sub>  | CC      | -                             | ±300                          | nA   | $0 V < V_{IN} < V_{DDP,}$<br>$T_A \le 125 \text{ °C}$               |  |

|                                                    |                   |         |                               | ±200                          | nA   | $0 V < V_{IN} < V_{DDP,}$<br>$T_A \le 85 \ ^{\circ}C^{12)}$         |  |

| Input leakage current<br>(all other) <sup>6)</sup> | I <sub>OZ2</sub>  |         | _                             | ±500                          | nA   | $0.45 \text{ V} < V_{\text{IN}} < V_{\text{DDP}}$                   |  |

| Configuration pull-up current <sup>7)</sup>        | I <sub>CPUF</sub> | 8)<br>I | _                             | -10                           | μA   | $V_{\rm IN} = V_{\rm IHmin}$                                        |  |

|                                                    | I <sub>CPUL</sub> | 9)      | -100                          | -                             | μA   | $V_{\rm IN} = V_{\rm ILmax}$                                        |  |

#### **DC Characteristics** (cont'd)

(Operating Conditions apply)<sup>1)</sup>

| Parameter                                                  | Symbol                          | Limit Values |      | Unit | <b>Test Condition</b>                        |  |

|------------------------------------------------------------|---------------------------------|--------------|------|------|----------------------------------------------|--|

|                                                            |                                 | min.         | max. |      |                                              |  |

| Configuration pull-down                                    | I <sub>CPDL</sub> <sup>8)</sup> | _            | 10   | μA   | $V_{\rm IN} = V_{\rm ILmax}$                 |  |

| current <sup>10)</sup>                                     | I <sub>CPDH</sub> <sup>9)</sup> | 120          | _    | μA   | $V_{\rm IN} = V_{\rm IHmin}$                 |  |

| Level inactive hold current <sup>11)</sup>                 | I <sub>LHI</sub> <sup>8)</sup>  | -            | -10  | μA   | $V_{\text{OUT}} = 0.5 \times V_{\text{DDP}}$ |  |

| Level active hold current <sup>11)</sup>                   | $I_{\rm LHA}^{(9)}$             | -100         | _    | μA   | $V_{\rm OUT}$ = 0.45 V                       |  |

| XTAL1 input current                                        | I <sub>IL</sub> CC              | _            | ±20  | μA   | $0 V < V_{IN} < V_{DDI}$                     |  |

| Pin capacitance <sup>12)</sup><br>(digital inputs/outputs) | C <sub>IO</sub> CC              | _            | 10   | pF   |                                              |  |

1) Keeping signal levels within the limits specified in this table, ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{OV}$ .

2) This parameter is tested for P2, P3, P4, P9.

The maximum deliverable output current of a port driver depends on the selected output driver mode, see Table 12, Current Limits for Port Output Drivers. The limit for pin groups must be respected.

4) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow V_{SS}$ ,  $V_{OH} \rightarrow V_{DDP}$ ). However, only the levels for nominal output currents are guaranteed.

- 5) This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage results from the external circuitry.

- 6) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{OV}$ .

- 7) This specification is valid during Reset for configuration on  $\overline{RD}$ ,  $\overline{WR}$ ,  $\overline{EA}$ , PORT0.

- 8) The maximum current may be drawn while the respective signal line remains inactive.

- 9) The minimum current must be drawn to drive the respective signal line active.

- 10) This specification is valid during Reset for configuration on ALE.

- 11) This specification is valid during Reset for pins P4.3-0, which can act as  $\overline{CS}$  outputs.

- 12) Not subject to production test verified by design/characterization.

| Port Output Driver<br>Mode | Maximum Output Current $(I_{OLmax}, -I_{OHmax})^{1}$ | Nominal Output Current<br>( <i>I</i> <sub>OLnom</sub> , - <i>I</i> <sub>OHnom</sub> ) |

|----------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------|

| Strong driver              | 10 mA                                                | 2.5 mA                                                                                |

| Medium driver              | 4.0 mA                                               | 1.0 mA                                                                                |

| Weak driver                | 0.5 mA                                               | 0.1 mA                                                                                |

#### Table 12 Current Limits for Port Output Drivers

1) An output current above  $|I_{OXnom}|$  may be drawn from up to three pins at the same time. For any group of 16 neighboring port output pins the total output current in each direction ( $\Sigma I_{OL}$  and  $\Sigma I_{OH}$ ) must remain below 50 mA.

#### Power Consumption XC164N

(Operating Conditions apply)

| Parameter                                                                                                                             | Symbol                                | Limit Values |                                                      | Unit | <b>Test Condition</b>                                                                                         |  |

|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------|------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                       |                                       | min.         | max.                                                 |      |                                                                                                               |  |

| Power supply current (active) with all peripherals active                                                                             | I <sub>DDI</sub>                      | -            | 15 +<br>2.6 × f <sub>CPU</sub>                       | mA   | <sup>1)</sup><br>f <sub>CPU</sub> in [MHz] <sup>2)</sup>                                                      |  |

| Pad supply current                                                                                                                    | I <sub>DDP</sub>                      | -            | 5                                                    | mA   | 3)                                                                                                            |  |

| Idle mode supply current<br>with all peripherals active                                                                               | I <sub>IDX</sub>                      | -            | 15 +<br>1.2 × f <sub>CPU</sub>                       | mA   | $f_{\rm CPU}$ in [MHz] <sup>2)</sup>                                                                          |  |

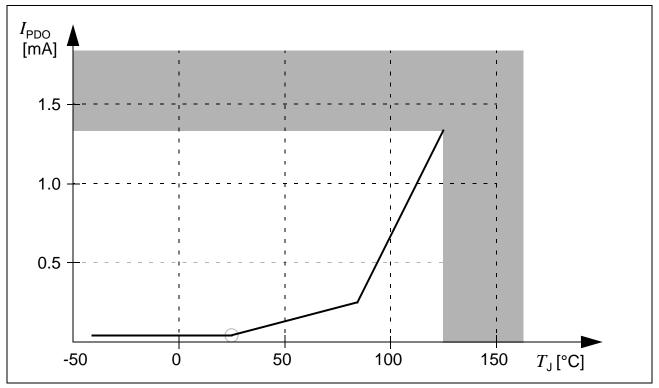

| Sleep and Power-down mode<br>supply current caused by<br>leakage <sup>4)</sup>                                                        | I <sub>PDL</sub> <sup>5)</sup>        | _            | 128,000<br>× e <sup>-α</sup>                         | mA   | $V_{\text{DDI}} = V_{\text{DDImax}}^{6)}$ $T_{\text{J}} \text{ in [°C]}$ $\alpha =$ $4670/(273+T_{\text{J}})$ |  |

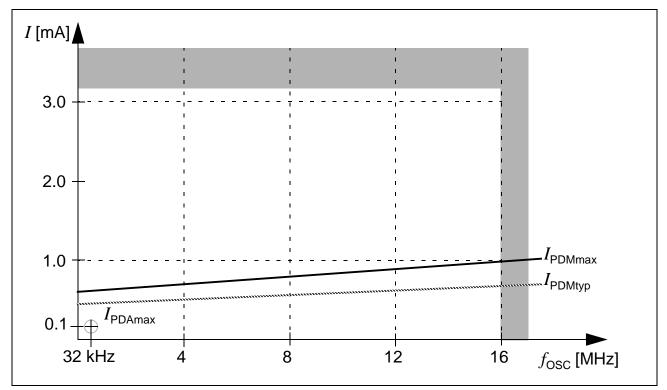

| Sleep and Power-down mode<br>supply current caused by<br>leakage and the RTC running,<br>clocked by the main oscillator <sup>4)</sup> | <i>I</i> <sub>PDM</sub> <sup>7)</sup> | -            | 0.6 +<br>0.02×f <sub>OSC</sub><br>+ I <sub>PDL</sub> | mA   | $V_{\text{DDI}}=V_{\text{DDImax}}$<br>$f_{\text{OSC}}$ in [MHz]                                               |  |

1) During Flash programming or erase operations the supply current is increased by max. 5 mA.

2) The supply current is a function of the operating frequency. This dependency is illustrated in Figure 10. These parameters are tested at  $V_{\text{DDImax}}$  and maximum CPU clock frequency with all outputs disconnected and all inputs at  $V_{\text{IL}}$  or  $V_{\text{IH}}$ .

- 3) The pad supply voltage pins ( $V_{DDP}$ ) mainly provides the current consumed by the pin output drivers. A small amount of current is consumed even though no outputs are driven, because the drivers' input stages are switched and also the Flash module draws some power from the  $V_{DDP}$  supply.

- 4) The total supply current in Sleep and Power-down mode is the sum of the temperature dependent leakage current and the frequency dependent current for RTC and main oscillator (if active).

Figure 11 Sleep and Power Down Supply Current due to RTC and Oscillator running, as a Function of Oscillator Frequency

Figure 12 Sleep and Power Down Leakage Supply Current as a Function of Temperature

#### **Timing Parameters**

# 5 Timing Parameters

## 5.1 Definition of Internal Timing

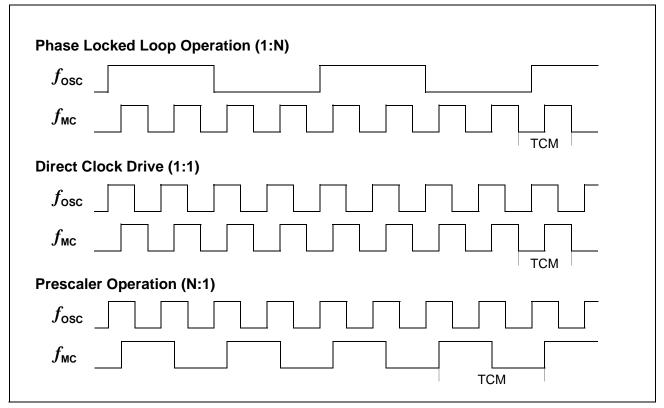

The internal operation of the XC164N is controlled by the internal master clock  $f_{MC}$ .

The master clock signal  $f_{\rm MC}$  can be generated from the oscillator clock signal  $f_{\rm OSC}$  via different mechanisms. The duration of master clock periods (TCMs) and their variation (and also the derived external timing) depend on the used mechanism to generate  $f_{\rm MC}$ . This influence must be regarded when calculating the timings for the XC164N.

Figure 13 Generation Mechanisms for the Master Clock

Note: The example for PLL operation shown in **Figure 13** refers to a PLL factor of 1:4, the example for prescaler operation refers to a divider factor of 2:1.

The used mechanism to generate the master clock is selected by register PLLCON.

CPU and EBC are clocked with the CPU clock signal  $f_{CPU}$ . The CPU clock can have the same frequency as the master clock ( $f_{CPU} = f_{MC}$ ) or can be the master clock divided by two:  $f_{CPU} = f_{MC}$  / 2. This factor is selected by bit CPSYS in register SYSCON1.

The specification of the external timing (AC Characteristics) depends on the period of the CPU clock, called "TCP".

The other peripherals are supplied with the system clock signal  $f_{SYS}$  which has the same frequency as the CPU clock signal  $f_{CPU}$ .

#### **Timing Parameters**

#### Table 17 External Bus Cycle Timing (Operating Conditions apply)

| Parameter                                                 | Symbol                  |    | Limits |      | Unit |

|-----------------------------------------------------------|-------------------------|----|--------|------|------|

|                                                           |                         |    | min.   | max. |      |

| Output valid delay for:<br>RD, WR(L/H)                    | <i>tc</i> <sub>10</sub> | CC | 1      | 15   | ns   |

| Output valid delay for:<br>BHE, ALE                       | <i>tc</i> <sub>11</sub> | CC | -1     | 8    | ns   |

| Output valid delay for:<br>A23A16, A15A0 (on PORT1)       | <i>tc</i> <sub>12</sub> | CC | 3      | 18   | ns   |

| Output valid delay for:<br>A15A0 (on PORT0)               | <i>tc</i> <sub>13</sub> | CC | 3      | 18   | ns   |

| Output valid delay for:<br>CS                             | <i>tc</i> <sub>14</sub> | CC | 3      | 16   | ns   |

| Output valid delay for:<br>D15D0 (write data, mux-mode)   | <i>tc</i> <sub>15</sub> | CC | 3      | 19   | ns   |

| Output valid delay for:<br>D15D0 (write data, demux-mode) | <i>tc</i> <sub>16</sub> | CC | 2      | 16   | ns   |

| Output hold time for:<br>RD, WR(L/H)                      | <i>tc</i> <sub>20</sub> | CC | -3     | 4    | ns   |

| Output hold time for:<br>BHE, ALE                         | <i>tc</i> <sub>21</sub> | CC | 0      | 11   | ns   |

| Output hold time for:<br>A23A16, A15A0 (on PORT0)         | <i>tc</i> <sub>23</sub> | CC | 1      | 13   | ns   |

| Output hold time for:<br>CS                               | <i>tc</i> <sub>24</sub> | CC | -2     | 4    | ns   |

| Output hold time for:<br>D15D0 (write data)               | <i>tc</i> <sub>25</sub> | CC | 1      | 13   | ns   |

| Input setup time for:<br>D15D0 (read data)                | <i>tc</i> <sub>30</sub> | SR | 29     | -    | ns   |

| Input hold time<br>D15…D0 (read data) <sup>1)</sup>       | <i>tc</i> <sub>31</sub> | SR | -5     | -    | ns   |

Read data are latched with the same (internal) clock edge that triggers the address change and the rising edge of RD. Therefore address changes before the end of RD have no impact on (demultiplexed) read cycles. Read data can be removed after the rising edge of RD

Note: The shaded parameters have been verified by characterization. They are not subject to production test.