Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c72-04-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

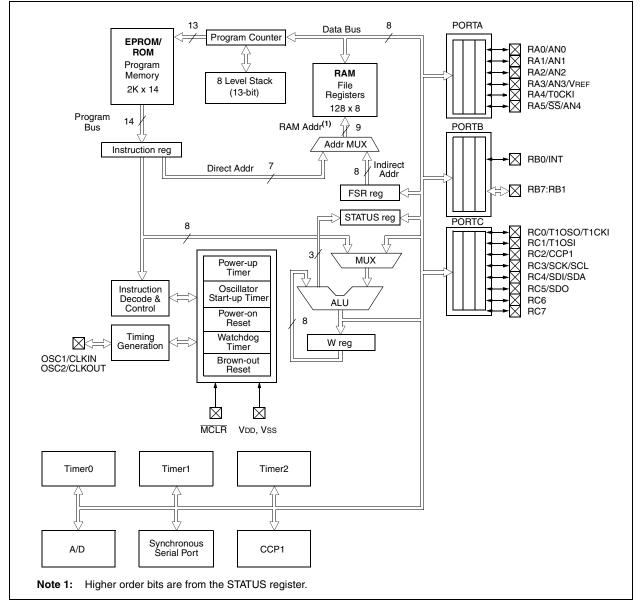

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the operation of the PIC16C72 device. Additional information may be found in the PIC<sup>®</sup> Mid-Range MCU Reference Manual (DS33023) which may be downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

The PIC16C72 belongs to the Mid-Range family of the PIC devices. A block diagram of the device is shown in Figure 1-1.

The program memory contains 2K words which translate to 2048 instructions, since each 14-bit program memory word is the same width as each device instruction. The data memory (RAM) contains 128 bytes.

There are also 22 I/O pins that are user-configurable on a pin-to-pin basis. Some pins are multiplexed with other device functions. These functions include:

- External interrupt

- Change on PORTB interrupt

- Timer0 clock input

- Timer1 clock/oscillator

- Capture/Compare/PWM

- A/D converter

- SPI/I<sup>2</sup>C

Table 1-1 details the pinout of the device with descriptions and details for each pin.

## FIGURE 1-1: PIC16C72/CR72 BLOCK DIAGRAM

# **PIC16C72 Series**

| Address              | Name       | Bit 7              | Bit 6                                                                                          | Bit 5                   | Bit 4         | Bit 3        | Bit 2           | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(3) |

|----------------------|------------|--------------------|------------------------------------------------------------------------------------------------|-------------------------|---------------|--------------|-----------------|--------|--------|--------------------------|-------------------------------------|

| Bank 1               |            | •                  |                                                                                                |                         |               | •            |                 | •      | •      | ·                        |                                     |

| 80h <sup>(1)</sup>   | INDF       | Addressing         | Addressing this location uses contents of FSR to address data memory (not a physical register) |                         |               |              |                 |        |        |                          | 0000 0000                           |

| 81h                  | OPTION_REG | RBPU               | INTEDG                                                                                         | TOCS                    | TOSE          | PSA          | PS2             | PS1    | PS0    | 1111 1111                | 1111 1111                           |

| 82h <sup>(1)</sup>   | PCL        | Program Co         | ounter's (PC)                                                                                  | Least Signif            | icant Byte    |              |                 |        |        | 0000 0000                | 0000 0000                           |

| 83h <sup>(1)</sup>   | STATUS     | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup>                                                                             | RP0                     | TO            | PD           | Z               | DC     | С      | 0001 1xxx                | 000q quuu                           |

| 84h <sup>(1)</sup>   | FSR        | Indirect data      | a memory ad                                                                                    | dress pointe            | er            |              |                 |        |        | xxxx xxxx                | uuuu uuuu                           |

| 85h                  | TRISA      | _                  | _                                                                                              | PORTA Dat               | a Direction F | Register     |                 |        |        | 11 1111                  | 11 1111                             |

| 86h                  | TRISB      | PORTB Dat          | a Direction F                                                                                  | Register                |               |              |                 |        |        | 1111 1111                | 1111 1111                           |

| 87h                  | TRISC      | PORTC Dat          | a Direction F                                                                                  | Register                |               |              |                 |        |        | 1111 1111                | 1111 1111                           |

| 88h                  | _          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 89h                  | _          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 8Ah <sup>(1,2)</sup> | PCLATH     | _                  | _                                                                                              | —                       | Write Buffer  | for the uppe | er 5 bits of th | e PC   |        | 0 0000                   | 0 0000                              |

| 8Bh <sup>(1)</sup>   | INTCON     | GIE                | PEIE                                                                                           | T0IE                    | INTE          | RBIE         | TOIF            | INTF   | RBIF   | 0000 000x                | 0000 000u                           |

| 8Ch                  | PIE1       | _                  | ADIE                                                                                           | _                       | —             | SSPIE        | CCP1IE          | TMR2IE | TMR1IE | -0 0000                  | -0 0000                             |

| 8Dh                  | _          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 8Eh                  | PCON       | —                  | _                                                                                              | _                       | _             | _            | _               | POR    | BOR    | dd                       | uu                                  |

| 8Fh                  | _          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 90h                  | _          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 91h                  | _          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 92h                  | PR2        | Timer2 Peri        | od Register                                                                                    |                         |               |              |                 |        |        | 1111 1111                | 1111 1111                           |

| 93h                  | SSPADD     | Synchronou         | is Serial Port                                                                                 | (I <sup>2</sup> C mode) | Address Reg   | gister       |                 |        |        | 0000 0000                | 0000 0000                           |

| 94h                  | SSPSTAT    | SMP <sup>(5)</sup> | CKE <sup>(5)</sup>                                                                             | D/Ā                     | Р             | S            | R/W             | UA     | BF     | 0000 0000                | 0000 0000                           |

| 95h                  | _          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 96h                  | _          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 97h                  | _          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 98h                  | _          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 99h                  | _          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 9Ah                  | _          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 9Bh                  | _          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 9Ch                  | —          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 9Dh                  | _          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | _                        | _                                   |

| 9Eh                  | —          | Unimpleme          | nted                                                                                           |                         |               |              |                 |        |        | —                        | _                                   |

| 9Fh                  | ADCON1     | _                  | —                                                                                              | —                       | _             | —            | PCFG2           | PCFG1  | PCFG0  | 000                      | 000                                 |

### TABLE 2-1 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved on the PIC16C72/CR72. Always maintain these bits clear.

5: SSPSTAT<7:6> are not implemented on the PIC16C72, read as '0'.

#### 2.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the Peripheral interrupts.

**Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## FIGURE 2-7: PIR1 REGISTER (ADDRESS 0Ch)

|          | R/W-0<br>ADIF                                | U-0                                                                                 | U-0                                              | R/W-0<br>SSPIF           | R/W-0<br>CCP1IF             | R/W-0<br>TMR2IF | R/W-0<br>TMR1IF | R = Readable bit                                                                      |

|----------|----------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------|-----------------------------|-----------------|-----------------|---------------------------------------------------------------------------------------|

| vit7     |                                              |                                                                                     |                                                  |                          |                             |                 | bitO            | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| oit 7:   | Unimpler                                     | nented: F                                                                           | lead as '0                                       | I                        |                             |                 |                 |                                                                                       |

| bit 6:   | <b>ADIF</b> : A/D<br>1 = An A/I<br>0 = The A | D convers                                                                           | ion compl                                        | eted (mus                | st be cleare                | d in softwa     | ıre)            |                                                                                       |

| bit 5-4: | Unimpler                                     | nented: R                                                                           | ead as '0                                        |                          |                             |                 |                 |                                                                                       |

| bit 3:   |                                              | ansmissio                                                                           | n/reception                                      | on is comp               | pt Flag bit<br>lete (must l | be cleared      | in software     | 9)                                                                                    |

| bit 2:   | 0 = No TN<br><u>Compare</u>                  | <u>Aode</u><br>R1 registe<br>/IR1 regist<br>Mode<br>R1 registe<br>/IR1 regist<br>de | r capture<br>er capture<br>r compare<br>er compa | occurred (<br>e occurred | curred (mu                  |                 |                 | are)                                                                                  |

| bit 1:   | <b>TMR2IF</b> : 1<br>1 = TMR2<br>0 = No TM   | to PR2 m                                                                            | natch occu                                       | urred (mus               | Flag bit<br>t be cleared    | d in softwa     | re)             |                                                                                       |

| bit 0:   | TMR1IF:                                      |                                                                                     |                                                  |                          | bit<br>cleared in :         | software)       |                 |                                                                                       |

# **PIC16C72 Series**

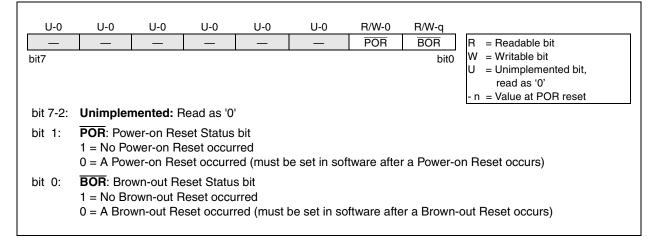

#### 2.2.2.6 PCON REGISTER

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external  $\overline{\text{MCLR}}$  Reset or WDT Reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition.

#### Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

### FIGURE 2-8: PCON REGISTER (ADDRESS 8Eh)

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

## EXAMPLE 2-1: INDIRECT ADDRESSING

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDR register now will return the value of 0Ah.

**Direct Addressing** Indirect Addressing RP1:RP0 from opcode 7 6 0 IRP FSR register 0 (2) (2)bank select location select bank select location select • 00 01 10 11 00h 80h 100h 180h not used (3) (3) Data Memory(1) FFh 1FFh 7Fh 17Fh Bank 0 Bank 1 Bank 2 Bank 3 Note 1: For register file map detail see Figure 2-2. 2: Maintain RP1 and IRP as clear for upward compatibility with future products. 3: Not implemented.

## FIGURE 2-11: DIRECT/INDIRECT ADDRESSING

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | movwf<br>clrf<br>incf | FSR<br>INDF<br>FSR | ;clear INDF register<br>;inc pointer |

|----------|-----------------------|--------------------|--------------------------------------|

|          | goto                  | -                  | ;all done?<br>;NO, clear next        |

| CONTINUE |                       |                    |                                      |

|          | :                     |                    | ;YES, continue                       |

### 5.2 <u>Timer1 Oscillator</u>

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 5-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

TABLE 5-1CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type                                   | e Freq                                                                                                                                                                   | C1           | C2           |  |  |  |  |  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--|--|--|--|--|

| LP                                         | 32 kHz                                                                                                                                                                   | 32 kHz 33 pF |              |  |  |  |  |  |

|                                            | 100 kHz                                                                                                                                                                  | 15 pF        | 15 pF        |  |  |  |  |  |

|                                            | 200 kHz                                                                                                                                                                  | 15 pF        | 15 pF        |  |  |  |  |  |

| These values are for design guidance only. |                                                                                                                                                                          |              |              |  |  |  |  |  |

| Crystals Tested:                           |                                                                                                                                                                          |              |              |  |  |  |  |  |

| 32.768 kH                                  | z Epson C-00                                                                                                                                                             | 1R32.768K-A  | $\pm$ 20 PPM |  |  |  |  |  |

| 100 kHz                                    | Epson C-2 1                                                                                                                                                              | 00.00 KC-P   | $\pm$ 20 PPM |  |  |  |  |  |

| 200 kHz                                    | STD XTL 20                                                                                                                                                               | 0.000 kHz    | $\pm$ 20 PPM |  |  |  |  |  |

| 0                                          | of oscillator but also increases the start-up                                                                                                                            |              |              |  |  |  |  |  |

| 2: S                                       | <ul> <li>time.</li> <li>2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropri-</li> </ul> |              |              |  |  |  |  |  |

ate values of external components.

## 5.3 <u>Timer1 Interrupt</u>

The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

#### 5.4 <u>Resetting Timer1 using a CCP Trigger</u> <u>Output</u>

If the CCP module is configured in compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The spe | cial e | event | trigg | ers from tl | ne CC | P1  |

|-------|---------|--------|-------|-------|-------------|-------|-----|

|       | module  | will   | not   | set   | interrupt   | flag  | bit |

|       | TMR1IF  | (PIR   | 1<0>  | ·).   |             |       |     |

Timer1 must be configured for either timer or synchronized counter mode to take advantage of this feature. If Timer1 is running in asynchronous counter mode, this reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer1.

## TABLE 5-2 REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address | Name   | Bit 7                                                                            | Bit 6   | Bit 5         | Bit 4         | Bit 3         | Bit 2      | Bit 1       | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|----------------------------------------------------------------------------------|---------|---------------|---------------|---------------|------------|-------------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh | INTCON | GIE                                                                              | PEIE    | TOIE          | INTE          | RBIE          | TOIF       | INTF        | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch     | PIR1   | (1)                                                                              | ADIF    | (1)           | (1)           | SSPIF         | CCP1IF     | TMR2IF      | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1   | (1)                                                                              | ADIE    | (1)           | (1)           | SSPIE         | CCP1IE     | TMR2IE      | TMR1IE | 0000 0000                | 0000 0000                       |

| 0Eh     | TMR1L  | Holding                                                                          | registe | r for the Lea | st Significan | t Byte of the | 16-bit TMF | R1 register |        | xxxx xxxx                | uuuu uuuu                       |

| 0Fh     | TMR1H  | TMR1H Holding register for the Most Significant Byte of the 16-bit TMR1 register |         |               |               |               |            |             |        | xxxx xxxx                | uuuu uuuu                       |

| 10h     | T1CON  | _                                                                                | -       | T1CKPS1       | T1CKPS0       | T1OSCEN       | T1SYNC     | TMR1CS      | TMR1ON | 00 0000                  | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module. Note 1: These bits are unimplemented, read as '0'. NOTES:

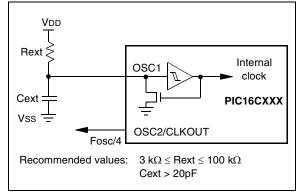

#### 10.2.3 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 10-4 shows how the R/C combination is connected to the PIC16CXXX family.

#### FIGURE 10-4: RC OSCILLATOR MODE

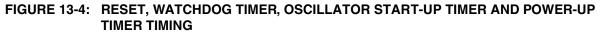

## 10.3 <u>Reset</u>

The PIC16CXXX family differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (normal operation)

- Brown-out Reset (BOR)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{\text{MCLR}}$  and WDT Reset, on  $\overline{\text{MCLR}}$  reset during SLEEP, and Brownout Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different reset situations as indicated in Table 10-4. These bits are used in software to determine the nature of the reset. See Table 10-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 10-5.

The PIC16C72/CR72 have a MCLR noise filter in the MCLR reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

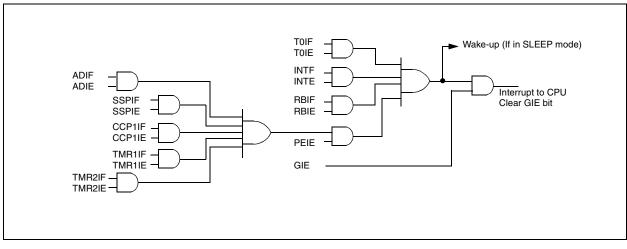

#### 10.10 Interrupts

The PIC16C72/CR72 has 8 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit

#### 10.10.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 10.13 for details on SLEEP mode.

#### 10.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 4.0)

#### 10.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 3.2)

#### FIGURE 10-11: INTERRUPT LOGIC

### 10.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, i.e., W register and STATUS register. This will have to be implemented in software.

Example 10-1 stores and restores the W and STATUS registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Executes the ISR code.

- d) Restores the STATUS register (and bank select bit).

- e) Restores the W register.

#### EXAMPLE 10-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

| MOVWF       | W_TEMP                  | ;Copy W to W_TEMP register, could be bank one or zero   |

|-------------|-------------------------|---------------------------------------------------------|

| SWAPF       | STATUS,W                | ;Swap status to be saved into W                         |

| CLRF        | STATUS                  | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF       | STATUS_TEMP             | ;Save status to bank zero STATUS_TEMP register          |

| :           |                         |                                                         |

| : Interrupt | Service Routine (ISR) - | user defined                                            |

| :           |                         |                                                         |

| SWAPF       | STATUS_TEMP,W           | ;Swap STATUS_TEMP register into W                       |

|             |                         | ;(sets bank to original state)                          |

| MOVWF       | STATUS                  | ;Move W into STATUS register                            |

| SWAPF       | W_TEMP,F                | ;Swap W_TEMP                                            |

| SWAPF       | W_TEMP,W                | ;Swap W_TEMP into W                                     |

Other peripherals cannot generate interrupts since during SLEEP, no on-chip clocks are present.

When the **SLEEP** instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 10.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

• If the interrupt occurs before the execution of a

SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

· If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the  $\overline{\text{TO}}$  bit will be set and the  $\overline{\text{PD}}$  bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

|                                | Q1 Q2 Q3 Q4     |              | Q1 Q2 Q3 Q4  | Q1 Q2 Q3 Q4                           | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 |

|--------------------------------|-----------------|--------------|--------------|---------------------------------------|-------------|-------------|

|                                |                 |              |              |                                       |             |             |

|                                | /               | Tost(2)      |              | ،<br>۱                                |             |             |

| INT pin                        | 1               |              |              | 1 1<br>1 1                            |             |             |

| INTF flag                      | 1               | Δ,           |              | Interrupt Latency                     |             |             |

| (INTCOŇ<1>)                    | +               | /            |              | (Note 2)                              |             |             |

| GIE bit                        | <u> </u>        | Processor in |              |                                       | 1           |             |

| (INTCON<7>)                    | r <b>∢</b><br>' | SLEEP        |              | 1 I                                   | 1           |             |

| INSTRUCTION FLOW               | 1               |              |              | i i<br>i i                            | 1           |             |

| PC X PC X                      | PC+1 X          | PC+2         | PC+2         | X PC + 2                              | 0004h       | 0005h       |

| Instruction { Inst(PC) = SLEEP | Inst(PC + 1)    | 1            | Inst(PC + 2) | · · · · · · · · · · · · · · · · · · · | Inst(0004h) | Inst(0005h) |

| Instruction Inst(PC - 1)       | SLEEP           | 1            | Inst(PC + 1) | Dummy cycle                           | Dummy cycle | Inst(0004h) |

#### FIGURE 10-14: WAKE-UP FROM SLEEP THROUGH INTERRUPT

- 3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

CLKOUT is not available in these osc modes, but shown here for timing reference.

## 10.14 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

## 10.15 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

#### In-Circuit Serial Programming<sup>™</sup> 10.16

PIC16CXXX family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For complete details of serial programming, please refer to the In-Circuit Serial Programming (ICSP™) Guide, DS30277.

#### 13.1 DC Characteristics: PIC16C72/CR72-04 (Commercial, Industrial, Extended) PIC16C72/CR72-10 (Commercial, Industrial, Extended) PIC16C72/CR72-20 (Commercial, Industrial, Extended)

|               | Standard Operating Conditions (unless otherwise stated)           |                       |            |         |                                    |                                      |                                                   |                       |        |                                                    |  |  |

|---------------|-------------------------------------------------------------------|-----------------------|------------|---------|------------------------------------|--------------------------------------|---------------------------------------------------|-----------------------|--------|----------------------------------------------------|--|--|

| DC CHA        | RACTERISTICS                                                      | Standard<br>Operating | •          | 0       | itions (u<br>-40°C<br>-40°C<br>0°C | $\leq TA \leq H$<br>$\leq TA \leq H$ | +125°C for<br>+85°C for<br>⊦85°C for<br>⊦70°C for | or extend<br>industri | al and |                                                    |  |  |

| Param         | Characteristic                                                    | Sym                   | F          | PIC16C7 | 2                                  | Р                                    | IC16CR7                                           | 72                    | Units  | Conditions                                         |  |  |

| No.           | onaracteristic                                                    | Oym                   | Min        | Тур†    | Max                                | Min                                  | Тур†                                              | Мах                   | Units  | Conditions                                         |  |  |

| D001<br>D001A | Supply Voltage                                                    | Vdd                   | 4.0<br>4.5 |         | <b>6.0</b><br>5.5                  | 4.0<br>4.5                           | -                                                 | <b>5.5</b><br>5.5     | V<br>V | XT, RC and LP osc<br>HS osc                        |  |  |

| D002*         | RAM Data Retention<br>Voltage (Note 1)                            | Vdr                   | -          | 1.5     | -                                  | -                                    | 1.5                                               | -                     | V      |                                                    |  |  |

| D003          | VDD start voltage to<br>ensure internal Power-<br>on Reset Signal | VPOR                  | -          | Vss     | -                                  | -                                    | Vss                                               | -                     | V      | See section on Power-<br>on Reset for details      |  |  |

| D004*         | VDD rise rate to ensure<br>internal Power-on<br>Reset Signal      | SVDD                  | 0.05       | -       | -                                  | 0.05                                 | -                                                 | -                     | V/ms   | See section on Power-<br>on Reset for details      |  |  |

| D005          | Brown-out Reset Volt-<br>age                                      | Bvdd                  | 3.7        | 4.0     | 4.3                                | 3.7                                  | 4.0                                               | 4.3                   | V      | BODEN bit in configura-<br>tion word enabled       |  |  |

|               |                                                                   |                       | 3.7        | 4.0     | 4.4                                | 3.7                                  | 4.0                                               | 4.4                   | V      | Extended Only                                      |  |  |

| D010          | Supply Current<br>(Note 2,5)                                      | IDD                   | -          | 2.7     | 5.0                                | -                                    | 2.7                                               | 5.0                   | mA     | XT, RC osc<br>Fosc = 4 MHz,<br>VDD = 5.5V (Note 4) |  |  |

| D013          |                                                                   |                       | -          | 10      | 20                                 | -                                    | 10                                                | 20                    | mA     | HS osc<br>Fosc = 20 MHz,<br>VDD = 5.5V             |  |  |

| D015          | Brown-out Reset<br>Current (Note 6)                               | ∆lbor                 | -          | 350     | 425                                | -                                    | 350                                               | 425                   | μA     | BOR enabled,<br>VDD = 5.0V                         |  |  |

| D020          | Power-down Current<br>(Note 3,5)                                  | IPD                   | -          | 10.5    | 42                                 | -                                    | 10.5                                              | 42                    | μA     | VDD = 4.0V, WDT<br>enabled, -40°C to +85°C         |  |  |

| D021          |                                                                   |                       | -          | 1.5     | 16                                 | -                                    | 1.5                                               | 16                    | μΑ     | VDD = 4.0V, WDT dis-<br>abled, -0°C to +70°C       |  |  |

| D021A         |                                                                   |                       | -          | 1.5     | 19                                 | -                                    | 1.5                                               | 19                    | μΑ     | VDD = 4.0V, WDT dis-<br>abled, -40°C to +85°C      |  |  |

| D021B         |                                                                   |                       | -          | 2.5     | 19                                 | -                                    | 2.5                                               | 19                    | μA     | VDD = 4.0V, WDT dis-<br>abled, -40°C to +125°C     |  |  |

| D023          | Brown-out Reset<br>Current (Note 6)                               | ∆lbor                 | -          | 350     | 425                                | -                                    | 350                                               | 425                   | μΑ     | BOR enabled VDD = 5.0V                             |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

Note 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

**Note 3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

**Note 4:** For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

**Note 5:** Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

**Note 6:** The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

## 13.2 DC Characteristics: PIC16LC72/LCR72-04 (Commercial, Industrial)

| DC CHA | DC CHARACTERISTICSStandard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ for industrial and $0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ for commercial |            |      |         |     |      |         |     |       |                                                                    |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|---------|-----|------|---------|-----|-------|--------------------------------------------------------------------|--|

| Param  |                                                                                                                                                                                                                      | <b>C</b> 1 | F    | PIC16C7 | 2   | Р    | IC16CR7 | 72  | Unite | Conditions                                                         |  |

| No.    | Characteristic                                                                                                                                                                                                       | Sym        | Min  | Typ†    | Max | Min  | Typ†    | Max | Units | Conditions                                                         |  |

| D001   | Supply Voltage                                                                                                                                                                                                       | Vdd        | 2.5  | -       | 6.0 | 2.5  | -       | 5.5 | V     | LP, XT, RC (DC - 4 MHz)                                            |  |

| D002*  | RAM Data Retention<br>Voltage (Note 1)                                                                                                                                                                               | VDR        | -    | 1.5     | -   | -    | 1.5     | -   | V     |                                                                    |  |

| D003   | VDD start voltage to<br>ensure internal Power-<br>on Reset signal                                                                                                                                                    | VPOR       | -    | Vss     | -   | -    | Vss     | -   | V     | See section on Power-<br>on Reset for details                      |  |

| D004*  | VDD rise rate to ensure<br>internal Power-on<br>Reset signal                                                                                                                                                         | SVDD       | 0.05 | -       | -   | 0.05 | -       | -   | V/ms  | See section on Power-<br>on Reset for details                      |  |

| D005   | Brown-out Reset Volt-<br>age                                                                                                                                                                                         | Bvdd       | 3.7  | 4.0     | 4.3 | 3.7  | 4.0     | 4.3 | V     | BODEN bit in configura-<br>tion word enabled                       |  |

| D010   | Supply Current<br>(Note 2,5)                                                                                                                                                                                         | IDD        | -    | 2.0     | 3.8 | -    | 2.0     | 3.8 | mA    | XT, RC osc configuration<br>Fosc = 4 MHz, VDD =<br>3.0V (Note 4)   |  |

| D010A  |                                                                                                                                                                                                                      |            | -    | 22.5    | 48  | -    | 22.5    | 48  | μA    | LP osc configuration<br>Fosc = 32 kHz, VDD =<br>3.0V, WDT disabled |  |

| D015*  | Brown-out Reset<br>Current (Note 6)                                                                                                                                                                                  | ∆lbor      | -    | 350     | 425 | -    | 350     | 425 | μA    | BOR enabled VDD = 5.0V                                             |  |

| D020   | Power-down Current<br>(Note 3,5)                                                                                                                                                                                     | IPD        | -    | 7.5     | 30  | -    | 7.5     | 30  | μA    | VDD = 3.0V, WDT<br>enabled, -40°C to +85°C                         |  |

| D021   |                                                                                                                                                                                                                      |            | -    | 0.9     | 5   | -    | 0.9     | 5   | μA    | VDD = 3.0V, WDT dis-<br>abled, 0°C to +70°C                        |  |

| D021A  |                                                                                                                                                                                                                      |            | -    | 0.9     | 5   | -    | 0.9     | 5   | μA    | VDD = 3.0V, WDT dis-<br>abled, -40°C to +85°C                      |  |

| D023*  | Brown-out Reset<br>Current (Note 6)                                                                                                                                                                                  | ∆lbor      | -    | 350     | 425 | -    | 350     | 425 | μA    | BOR enabled VDD = 5.0V                                             |  |

\* These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

**Note 2:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

**Note 3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

**Note 4:** For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

**Note 5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

**Note 6:** The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

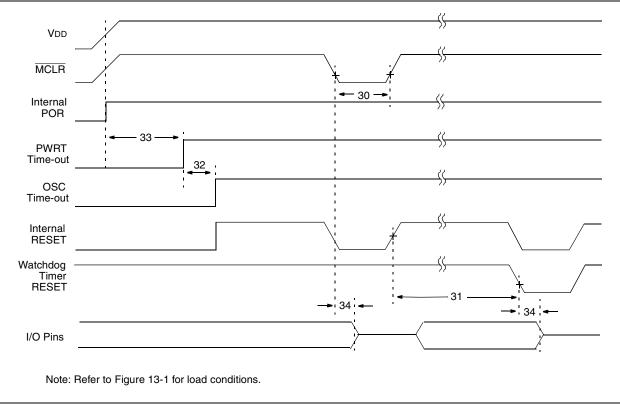

#### FIGURE 13-5: BROWN-OUT RESET TIMING

## TABLE 13-5RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                            | Min | Тур†     | Max | Units | Conditions                |

|------------------|-------|-----------------------------------------------------------|-----|----------|-----|-------|---------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                    | 2   | _        | —   | μs    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)          | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period                         | _   | 1024Tosc | _   | —     | Tosc = OSC1 period        |

| 33*              | Tpwrt | Power-up Timer Period                                     | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34               | Tioz  | I/O Hi-impedance from MCLR Low<br>or Watchdog Timer Reset | —   | _        | 2.1 | μs    |                           |

| 35               | TBOR  | Brown-out Reset pulse width                               | 100 | _        |     | μS    | $VDD \le BVDD$ (D005)     |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

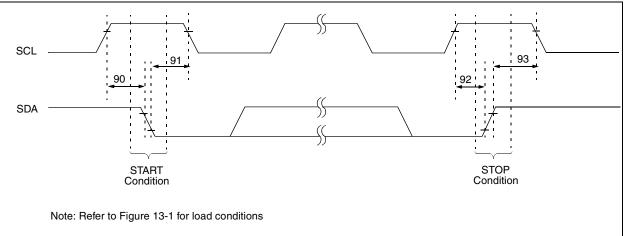

## FIGURE 13-12: I<sup>2</sup>C BUS START/STOP BITS TIMING

| Parameter<br>No. | Sym     | Characteristic  |              | Min  | Тур | Max | Units | Conditions                        |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|

| 90               | TSU:STA | START condition | 100 kHz mode | 4700 |     |     | ns    | Only relevant for repeated START  |

|                  |         | Setup time      | 400 kHz mode | 600  | _   | _   |       | condition                         |

| 91               | THD:STA | START condition | 100 kHz mode | 4000 | _   |     | ns    | After this period the first clock |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   |       | pulse is generated                |

| 92               | TSU:STO | STOP condition  | 100 kHz mode | 4700 | _   |     | ns    |                                   |

|                  |         | Setup time      | 400 kHz mode | 600  | _   |     |       |                                   |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | —   | —   | ns    |                                   |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   |       |                                   |

## PIC16C72 Series PIC16C72

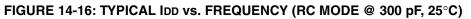

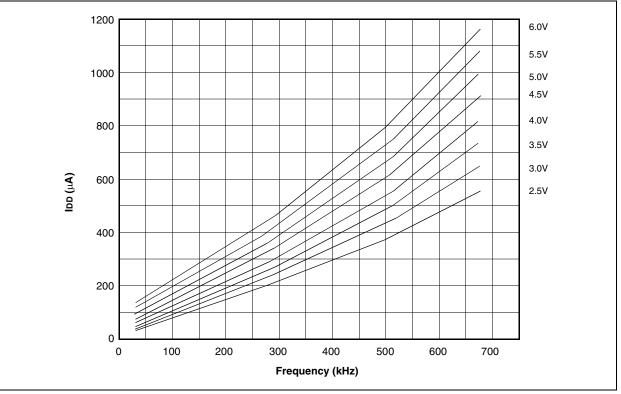

FIGURE 14-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

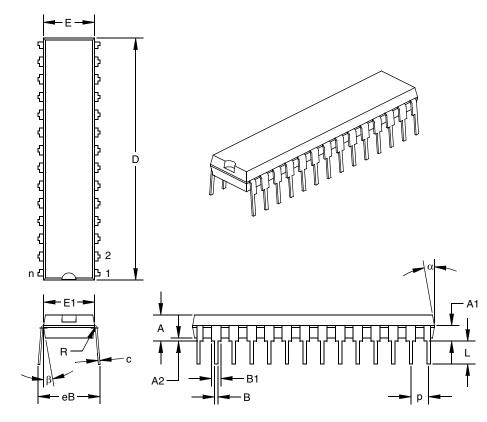

### 16.3 <u>28-Lead Plastic Dual In-line (300 mil) (SP)</u>

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                        |                 |       | INCHES* |       | М     | ILLIMETER | S     |

|------------------------------|-----------------|-------|---------|-------|-------|-----------|-------|

| Dimension Limits             |                 | MIN   | NOM     | MAX   | MIN   | NOM       | MAX   |

| PCB Row Spacing              |                 |       | 0.300   |       |       | 7.62      |       |

| Number of Pins               | n               |       | 28      |       |       | 28        |       |

| Pitch                        | р               |       | 0.100   |       |       | 2.54      |       |

| Lower Lead Width             | В               | 0.016 | 0.019   | 0.022 | 0.41  | 0.48      | 0.56  |

| Upper Lead Width             | B1 <sup>†</sup> | 0.040 | 0.053   | 0.065 | 1.02  | 1.33      | 1.65  |

| Shoulder Radius              | R               | 0.000 | 0.005   | 0.010 | 0.00  | 0.13      | 0.25  |

| Lead Thickness               | с               | 0.008 | 0.010   | 0.012 | 0.20  | 0.25      | 0.30  |

| Top to Seating Plane         | А               | 0.140 | 0.150   | 0.160 | 3.56  | 3.81      | 4.06  |

| Top of Lead to Seating Plane | A1              | 0.070 | 0.090   | 0.110 | 1.78  | 2.29      | 2.79  |

| Base to Seating Plane        | A2              | 0.015 | 0.020   | 0.025 | 0.38  | 0.51      | 0.64  |

| Tip to Seating Plane         | L               | 0.125 | 0.130   | 0.135 | 3.18  | 3.30      | 3.43  |

| Package Length               | D‡              | 1.345 | 1.365   | 1.385 | 34.16 | 34.67     | 35.18 |

| Molded Package Width         | E‡              | 0.280 | 0.288   | 0.295 | 7.11  | 7.30      | 7.49  |

| Radius to Radius Width       | E1              | 0.270 | 0.283   | 0.295 | 6.86  | 7.18      | 7.49  |

| Overall Row Spacing          | eB              | 0.320 | 0.350   | 0.380 | 8.13  | 8.89      | 9.65  |

| Mold Draft Angle Top         | α               | 5     | 10      | 15    | 5     | 10        | 15    |

| Mold Draft Angle Bottom      | β               | 5     | 10      | 15    | 5     | 10        | 15    |

\* Controlling Parameter.

<sup>†</sup> Dimension "B1" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B1."

Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."

| Block Diagram47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sup>2</sup> C Operation47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Master Mode51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Mode47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Mode Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Multi-Master Mode51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 49 Reception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Reception Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SCL and SDA pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Slave Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| In-Circuit Serial Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| INDF Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Indirect Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |