Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

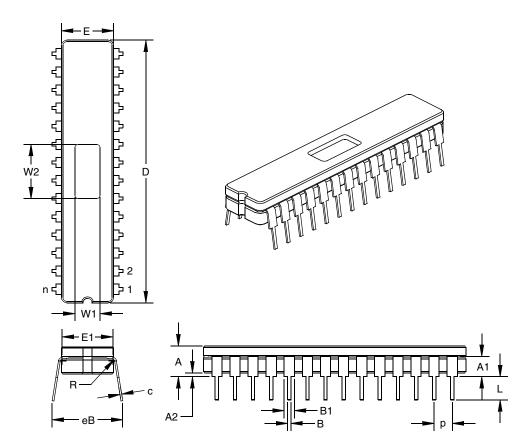

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c72-04i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

|                                                              | •   |

|--------------------------------------------------------------|-----|

| 1.0 Device Overview                                          |     |

| 2.0 Memory Organization                                      |     |

| 3.0 I/O Ports                                                | 19  |

| 4.0 Timer0 Module                                            | 25  |

| 5.0 Timer1 Module                                            | 27  |

| 6.0 Timer2 Module                                            | 31  |

| 7.0 Capture/Compare/PWM (CCP) Module                         | 33  |

| 8.0 Synchronous Serial Port (SSP) Module                     | 39  |

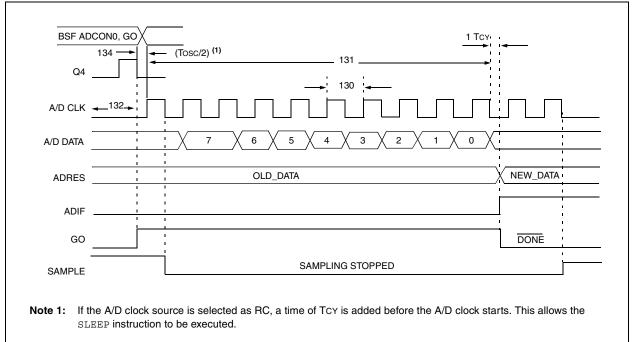

| 9.0 Analog-to-Digital Converter (A/D) Module                 | 53  |

| 10.0 Special Features of the CPU                             | 59  |

| 11.0 Instruction Set Summary                                 | 73  |

| 12.0 Development Support                                     | 75  |

| 13.0 Electrical Characteristics - PIC16C72 Series            | 77  |

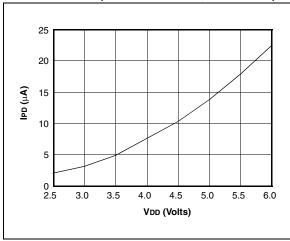

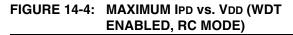

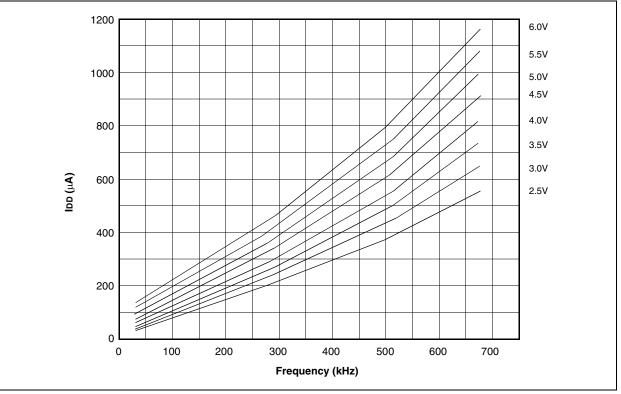

| 14.0 DC and AC Characteristics Graphs and Tables - PIC16C72  |     |

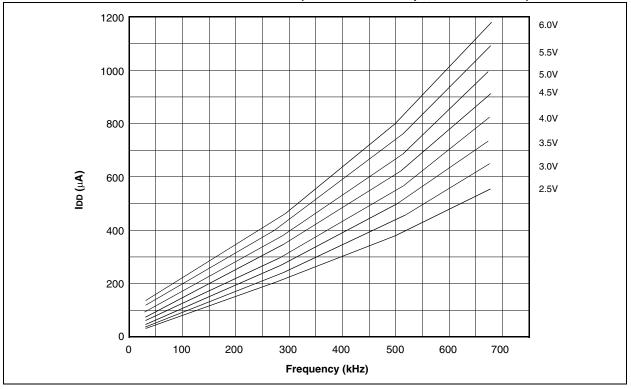

| 15.0 DC and AC Characteristics Graphs and Tables - PIC16CR72 | 107 |

| 16.0 Packaging Information                                   |     |

| Appendix A: What's New in this Data Sheet                    | 115 |

| Appendix B: What's Changed in this Data Sheet                | 115 |

| Appendix C: Device Differences                               | 115 |

| Index                                                        |     |

| On-Line Support                                              | 121 |

| Reader Response                                              |     |

| PIC16C72 Series Product Identification System                | 125 |

| Sales and Support                                            |     |

# To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

| Key Reference Manual Features         | PIC16C72               | PIC16CR72              |

|---------------------------------------|------------------------|------------------------|

| Operating Frequency                   | DC - 20MHz             | DC - 20MHz             |

| Resets                                | POR, PWRT, OST, BOR    | POR, PWRT, OST, BOR    |

| Program Memory - (14-bit words)       | 2K (EPROM)             | 2K (ROM)               |

| Data Memory - RAM (8-bit bytes)       | 128                    | 128                    |

| Interrupts                            | 8                      | 8                      |

| I/O Ports                             | PortA, PortB, PortC    | PortA, PortB, PortC    |

| Timers                                | Timer0, Timer1, Timer2 | Timer0, Timer1, Timer2 |

| Capture/Compare/PWM Modules           | 1                      | 1                      |

| Serial Communications                 | Basic SSP              | SSP                    |

| 8-Bit A/D Converter                   | 5 channels             | 5 channels             |

| Instruction Set (No. of Instructions) | 35                     | 35                     |

| TABLE 1-1PIC16C72/CR72 PINOUT DESCRIPTION | TABLE 1-1 | PIC16C72/CR72 PINOUT DESCRIPTION |

|-------------------------------------------|-----------|----------------------------------|

|-------------------------------------------|-----------|----------------------------------|

| Pin Name          | lame Pin# I/O/P Buffer<br>Type Type |     | Buffer<br>Type         | Description                                                                                                                                                                                                 |  |  |  |  |  |

|-------------------|-------------------------------------|-----|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| OSC1/CLKIN        | 9                                   | I   | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                       |  |  |  |  |  |

| OSC2/CLKOUT       | 10                                  | 0   | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate |  |  |  |  |  |

| MCLR/VPP          | 1                                   | I/P | ST                     | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                     |  |  |  |  |  |

|                   |                                     |     |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                         |  |  |  |  |  |

| RA0/AN0           | 2                                   | I/O | TTL                    | RA0 can also be analog input0.                                                                                                                                                                              |  |  |  |  |  |

| RA1/AN1           | 3                                   | I/O | TTL                    | RA1 can also be analog input1.                                                                                                                                                                              |  |  |  |  |  |

| RA2/AN2           | 4                                   | I/O | TTL                    | RA2 can also be analog input2.                                                                                                                                                                              |  |  |  |  |  |

| RA3/AN3/VREF      | 5                                   | I/O | TTL                    | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                   |  |  |  |  |  |

| RA4/T0CKI         | 6                                   | I/O | ST                     | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                            |  |  |  |  |  |

| RA5/SS/AN4        | 7                                   | I/O | TTL                    | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                          |  |  |  |  |  |

|                   |                                     |     |                        | PORTB is a bi-directional I/O port. PORTB can be software                                                                                                                                                   |  |  |  |  |  |

|                   |                                     |     |                        | programmed for internal weak pull-up on all inputs.                                                                                                                                                         |  |  |  |  |  |

| RB0/INT           | 21                                  | I/O | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                 |  |  |  |  |  |

| RB1               | 22                                  | I/O | TTL                    |                                                                                                                                                                                                             |  |  |  |  |  |

| RB2               | 23                                  | I/O | TTL                    |                                                                                                                                                                                                             |  |  |  |  |  |

| RB3               | 24                                  | I/O | TTL                    |                                                                                                                                                                                                             |  |  |  |  |  |

| RB4               | 25                                  | I/O | TTL                    | Interrupt on change pin.                                                                                                                                                                                    |  |  |  |  |  |

| RB5               | 26                                  | I/O | TTL                    | Interrupt on change pin.                                                                                                                                                                                    |  |  |  |  |  |

| RB6               | 27                                  | I/O | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                          |  |  |  |  |  |

| RB7               | 28                                  | I/O | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                           |  |  |  |  |  |

|                   |                                     |     |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                         |  |  |  |  |  |

| RC0/T1OSO/T1CKI   | 11                                  | I/O | ST                     | RC0 can also be the Timer1 oscillator output or Timer1 clock input.                                                                                                                                         |  |  |  |  |  |

| RC1/T1OSI         | 12                                  | I/O | ST                     | RC1 can also be the Timer1 oscillator input.                                                                                                                                                                |  |  |  |  |  |

| RC2/CCP1          | 13                                  | I/O | ST                     | RC2 can also be the Capture1 input/Compare1 output/PWM1 output.                                                                                                                                             |  |  |  |  |  |

| RC3/SCK/SCL       | 14                                  | I/O | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                          |  |  |  |  |  |

| RC4/SDI/SDA       | 15                                  | I/O | ST                     | RC4 can also be the SPI Data In (SPI mode) or data $I/O$ (I <sup>2</sup> C mode).                                                                                                                           |  |  |  |  |  |

| RC5/SDO           | 16                                  | I/O | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                |  |  |  |  |  |

| RC6               | 17                                  | I/O | ST                     |                                                                                                                                                                                                             |  |  |  |  |  |

| RC7               | 18                                  | I/O | ST                     |                                                                                                                                                                                                             |  |  |  |  |  |

| Vss               | 8, 19                               | P   | _                      | Ground reference for logic and I/O pins.                                                                                                                                                                    |  |  |  |  |  |

| VDD               | 20                                  | P   | <u> </u>               | Positive supply for logic and I/O pins.                                                                                                                                                                     |  |  |  |  |  |

| Legend: I = input | O = output                          | 1   | I/O = input/o          |                                                                                                                                                                                                             |  |  |  |  |  |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

# The special function registers can be classified into two TABLE 2-1 SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                              | Bit 6              | Bit 5         | Bit 4          | Bit 3         | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(3) |

|----------------------|---------|------------------------------------|--------------------|---------------|----------------|---------------|-----------------|---------------|-----------|--------------------------|-------------------------------------|

| Bank 0               |         |                                    |                    |               |                |               |                 |               |           |                          |                                     |

| 00h <sup>(1)</sup>   | INDF    | Addressing                         | this location      | uses conten   | ts of FSR to   | address data  | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                           |

| 01h                  | TMR0    | Timer0 mod                         | ule's registe      | r             |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                           |

| 02h <sup>(1)</sup>   | PCL     | Program Co                         | ounter's (PC)      | Least Signif  | icant Byte     |               |                 |               |           | 0000 0000                | 0000 0000                           |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(4)</sup>                 | RP1 <sup>(4)</sup> | RP0           | TO             | PD            | Z               | DC            | С         | 0001 1xxx                | 000q quuu                           |

| 04h <sup>(1)</sup>   | FSR     | Indirect data                      | a memory ad        | ldress pointe | r              |               |                 |               |           | xxxx xxxx                | uuuu uuuu                           |

| 05h                  | PORTA   | _                                  | -                  | PORTA Dat     | a Latch whe    | n written: PO | RTA pins wh     | ien read      |           | 0x 0000                  | 0u 0000                             |

| 06h                  | PORTB   | PORTB Dat                          | a Latch whe        | n written: PC | ORTB pins wl   | nen read      |                 |               |           | XXXX XXXX                | uuuu uuuu                           |

| 07h                  | PORTC   | PORTC Dat                          | a Latch whe        | n written: PC | ORTC pins w    | hen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                           |

| 08h                  | —       | Unimplemen                         | nted               |               |                |               |                 |               |           | —                        | —                                   |

| 09h                  | _       | Unimplemen                         | Unimplemented      |               |                |               |                 |               |           |                          |                                     |

| 0Ah <sup>(1,2)</sup> | PCLATH  | —                                  |                    |               | Write Buffer   | for the uppe  | er 5 bits of th | e Program C   | ounter    | 0 0000                   | 0 0000                              |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                                | PEIE               | TOIE          | INTE           | RBIE          | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                           |

| 0Ch                  | PIR1    | —                                  | ADIF               | —             | —              | SSPIF         | CCP1IF          | TMR2IF        | TMR1IF    | -0 0000                  | -0 0000                             |

| 0Dh                  | —       | Unimplemen                         | nted               |               |                |               |                 |               |           | —                        | —                                   |

| 0Eh                  | TMR1L   | Holding regi                       | ster for the L     | east Signific | ant Byte of t  | he 16-bit TM  | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                           |

| 0Fh                  | TMR1H   | Holding regi                       | ster for the M     | Most Signific | ant Byte of th | ne 16-bit TMF | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                           |

| 10h                  | T1CON   | —                                  | -                  | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC          | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                             |

| 11h                  | TMR2    | Timer2 mod                         | ule's registe      | r             |                |               |                 |               |           | 0000 0000                | 0000 0000                           |

| 12h                  | T2CON   | —                                  | TOUTPS3            | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON          | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                           |

| 13h                  | SSPBUF  | Synchronou                         | s Serial Port      | Receive Bu    | ffer/Transmit  | Register      |                 |               |           | XXXX XXXX                | uuuu uuuu                           |

| 14h                  | SSPCON  | WCOL                               | SSPOV              | SSPEN         | СКР            | SSPM3         | SSPM2           | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                           |

| 15h                  | CCPR1L  | Capture/Compare/PWM Register (LSB) |                    |               |                |               |                 |               |           |                          | uuuu uuuu                           |

| 16h                  | CCPR1H  | Capture/Cor                        | mpare/PWM          | Register (M   | SB)            |               |                 |               |           | XXXX XXXX                | uuuu uuuu                           |

| 17h                  | CCP1CON | —                                  | —                  | CCP1X         | CCP1Y          | CCP1M3        | CCP1M2          | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                             |

| 18h-1Dh              | _       | Unimplemer                         | nted               |               |                |               |                 |               |           | _                        |                                     |

| 1Eh                  | ADRES   | A/D Result I                       | Register           |               |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                           |

| 1Fh                  | ADCON0  | ADCS1                              | ADCS0              | CHS2          | CHS1           | CHS0          | GO/DONE         | _             | ADON      | 0000 00-0                | 0000 00-0                           |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved on the PIC16C72/CR72. Always maintain these bits clear.

5: SSPSTAT<7:6> are not implemented on the PIC16C72, read as '0'.

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

# EXAMPLE 2-1: INDIRECT ADDRESSING

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDR register now will return the value of 0Ah.

**Direct Addressing** Indirect Addressing RP1:RP0 from opcode 7 6 0 IRP FSR register 0 (2) (2)bank select location select bank select location select • 00 01 10 11 00h 80h 100h 180h not used (3) (3) Data Memory(1) FFh 1FFh 7Fh 17Fh Bank 0 Bank 1 Bank 2 Bank 3 Note 1: For register file map detail see Figure 2-2. 2: Maintain RP1 and IRP as clear for upward compatibility with future products. 3: Not implemented.

# FIGURE 2-11: DIRECT/INDIRECT ADDRESSING

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | movwf<br>clrf<br>incf | FSR<br>INDF<br>FSR | ;clear INDF register<br>;inc pointer |

|----------|-----------------------|--------------------|--------------------------------------|

|          | goto                  | -                  | ;all done?<br>;NO, clear next        |

| CONTINUE |                       |                    |                                      |

|          | :                     |                    | ;YES, continue                       |

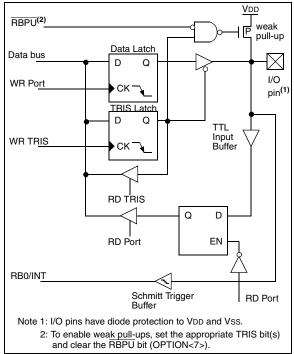

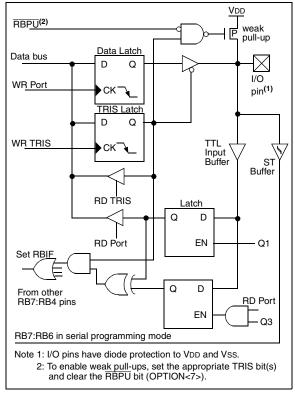

### 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output, i.e., put the contents of the output latch on the selected pin.

#### EXAMPLE 3-1: INITIALIZING PORTB

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| CLRF  | PORTB   |     | ; | Initialize PORTB by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISB   |     | ; | Set RB<3:0> as inputs |

|       |         |     | ; | RB<5:4> as outputs    |

|       |         |     | ; | RB<7:6> as inputs     |

|       |         |     |   |                       |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\text{RBPU}}$  (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

#### FIGURE 3-4: BLOCK DIAGRAM OF RB7:RB4 PINS

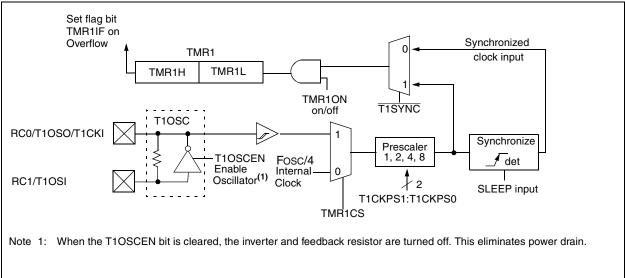

# FIGURE 5-2: TIMER1 BLOCK DIAGRAM

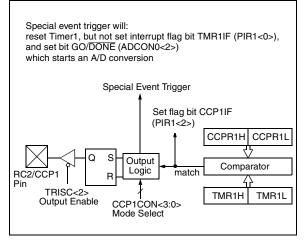

# 7.2 <u>Compare Mode</u>

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- driven High

- driven Low

- remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

### FIGURE 7-3: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 7.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force       |  |  |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|--|--|

|       | the RC2/CCP1 compare output latch to the       |  |  |  |  |  |  |  |

|       | default low level. This is not the data latch. |  |  |  |  |  |  |  |

#### 7.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 7.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 7.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special trigger output of CCP1 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

Note: The special event trigger from the CCP1 module will not set interrupt flag bit TMR1IF (PIR1<0>).

# TABLE 7-2 REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address | Name    | Bit 7                         | Bit 6                               | Bit 5        | Bit 4       | Bit 3         | Bit 2      | Bit 1       | Bit 0  | PC   | e on:<br>)R,<br>)R | all o | e on<br>other<br>sets |

|---------|---------|-------------------------------|-------------------------------------|--------------|-------------|---------------|------------|-------------|--------|------|--------------------|-------|-----------------------|

| 0Bh,8Bh | INTCON  | GIE                           | PEIE                                | TOIE         | INTE        | RBIE          | T0IF       | INTF        | RBIF   | 0000 | 000x               | 0000  | 000u                  |

| 0Ch     | PIR1    | (1)                           | ADIF                                | (1)          | (1)         | SSPIF         | CCP1IF     | TMR2IF      | TMR1IF | 0000 | 0000               | 0000  | 0000                  |

| 8Ch     | PIE1    | (1)                           | ADIE                                | (1)          | (1)         | SSPIE         | CCP1IE     | TMR2IE      | TMR1IE | 0000 | 0000               | 0000  | 0000                  |

| 87h     | TRISC   | PORTC Data Direction Register |                                     |              |             |               |            |             |        |      | 1111               | 1111  | 1111                  |

| 0Eh     | TMR1L   | Holding reg                   | gister fo                           | or the Least | Significant | Byte of the   | 16-bit TMF | R1 register |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 0Fh     | TMR1H   | Holding reg                   | gister fo                           | or the Most  | Significant | Byte of the 1 | 16-bit TMR | 1register   |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 10h     | T1CON   | —                             |                                     | T1CKPS1      | T1CKPS0     | T1OSCEN       | T1SYNC     | TMR1CS      | TMR1ON | 00   | 0000               | uu    | uuuu                  |

| 15h     | CCPR1L  | Capture/Co                    | Capture/Compare/PWM register1 (LSB) |              |             |               |            |             |        |      | xxxx               | uuuu  | uuuu                  |

| 16h     | CCPR1H  | Capture/Co                    | Capture/Compare/PWM register1 (MSB) |              |             |               |            |             |        |      | xxxx               | uuuu  | uuuu                  |

| 17h     | CCP1CON | —                             |                                     | CCP1X        | CCP1Y       | CCP1M3        | CCP1M2     | CCP1M1      | CCP1M0 | 00   | 0000               | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1. Note 1: These bits/registers are unimplemented, read as '0'.

# **PIC16C72 Series**

### 8.2 SPI Mode for PIC16C72

Г

This section contains register definitions and operational characteristics of the SPI module on the PIC16C72 device only. Additional information on SPI operation may be found in the PIC<sup>®</sup> Mid-Range MCU Reference Manual, DS33023.

1

# FIGURE 8-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h) (PIC16C72)

| U-0      | U-0                                                                                                                                                                                                                                                                    | R-0                           | R-0        | R-0                                                     | R-0           | R-0          | R-0         |                                                                                      |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------|---------------------------------------------------------|---------------|--------------|-------------|--------------------------------------------------------------------------------------|--|--|--|--|

|          | —                                                                                                                                                                                                                                                                      | D/A                           | Р          | S                                                       | R/W           | UA           | BF          | R = Readable bit                                                                     |  |  |  |  |

| bit7     |                                                                                                                                                                                                                                                                        |                               |            |                                                         |               |              | bitO        | W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |  |  |  |  |

| bit 7-6: | Unimpl                                                                                                                                                                                                                                                                 | emented                       | : Read as  | '0'                                                     |               |              |             |                                                                                      |  |  |  |  |

| bit 5:   | <ul> <li>D/A: Data/Address bit (l<sup>2</sup>C mode only)</li> <li>1 = Indicates that the last byte received or transmitted was data</li> <li>0 = Indicates that the last byte received or transmitted was address</li> </ul>                                          |                               |            |                                                         |               |              |             |                                                                                      |  |  |  |  |

| bit 4:   | <ul> <li>P: Stop bit (I<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, SSPEN is cleared)</li> <li>1 = Indicates that a stop bit has been detected last (this bit is '0' on RESET)</li> <li>0 = Stop bit was not detected last</li> </ul> |                               |            |                                                         |               |              |             |                                                                                      |  |  |  |  |

| bit 3:   | <ul> <li>Start bit (I<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, SSPEN is cleared)</li> <li>1 = Indicates that a start bit has been detected last (this bit is '0' on RESET)</li> <li>0 = Start bit was not detected last</li> </ul> |                               |            |                                                         |               |              |             |                                                                                      |  |  |  |  |

| bit 2:   | This bit                                                                                                                                                                                                                                                               | holds the<br>o the next<br>ad | R/W bit i  | ation (I <sup>2</sup> C r<br>nformation<br>stop bit, or | following the | e last addre | ss match. T | his bit is valid from the address                                                    |  |  |  |  |

| bit 1:   | 1 = Indi                                                                                                                                                                                                                                                               | cates that                    | the user i | t I <sup>2</sup> C mode<br>needs to up<br>to be upda    | odate the add | dress in the | SSPADD re   | egister                                                                              |  |  |  |  |

| bit 0:   | BF: Buf                                                                                                                                                                                                                                                                | fer Full St                   | atus bit   |                                                         |               |              |             |                                                                                      |  |  |  |  |

|          | <u>Receive</u> (SPI and I <sup>2</sup> C modes)<br>1 = Receive complete, SSPBUF is full<br>0 = Receive not complete, SSPBUF is empty                                                                                                                                   |                               |            |                                                         |               |              |             |                                                                                      |  |  |  |  |

|          | 1 = Trar                                                                                                                                                                                                                                                               |                               | ogress, S  | SPBUF is f<br>PBUF is en                                |               |              |             |                                                                                      |  |  |  |  |

# FIGURE 8-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h) (PIC16C72)

| R/W-0    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                             | R/W-0                                                                                                                                    | R/W-0                                                                                                                  | R/W-0                                                                                            | R/W-0                                                         | R/W-0                   |                                                                                      |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

| WCOL     | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SSPEN                                                                                                                                             | CKP                                                                                                                                      | SSPM3                                                                                                                  | SSPM2                                                                                            | SSPM1                                                         | SSPM0                   | R = Readable bit                                                                     |  |  |  |  |

| bit7     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                   |                                                                                                                                          |                                                                                                                        |                                                                                                  |                                                               | bit0                    | W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |  |  |  |  |

| bit 7:   | 1 = The S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | cleared in s                                                                                                                                      | gister is w                                                                                                                              |                                                                                                                        | e it is still tr                                                                                 | ansmitting                                                    | g the previou           |                                                                                      |  |  |  |  |

| bit 6:   | SSPOV: F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Receive Ov                                                                                                                                        | erflow De                                                                                                                                | tect bit                                                                                                               |                                                                                                  |                                                               |                         |                                                                                      |  |  |  |  |

|          | In SPI mode         1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR register is lost. Overflow can only occur in slave mode. The user must read the SSP-BUF, even if only transmitting data, to avoid setting overflow. In master operation, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.         0 = No overflow         In l <sup>2</sup> C mode |                                                                                                                                                   |                                                                                                                                          |                                                                                                                        |                                                                                                  |                                                               |                         |                                                                                      |  |  |  |  |

|          | 1 = A byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | is received<br>t mode. SS                                                                                                                         |                                                                                                                                          | SSPBUF i<br>st be cleare                                                                                               |                                                                                                  |                                                               |                         | us byte. SSPOV is a "don't care"                                                     |  |  |  |  |

| bit 5:   | SSPEN: S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Synchronou                                                                                                                                        | us Serial F                                                                                                                              | Port Enable                                                                                                            | e bit                                                                                            |                                                               |                         |                                                                                      |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | es serial po                                                                                                                                      |                                                                                                                                          | nfigures So<br>onfigures th                                                                                            |                                                                                                  |                                                               | is serial por<br>t pins | t pins                                                                               |  |  |  |  |

|          | 0 = Disabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | es the seria<br>les serial p                                                                                                                      | ort and co                                                                                                                               | onfigures th                                                                                                           | nese pins a                                                                                      | as I/O port                                                   |                         | al port pins<br>s input or output.                                                   |  |  |  |  |

| bit 4:   | CKP: Cloc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ck Polarity                                                                                                                                       | Select bit                                                                                                                               |                                                                                                                        |                                                                                                  |                                                               |                         |                                                                                      |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ate for cloc                                                                                                                                      |                                                                                                                                          |                                                                                                                        |                                                                                                  |                                                               |                         | receive on rising edge.<br>ceive on falling edge.                                    |  |  |  |  |

|          | 1 = Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ase control<br>e clock                                                                                                                            | clock stre                                                                                                                               | etch) (Used                                                                                                            | to ensure                                                                                        | data setu                                                     | p time)                 |                                                                                      |  |  |  |  |

| bit 3-0: | 0001 = SI 0010 = SI 0011 = SI 0100 = SI 0101 = SI 0110 = I2 0111 = I2 1011 = I2 1110 = I2                                                                                                                                                                                                                                                                                                                                                                                                                     | PI master of<br>PI master of<br>PI master of<br>PI master of<br>PI slave mo<br>C slave mo<br>C slave mo<br>C slave mo<br>C slave mo<br>C slave mo | operation,<br>operation,<br>operation,<br>operation,<br>ode, clock<br>ode, clock<br>ode, 7-bit<br>ode, 10-bit<br>controlle<br>ode, 7-bit | clock = Fo<br>clock = Fo<br>clock = Fo<br>clock = TM<br>= SCK pin<br>address<br>address<br>d master op<br>address with | sc/4<br>sc/16<br>sc/64<br>/IR2 outpu<br>n. SS pin c<br>n. SS pin c<br>peration (s<br>th start an | t/2<br>ontrol ena<br>ontrol disa<br>slave idle)<br>d stop bit |                         |                                                                                      |  |  |  |  |

| 3.2.1 O  | PERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I OF SSP I                                                                                                                                        | MODULE                                                                                                                                   | IN SPI                                                                                                                 |                                                                                                  | A block                                                       | diagram of              | the SSP Module in SPI Mode is                                                        |  |  |  |  |

MODE - PIC16C72

shown in Figure 8-3.

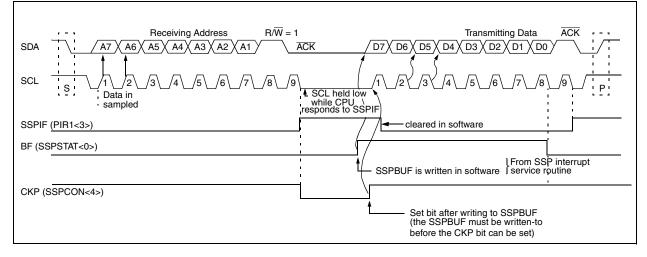

#### 8.4.1.3 TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSP-BUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 8-9). An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

# 10.2 Oscillator Configurations

#### 10.2.1 OSCILLATOR TYPES

The PIC16CXXX family can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

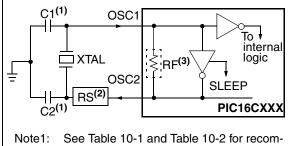

# 10.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

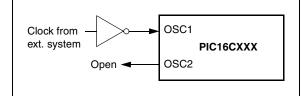

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 10-2). The PIC16CXXX family oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/ CLKIN pin (Figure 10-3).

#### FIGURE 10-2: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

- mended values of C1 and C2. 2: A series resistor (RS) may be required for

- AT strip cut crystals. 3: BE varies with the crystal chosen

- 3: RF varies with the crystal chosen.

#### FIGURE 10-3: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

# TABLE 10-1 CERAMIC RESONATORS

| Ranges Te | ested: |      |

|-----------|--------|------|

| Mode      | Freq   | OSC1 |

| Mode                                                                    | Freq                         | Freq OSC1   |             |  |  |  |

|-------------------------------------------------------------------------|------------------------------|-------------|-------------|--|--|--|

| XT                                                                      | 455 kHz                      | 68 - 100 pF | 68 - 100 pF |  |  |  |

|                                                                         | 2.0 MHz                      | 15 - 68 pF  | 15 - 68 pF  |  |  |  |

|                                                                         | 4.0 MHz                      | 15 - 68 pF  | 15 - 68 pF  |  |  |  |

| HS                                                                      | 8.0 MHz                      | 10 - 68 pF  | 10 - 68 pF  |  |  |  |

|                                                                         | 16.0 MHz                     | 10 - 22 pF  | 10 - 22 pF  |  |  |  |

| These values are for design guidance only. See notes at bottom of page. |                              |             |             |  |  |  |

| Resonator                                                               | rs Used:                     |             |             |  |  |  |

| 455 kHz                                                                 | Panasonic E                  | FO-A455K04B | ± 0.3%      |  |  |  |

| 2.0 MHz                                                                 | Murata Erie CSA2.00MG ± 0.5% |             |             |  |  |  |

| 4.0 MHz                                                                 | Murata Erie CSA4.00MG ± 0.5% |             |             |  |  |  |

| 8.0 MHz                                                                 | Murata Erie CSA8.00MT ± 0.5% |             |             |  |  |  |

| 16.0 MHz                                                                | Murata Erie                  | CSA16.00MX  | ± 0.5%      |  |  |  |

All resonators used did not have built-in capacitors.

# TABLE 10-2CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|-----------------|------------------|------------------|

| LP       | 32 kHz          | 33 pF            | 33 pF            |

|          | 200 kHz         | 15 pF            | 15 pF            |

| ХТ       | 200 kHz         | 47-68 pF         | 47-68 pF         |

|          | 1 MHz           | 15 pF            | 15 pF            |

|          | 4 MHz           | 15 pF            | 15 pF            |

| HS       | 4 MHz           | 15 pF            | 15 pF            |

|          | 8 MHz           | 15-33 pF         | 15-33 pF         |

|          | 20 MHz          | 15-33 pF         | 15-33 pF         |

|          | -               |                  |                  |

These values are for design guidance only. See notes at bottom of page.

| Crystals Used |                        |          |  |  |  |  |

|---------------|------------------------|----------|--|--|--|--|

| 32 kHz        | Epson C-001R32.768K-A  | ± 20 PPM |  |  |  |  |

| 200 kHz       | STD XTL 200.000KHz     | ± 20 PPM |  |  |  |  |

| 1 MHz         | ECS ECS-10-13-1        | ± 50 PPM |  |  |  |  |

| 4 MHz         | ECS ECS-40-20-1        | ± 50 PPM |  |  |  |  |

| 8 MHz         | EPSON CA-301 8.000M-C  | ± 30 PPM |  |  |  |  |

| 20 MHz        | EPSON CA-301 20.000M-C | ± 30 PPM |  |  |  |  |

Note 1: Recommended values of C1 and C2 are identical to the ranges tested (Table 10-1).

- 2: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification.

#### 10.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

#### 10.13.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. SSP (Start/Stop) bit detect interrupt.

- 3. SSP transmit or receive in slave mode (SPI/l<sup>2</sup>C).

- 4. CCP capture mode interrupt.

- 5. A/D conversion (when A/D clock source is RC).

- 6. Special event trigger (Timer1 in asynchronous mode using an external clock).

# 13.0 ELECTRICAL CHARACTERISTICS - PIC16C72 SERIES

#### Absolute Maximum Ratings †

| Parameter                                                                               | PIC16C72              | PIC16CR72             |

|-----------------------------------------------------------------------------------------|-----------------------|-----------------------|

| Ambient temperature under bias                                                          | -55 to +125°C         | -55 to +125°C         |

| Storage temperature                                                                     | -65°C to +150°C       | -65°C to +150°C       |

| Voltage on any pin with respect to VSS (except VDD, $\overline{\text{MCLR}}$ , and RA4) | -0.3V to (VDD + 0.3V) | -0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to VSS                                                      | -0.3 to +7.5V         | TBD                   |

| Voltage on MCLR with respect to Vss (Note 1)                                            | -0.3 to +14V          | TBD                   |

| Voltage on RA4 with respect to Vss                                                      | -0.3 to +14V          | TBD                   |

| Total power dissipation (Note 2)                                                        | 1.0W                  | 1.0W                  |

| Maximum current out of Vss pin                                                          | 300 mA                | 300 mA                |

| Maximum current into VDD pin                                                            | 250 mA                | 250 mA                |

| Input clamp current, Iık (Vı < 0 or Vı > VDD)                                           | ± 20 mA               | $\pm$ 20 mA           |

| Output clamp current, IOK (Vo < 0 or Vo > VDD)                                          | ± 20 mA               | ± 20 mA               |

| Maximum output current sunk by any I/O pin                                              | 25 mA                 | 25 mA                 |

| Maximum output current sourced by any I/O pin                                           | 25 mA                 | 25 mA                 |

| Maximum current sunk by PORTA and PORTB (combined)                                      | 200 mA                | 200 mA                |

| Maximum current sourced by PORTA and PORTB (combined)                                   | 200 mA                | 200 mA                |

| Maximum current sunk by PORTC                                                           | 200 mA                | 200 mA                |

| Maximum current sourced by PORTC                                                        | 200 mA                | 200 mA                |

Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

2. Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\Sigma$  IOH} +  $\Sigma$  {(VDD - VOH) x IOH} +  $\Sigma$ (VOI x IOL).

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# **PIC16C72 Series**

# TABLE 13-1 CROSS REFERENCE OF DEVICE SPECS (PIC16C72) FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| OSC | PIC16C72-04 PIC16C72-10                                                                                                                             |                                                                                                                                                    | PIC16C72-20                                                                                                                                        | PIC16LC72-04                                                                                              | JW Devices                                                                                                |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 µA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 µA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5.0 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                  |