Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                              |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c72-20e-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

| RP1* RF | 20 (ST/ | ATUS<6:5>) |

|---------|---------|------------|

|---------|---------|------------|

$= 00 \rightarrow Bank0$

- $= 01 \rightarrow \text{Bank1}$

- =  $10 \rightarrow$  Bank2 (not implemented)

- = 11  $\rightarrow$  Bank3 (not implemented)

\* Maintain this bit clear to ensure upward compatibility with future products.

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM.

All implemented banks contain special function registers. Some "high use" special function registers from one bank may be mirrored in another bank for code reduction and quicker access (ex; the STATUS register is in Bank 0 and Bank 1).

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly through the File Select Register FSR (Section 2.5).

# FIGURE 2-2: REGISTER FILE MAP

| File      |                      |                     | File        |

|-----------|----------------------|---------------------|-------------|

| Address   | 3                    |                     | Address     |

| 00h       | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup> | 80h         |

| 01h       | TMR0                 | OPTION              | 81h         |

| 02h       | PCL                  | PCL                 | 82h         |

| 03h       | STATUS               | STATUS              | 83h         |

| 04h       | FSR                  | FSR                 | 84h         |

| 05h       | PORTA                | TRISA               | 85h         |

| 06h       | PORTB                | TRISB               | 86h         |

| 07h       | PORTC                | TRISC               | 87h         |

| 08h       |                      |                     | 88h         |

| 09h       |                      |                     | 89h         |

| 0Ah       | PCLATH               | PCLATH              | 8Ah         |

| 0Bh       | INTCON               | INTCON              | 8Bh         |

| 0Ch       | PIR1                 | PIE1                | 8Ch         |

| 0Dh       |                      |                     | 8Dh         |

| 0Eh       | TMR1L                | PCON                | 8Eh         |

| 0Fh       | TMR1H                |                     | 8Fh         |

| 10h       | T1CON                |                     | 90h         |

| 11h       | TMR2                 |                     | 91h         |

| 12h       | T2CON                | PR2                 | 92h         |

| 13h       | SSPBUF               | SSPADD              | 93h         |

| 14h       | SSPCON               | SSPSTAT             | 94h         |

| 15h       | CCPR1L               |                     | 95h         |

| 16h       | CCPR1H               |                     | 96h         |

| 17h       | CCP1CON              |                     | 97h         |

| 18h       |                      |                     | 98h         |

| 19h       |                      |                     | 99h         |

| 1Ah       |                      |                     | 9Ah         |

| 1Bh       |                      |                     | 9Bh         |

| 1Ch       |                      |                     | 9Ch         |

| 1Dh       |                      |                     | 9Dh         |

| 1Eh       | ADRES                |                     | 9Eh         |

| 1Fh       | ADCON0               | ADCON1              | 9Fh         |

| 20h       | 0                    | 0                   | A0h         |

|           | General<br>Purpose   | General<br>Purpose  |             |

|           | Register             | Register            |             |

|           |                      |                     | BFh         |

|           |                      |                     | C0h         |

|           |                      |                     |             |

| 1         |                      |                     |             |

|           |                      |                     |             |

| 7Fh       |                      |                     | FFh         |

|           | Bank 0               | Bank 1              |             |

|           |                      |                     |             |

|           | plemented data me    |                     | ead as '0'. |

| Note 1: 1 | Not a physical regis | ster.               |             |

|           |                      |                     |             |

#### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Figure 2-3, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{TO}$  and  $\overline{PD}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- Note 1: These devices do not use bits IRP and RP1 (STATUS<7:6>). Maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| R/W-0    | R/W-0                                            | R/W-0                                                                                                                                                                                                                                                | R-1                                  | <u>R-1</u>                                | R/W-x         | R/W-x                                     | R/W-x                       |                                                                                       |  |  |

|----------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------|---------------|-------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------|--|--|

| IRP      | RP1                                              | RP0                                                                                                                                                                                                                                                  | TO                                   | PD                                        | Z             | DC                                        | С                           | R = Readable bit                                                                      |  |  |

| bit7     |                                                  |                                                                                                                                                                                                                                                      |                                      |                                           |               |                                           | bitO                        | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |

| bit 7:   | 1 = Bank 2                                       | ster Bank 3<br>2, 3 (100h<br>0, 1 (00h -                                                                                                                                                                                                             | - 1FFh)                              | (used for i                               | ndirect addı  | essing)                                   |                             |                                                                                       |  |  |

| bit 6-5: | 11 = Bank<br>10 = Bank<br>01 = Bank<br>00 = Bank | < 3 (180h -<br>< 2 (100h -<br>< 1 (80h - F<br>< 0 (00h - 7<br>< is 128 by                                                                                                                                                                            | 1FFh)<br>17Fh)<br>FFh)<br>′Fh)       | ·                                         | ed for direct |                                           |                             | <sup>9</sup> bit is reserved. Always maintai                                          |  |  |

| bit 4:   | 1 = After p                                      | TO: Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                                      |                                      |                                           |               |                                           |                             |                                                                                       |  |  |

| bit 3:   |                                                  | r-down bit<br>oower-up o<br>ecution of t                                                                                                                                                                                                             |                                      |                                           |               |                                           |                             |                                                                                       |  |  |

| bit 2:   |                                                  | sult of an                                                                                                                                                                                                                                           |                                      |                                           | peration is z |                                           |                             |                                                                                       |  |  |

| bit 1:   | 1 = A carr                                       | <b>DC</b> : Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow the polarity is reversed)<br>1 = A carry-out from the 4th low order bit of the result occurred<br>0 = No carry-out from the 4th low order bit of the result |                                      |                                           |               |                                           |                             |                                                                                       |  |  |

| bit 0:   | 1 = A carr<br>0 = No car<br>Note: For            | y-out from<br>rry-out from<br>borrow the<br>berand. Fo                                                                                                                                                                                               | the most<br>n the mos<br>polarity is | significant<br>t significar<br>s reversed |               | esult occur<br>result occu<br>ion is exec | red<br>irred<br>uted by ade | ding the two's complement of th<br>either the high or low order bit o                 |  |  |

# FIGURE 2-3: STATUS REGISTER (ADDRESS 03h, 83h)

# **PIC16C72 Series**

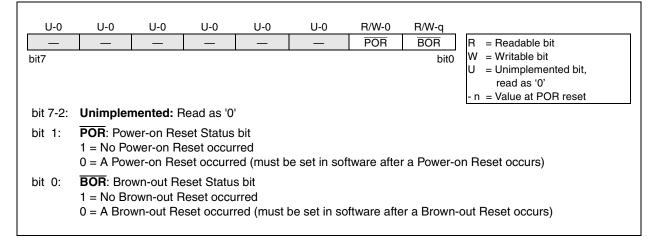

#### 2.2.2.6 PCON REGISTER

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external  $\overline{\text{MCLR}}$  Reset or WDT Reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition.

#### Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

## FIGURE 2-8: PCON REGISTER (ADDRESS 8Eh)

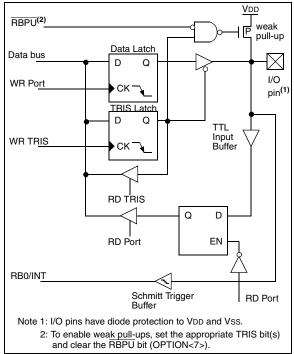

## 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output, i.e., put the contents of the output latch on the selected pin.

#### EXAMPLE 3-1: INITIALIZING PORTB

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| CLRF  | PORTB   |     | ; | Initialize PORTB by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISB   |     | ; | Set RB<3:0> as inputs |

|       |         |     | ; | RB<5:4> as outputs    |

|       |         |     | ; | RB<7:6> as inputs     |

|       |         |     |   |                       |

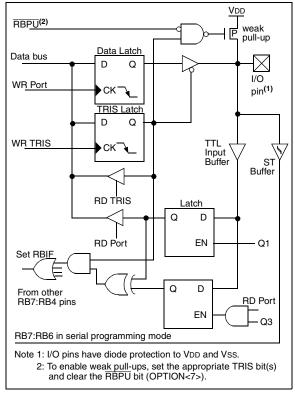

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\text{RBPU}}$  (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

### FIGURE 3-4: BLOCK DIAGRAM OF RB7:RB4 PINS

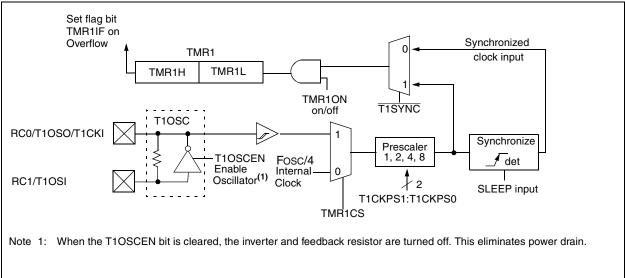

# 5.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (Both registers)

- Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- Reset from CCP module trigger

Timer1 has a control register, shown in Figure 5-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 5-2 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the  $PIC^{\textcircled{R}}$  Mid-Range MCU Reference Manual, DS33023.

# 5.1 <u>Timer1 Operation</u>

Timer1 can operate in one of these modes:

- As a timer

- As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored.

Timer1 also has an internal "reset input". This reset can be generated by the CCP module (Section 7.0).

# FIGURE 5-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

| U-0      | U-0                                                                                                                                                                                                             | R/W-0                                                            | R/W-0                | R/W-0        | R/W-0        | R/W-0        | R/W-0    |                                                                                       |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------|--------------|--------------|--------------|----------|---------------------------------------------------------------------------------------|--|--|

| _        | _                                                                                                                                                                                                               | T1CKPS1                                                          | T1CKPS0              | T1OSCEN      | T1SYNC       | TMR1CS       | TMR1ON   | R = Readable bit                                                                      |  |  |

| bit7     |                                                                                                                                                                                                                 |                                                                  |                      |              |              |              | bitO     | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |

| bit 7-6: | Unimple                                                                                                                                                                                                         | mented: F                                                        | Read as '0'          |              |              |              |          |                                                                                       |  |  |

| bit 5-4: | 11 = 1:8<br>10 = 1:4<br>01 = 1:2                                                                                                                                                                                | 1:T1CKPS<br>Prescale v<br>Prescale v<br>Prescale v<br>Prescale v | alue<br>alue<br>alue | Input Cloc   | k Prescale   | e Select bit | S        |                                                                                       |  |  |

| bit 3:   | <b>T1OSCEN</b> : Timer1 Oscillator Enable Control bit<br>1 = Oscillator is enabled<br>0 = Oscillator is shut off<br>Note: The oscillator inverter and feedback resistor are turned off to eliminate power drain |                                                                  |                      |              |              |              |          |                                                                                       |  |  |

| bit 2:   | T1SYNC:                                                                                                                                                                                                         | Timer1 E                                                         | xternal Clo          | ock Input S  | Synchroniza  | ation Contr  | ol bit   |                                                                                       |  |  |

|          | T1SYNC: Timer1 External Clock Input Synchronization Control bit <u>TMR1CS = 1</u> 1 = Do not synchronize external clock input         0 = Synchronize external clock input                                      |                                                                  |                      |              |              |              |          |                                                                                       |  |  |

|          | <u>TMR1CS</u><br>This bit is                                                                                                                                                                                    |                                                                  | Timer1 use           | es the inter | rnal clock v | vhen TMR     | 1CS = 0. |                                                                                       |  |  |

| bit 1:   | <b>TMR1CS</b> : Timer1 Clock Source Select bit<br>1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge)<br>0 = Internal clock (Fosc/4)                                                               |                                                                  |                      |              |              |              |          |                                                                                       |  |  |

| bit 0:   |                                                                                                                                                                                                                 | l: Timer1 C<br>les Timer1<br>s Timer1                            | Dn bit               |              |              |              |          |                                                                                       |  |  |

# FIGURE 5-2: TIMER1 BLOCK DIAGRAM

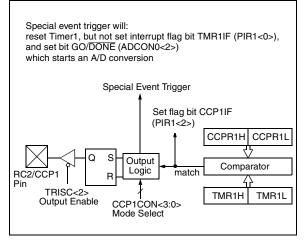

# 7.2 <u>Compare Mode</u>

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- driven High

- driven Low

- remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

# FIGURE 7-3: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 7.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force       |

|-------|------------------------------------------------|

|       | the RC2/CCP1 compare output latch to the       |

|       | default low level. This is not the data latch. |

#### 7.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 7.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 7.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special trigger output of CCP1 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

Note: The special event trigger from the CCP1 module will not set interrupt flag bit TMR1IF (PIR1<0>).

# TABLE 7-2 REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address | Name    | Bit 7                               | Bit 6                               | Bit 5        | Bit 4       | Bit 3         | Bit 2      | Bit 1       | Bit 0  | PC   | e on:<br>)R,<br>)R | all o | e on<br>other<br>sets |

|---------|---------|-------------------------------------|-------------------------------------|--------------|-------------|---------------|------------|-------------|--------|------|--------------------|-------|-----------------------|

| 0Bh,8Bh | INTCON  | GIE                                 | PEIE                                | TOIE         | INTE        | RBIE          | T0IF       | INTF        | RBIF   | 0000 | 000x               | 0000  | 000u                  |

| 0Ch     | PIR1    | (1)                                 | ADIF                                | (1)          | (1)         | SSPIF         | CCP1IF     | TMR2IF      | TMR1IF | 0000 | 0000               | 0000  | 0000                  |

| 8Ch     | PIE1    | (1)                                 | ADIE                                | (1)          | (1)         | SSPIE         | CCP1IE     | TMR2IE      | TMR1IE | 0000 | 0000               | 0000  | 0000                  |

| 87h     | TRISC   | PORTC Da                            | PORTC Data Direction Register       |              |             |               |            |             |        |      | 1111               | 1111  | 1111                  |

| 0Eh     | TMR1L   | Holding reg                         | gister fo                           | or the Least | Significant | Byte of the   | 16-bit TMF | R1 register |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 0Fh     | TMR1H   | Holding reg                         | gister fo                           | or the Most  | Significant | Byte of the 1 | 16-bit TMR | 1register   |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 10h     | T1CON   | —                                   |                                     | T1CKPS1      | T1CKPS0     | T1OSCEN       | T1SYNC     | TMR1CS      | TMR1ON | 00   | 0000               | uu    | uuuu                  |

| 15h     | CCPR1L  | Capture/Co                          | Capture/Compare/PWM register1 (LSB) |              |             |               |            |             |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 16h     | CCPR1H  | Capture/Compare/PWM register1 (MSB) |                                     |              |             |               |            |             | xxxx   | xxxx | uuuu               | uuuu  |                       |

| 17h     | CCP1CON | —                                   |                                     | CCP1X        | CCP1Y       | CCP1M3        | CCP1M2     | CCP1M1      | CCP1M0 | 00   | 0000               | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1. Note 1: These bits/registers are unimplemented, read as '0'. For an example PWM period and duty cycle calculation, see the PIC<sup>®</sup> Mid-Range MCU Reference Manual (DS33023).

#### 7.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

# TABLE 7-3 EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

# TABLE 7-4REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address | Name    | Bit 7                               | Bit 6                               | Bit 5       | Bit 4       | Bit 3       | Bit 2      | Bit 1       | Bit 0       | Value<br>PC<br>BC | PR,  | all o | ie on<br>other<br>sets |

|---------|---------|-------------------------------------|-------------------------------------|-------------|-------------|-------------|------------|-------------|-------------|-------------------|------|-------|------------------------|

| 0Bh,8Bh | INTCON  | GIE                                 | PEIE                                | T0IE        | INTE        | RBIE        | T0IF       | INTF        | RBIF        | 0000              | 000x | 0000  | 000u                   |

| 0Ch     | PIR1    | (1)                                 | ADIF                                | (1)         | (1)         | SSPIF       | CCP1IF     | TMR2IF      | TMR1IF      | 0000              | 0000 | 0000  | 0000                   |

| 8Ch     | PIE1    | (1)                                 | ADIE                                | (1)         | (1)         | SSPIE       | CCP1IE     | TMR2IE      | TMR1IE      | 0000              | 0000 | 0000  | 0000                   |

| 87h     | TRISC   | PORTC D                             | PORTC Data Direction Register       |             |             |             |            |             |             |                   |      | 1111  | 1111                   |

| 11h     | TMR2    | Timer2 mo                           | dule's regist                       | ter         |             |             |            |             |             | 0000              | 0000 | 0000  | 0000                   |

| 92h     | PR2     | Timer2 mo                           | dule's perio                        | d register  |             |             |            |             |             | 1111              | 1111 | 1111  | 1111                   |

| 12h     | T2CON   | —                                   | TOUTPS<br>3                         | TOUTPS<br>2 | TOUTPS<br>1 | TOUTPS<br>0 | TMR2O<br>N | T2CKPS<br>1 | T2CKPS<br>0 | -000              | 0000 | -000  | 0000                   |

| 15h     | CCPR1L  | Capture/Co                          | Capture/Compare/PWM register1 (LSB) |             |             |             |            |             |             |                   | xxxx | uuuu  | uuuu                   |

| 16h     | CCPR1H  | Capture/Compare/PWM register1 (MSB) |                                     |             |             |             |            |             |             | xxxx              | xxxx | uuuu  | uuuu                   |

| 17h     | CCP1CON | —                                   | _                                   | CCP1X       | CCP1Y       | CCP1M3      | CCP1M2     | CCP1M1      | CCP1M0      | 00                | 0000 | 00    | 0000                   |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: These bits/registers are unimplemented, read as '0'.

٦

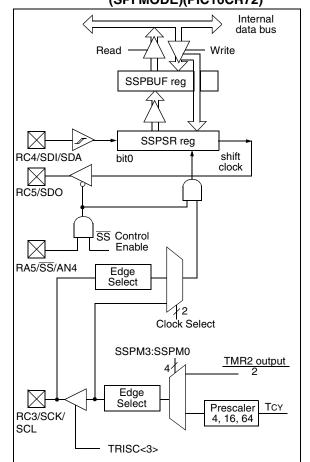

## 8.3 SPI Mode for PIC16CR72

Γ

This section contains register definitions and operational characteristics of the SPI module on the PIC16CR72 device only. Additional information on SPI operation may be found in the  $PIC^{\ensuremath{\mathbb{R}}}$  Mid-Range MCU Reference Manual, DS33023.

## FIGURE 8-4: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h) (PIC16CR72)

| R/W-0  | R/W-0                                                                                                                                                                                                                                                                                                                                                | R-0                                                                                                                                                                                                                                                                                              | R-0                          | R-0                                                  | R-0                                            | R-0          | R-0        |                                                                                      |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------|------------------------------------------------|--------------|------------|--------------------------------------------------------------------------------------|--|--|--|--|

| SMP    | CKE                                                                                                                                                                                                                                                                                                                                                  | D/Ā                                                                                                                                                                                                                                                                                              | Р                            | S                                                    | R/W                                            | UA           | BF         | R = Readable bit                                                                     |  |  |  |  |

| bit7   |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                  |                              |                                                      |                                                |              | bitO       | W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |  |  |  |  |

| bit 7: | <u>SPI Mas</u><br>1 = Inpu<br>0 = Inpu<br><u>SPI Slav</u>                                                                                                                                                                                                                                                                                            | <u>ster Ope</u><br>it data sa<br>it data sa<br>ve Mode                                                                                                                                                                                                                                           | ampled at<br>ampled at       | end of data<br>middle of d                           | output time<br>ata output tir<br>ed in slave n |              |            |                                                                                      |  |  |  |  |

| bit 6: | $\frac{CKP = 0}{1 = Data}$ $0 = Data$ $\frac{CKP = 1}{1 = Data}$                                                                                                                                                                                                                                                                                     | SMP must be cleared when SPI is used in slave mode<br>CKE: SPI Clock Edge Select<br>CKP = 0<br>1 = Data transmitted on rising edge of SCK<br>0 = Data transmitted on falling edge of SCK<br>CKP = 1<br>1 = Data transmitted on falling edge of SCK<br>0 = Data transmitted on rising edge of SCK |                              |                                                      |                                                |              |            |                                                                                      |  |  |  |  |

| bit 5: | 1 = India                                                                                                                                                                                                                                                                                                                                            | cates tha                                                                                                                                                                                                                                                                                        | at the last b                |                                                      | )<br>ed or transmi<br>ed or transmi            |              |            |                                                                                      |  |  |  |  |

| bit 4: | detected<br>1 = India                                                                                                                                                                                                                                                                                                                                | d last, St<br>cates tha                                                                                                                                                                                                                                                                          | SPEN is cl                   | eared)<br>t has been                                 | cleared whe                                    |              |            | disabled, or when the Start bit is                                                   |  |  |  |  |

| bit 3: | detected<br>1 = India                                                                                                                                                                                                                                                                                                                                | d last, SS<br>cates tha                                                                                                                                                                                                                                                                          | SPEN is cle<br>at a start bi | eared)<br>It has been                                | cleared whe                                    |              |            | disabled, or when the Stop bit is<br>ET)                                             |  |  |  |  |

| bit 2: | <ul> <li>0 = Start bit was not detected last</li> <li><b>R/W</b>: Read/Write bit information (I<sup>2</sup>C mode only)</li> <li>This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next start bit, stop bit, or ACK bit.</li> <li>1 = Read</li> <li>0 = Write</li> </ul> |                                                                                                                                                                                                                                                                                                  |                              |                                                      |                                                |              |            |                                                                                      |  |  |  |  |

| bit 1: | 1 = India                                                                                                                                                                                                                                                                                                                                            | cates tha                                                                                                                                                                                                                                                                                        | at the user                  | it I <sup>2</sup> C mode<br>needs to u<br>to be upda | pdate the ad                                   | dress in the | e SSPADD r | register                                                                             |  |  |  |  |

| bit 0: | BF: Buf                                                                                                                                                                                                                                                                                                                                              | fer Full S                                                                                                                                                                                                                                                                                       | Status bit                   |                                                      |                                                |              |            |                                                                                      |  |  |  |  |

|        | <u>Receive</u> (SPI and I <sup>2</sup> C modes)<br>1 = Receive complete, SSPBUF is full<br>0 = Receive not complete, SSPBUF is empty                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                  |                              |                                                      |                                                |              |            |                                                                                      |  |  |  |  |

|        | 1 = Tran                                                                                                                                                                                                                                                                                                                                             | ismit in p                                                                                                                                                                                                                                                                                       |                              | SPBUF is t<br>PBUF is en                             |                                                |              |            |                                                                                      |  |  |  |  |

|        |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                  |                              |                                                      |                                                |              |            |                                                                                      |  |  |  |  |

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally a fourth pin may be used when in a slave mode of operation:

Slave Select (SS) RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master Operation (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock Edge (Output data on rising/falling edge of SCK)

- Clock Rate (master operation only)

- Slave Select Mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON register, and then set bit SSPEN. This configures the SDI, SDO, SCK, and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (master operation) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set

| Note: | When the SPI is in Slave Mode with $\overline{SS}$ pin      |

|-------|-------------------------------------------------------------|

|       | control enabled, (SSPCON<3:0> = 0100)                       |

|       | the SPI module will reset if the $\overline{SS}$ pin is set |

|       | to VDD.                                                     |

**Note:** If the SPI is used in Slave Mode with CKE = '1', then the  $\overline{SS}$  pin control must be enabled.

#### FIGURE 8-6: SSP BLOCK DIAGRAM (SPI MODE)(PIC16CR72)

| TABLE 8-2 | REGISTERS ASSOCIATED WITH SPI OPERATION (PIC16CR72) |

|-----------|-----------------------------------------------------|

|           |                                                     |

| Address | Name    | Bit 7      | Bit 6       | Bit 5      | Bit 4     | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|---------|------------|-------------|------------|-----------|------------|----------|--------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh | INTCON  | GIE        | PEIE        | TOIE       | INTE      | RBIE       | T0IF     | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch     | PIR1    | (1)        | ADIF        | (1)        | (1)       | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1    | (1)        | ADIE        | (1)        | (1)       | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 87h     | TRISC   | PORTC Dat  | a Direction | n Register |           |            |          |        |        | 1111 1111                | 1111 1111                       |

| 13h     | SSPBUF  | Synchronou | s Serial P  | ort Receiv | e Buffer/ | Transmit F | Register |        |        | xxxx xxxx                | uuuu uuuu                       |

| 14h     | SSPCON  | WCOL       | SSPOV       | SSPEN      | CKP       | SSPM3      | SSPM2    | SSPM1  | SSPM0  | 0000 0000                | 0000 0000                       |

| 85h     | TRISA   | —          | _           | PORTA [    | Data Dire | 11 1111    | 11 1111  |        |        |                          |                                 |

| 94h     | SSPSTAT | SMP        | CKE         | D/A        | Р         | S          | R/W      | UA     | BF     | 0000 0000                | 0000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode. Note 1: Always maintain these bits clear.

# FIGURE 10-10: SLOW RISE TIME (MCLR TIED TO VDD)

|                | 5V    |

|----------------|-------|

| VDD            | 0V1V  |

| MCLR           |       |

| INTERNAL POR   | TPWRT |

| PWRT TIME-OUT  |       |

| OST TIME-OUT   |       |

| INTERNAL RESET |       |

#### 13.1 DC Characteristics: PIC16C72/CR72-04 (Commercial, Industrial, Extended) PIC16C72/CR72-10 (Commercial, Industrial, Extended) PIC16C72/CR72-20 (Commercial, Industrial, Extended)

|                    | Standard Operating Conditions (unless otherwise stated)           |       |            |         |                                      |                                                   |                       |                   |        |                                                              |  |

|--------------------|-------------------------------------------------------------------|-------|------------|---------|--------------------------------------|---------------------------------------------------|-----------------------|-------------------|--------|--------------------------------------------------------------|--|

| DC CHARACTERISTICS |                                                                   | 1 0 1 |            |         | $\leq TA \leq H$<br>$\leq TA \leq H$ | +125°C for<br>+85°C for<br>⊦85°C for<br>⊦70°C for | or extend<br>industri |                   |        |                                                              |  |

| Param              | Characteristic                                                    | Sym   | F          | PIC16C7 | 2                                    | Р                                                 | IC16CR7               | 72                | Units  | Conditions                                                   |  |

| No.                | onaraoteristio                                                    | ° y m | Min        | Тур†    | Max                                  | Min                                               | Typ†                  | Мах               | Units  | Conditions                                                   |  |

| D001<br>D001A      | Supply Voltage                                                    | Vdd   | 4.0<br>4.5 | -       | <b>6.0</b><br>5.5                    | 4.0<br>4.5                                        | -                     | <b>5.5</b><br>5.5 | V<br>V | XT, RC and LP osc<br>HS osc                                  |  |

| D002*              | RAM Data Retention<br>Voltage (Note 1)                            | VDR   | -          | 1.5     | -                                    | -                                                 | 1.5                   | -                 | V      |                                                              |  |

| D003               | VDD start voltage to<br>ensure internal Power-<br>on Reset Signal | VPOR  | -          | Vss     | -                                    | -                                                 | Vss                   | -                 | V      | See section on Power-<br>on Reset for details                |  |

| D004*              | VDD rise rate to ensure<br>internal Power-on<br>Reset Signal      | SVDD  | 0.05       | -       | -                                    | 0.05                                              | -                     | -                 | V/ms   | See section on Power-<br>on Reset for details                |  |

| D005               | Brown-out Reset Volt-<br>age                                      | Bvdd  | 3.7        | 4.0     | 4.3                                  | 3.7                                               | 4.0                   | 4.3               | V      | BODEN bit in configura-<br>tion word enabled                 |  |

|                    |                                                                   |       | 3.7        | 4.0     | 4.4                                  | 3.7                                               | 4.0                   | 4.4               | V      | Extended Only                                                |  |

| D010               | Supply Current<br>(Note 2,5)                                      | IDD   | -          | 2.7     | 5.0                                  | -                                                 | 2.7                   | 5.0               | mA     | XT, RC osc<br>Fosc = 4 MHz,<br>VDD = 5.5V (Note 4)           |  |

| D013               |                                                                   |       | -          | 10      | 20                                   | -                                                 | 10                    | 20                | mA     | HS osc<br>Fosc = 20 MHz,<br>VDD = 5.5V                       |  |

| D015               | Brown-out Reset<br>Current (Note 6)                               | ∆lbor | -          | 350     | 425                                  | -                                                 | 350                   | 425               | μA     | BOR enabled,<br>VDD = 5.0V                                   |  |

| D020               | Power-down Current<br>(Note 3,5)                                  | IPD   | -          | 10.5    | 42                                   | -                                                 | 10.5                  | 42                | μA     | VDD = 4.0V, WDT<br>enabled, -40°C to +85°C                   |  |

| D021               |                                                                   |       | -          | 1.5     | 16                                   | -                                                 | 1.5                   | 16                | μA     | $VDD = 4.0V$ , WDT disabled, $-0^{\circ}C$ to $+70^{\circ}C$ |  |

| D021A              |                                                                   |       | -          | 1.5     | 19                                   | -                                                 | 1.5                   | 19                | μA     | VDD = 4.0V, WDT dis-<br>abled, -40°C to +85°C                |  |

| D021B              |                                                                   |       | -          | 2.5     | 19                                   | -                                                 | 2.5                   | 19                | μA     | VDD = 4.0V, WDT dis-<br>abled, -40°C to +125°C               |  |

| D023               | Brown-out Reset<br>Current (Note 6)                               | ∆lbor | -          | 350     | 425                                  | -                                                 | 350                   | 425               | μA     | BOR enabled VDD = 5.0V                                       |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

Note 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

**Note 3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

**Note 4:** For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

**Note 5:** Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

**Note 6:** The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

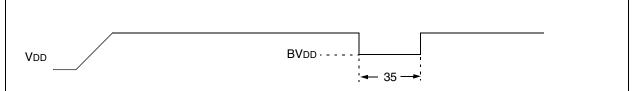

#### FIGURE 13-5: BROWN-OUT RESET TIMING

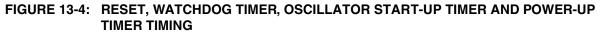

# TABLE 13-5RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                            |     | Тур†     | Max | Units | Conditions                |

|------------------|-------|-----------------------------------------------------------|-----|----------|-----|-------|---------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                    | 2   | —        | —   | μs    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)          | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period                         | _   | 1024Tosc | _   | —     | Tosc = OSC1 period        |

| 33*              | Tpwrt | Power-up Timer Period                                     | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34               | Tioz  | I/O Hi-impedance from MCLR Low<br>or Watchdog Timer Reset | —   | _        | 2.1 | μs    |                           |

| 35               | TBOR  | Brown-out Reset pulse width                               | 100 | _        |     | μS    | $VDD \le BVDD$ (D005)     |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Param<br>No. | Sym                   | Characteristic                             | Min      | Тур† | Max | Units | Conditions |

|--------------|-----------------------|--------------------------------------------|----------|------|-----|-------|------------|

| 70           | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                  | Тсү      | -    | —   | ns    |            |

| 71           | TscH                  | SCK input high time (slave mode)           | Tcy + 20 | _    | —   | ns    |            |

| 72           | TscL                  | SCK input low time (slave mode)            | TCY + 20 | _    | _   | ns    |            |

| 73           | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge   | 50       | -    | —   | ns    |            |

| 74           | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge    | 50       | -    | -   | ns    |            |

| 75           | TdoR                  | SDO data output rise time                  | _        | 10   | 25  | ns    |            |

| 76           | TdoF                  | SDO data output fall time                  | —        | 10   | 25  | ns    |            |

| 77           | TssH2doZ              | SS <sup>↑</sup> to SDO output hi-impedance | 10       | -    | 50  | ns    |            |

| 78           | TscR                  | SCK output rise time (master mode)         | _        | 10   | 25  | ns    |            |

| 79           | TscF                  | SCK output fall time (master mode)         | —        | 10   | 25  | ns    |            |

| 80           | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge       | —        | _    | 50  | ns    |            |

TABLE 13-8

SPI SLAVE MODE REQUIREMENTS (CKE=0) - PIC16C72

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Parameter<br>No. | lo.                   |                                                            | Min         | Тур† | Max | Units | Conditions |

|------------------|-----------------------|------------------------------------------------------------|-------------|------|-----|-------|------------|

| 70*              |                       |                                                            | Тсү         | —    | —   | ns    |            |

| 71*              | TscH                  | SCK input high time (slave mode)                           | TCY + 20    | _    | _   | ns    |            |

| 72*              | TscL                  | SCK input low time (slave mode)                            | TCY + 20    | _    | _   | ns    |            |

| 73*              | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge                   | 100         | _    | —   | ns    |            |

| 74*              | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                    | 100         | —    | —   | ns    |            |

| 75*              | TdoR                  | SDO data output rise time                                  | —           | 10   | 25  | ns    |            |

| 76*              | TdoF                  | SDO data output fall time                                  | —           | 10   | 25  | ns    |            |

| 77*              | TssH2doZ              | SS↑ to SDO output hi-impedance                             | 10          | _    | 50  | ns    |            |

| 78*              | TscR                  | SCK output rise time (master mode)                         | —           | 10   | 25  | ns    |            |

| 79*              | TscF                  | SCK output fall time (master mode)                         | _           | 10   | 25  | ns    |            |

| 80*              | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                       | —           | —    | 50  | ns    |            |

| 81*              | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK edge                          | Тсү         | —    | —   | ns    |            |

| 82*              | TssL2doV              | SDO data output valid after $\overline{SS}\downarrow$ edge | —           | _    | 50  | ns    |            |

| 83*              | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                        | 1.5Tcy + 40 | _    | —   | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

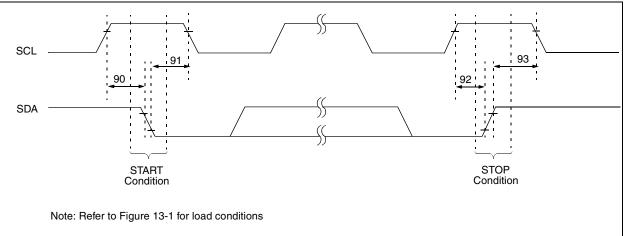

# FIGURE 13-12: I<sup>2</sup>C BUS START/STOP BITS TIMING

| Parameter<br>No. | Sym     | Characteristic  |              |      | Тур | Max | Units | Conditions                        |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|

| 90               | TSU:STA | START condition | 100 kHz mode | 4700 |     | —   | ns    | Only relevant for repeated START  |

|                  |         | Setup time      | 400 kHz mode | 600  | _   | _   |       | condition                         |

| 91               | THD:STA | START condition | 100 kHz mode | 4000 | _   | _   | ns    | After this period the first clock |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   |       | pulse is generated                |

| 92               | TSU:STO | STOP condition  | 100 kHz mode | 4700 | _   | _   | ns    |                                   |

|                  |         | Setup time      | 400 kHz mode | 600  | _   | _   |       |                                   |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | —   | —   | ns    |                                   |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   |       |                                   |

NOTES:

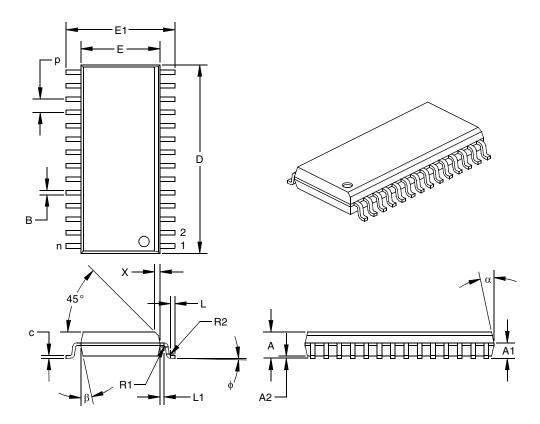

# 16.4 <u>28-Lead Plastic Surface Mount (SOIC - Wide, 300 mil Body) (SO)</u>

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                   |                |       | INCHES* |       | М     | MILLIMETERS |       |  |  |

|-------------------------|----------------|-------|---------|-------|-------|-------------|-------|--|--|

| Dimension Limits        |                | MIN   | NOM     | MAX   | MIN   | NOM         | MAX   |  |  |

| Pitch                   | р              |       | 0.050   |       |       | 1.27        |       |  |  |

| Number of Pins          | n              |       | 28      |       |       | 28          |       |  |  |

| Overall Pack. Height    | А              | 0.093 | 0.099   | 0.104 | 2.36  | 2.50        | 2.64  |  |  |

| Shoulder Height         | A1             | 0.048 | 0.058   | 0.068 | 1.22  | 1.47        | 1.73  |  |  |

| Standoff                | A2             | 0.004 | 0.008   | 0.011 | 0.10  | 0.19        | 0.28  |  |  |

| Molded Package Length   | D <sup>‡</sup> | 0.700 | 0.706   | 0.712 | 17.78 | 17.93       | 18.08 |  |  |

| Molded Package Width    | E‡             | 0.292 | 0.296   | 0.299 | 7.42  | 7.51        | 7.59  |  |  |

| Outside Dimension       | E1             | 0.394 | 0.407   | 0.419 | 10.01 | 10.33       | 10.64 |  |  |

| Chamfer Distance        | х              | 0.010 | 0.020   | 0.029 | 0.25  | 0.50        | 0.74  |  |  |

| Shoulder Radius         | R1             | 0.005 | 0.005   | 0.010 | 0.13  | 0.13        | 0.25  |  |  |

| Gull Wing Radius        | R2             | 0.005 | 0.005   | 0.010 | 0.13  | 0.13        | 0.25  |  |  |

| Foot Length             | L              | 0.011 | 0.016   | 0.021 | 0.28  | 0.41        | 0.53  |  |  |

| Foot Angle              | φ              | 0     | 4       | 8     | 0     | 4           | 8     |  |  |

| Radius Centerline       | L1             | 0.010 | 0.015   | 0.020 | 0.25  | 0.38        | 0.51  |  |  |

| Lead Thickness          | с              | 0.009 | 0.011   | 0.012 | 0.23  | 0.27        | 0.30  |  |  |

| Lower Lead Width        | Bţ             | 0.014 | 0.017   | 0.019 | 0.36  | 0.42        | 0.48  |  |  |

| Mold Draft Angle Top    | α              | 0     | 12      | 15    | 0     | 12          | 15    |  |  |

| Mold Draft Angle Bottom | β              | 0     | 12      | 15    | 0     | 12          | 15    |  |  |

<sup>\*</sup> Controlling Parameter.

<sup>†</sup> Dimension "B" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B."

<sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."

NOTES:

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support