Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                    |

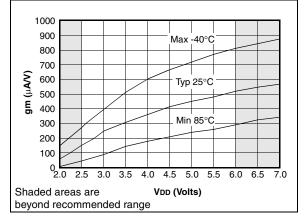

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c72t-20i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

# The special function registers can be classified into two TABLE 2-1 SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                                                  | Bit 6          | Bit 5         | Bit 4          | Bit 3         | Bit 2       | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(3) |

|----------------------|---------|--------------------------------------------------------|----------------|---------------|----------------|---------------|-------------|---------------|-----------|--------------------------|-------------------------------------|

| Bank 0               |         |                                                        |                |               |                |               |             |               |           |                          |                                     |

| 00h <sup>(1)</sup>   | INDF    | Addressing                                             | this location  | uses conten   | ts of FSR to   | address data  | a memory (n | ot a physical | register) | 0000 0000                | 0000 0000                           |

| 01h                  | TMR0    | Timer0 mod                                             | ule's registe  | r             |                |               |             |               |           | xxxx xxxx                | uuuu uuuu                           |

| 02h <sup>(1)</sup>   | PCL     | Program Co                                             | ounter's (PC)  | Least Signif  | icant Byte     |               |             |               |           | 0000 0000                | 0000 0000                           |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(4)</sup> RP1 <sup>(4)</sup> RP0 TO PD Z DC C |                |               |                |               |             |               |           | 0001 1xxx                | 000q quuu                           |

| 04h <sup>(1)</sup>   | FSR     | Indirect data                                          | a memory ad    | ldress pointe | r              |               |             |               |           | xxxx xxxx                | uuuu uuuu                           |

| 05h                  | PORTA   | _                                                      | -              | PORTA Dat     | a Latch whe    | n written: PO | RTA pins wh | ien read      |           | 0x 0000                  | 0u 0000                             |

| 06h                  | PORTB   | PORTB Dat                                              | a Latch whe    | n written: PC | ORTB pins wl   | nen read      |             |               |           | XXXX XXXX                | uuuu uuuu                           |

| 07h                  | PORTC   | PORTC Dat                                              | a Latch whe    | n written: PC | ORTC pins w    | hen read      |             |               |           | xxxx xxxx                | uuuu uuuu                           |

| 08h                  | —       | Unimplemen                                             | nted           |               |                |               |             |               |           | —                        | —                                   |

| 09h                  | _       | Unimplemented                                          |                |               |                |               |             |               | —         | —                        |                                     |

| 0Ah <sup>(1,2)</sup> | PCLATH  |                                                        |                |               |                |               |             |               | 0 0000    | 0 0000                   |                                     |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                                                    | PEIE           | TOIE          | INTE           | RBIE          | TOIF        | INTF          | RBIF      | 0000 000x                | 0000 000u                           |

| 0Ch                  | PIR1    | —                                                      | ADIF           | —             | —              | SSPIF         | CCP1IF      | TMR2IF        | TMR1IF    | -0 0000                  | -0 0000                             |

| 0Dh                  | —       | Unimplemen                                             | nted           |               |                |               |             |               |           | —                        | —                                   |

| 0Eh                  | TMR1L   | Holding regi                                           | ster for the L | east Signific | ant Byte of t  | he 16-bit TM  | R1 register |               |           | xxxx xxxx                | uuuu uuuu                           |

| 0Fh                  | TMR1H   | Holding regi                                           | ster for the M | Most Signific | ant Byte of th | ne 16-bit TMF | R1 register |               |           | xxxx xxxx                | uuuu uuuu                           |

| 10h                  | T1CON   | —                                                      | -              | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC      | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                             |

| 11h                  | TMR2    | Timer2 mod                                             | ule's registe  | r             |                |               |             |               |           | 0000 0000                | 0000 0000                           |

| 12h                  | T2CON   | —                                                      | TOUTPS3        | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON      | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                           |

| 13h                  | SSPBUF  | Synchronou                                             | s Serial Port  | Receive Bu    | ffer/Transmit  | Register      |             |               |           | XXXX XXXX                | uuuu uuuu                           |

| 14h                  | SSPCON  | WCOL                                                   | SSPOV          | SSPEN         | СКР            | SSPM3         | SSPM2       | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                           |

| 15h                  | CCPR1L  | Capture/Cor                                            | mpare/PWM      | Register (LS  | SB)            |               |             |               |           | XXXX XXXX                | uuuu uuuu                           |

| 16h                  | CCPR1H  | Capture/Cor                                            | mpare/PWM      | Register (M   | SB)            |               |             |               |           | XXXX XXXX                | uuuu uuuu                           |

| 17h                  | CCP1CON | —                                                      | —              | CCP1X         | CCP1Y          | CCP1M3        | CCP1M2      | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                             |

| 18h-1Dh              |         | Unimplemer                                             | nted           |               |                |               |             |               |           | _                        |                                     |

| 1Eh                  | ADRES   | A/D Result Register                                    |                |               |                |               |             |               |           | xxxx xxxx                | uuuu uuuu                           |

| 1Fh                  | ADCON0  | ADCS1                                                  | ADCS0          | CHS2          | CHS1           | CHS0          | GO/DONE     | _             | ADON      | 0000 00-0                | 0000 00-0                           |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved on the PIC16C72/CR72. Always maintain these bits clear.

5: SSPSTAT<7:6> are not implemented on the PIC16C72, read as '0'.

#### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Figure 2-3, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{TO}$  and  $\overline{PD}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- Note 1: These devices do not use bits IRP and RP1 (STATUS<7:6>). Maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| R/W-0    | R/W-0                                            | R/W-0                                                                     | R-1                                  | <u>R-1</u>                                | R/W-x                                          | R/W-x                                     | R/W-x                       |                                                                                       |

|----------|--------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------|-------------------------------------------|------------------------------------------------|-------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------|

| IRP      | RP1                                              | RP0                                                                       | TO                                   | PD                                        | Z                                              | DC                                        | С                           | R = Readable bit                                                                      |

| bit7     |                                                  |                                                                           |                                      |                                           |                                                |                                           | bitO                        | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:   | 1 = Bank 2                                       | ster Bank 3<br>2, 3 (100h<br>0, 1 (00h -                                  | - 1FFh)                              | (used for i                               | ndirect addı                                   | essing)                                   |                             |                                                                                       |

| bit 6-5: | 11 = Bank<br>10 = Bank<br>01 = Bank<br>00 = Bank | < 3 (180h -<br>< 2 (100h -<br>< 1 (80h - F<br>< 0 (00h - 7<br>< is 128 by | 1FFh)<br>17Fh)<br>FFh)<br>′Fh)       | ·                                         | ed for direct                                  |                                           |                             | <sup>9</sup> bit is reserved. Always maintai                                          |

| bit 4:   |                                                  |                                                                           |                                      | struction,                                | or sleep ir                                    | struction                                 |                             |                                                                                       |

| bit 3:   |                                                  | r-down bit<br>oower-up o<br>ecution of t                                  |                                      |                                           |                                                |                                           |                             |                                                                                       |

| bit 2:   |                                                  | sult of an                                                                |                                      |                                           | peration is z                                  |                                           |                             |                                                                                       |

| bit 1:   | 1 = A carr                                       | y-out from                                                                | the 4th lo                           | w order bi                                | w, SUBLW, S<br>t of the resu<br>bit of the res | It occurred                               |                             | or borrow the polarity is reversed                                                    |

| bit 0:   | 1 = A carr<br>0 = No car<br>Note: For            | y-out from<br>rry-out from<br>borrow the<br>berand. Fo                    | the most<br>n the mos<br>polarity is | significant<br>t significar<br>s reversed |                                                | esult occur<br>result occu<br>ion is exec | red<br>irred<br>uted by ade | ding the two's complement of th<br>either the high or low order bit o                 |

# FIGURE 2-3: STATUS REGISTER (ADDRESS 03h, 83h)

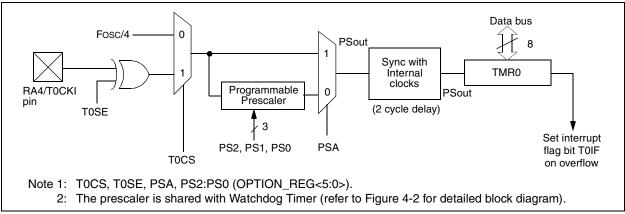

# 4.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- Internal or external clock select

- Edge select for external clock

- 8-bit software programmable prescaler

- Interrupt on overflow from FFh to 00h

Figure 4-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range MCU Reference Manual, DS33023.

#### 4.1 <u>Timer0 Operation</u>

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the PIC<sup>®</sup> Mid-Range MCU Reference Manual, DS33023.

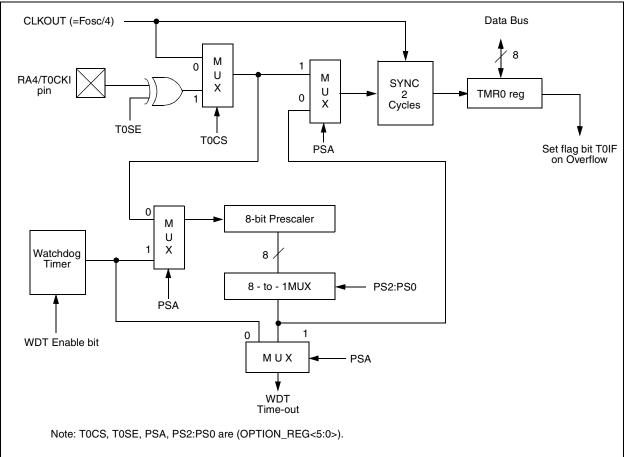

#### 4.2 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 4-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

#### FIGURE 4-1: TIMER0 BLOCK DIAGRAM

#### 4.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

**Note:** To avoid an unintended device RESET, a specific instruction sequence (shown in the PIC<sup>®</sup> Mid-Range MCU Reference Manual, DS3023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

### 4.3 <u>Timer0 Interrupt</u>

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP.

#### FIGURE 4-2: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

## TABLE 4-1 REGISTERS ASSOCIATED WITH TIMER0

| Address               | Name       | Bit 7  | Bit 6                    | Bit 5                         | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0   | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------------------|------------|--------|--------------------------|-------------------------------|-------|-------|-------|-------|---------|--------------------------|---------------------------|

| 01h,101h              | TMR0       | Timer0 | Timer0 module's register |                               |       |       |       |       |         | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE                     | TOIE                          | INTE  | RBIE  | T0IF  | INTF  | RBIF    | 0000 000x                | 0000 000u                 |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG                   | TOCS                          | T0SE  | PSA   | PS2   | PS1   | PS0     | 1111 1111                | 1111 1111                 |

| 85h                   | TRISA      | _      | _                        | PORTA Data Direction Register |       |       |       |       | 11 1111 | 11 1111                  |                           |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

For an example PWM period and duty cycle calculation, see the PIC<sup>®</sup> Mid-Range MCU Reference Manual (DS33023).

#### 7.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

# TABLE 7-3 EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

## TABLE 7-4REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address | Name    | Bit 7                               | Bit 6                               | Bit 5       | Bit 4       | Bit 3       | Bit 2      | Bit 1       | Bit 0       | Value<br>PC<br>BC | PR,  | all o | ie on<br>other<br>sets |

|---------|---------|-------------------------------------|-------------------------------------|-------------|-------------|-------------|------------|-------------|-------------|-------------------|------|-------|------------------------|

| 0Bh,8Bh | INTCON  | GIE                                 | PEIE                                | T0IE        | INTE        | RBIE        | T0IF       | INTF        | RBIF        | 0000              | 000x | 0000  | 000u                   |

| 0Ch     | PIR1    | (1)                                 | ADIF                                | (1)         | (1)         | SSPIF       | CCP1IF     | TMR2IF      | TMR1IF      | 0000              | 0000 | 0000  | 0000                   |

| 8Ch     | PIE1    | (1)                                 | ADIE                                | (1)         | (1)         | SSPIE       | CCP1IE     | TMR2IE      | TMR1IE      | 0000              | 0000 | 0000  | 0000                   |

| 87h     | TRISC   | PORTC D                             | PORTC Data Direction Register       |             |             |             |            |             |             |                   | 1111 | 1111  | 1111                   |

| 11h     | TMR2    | Timer2 mo                           | Timer2 module's register            |             |             |             |            |             |             | 0000              | 0000 | 0000  | 0000                   |

| 92h     | PR2     | Timer2 mo                           | dule's perio                        | d register  |             |             |            |             |             | 1111              | 1111 | 1111  | 1111                   |

| 12h     | T2CON   | —                                   | TOUTPS<br>3                         | TOUTPS<br>2 | TOUTPS<br>1 | TOUTPS<br>0 | TMR2O<br>N | T2CKPS<br>1 | T2CKPS<br>0 | -000              | 0000 | -000  | 0000                   |

| 15h     | CCPR1L  | Capture/Co                          | Capture/Compare/PWM register1 (LSB) |             |             |             |            |             |             |                   | xxxx | uuuu  | uuuu                   |

| 16h     | CCPR1H  | Capture/Compare/PWM register1 (MSB) |                                     |             |             |             |            |             |             | xxxx              | xxxx | uuuu  | uuuu                   |

| 17h     | CCP1CON | —                                   | _                                   | CCP1X       | CCP1Y       | CCP1M3      | CCP1M2     | CCP1M1      | CCP1M0      | 00                | 0000 | 00    | 0000                   |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: These bits/registers are unimplemented, read as '0'.

NOTES:

# 8.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

# 8.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SSP module in  $I^2C$  mode works the same in all PIC16C72 series devices that have an SSP module. However the SSP Module in SPI mode has differences between the PIC16C72 and the PIC16CR72 device.

The register definitions and operational description of SPI mode has been split into two sections because of the differences between the PIC16C72 and the PIC16CR72 device. The default reset values of both the SPI modules is the same regardless of the device:

- 8.2 SPI Mode for PIC16C72 ...... 40

- 8.3 SPI Mode for PIC16CR72 ...... 43

For an I<sup>2</sup>C Overview, refer to the PIC<sup>®</sup> Mid-Range MCU Reference Manual (DS33023). Also, refer to Application Note AN578, *"Use of the SSP Module in the I<sup>2</sup>C Multi-Master Environment."*

٦

#### 8.3 SPI Mode for PIC16CR72

Γ

This section contains register definitions and operational characteristics of the SPI module on the PIC16CR72 device only. Additional information on SPI operation may be found in the  $PIC^{\ensuremath{\mathbb{R}}}$  Mid-Range MCU Reference Manual, DS33023.

### FIGURE 8-4: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h) (PIC16CR72)

| R/W-0  | R/W-0                                                                                                                                                                                                                                                                  | R-0                                                      | R-0                          | R-0                                                             | R-0                                 | R-0          | R-0         |                                                                                      |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------|-----------------------------------------------------------------|-------------------------------------|--------------|-------------|--------------------------------------------------------------------------------------|--|--|--|

| SMP    | CKE                                                                                                                                                                                                                                                                    | D/Ā                                                      | Р                            | S                                                               | R/W                                 | UA           | BF          | R = Readable bit                                                                     |  |  |  |

| bit7   |                                                                                                                                                                                                                                                                        |                                                          |                              |                                                                 |                                     |              | bitO        | W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |  |  |  |

| bit 7: | SMP: SPI data input sample phase         SPI Master Operation         1 = Input data sampled at end of data output time         0 = Input data sampled at middle of data output time         SPI Slave Mode         SMP must be cleared when SPI is used in slave mode |                                                          |                              |                                                                 |                                     |              |             |                                                                                      |  |  |  |

| bit 6: | $\frac{CKP = 0}{1 = Data}$ $0 = Data$ $\frac{CKP = 1}{1 = Data}$                                                                                                                                                                                                       | <u>)</u><br>a transm<br>a transm<br><u>l</u><br>a transm | itted on fal<br>itted on fal | ect<br>ing edge of<br>ling edge o<br>ling edge o<br>ing edge of | f SCK<br>f SCK                      |              |             |                                                                                      |  |  |  |

| bit 5: | 1 = India                                                                                                                                                                                                                                                              | cates tha                                                | at the last b                |                                                                 | )<br>ed or transmi<br>ed or transmi |              |             |                                                                                      |  |  |  |

| bit 4: | detected<br>1 = India                                                                                                                                                                                                                                                  | d last, St<br>cates tha                                  | SPEN is cl                   | eared)<br>t has been                                            | cleared whe                         |              |             | disabled, or when the Start bit is                                                   |  |  |  |

| bit 3: | detected<br>1 = India                                                                                                                                                                                                                                                  | d last, SS<br>cates tha                                  | SPEN is cl                   | eared)<br>It has been                                           | cleared whe                         |              |             | disabled, or when the Stop bit is<br>ET)                                             |  |  |  |

| bit 2: | This bit                                                                                                                                                                                                                                                               | holds th<br>match t<br>d                                 | ne R/W bit                   |                                                                 |                                     |              | dress match | n. This bit is only valid from the                                                   |  |  |  |

| bit 1: | 1 = India                                                                                                                                                                                                                                                              | cates tha                                                | at the user                  | it I <sup>2</sup> C mode<br>needs to u<br>to be upda            | pdate the ad                        | dress in the | e SSPADD r  | register                                                                             |  |  |  |

| bit 0: | BF: Buf                                                                                                                                                                                                                                                                | fer Full S                                               | Status bit                   |                                                                 |                                     |              |             |                                                                                      |  |  |  |

|        | 1 = Rec                                                                                                                                                                                                                                                                | eive con                                                 |                              | es)<br>PBUF is full<br>SSPBUF is                                |                                     |              |             |                                                                                      |  |  |  |

|        | 1 = Tran                                                                                                                                                                                                                                                               | ismit in p                                               |                              | SPBUF is t<br>PBUF is en                                        |                                     |              |             |                                                                                      |  |  |  |

|        |                                                                                                                                                                                                                                                                        |                                                          |                              |                                                                 |                                     |              |             |                                                                                      |  |  |  |

## FIGURE 8-5: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h) (PIC16CR72)

| R/W-0    | R/W-0                                                                                                           | R/W-0                                                                                                                                             | R/W-0                                                                                                                                      | R/W-0                                                                                                               | R/W-0                                                                                               | R/W-0                                                           | R/W-0                  |                                                                                                                          |

|----------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------|

| WCOL     | SSPOV                                                                                                           | SSPEN                                                                                                                                             | CKP                                                                                                                                        | SSPM3                                                                                                               | SSPM2                                                                                               | SSPM1                                                           | SSPM0                  | R = Readable bit                                                                                                         |

| bit7     |                                                                                                                 |                                                                                                                                                   |                                                                                                                                            |                                                                                                                     |                                                                                                     |                                                                 | bit0                   | W = Writable bit<br>U = Unimplemented bit, rea<br>as '0'<br>- n =Value at POR reset                                      |

| bit 7:   | 1 = The S                                                                                                       | leared in s                                                                                                                                       | gister is w                                                                                                                                |                                                                                                                     | e it is still tr                                                                                    | ransmitting                                                     | the previo             | us word                                                                                                                  |

| bit 6:   | SSPOV: R                                                                                                        | eceive Ov                                                                                                                                         | erflow Ind                                                                                                                                 | icator bit                                                                                                          |                                                                                                     |                                                                 |                        |                                                                                                                          |

|          | the data in<br>if only trar                                                                                     | byte is rece<br>SSPSR is<br>asmitting da<br>reception (                                                                                           | lost. Over<br>ata, to ave                                                                                                                  | rflow can o<br>oid setting                                                                                          | only occur i<br>overflow.                                                                           | in slave mo<br>In master                                        | ode. The us operation, | revious data. In case of overflor<br>er must read the SSPBUF, event<br>the overflow bit is not set sind<br>BUF register. |

|          |                                                                                                                 | is received<br>mode. SS                                                                                                                           |                                                                                                                                            |                                                                                                                     |                                                                                                     |                                                                 |                        | us byte. SSPOV is a "don't car                                                                                           |

| bit 5:   | SSPEN: S                                                                                                        | ynchronou                                                                                                                                         | is Serial P                                                                                                                                | ort Enable                                                                                                          | e bit                                                                                               |                                                                 |                        |                                                                                                                          |

|          | $\frac{\text{In SPI model}}{1 = \text{Enable}}$ $0 = \text{Disable}$                                            | es serial po                                                                                                                                      |                                                                                                                                            |                                                                                                                     |                                                                                                     |                                                                 | s serial por<br>pins   | t pins                                                                                                                   |

|          | 0 = Disabl                                                                                                      | es the seria                                                                                                                                      | ort and co                                                                                                                                 | nfigures th                                                                                                         | nese pins a                                                                                         | as I/O port                                                     | pins                   | ial port pins<br>s input or output.                                                                                      |

| bit 4:   | <b>CKP</b> : Cloc<br>In SPI mod<br>1 = Idle sta0 = Idle staIn I2C modSCK relea1 = Enable0 = Holds               | de<br>ate for cloc<br>ate for cloc<br>de<br>se control<br>e clock                                                                                 | k is a higł<br>k is a low                                                                                                                  | level                                                                                                               | to ensure                                                                                           | data setu                                                       | p time)                |                                                                                                                          |

| bit 3-0: | $0001 = SF$ $0010 = SF$ $0100 = SF$ $0101 = SF$ $0110 = I^{2}C$ $0111 = I^{2}C$ $1011 = I^{2}C$ $1110 = I^{2}C$ | PI master of<br>PI master of<br>PI master of<br>PI master of<br>PI slave mo<br>C slave mo<br>C slave mo<br>C slave mo<br>C slave mo<br>C slave mo | pperation,<br>pperation,<br>pperation,<br>pperation,<br>ode, clock<br>ode, clock<br>de, 7-bit a<br>de, 10-bit<br>controlled<br>de, 7-bit a | clock = FC<br>clock = FC<br>clock = FC<br>clock = TN<br>= SCK pir<br>address<br>address<br>d master o<br>address wi | osc/4<br>osc/16<br>osc/64<br>/IR2 outpu<br>a. SS pin c<br>a. SS pin c<br>peration (s<br>th start an | t/2<br>ontrol ena<br>ontrol disa<br>slave idle)<br>d stop bit i |                        |                                                                                                                          |

MODE - PIC16CR72

A block diagram of the SSP Module in SPI Mode is shown in Figure 8-6.

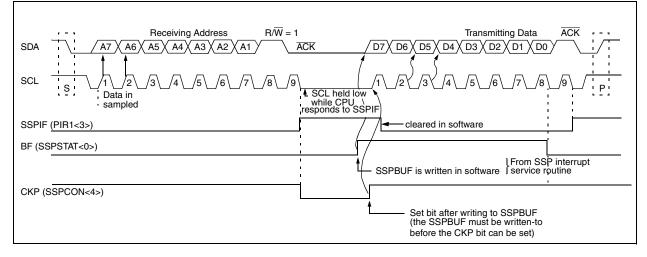

#### 8.4.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

### FIGURE 8-8: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address         R/W           SDA         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | =0Receiving Data<br>                        |                                        |            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------|------------|

| SSPIF (PIR1<3>)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Cleared in software                         | <br>                                   | Bus Master |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             | <u>+</u><br>Ⅰ                          | terminates |

| BF (SSPSTAT<0>)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>SSPBUF register is read</li> </ul> |                                        |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |                                        |            |

| SSPOV (SSPCON<6>)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                             |                                        |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bit SSPOV is set be                         | ecause the SSPBUF register is still fu | ill. 📥 🛛   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             | ACK is not se                          | ent.       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |                                        |            |

#### 8.4.1.3 TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSP-BUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 8-9). An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

#### 10.2 **Oscillator Configurations**

#### 10.2.1 **OSCILLATOR TYPES**

The PIC16CXXX family can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

#### 10.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

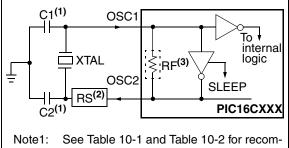

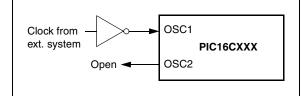

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 10-2). The PIC16CXXX family oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/ CLKIN pin (Figure 10-3).

#### FIGURE 10-2: CRYSTAL/CERAMIC **RESONATOR OPERATION** (HS, XT OR LP **OSC CONFIGURATION)**

- mended values of C1 and C2. 2: A series resistor (RS) may be required for

- AT strip cut crystals.

- 3: RF varies with the crystal chosen.

#### FIGURE 10-3: EXTERNAL CLOCK INPUT **OPERATION (HS, XT OR LP OSC CONFIGURATION)**

#### **TABLE 10-1 CERAMIC RESONATORS**

Г

| Ranges Tested: |                                                                         |                                         |                                         |  |  |  |  |  |  |

|----------------|-------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|--|--|--|

| Mode           | Freq                                                                    | OSC1                                    | OSC2                                    |  |  |  |  |  |  |

| XT             | 455 kHz<br>2.0 MHz<br>4.0 MHz                                           | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |  |  |  |  |

| HS             | 8.0 MHz<br>16.0 MHz                                                     | 10 - 68 pF<br>10 - 22 pF                | 10 - 68 pF<br>10 - 22 pF                |  |  |  |  |  |  |

|                | These values are for design guidance only. See notes at bottom of page. |                                         |                                         |  |  |  |  |  |  |

| Resonator      | rs Used:                                                                |                                         |                                         |  |  |  |  |  |  |

| 455 kHz        | Panasonic E                                                             | FO-A455K04B                             | ± 0.3%                                  |  |  |  |  |  |  |

| 2.0 MHz        | Murata Erie                                                             | $\pm 0.5\%$                             |                                         |  |  |  |  |  |  |

| 4.0 MHz        | Murata Erie                                                             | Murata Erie CSA4.00MG ± 0.5%            |                                         |  |  |  |  |  |  |

| 8.0 MHz        | Murata Erie                                                             | CSA8.00MT                               | $\pm 0.5\%$                             |  |  |  |  |  |  |

#### **TABLE 10-2 CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR**

All resonators used did not have built-in capacitors.

± 0.5%

16.0 MHz Murata Erie CSA16.00MX

| Osc Type | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|-----------------|------------------|------------------|

| LP       | 32 kHz          | 33 pF            | 33 pF            |

|          | 200 kHz         | 15 pF            | 15 pF            |

| XT       | 200 kHz         | 47-68 pF         | 47-68 pF         |

|          | 1 MHz           | 15 pF            | 15 pF            |

|          | 4 MHz           | 15 pF            | 15 pF            |

| HS       | 4 MHz           | 15 pF            | 15 pF            |

|          | 8 MHz           | 15-33 pF         | 15-33 pF         |

|          | 20 MHz          | 15-33 pF         | 15-33 pF         |

|          |                 |                  |                  |

These values are for design guidance only. See notes at bottom of page.

| Crystals Used |                        |          |  |  |  |

|---------------|------------------------|----------|--|--|--|

| 32 kHz        | Epson C-001R32.768K-A  | ± 20 PPM |  |  |  |

| 200 kHz       | STD XTL 200.000KHz     | ± 20 PPM |  |  |  |

| 1 MHz         | ECS ECS-10-13-1        | ± 50 PPM |  |  |  |

| 4 MHz         | ECS ECS-40-20-1        | ± 50 PPM |  |  |  |

| 8 MHz         | EPSON CA-301 8.000M-C  | ± 30 PPM |  |  |  |

| 20 MHz        | EPSON CA-301 20.000M-C | ± 30 PPM |  |  |  |

Note 1: Recommended values of C1 and C2 are identical to the ranges tested (Table 10-1).

- 2: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification.

#### 10.4 Power-On Reset (POR)

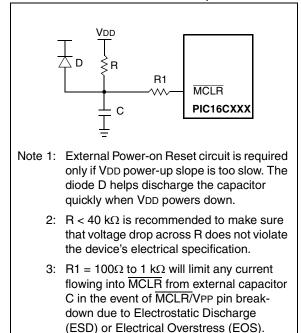

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details. For a slow rise time, see Figure 10-6.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the startup conditions.

#### FIGURE 10-6: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

# 10.5 <u>Power-up Timer (PWRT)</u>

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

# 10.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

# 10.7 Brown-Out Reset (BOR)

A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V (3.8V - 4.2V range) for greater than parameter #35, the brown-out situation will reset the chip. A reset may not occur if VDD falls below 4.0V for less than parameter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms. If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer will execute a 72 ms time delay. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

#### 10.10 Interrupts

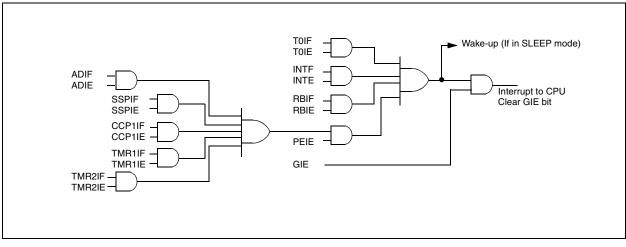

The PIC16C72/CR72 has 8 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit

#### 10.10.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 10.13 for details on SLEEP mode.

#### 10.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 4.0)

#### 10.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 3.2)

#### FIGURE 10-11: INTERRUPT LOGIC

# **PIC16C72 Series**

# TABLE 13-1 CROSS REFERENCE OF DEVICE SPECS (PIC16C72) FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| OSC | PIC16C72-04                                                                                                                                         | PIC16C72-10                                                                                                                                        | PIC16C72-20                                                                                                                                        | PIC16LC72-04                                                                                              | JW Devices                                                                                                |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 µA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 µA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5.0 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                  |

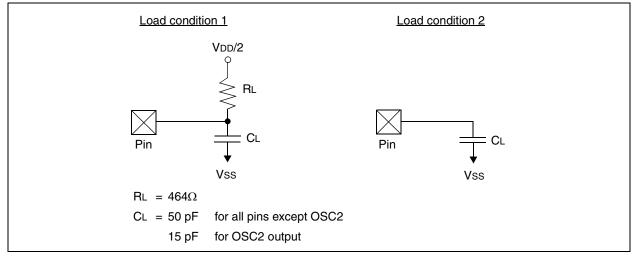

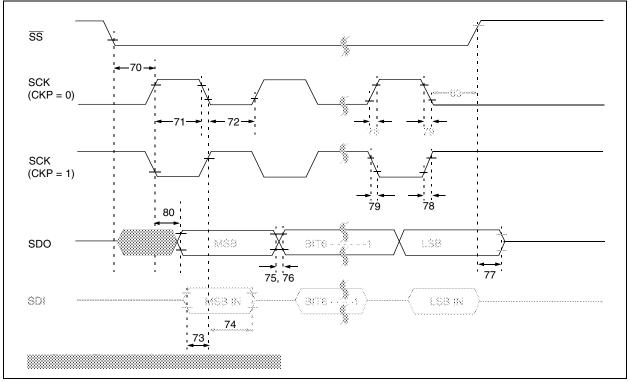

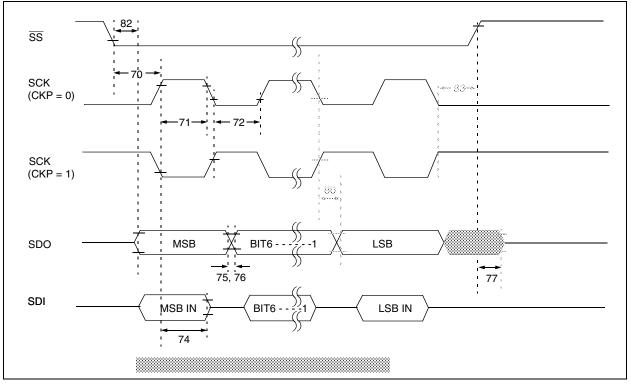

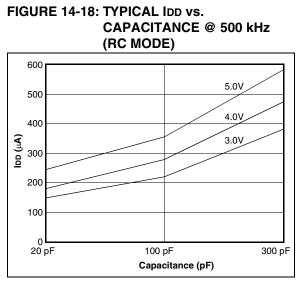

| хт  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 µA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5.0 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                  |