Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc72-04i-so |

TABLE 1-1 PIC16C72/CR72 PINOUT DESCRIPTION

| Pin Name          | Pin#       | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                  |

|-------------------|------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 9          | ı             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT       | 10         | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/VPP          | 1          | I/P           | ST                     | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                      |

|                   |            |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0           | 2          | I/O           | TTL                    | RA0 can also be analog input0.                                                                                                                                                                               |

| RA1/AN1           | 3          | I/O           | TTL                    | RA1 can also be analog input1.                                                                                                                                                                               |

| RA2/AN2           | 4          | I/O           | TTL                    | RA2 can also be analog input2.                                                                                                                                                                               |

| RA3/AN3/VREF      | 5          | I/O           | TTL                    | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                    |

| RA4/T0CKI         | 6          | I/O           | ST                     | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                             |

| RA5/SS/AN4        | 7          | I/O           | TTL                    | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                           |

|                   |            |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT           | 21         | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1               | 22         | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB2               | 23         | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB3               | 24         | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB4               | 25         | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB5               | 26         | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB6               | 27         | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                           |

| RB7               | 28         | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                            |

|                   |            |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI   | 11         | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or Timer1 clock input.                                                                                                                                          |

| RC1/T1OSI         | 12         | I/O           | ST                     | RC1 can also be the Timer1 oscillator input.                                                                                                                                                                 |

| RC2/CCP1          | 13         | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/PWM1 output.                                                                                                                                              |

| RC3/SCK/SCL       | 14         | I/O           | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                           |

| RC4/SDI/SDA       | 15         | I/O           | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |

| RC5/SDO           | 16         | I/O           | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6               | 17         | I/O           | ST                     | ,                                                                                                                                                                                                            |

| RC7               | 18         | I/O           | ST                     |                                                                                                                                                                                                              |

| Vss               | 8, 19      | Р             | _                      | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| VDD               | 20         | Р             | _                      | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Logond: L-input ( | ) - output | L             | L                      | putaut B – power                                                                                                                                                                                             |

Legend: I = input O = output

I/O = input/output

P = power

— = Not used

TTL = TTL input

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

#### 2.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the peripheral interrupts.

**Note:** Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

#### FIGURE 2-6: PIE1 REGISTER (ADDRESS 8Ch)

| U-0      | R/W-0     | U-0                                     | U-0        | R/W-0      | R/W-0       | R/W-0  | R/W-0  |                                                                              |

|----------|-----------|-----------------------------------------|------------|------------|-------------|--------|--------|------------------------------------------------------------------------------|

| _        | ADIE      | _                                       | _          | SSPIE      | CCP1IE      | TMR2IE | TMR1IE | R = Readable bit                                                             |

| bit7     |           |                                         |            |            |             |        | bit0   | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

| bit 7:   | Unimpler  | mented: P                               | lead as '0 |            |             |        |        |                                                                              |

| bit 6:   | 1 = Enabl | O Converte<br>es the A/D<br>les the A/D | interrupt  |            | it          |        |        |                                                                              |

| bit 5-4: | Unimpler  | mented: R                               | ead as '0' |            |             |        |        |                                                                              |

| bit 3:   | 1 = Enabl | ynchronou<br>es the SS<br>les the SS    | P interrup | t          | pt Enable t | oit    |        |                                                                              |

| bit 2:   | 1 = Enabl | CCP1 Inte<br>es the CC<br>les the CC    | P1 interru | pt         |             |        |        |                                                                              |

| bit 1:   | 1 = Enabl | TMR2 to F<br>es the TM<br>les the TM    | R2 to PR   | 2 match in | •           |        |        |                                                                              |

| bit 0:   | 1 = Enabl | TMR1 Ove<br>es the TM<br>les the TM     | R1 overflo | w interrup | ot          |        |        |                                                                              |

TABLE 3-5 PORTC FUNCTIONS

| Name            | Bit# | Buffer Type | Function                                                                              |

|-----------------|------|-------------|---------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input                  |

| RC1/T1OSI       | bit1 | ST          | Input/output port pin or Timer1 oscillator input                                      |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output                   |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).       |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output                          |

| RC6             | bit6 | ST          | Input/output port pin                                                                 |

| RC7             | bit7 | ST          | Input/output port pin                                                                 |

Legend: ST = Schmitt Trigger input

#### TABLE 3-6 SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7   | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|---------|-------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 07h     | PORTC | RC7     | RC6                           | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                 |

| 87h     | TRISC | PORTC I | PORTC Data Direction Register |       |       |       |       |       |       |                          | 1111 1111                 |

Legend: x = unknown, u = unchanged.

#### 5.2 <u>Timer1 Oscillator</u>

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 5-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

TABLE 5-1 CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type                               | Freq            | C2            |           |  |  |  |  |

|----------------------------------------|-----------------|---------------|-----------|--|--|--|--|

| LP                                     | 32 kHz          | 33 pF         | 33 pF     |  |  |  |  |

|                                        | 100 kHz         | 15 pF         |           |  |  |  |  |

|                                        | 200 kHz         | 15 pF         | 15 pF     |  |  |  |  |

| These v                                | alues are for o | design guidan | ice only. |  |  |  |  |

| Crystals Tes                           | sted:           |               |           |  |  |  |  |

| 32.768 kHz                             | Epson C-00      | 1R32.768K-A   | ± 20 PPM  |  |  |  |  |

| 100 kHz Epson C-2 100.00 KC-P ± 20 PPM |                 |               |           |  |  |  |  |

| 200 kHz STD XTL 200.000 kHz ± 20 PPM   |                 |               |           |  |  |  |  |

|                                        |                 |               |           |  |  |  |  |

- Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

#### 5.3 <u>Timer1 Interrupt</u>

The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

### 5.4 Resetting Timer1 using a CCP Trigger Output

If the CCP module is configured in compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The special event triggers from the | CCP1   |

|-------|-------------------------------------|--------|

|       | module will not set interrupt fla   | ag bit |

|       | TMR1IF (PIR1<0>).                   |        |

Timer1 must be configured for either timer or synchronized counter mode to take advantage of this feature. If Timer1 is running in asynchronous counter mode, this reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer1.

TABLE 5-2 REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address | Name   | Bit 7   | Bit 6                                                                      | Bit 5         | Bit 4         | Bit 3         | Bit 3 Bit 2 Bit 1 Bit 0 PO |             | Value on:<br>POR,<br>BOR | Value on all other resets |           |

|---------|--------|---------|----------------------------------------------------------------------------|---------------|---------------|---------------|----------------------------|-------------|--------------------------|---------------------------|-----------|

| 0Bh,8Bh | INTCON | GIE     | PEIE                                                                       | TOIE          | INTE          | RBIE          | TOIF                       | INTF        | RBIF                     | 0000 000x                 | 0000 000u |

| 0Ch     | PIR1   | (1)     | ADIF                                                                       | (1)           | (1)           | SSPIF         | CCP1IF                     | TMR2IF      | TMR1IF                   | 0000 0000                 | 0000 0000 |

| 8Ch     | PIE1   | (1)     | ADIE                                                                       | (1)           | (1)           | SSPIE         | CCP1IE                     | TMR2IE      | TMR1IE                   | 0000 0000                 | 0000 0000 |

| 0Eh     | TMR1L  | Holding | registe                                                                    | r for the Lea | st Significan | t Byte of the | 16-bit TMF                 | R1 register |                          | xxxx xxxx                 | uuuu uuuu |

| 0Fh     | TMR1H  | Holding | Holding register for the Most Significant Byte of the 16-bit TMR1 register |               |               |               |                            |             |                          | xxxx xxxx                 | uuuu uuuu |

| 10h     | T1CON  | _       | _                                                                          | T1CKPS1       | T1CKPS0       | T1OSCEN       | T1SYNC                     | TMR1CS      | TMR10N                   | 00 0000                   | uu uuuu   |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: These bits are unimplemented, read as '0'.

#### 8.4.1.1 ADDRESSING

Once the SSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) - on the falling edge of the ninth SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address the first byte would equal

'1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7- 9 for slave-transmitter:

- Receive first (high) byte of Address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- Receive second (low) byte of Address (bits SSPIF, BF, and UA are set).

- Update the SSPADD register with the first (high) byte of Address, if match releases SCL line, this will clear bit UA.

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive repeated START condition.

- Receive first (high) byte of Address (bits SSPIF and BF are set).

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

TABLE 8-3 DATA TRANSFER RECEIVED BYTE ACTIONS

|    | ts as Data<br>Received |                    |                    | Set bit SSPIF                     |

|----|------------------------|--------------------|--------------------|-----------------------------------|

| BF | SSPOV                  | $SSPSR \to SSPBUF$ | Generate ACK Pulse | (SSP Interrupt occurs if enabled) |

| 0  | 0                      | Yes                | Yes                | Yes                               |

| 1  | 0                      | No                 | No                 | Yes                               |

| 1  | 1                      | No                 | No                 | Yes                               |

| 0  | 1                      | No                 | No                 | Yes                               |

**NOTES:**

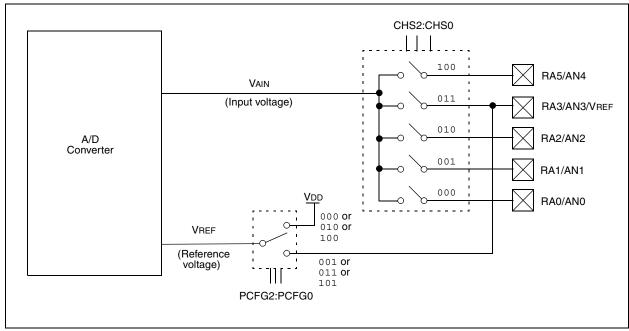

The ADRES register contains the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRES register, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 9-3.

The value that is in the ADRES register is not modified for a Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 9.1. After this acquisition time has elapsed the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins / voltage reference / and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- · Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared

- Waiting for the A/D interrupt

- 6. Read A/D Result register (ADRES), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

#### FIGURE 9-3: A/D BLOCK DIAGRAM

#### 9.2 <u>Selecting the A/D Conversion Clock</u>

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.5TAD per 8-bit conversion. The source of the A/D conversion clock is software selectable. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- · Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 9-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

#### 9.3 Configuring Analog Port Pins

The ADCON1, TRISA, and TRISE registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

Note 2: Analog levels on any pin that is defined as a digital input (including the AN4:AN0 pins), may cause the input buffer to consume current that is out of the devices specification.

TABLE 9-1 TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock              | Source (TAD) | Device Frequency          |                           |                           |                         |  |  |  |  |

|-----------------------|--------------|---------------------------|---------------------------|---------------------------|-------------------------|--|--|--|--|

| Operation ADCS1:ADCS0 |              | 20 MHz                    | 5 MHz                     | 1.25 MHz                  | 333.33 kHz              |  |  |  |  |

| 2Tosc                 | 00           | 100 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6 μs                    |  |  |  |  |

| 8Tosc                 | 01           | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6.4 μs                    | 24 μs <sup>(3)</sup>    |  |  |  |  |

| 32Tosc                | 10           | 1.6 μs                    | 6.4 μs                    | 25.6 μs <sup>(3)</sup>    | 96 μs <sup>(3)</sup>    |  |  |  |  |

| RC <sup>(5)</sup>     | 11           | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1)</sup> |  |  |  |  |

Legend: Shaded cells are outside of recommended range.

- Note 1: The RC source has a typical TAD time of 4  $\mu s$ .

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: When device frequency is greater than 1 MHz, the RC A/D conversion clock source is recommended for sleep operation only.

- 5: For extended voltage devices (LC), please refer to Electrical Specifications section.

TABLE 10-6 INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or Inter-<br>rupt |

|----------|------------------------------------|--------------------------|-----------------------------------|

| W        | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                         |

| INDF     | N/A                                | N/A                      | N/A                               |

| TMR0     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                         |

| PCL      | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>             |

| STATUS   | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu(3)                      |

| FSR      | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                         |

| PORTA    | 0x 0000                            | 0u 0000                  | uu uuuu                           |

| PORTB    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                         |

| PORTC    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                         |

| PCLATH   | 0 0000                             | 0 0000                   | u uuuu                            |

| INTCON   | 0000 000x                          | 0000 000u                | uuuu uuuu(1)                      |

| PIR1     | -0 0000                            | -0 0000                  | -u uuuu(1)                        |

| TMR1L    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                         |

| TMR1H    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                         |

| T1CON    | 00 0000                            | uu uuuu                  | uu uuuu                           |

| TMR2     | 0000 0000                          | 0000 0000                | uuuu uuuu                         |

| T2CON    | -000 0000                          | -000 0000                | -uuu uuuu                         |

| SSPBUF   | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                         |

| SSPCON   | 0000 0000                          | 0000 0000                | uuuu uuuu                         |

| CCPR1L   | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                         |

| CCPR1H   | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                         |

| CCP1CON  | 00 0000                            | 00 0000                  | uu uuuu                           |

| ADRES    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                         |

| ADCON0   | 0000 00-0                          | 0000 00-0                | uuuu uu-u                         |

| OPTION   | 1111 1111                          | 1111 1111                | uuuu uuuu                         |

| TRISA    | 11 1111                            | 11 1111                  | uu uuuu                           |

| TRISB    | 1111 1111                          | 1111 1111                | uuuu uuuu                         |

| TRISC    | 1111 1111                          | 1111 1111                | uuuu uuuu                         |

| PIE1     | -0 0000                            | -0 0000                  | -u uuuu                           |

| PCON     | 0u                                 | uu                       | uu                                |

| PR2      | 1111 1111                          | 1111 1111                | 1111 1111                         |

| SSPADD   | 0000 0000                          | 0000 0000                | uuuu uuuu                         |

| SSPSTAT  | 00 0000                            | 00 0000                  | uu uuuu                           |

| ADCON1   | 000                                | 000                      | uuu                               |

Legend: u = unchanged, x = unknown, -= unimplemented bit, read as '0', <math>q = value depends on condition

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

<sup>2:</sup> When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

<sup>3:</sup> See Table 10-5 for reset value for specific condition.

#### 10.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, i.e., W register and STATUS register. This will have to be implemented in software.

Example 10-1 stores and restores the W and STATUS registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

#### The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Executes the ISR code.

- d) Restores the STATUS register (and bank select bit).

- e) Restores the W register.

#### **EXAMPLE 10-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM**

```

W TEMP

;Copy W to W TEMP register, could be bank one or zero

SWAPF

STATUS, W

;Swap status to be saved into W

CLRF

STATUS

; bank 0, regardless of current bank, Clears IRP, RP1, RP0

MOVWF

STATUS TEMP

;Save status to bank zero STATUS_TEMP register

: Interrupt Service Routine (ISR) - user defined

;Swap STATUS_TEMP register into \mbox{W}

SWAPF

STATUS_TEMP,W

;(sets bank to original state)

MOVWF

; Move W into STATUS register

STATUS

W TEMP, F

; Swap W TEMP

SWAPF

SWAPF

W TEMP, W

;Swap W TEMP into W

```

TABLE 11-2 PIC16CXXX INSTRUCTION SET

| Mnemo  |                                        | Description                  | Cycles  |        | 14-Bit | Opcode | 9    | Status   | Notes |  |

|--------|----------------------------------------|------------------------------|---------|--------|--------|--------|------|----------|-------|--|

| Operan | ıds                                    |                              |         | MSb    |        |        | LSb  | Affected |       |  |

|        | BYTE-ORIENTED FILE REGISTER OPERATIONS |                              |         |        |        |        |      |          |       |  |

| ADDWF  | f, d                                   | Add W and f                  | 1       | 00     | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |  |

| ANDWF  | f, d                                   | AND W with f                 | 1       | 0.0    | 0101   | dfff   | ffff | Z        | 1,2   |  |

| CLRF   | f                                      | Clear f                      | 1       | 00     | 0001   | lfff   | ffff | Z        | 2     |  |

| CLRW   | -                                      | Clear W                      | 1       | 0.0    | 0001   | 0xxx   | xxxx | Z        |       |  |

| COMF   | f, d                                   | Complement f                 | 1       | 0.0    | 1001   | dfff   | ffff | Z        | 1,2   |  |

| DECF   | f, d                                   | Decrement f                  | 1       | 00     | 0011   | dfff   | ffff | Z        | 1,2   |  |

| DECFSZ | f, d                                   | Decrement f, Skip if 0       | 1(2)    | 0.0    | 1011   | dfff   | ffff |          | 1,2,3 |  |

| INCF   | f, d                                   | Increment f                  | 1       | 00     | 1010   | dfff   | ffff | Z        | 1,2   |  |

| INCFSZ | f, d                                   | Increment f, Skip if 0       | 1(2)    | 0.0    | 1111   | dfff   | ffff |          | 1,2,3 |  |

| IORWF  | f, d                                   | Inclusive OR W with f        | ì       | 0.0    | 0100   | dfff   | ffff | Z        | 1,2   |  |

| MOVF   | f, d                                   | Move f                       | 1       | 0.0    | 1000   | dfff   | ffff | Z        | 1,2   |  |

| MOVWF  | f                                      | Move W to f                  | 1       | 0.0    | 0000   | lfff   | ffff |          |       |  |

| NOP    | -                                      | No Operation                 | 1       | 0.0    | 0000   | 0xx0   | 0000 |          |       |  |

| RLF    | f, d                                   | Rotate Left f through Carry  | 1       | 0.0    | 1101   | dfff   | ffff | С        | 1,2   |  |

| RRF    | f, d                                   | Rotate Right f through Carry | 1       | 0.0    | 1100   | dfff   | ffff | С        | 1,2   |  |

| SUBWF  | f, d                                   | Subtract W from f            | 1       | 0.0    | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |  |

| SWAPF  | f, d                                   | Swap nibbles in f            | 1       | 0.0    | 1110   | dfff   | ffff | , ,      | 1,2   |  |

| XORWF  | f, d                                   | Exclusive OR W with f        | 1       | 00     | 0110   | dfff   | ffff | Z        | 1,2   |  |

|        |                                        | BIT-ORIENTED FILE REGIST     | ER OPER | RATION | IS     |        |      | •        |       |  |

| BCF    | f, b                                   | Bit Clear f                  | 1       | 01     | 00bb   | bfff   | ffff |          | 1,2   |  |

| BSF    | f, b                                   | Bit Set f                    | 1       | 01     | 01bb   | bfff   | ffff |          | 1,2   |  |

| BTFSC  | f, b                                   | Bit Test f, Skip if Clear    | 1 (2)   | 01     | 10bb   | bfff   | ffff |          | 3     |  |

| BTFSS  | f, b                                   | Bit Test f, Skip if Set      | 1 (2)   | 01     | 11bb   | bfff   | ffff |          | 3     |  |

|        |                                        | LITERAL AND CONTROL          | OPERAT  | IONS   |        |        |      |          |       |  |

| ADDLW  | k                                      | Add literal and W            | 1       | 11     | 111x   | kkkk   | kkkk | C,DC,Z   |       |  |

| ANDLW  | k                                      | AND literal with W           | 1       | 11     | 1001   | kkkk   | kkkk | Ζ        |       |  |

| CALL   | k                                      | Call subroutine              | 2       | 10     | 0kkk   | kkkk   | kkkk |          |       |  |

| CLRWDT | -                                      | Clear Watchdog Timer         | 1       | 0.0    | 0000   | 0110   | 0100 | TO,PD    |       |  |

| GOTO   | k                                      | Go to address                | 2       | 10     | 1kkk   | kkkk   | kkkk |          |       |  |

| IORLW  | k                                      | Inclusive OR literal with W  | 1       | 11     | 1000   | kkkk   | kkkk | Z        |       |  |

| MOVLW  | k                                      | Move literal to W            | 1       | 11     | 00xx   | kkkk   | kkkk |          |       |  |

| RETFIE | -                                      | Return from interrupt        | 2       | 0.0    | 0000   | 0000   | 1001 |          |       |  |

| RETLW  | k                                      | Return with literal in W     | 2       | 11     | 01xx   | kkkk   | kkkk |          |       |  |

| RETURN | -                                      | Return from Subroutine       | 2       | 0.0    | 0000   | 0000   | 1000 |          |       |  |

| SLEEP  | -                                      | Go into standby mode         | 1       | 0.0    | 0000   | 0110   | 0011 | TO,PD    |       |  |

| SUBLW  | k                                      | Subtract W from literal      | 1       | 11     |        | kkkk   |      | C,DC,Z   |       |  |

| XORLW  | k                                      | Exclusive OR literal with W  | 1       | 11     | 1010   | kkkk   | kkkk | Z        |       |  |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

<sup>2:</sup> If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

<sup>3:</sup> If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

#### 13.0 ELECTRICAL CHARACTERISTICS - PIC16C72 SERIES

#### **Absolute Maximum Ratings †**

| Parameter                                                          | PIC16C72              | PIC16CR72             |

|--------------------------------------------------------------------|-----------------------|-----------------------|

| Ambient temperature under bias                                     | -55 to +125°C         | -55 to +125°C         |

| Storage temperature                                                | -65°C to +150°C       | -65°C to +150°C       |

| Voltage on any pin with respect to VSS (except VDD, MCLR, and RA4) | -0.3V to (VDD + 0.3V) | -0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to VSS                                 | -0.3 to +7.5V         | TBD                   |

| Voltage on MCLR with respect to Vss (Note 1)                       | -0.3 to +14V          | TBD                   |

| Voltage on RA4 with respect to Vss                                 | -0.3 to +14V          | TBD                   |

| Total power dissipation (Note 2)                                   | 1.0W                  | 1.0W                  |

| Maximum current out of Vss pin                                     | 300 mA                | 300 mA                |

| Maximum current into VDD pin                                       | 250 mA                | 250 mA                |

| Input clamp current, IIK (VI < 0 or VI > VDD)                      | ± 20 mA               | ± 20 mA               |

| Output clamp current, IOK (Vo < 0 or Vo > VDD)                     | ± 20 mA               | ± 20 mA               |

| Maximum output current sunk by any I/O pin                         | 25 mA                 | 25 mA                 |

| Maximum output current sourced by any I/O pin                      | 25 mA                 | 25 mA                 |

| Maximum current sunk by PORTA and PORTB (combined)                 | 200 mA                | 200 mA                |

| Maximum current sourced by PORTA and PORTB (combined)              | 200 mA                | 200 mA                |

| Maximum current sunk by PORTC                                      | 200 mA                | 200 mA                |

| Maximum current sourced by PORTC                                   | 200 mA                | 200 mA                |

<sup>1.</sup> Voltage spikes below Vss at the  $\overline{\text{MCLR}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}}$  pin rather than pulling this pin directly to Vss.

<sup>2.</sup> Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD - VOH) x IOH} +  $\sum$  (VOI x IOL).

<sup>†</sup> NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 13.1 DC Characteristics: PIC16C72/CR72-04 (Commercial, Industrial, Extended)

**DC CHARACTERISTICS**

PIC16C72/CR72-10 (Commercial, Industrial, Extended)

PIC16C72/CR72-20 (Commercial, Industrial, Extended)

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C}$  for extended,

-40°C  $\leq$  TA  $\leq$  +85°C for industrial and 0°C  $\leq$  TA  $\leq$  +70°C for commercial

| 0°C ≤ TA ≤ +70°C for commercial |                                                                   |       |            |         |                |            |        |                |        |                                                    |

|---------------------------------|-------------------------------------------------------------------|-------|------------|---------|----------------|------------|--------|----------------|--------|----------------------------------------------------|

| Param                           | Characteristic                                                    | Sym   | F          | PIC16C7 | 2              | PIC16CR72  |        |                | Units  | Conditions                                         |

| No.                             | Characteristic                                                    | Sylli | Min        | Typ†    | Max            | Min        | Typ†   | Max            | Ullits | Conditions                                         |

| D001<br>D001A                   | Supply Voltage                                                    | VDD   | 4.0<br>4.5 | -<br>-  | <b>6.0</b> 5.5 | 4.0<br>4.5 | -<br>- | <b>5.5</b> 5.5 | V<br>V | XT, RC and LP osc<br>HS osc                        |

| D002*                           | RAM Data Retention<br>Voltage (Note 1)                            | VDR   | -          | 1.5     | -              | -          | 1.5    | -              | V      |                                                    |

| D003                            | VDD start voltage to<br>ensure internal Power-<br>on Reset Signal | VPOR  | -          | Vss     | -              | -          | Vss    | -              | V      | See section on Power-<br>on Reset for details      |

| D004*                           | VDD rise rate to ensure internal Power-on Reset Signal            | SVDD  | 0.05       | -       | -              | 0.05       | -      | -              | V/ms   | See section on Power-<br>on Reset for details      |

| D005                            | Brown-out Reset Voltage                                           | Bvdd  | 3.7        | 4.0     | 4.3            | 3.7        | 4.0    | 4.3            | V      | BODEN bit in configura-<br>tion word enabled       |

|                                 |                                                                   |       | 3.7        | 4.0     | 4.4            | 3.7        | 4.0    | 4.4            | V      | Extended Only                                      |

| D010                            | Supply Current (Note 2,5)                                         | IDD   | -          | 2.7     | 5.0            | -          | 2.7    | 5.0            | mA     | XT, RC osc<br>Fosc = 4 MHz,<br>VDD = 5.5V (Note 4) |

| D013                            |                                                                   |       | -          | 10      | 20             | -          | 10     | 20             | mA     | HS osc<br>Fosc = 20 MHz,<br>VDD = 5.5V             |

| D015                            | Brown-out Reset<br>Current (Note 6)                               | ∆lbor | -          | 350     | 425            | -          | 350    | 425            | μА     | BOR enabled,<br>VDD = 5.0V                         |

| D020                            | Power-down Current (Note 3,5)                                     | IPD   | -          | 10.5    | 42             | -          | 10.5   | 42             | μА     | VDD = 4.0V, WDT enabled, -40°C to +85°C            |

| D021                            |                                                                   |       | -          | 1.5     | 16             | -          | 1.5    | 16             | μΑ     | VDD = 4.0V, WDT disabled, -0°C to +70°C            |

| D021A                           |                                                                   |       | -          | 1.5     | 19             | -          | 1.5    | 19             | μΑ     | VDD = 4.0V, WDT disabled, -40°C to +85°C           |

| D021B                           |                                                                   |       | -          | 2.5     | 19             | -          | 2.5    | 19             | μΑ     | VDD = 4.0V, WDT disabled, -40°C to +125°C          |

| D023                            | Brown-out Reset<br>Current (Note 6)                               | ∆lbor | -          | 350     | 425            | -          | 350    | 425            | μА     | BOR enabled VDD = 5.0V                             |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- Note 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

- **Note 3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- **Note 4:** For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- Note 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- Note 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

#### 13.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS                     |                          | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|---------------------------------|--------------------------|-----------|----------------------------------------|

| 2. TppS                         |                          | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                               |                          |           |                                        |

| F                               | Frequency                | Т         | Time                                   |

| Lowercase letters               | (pp) and their meanings: |           |                                        |

| рр                              |                          |           |                                        |

| СС                              | CCP1                     | osc       | OSC1                                   |

| ck                              | CLKOUT                   | rd        | RD                                     |

| cs                              | CS                       | rw        | RD or WR                               |

| di                              | SDI                      | sc        | SCK                                    |

| do                              | SDO                      | ss        | SS                                     |

| dt                              | Data in                  | tO        | T0CKI                                  |

| io                              | I/O port                 | t1        | T1CKI                                  |

| mc                              | MCLR                     | wr        | WR                                     |

| Uppercase letters               | and their meanings:      |           |                                        |

| S                               |                          |           |                                        |

| F                               | Fall                     | Р         | Period                                 |

| Н                               | High                     | R         | Rise                                   |

| 1                               | Invalid (Hi-impedance)   | V         | Valid                                  |

| L                               | Low                      | Z         | Hi-impedance                           |

| I <sup>2</sup> C only           |                          |           |                                        |

| AA                              | output access            | High      | High                                   |

| BUF                             | Bus free                 | Low       | Low                                    |

| Tcc:st (I <sup>2</sup> C specif | cations only)            |           |                                        |

| CC                              |                          |           |                                        |

| HD                              | Hold                     | SU        | Setup                                  |

| ST                              |                          |           |                                        |

| DAT                             | DATA input hold          | STO       | STOP condition                         |

| STA                             | START condition          |           |                                        |

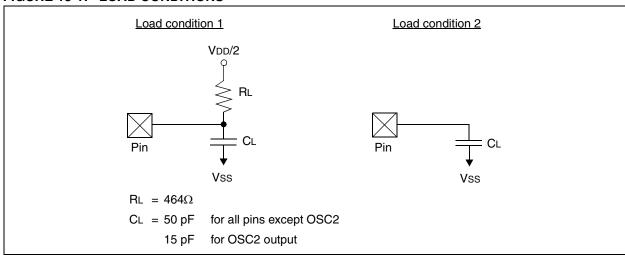

#### FIGURE 13-1: LOAD CONDITIONS

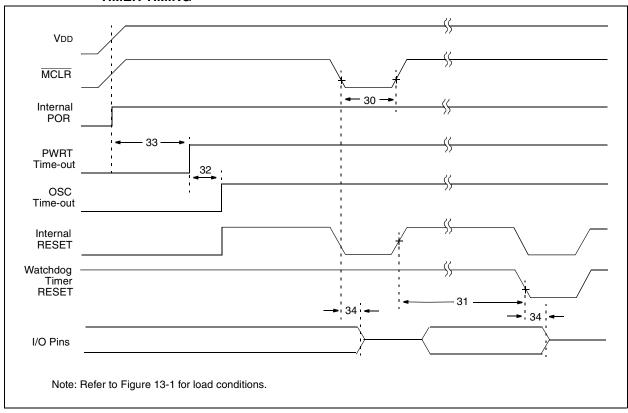

FIGURE 13-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

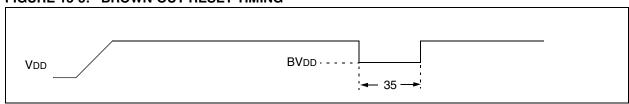

FIGURE 13-5: BROWN-OUT RESET TIMING

TABLE 13-5 RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions                                         |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|----------------------------------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 2   | _        | _   | μS    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 31*              | Twdt  | Watchdog Timer Time-out Period (No Prescaler)          | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C                          |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | _   | _     | Tosc = OSC1 period                                 |

| 33*              | Tpwrt | Power-up Timer Period                                  | 28  | 72       | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 34               | Tioz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _        | 2.1 | μS    |                                                    |

| 35               | TBOR  | Brown-out Reset pulse width                            | 100 | _        | _   | μS    | VDD ≤ BVDD (D005)                                  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

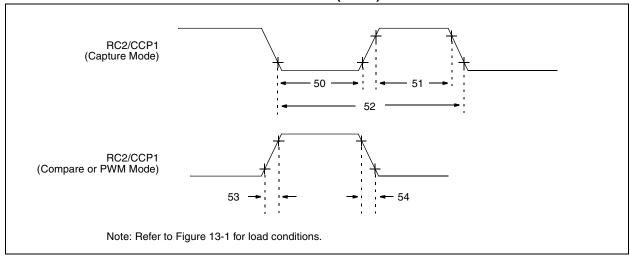

FIGURE 13-7: CAPTURE/COMPARE/PWM TIMINGS (CCP1)

TABLE 13-7 CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1)

| Param<br>No. | Sym  | Characteristic        |                |                                 | Min            | Тур† | Max | Units | Conditions                        |

|--------------|------|-----------------------|----------------|---------------------------------|----------------|------|-----|-------|-----------------------------------|

| 50*          | TccL | CCP1 input low time   | No Prescaler   |                                 | 0.5Tcy + 20    | _    | _   | ns    |                                   |

|              |      |                       | With Prescaler | PIC16 <b>C</b> 72/ <b>CR</b> 72 | 10             | _    | _   | ns    |                                   |

|              |      |                       |                | PIC16LC72/LCR72                 | 20             | _    | _   | ns    |                                   |

| 51*          | ТссН | CCP1 input high time  | No Prescaler   |                                 | 0.5Tcy + 20    | _    | _   | ns    |                                   |

|              |      |                       | With Prescaler | PIC16 <b>C</b> 72/ <b>CR</b> 72 | 10             | _    | _   | ns    |                                   |

|              |      |                       |                | PIC16LC72/LCR72                 | 20             | _    | _   | ns    |                                   |

| 52*          | TccP | CCP1 input period     |                |                                 | 3Tcy + 40<br>N | _    | _   | ns    | N = prescale<br>value (1,4 or 16) |

| 53*          | TccR | CCP1 output rise time |                | PIC16 <b>C</b> 72/ <b>CR</b> 72 | _              | 10   | 25  | ns    |                                   |

|              |      |                       |                | PIC16LC72/LCR72                 | _              | 25   | 45  | ns    |                                   |

| 54*          | TccF | CCP1 output fall time |                | PIC16 <b>C</b> 72/ <b>CR</b> 72 | _              | 10   | 25  | ns    |                                   |

|              |      |                       |                | PIC16LC72/LCR72                 | _              | 25   | 45  | ns    |                                   |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### TABLE 13-12 A/D CONVERTER CHARACTERISTICS:

PIC16C72/CR72-04 (Commercial, Industrial, Extended) PIC16C72/CR72-10 (Commercial, Industrial, Extended) PIC16C72/CR72-20 (Commercial, Industrial, Extended) PIC16LC72/LCR72-04 (Commercial, Industrial)

| Param<br>No. | Sym  | Char                             | acteristic                      | Min       | Тур†       | Max        | Units                                          | Conditions                                                                                        |

|--------------|------|----------------------------------|---------------------------------|-----------|------------|------------|------------------------------------------------|---------------------------------------------------------------------------------------------------|

| A01          | NR   | Resolution                       | _                               |           | 8 bits     | bit        | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$ |                                                                                                   |

| A02          | EABS | Total Absolute er                | ror                             | _         | _          | < ± 1      | LSb                                            | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF                                                          |

| A03          | EIL  | Integral linearity               | error                           | _         | _          | < ± 1      | LSb                                            | $VREF = VDD = 5.12V$ , $VSS \le VAIN \le VREF$                                                    |

| A04          | EDL  | Differential linearity error     |                                 | _         | _          | < ± 1      | LSb                                            | $VREF = VDD = 5.12V$ , $VSS \le VAIN \le VREF$                                                    |

| A05          | EFS  | Full scale error                 |                                 | _         | _          | < ± 1      | LSb                                            | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF                                                          |

| A06          | Eoff | Offset error                     |                                 | _         | _          | < ± 1      | LSb                                            | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                                                    |

| A10          |      | Monotonicity                     |                                 | _         | guaranteed | _          | _                                              | $Vss \leq Vain \leq Vref$                                                                         |

| A20          | VREF | Reference voltage                |                                 | 2.5V      |            | VDD + 0.3  | V                                              |                                                                                                   |

| A25          | Vain | Analog input voltage             |                                 | Vss - 0.3 | _          | VREF + 0.3 | V                                              |                                                                                                   |

| A30          | ZAIN | Recommended in analog voltage so | •                               | _         | _          | 10.0       | kΩ                                             |                                                                                                   |

| A40          | lad  | A/D conversion                   | PIC16 <b>C</b> 72/ <b>CR</b> 72 | _         | 180        | _          | μΑ                                             | Average current con-                                                                              |

|              |      | current (VDD) PIC16LC72/LCR72    |                                 | _         | 90         | _          | μΑ                                             | sumption when A/D is on. (Note 1)                                                                 |

| A50          | IREF | VREF input current (Note 2)      |                                 | 10        | _          | 1000       | μА                                             | During VAIN acquisition. Based on differential of VHOLD to VAIN to charge CHOLD, see Section 9.1. |

|              |      |                                  |                                 | _         | _          | 10         | μΑ                                             | During A/D Conversion cycle                                                                       |

<sup>\*</sup> These parameters are characterized but not tested.

The power-down current spec includes any such leakage from the A/D module.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current.

Note 2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

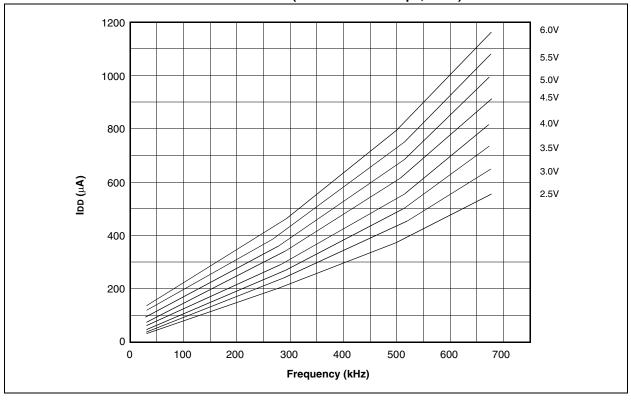

FIGURE 14-16: TYPICAL IDD vs. FREQUENCY (RC MODE @ 300 pF, 25°C)

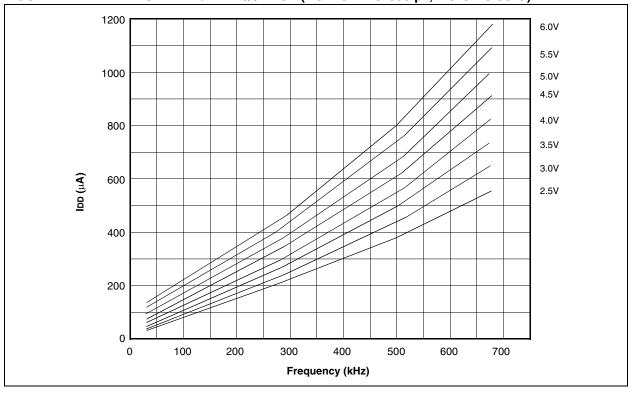

FIGURE 14-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

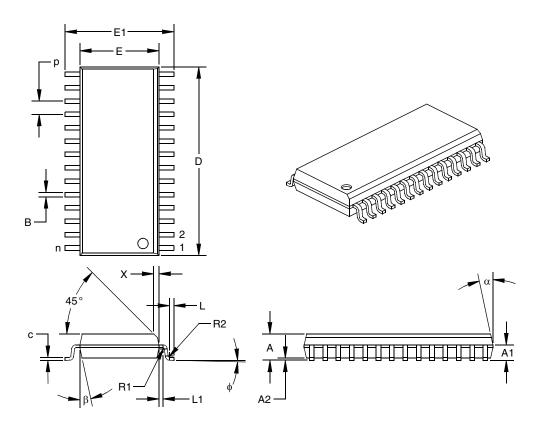

#### 16.4 28-Lead Plastic Surface Mount (SOIC - Wide, 300 mil Body) (SO)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                   |                |       | INCHES* |       | М     | ILLIMETER | S     |

|-------------------------|----------------|-------|---------|-------|-------|-----------|-------|

| Dimension Limits        |                | MIN   | MOM     | MAX   | MIN   | NOM       | MAX   |

| Pitch                   | р              |       | 0.050   |       |       | 1.27      |       |

| Number of Pins          | n              |       | 28      |       |       | 28        |       |

| Overall Pack. Height    | Α              | 0.093 | 0.099   | 0.104 | 2.36  | 2.50      | 2.64  |

| Shoulder Height         | A1             | 0.048 | 0.058   | 0.068 | 1.22  | 1.47      | 1.73  |

| Standoff                | A2             | 0.004 | 0.008   | 0.011 | 0.10  | 0.19      | 0.28  |

| Molded Package Length   | D <sup>‡</sup> | 0.700 | 0.706   | 0.712 | 17.78 | 17.93     | 18.08 |

| Molded Package Width    | E <sup>‡</sup> | 0.292 | 0.296   | 0.299 | 7.42  | 7.51      | 7.59  |

| Outside Dimension       | E1             | 0.394 | 0.407   | 0.419 | 10.01 | 10.33     | 10.64 |

| Chamfer Distance        | X              | 0.010 | 0.020   | 0.029 | 0.25  | 0.50      | 0.74  |

| Shoulder Radius         | R1             | 0.005 | 0.005   | 0.010 | 0.13  | 0.13      | 0.25  |

| Gull Wing Radius        | R2             | 0.005 | 0.005   | 0.010 | 0.13  | 0.13      | 0.25  |

| Foot Length             | L              | 0.011 | 0.016   | 0.021 | 0.28  | 0.41      | 0.53  |

| Foot Angle              | ф              | 0     | 4       | 8     | 0     | 4         | 8     |

| Radius Centerline       | L1             | 0.010 | 0.015   | 0.020 | 0.25  | 0.38      | 0.51  |

| Lead Thickness          | С              | 0.009 | 0.011   | 0.012 | 0.23  | 0.27      | 0.30  |

| Lower Lead Width        | Β <sup>†</sup> | 0.014 | 0.017   | 0.019 | 0.36  | 0.42      | 0.48  |

| Mold Draft Angle Top    | α              | 0     | 12      | 15    | 0     | 12        | 15    |

| Mold Draft Angle Bottom | β              | 0     | 12      | 15    | 0     | 12        | 15    |

<sup>\*</sup> Controlling Parameter.

<sup>&</sup>lt;sup>†</sup> Dimension "B" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B."

<sup>&</sup>lt;sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."

| Block Diagram                             | 47     | PCFG0 bit                             | 54     |

|-------------------------------------------|--------|---------------------------------------|--------|

| I <sup>2</sup> C Operation                |        | PCFG1 bit                             |        |

| Master Mode                               |        | PCFG2 bit                             |        |

| Mode                                      |        | PCL Register                          |        |

| Mode Selection                            |        | PCLATH                                |        |

|                                           |        |                                       |        |

| Multi-Master Mode                         |        | PCLATH Register                       |        |

| Reception                                 |        | PCON Register                         |        |

| Reception Timing Diagram                  |        | PD bit                                |        |

| SCL and SDA pins                          |        | PICDEM-1 Low-Cost PIC16/17 Demo Board |        |

| Slave Mode                                | 47     | PICDEM-2 Low-Cost PIC16CXX Demo Board |        |

| Transmission                              | 50     | PICMASTER™ RT In-Circuit Emulator     | 75     |

| In-Circuit Serial Programming             | 59, 72 | PICSTART™ Low-Cost Development System | 75     |

| INDF Register                             | 8, 17  | PIE1 Register                         | 12     |

| Indirect Addressing                       |        | Pin Functions                         |        |

| Initialization Condition for all Register |        | MCLR/Vpp                              |        |

| Instruction Format                        |        | OSC1/CLKIN                            |        |

| Instruction Set                           |        | OSC2/CLKOUT                           |        |

|                                           | 70     |                                       |        |

| Section                                   |        | RA0/AN0                               |        |

| Summary Table                             |        | RA1/AN1                               |        |

| INT Interrupt                             |        | RA2/AN2                               |        |

| INTCON Register                           |        | RA3/AN3/Vref                          |        |

| INTEDG bit                                | ,      | RA4/T0CKI                             |        |

| Internal Sampling Switch (Rss) Impedance  | 56     | RA5/AN4/SS                            |        |

| Interrupts                                | 59     | RB0/INT                               | 4      |

| PortB Change                              | 68     | RB1                                   | 2      |

| RB7:RB4 Port Change                       | 21     | RB2                                   |        |

| Section                                   |        | RB3                                   |        |

| TMR0                                      |        | RB4                                   |        |

| IRP bit                                   |        | RB5                                   |        |

| IIII DIL                                  | 9      |                                       |        |

| L                                         |        | RB6                                   |        |

| Loading of PC                             | 15     | RB7                                   |        |

| Loading of PC                             | 15     | RC0/T10S0/T1CKI                       |        |

| M                                         |        | RC1/T1OSI                             |        |

|                                           | 04.04  | RC2/CCP1                              |        |

| MCLR                                      | 61, 64 | RC3/SCK/SCL                           | 4      |

| Memory                                    |        | RC4/SDI/SDA                           | 4      |

| Data Memory                               | 6      | RC5/SDO                               | 4      |

| Program Memory                            | 5      | RC6                                   | 2      |

| Program Memory Maps                       |        | RC7                                   |        |

| PIC16C72                                  | 5      | SCK                                   |        |

| PIC16CR72                                 | 5      | SDI                                   |        |

| Register File Maps                        |        | SDO                                   |        |

| PIC16C72                                  | 6      | <u>SS</u>                             |        |

| PIC16CR72                                 |        |                                       |        |

| MPASM Assembler                           |        | Vdd                                   |        |

|                                           |        | Vss                                   | 4      |

| MPSIM Software Simulator                  | /5     | Pinout Descriptions                   |        |

| 0                                         |        | PIC16C72                              |        |

|                                           | 70     | PIC16CR72                             |        |

| OPCODE                                    |        | PIR1 Register                         | 13     |

| OPTION Register                           |        | POR                                   | 63, 64 |

| OSC selection                             | 59     | Oscillator Start-up Timer (OST)       |        |

| Oscillator                                |        | Power Control Register (PCON)         |        |

| HS                                        | 60, 64 | Power-on Reset (POR)                  |        |

| LP                                        | 60, 64 | Power-up Timer (PWRT)                 |        |

| RC                                        | · ·    | . , ,                                 |        |

| XT                                        |        | Power-Up-Timer (PWRT)                 |        |

| Oscillator Configurations                 | , -    | Time-out Sequence                     |        |

| Output of TMR2                            |        | TO                                    |        |

| Output of TWINZ                           |        | POR bit                               | 14, 64 |

| P                                         |        | Port RB Interrupt                     | 68     |

|                                           | 40.40  | PORTA                                 | 65     |

| P                                         | 40, 43 | PORTA Register                        | 7, 19  |

| Packaging                                 |        | PORTB                                 |        |

| 28-Lead Ceramic w/Window                  |        | PORTB Register                        |        |

| 28-Lead PDIP                              |        | PORTC                                 |        |

| 28-Lead SOIC                              | 112    | PORTC Register                        |        |

| 28-Lead SSOP                              | 113    | S .                                   |        |

| Paging, Program Memory                    |        | Power-down Mode (SLEEP)               | /      |

| ,                                         | -      |                                       |        |