Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc72-04i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

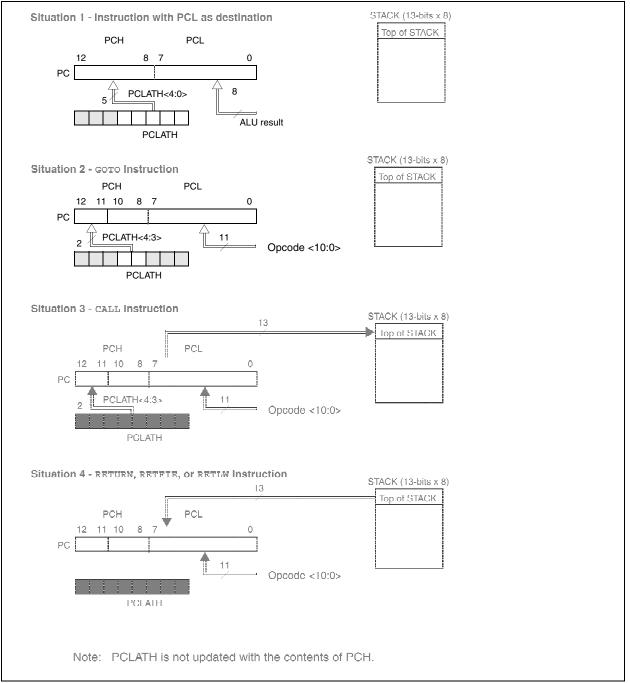

#### 2.3 PCL and PCLATH

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly readable or writable. All updates to the PCH register go through the PCLATH register.

Figure 2-9 shows the four situations for the loading of the PC. Example 1 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). Example 2 shows how the PC is loaded during a GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH). Example 3 shows how the PC is loaded during a CALL instruction (PCLATH<4:3>  $\rightarrow$ PCH), with the PC loaded (PUSHed) onto the Top of Stack. Finally, example 4 shows how the PC is loaded during one of the return instructions where the PC is loaded (POPed) from the Top of Stack.

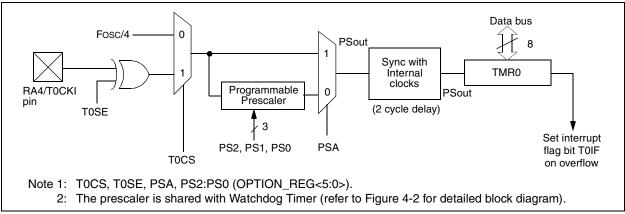

### 4.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- Internal or external clock select

- Edge select for external clock

- 8-bit software programmable prescaler

- Interrupt on overflow from FFh to 00h

Figure 4-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range MCU Reference Manual, DS33023.

#### 4.1 <u>Timer0 Operation</u>

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the PIC<sup>®</sup> Mid-Range MCU Reference Manual, DS33023.

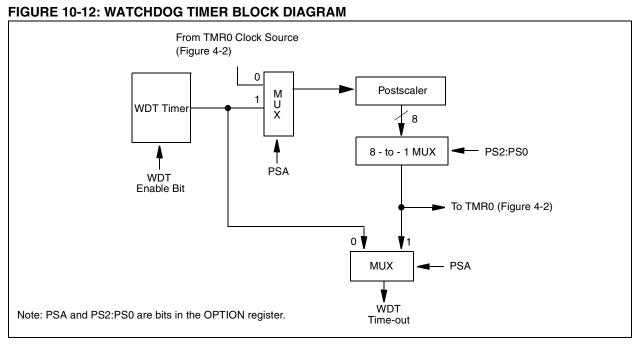

#### 4.2 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 4-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

#### FIGURE 4-1: TIMER0 BLOCK DIAGRAM

#### 5.2 <u>Timer1 Oscillator</u>

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 5-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

TABLE 5-1CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type         | e Freq                                                                                                                                            | C1                    | C2           |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|--|--|

| LP               | 32 kHz                                                                                                                                            | 33 pF                 | 33 pF        |  |  |

|                  | 100 kHz                                                                                                                                           | 15 pF                 | 15 pF        |  |  |

|                  | 200 kHz                                                                                                                                           | 15 pF                 | 15 pF        |  |  |

| These            | values are for                                                                                                                                    | design guidar         | ice only.    |  |  |

| Crystals Tested: |                                                                                                                                                   |                       |              |  |  |

| 32.768 kH        | z Epson C-00                                                                                                                                      | Epson C-001R32.768K-A |              |  |  |

| 100 kHz          | Epson C-2 1                                                                                                                                       | 00.00 KC-P            | $\pm$ 20 PPM |  |  |

| 200 kHz          | STD XTL 20                                                                                                                                        | 0.000 kHz             | $\pm$ 20 PPM |  |  |

| 0                | of oscillator but also increases the start-up                                                                                                     |                       |              |  |  |

| 2: S             | time.<br>Since each resonator/crystal has its own<br>characteristics, the user should consult the<br>resonator/crystal manufacturer for appropri- |                       |              |  |  |

ate values of external components.

#### 5.3 <u>Timer1 Interrupt</u>

The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

#### 5.4 <u>Resetting Timer1 using a CCP Trigger</u> <u>Output</u>

If the CCP module is configured in compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The special event triggers from the CCP1 |      |     |     |           |      |     |

|-------|------------------------------------------|------|-----|-----|-----------|------|-----|

|       | module                                   | will | not | set | interrupt | flag | bit |

|       | TMR1IF (PIR1<0>).                        |      |     |     |           |      |     |

Timer1 must be configured for either timer or synchronized counter mode to take advantage of this feature. If Timer1 is running in asynchronous counter mode, this reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer1.

### TABLE 5-2 REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address | Name   | Bit 7                                                                         | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|-------------------------------------------------------------------------------|-------|---------|---------|---------|--------|--------|-----------|--------------------------|---------------------------------|

| 0Bh,8Bh | INTCON | GIE                                                                           | PEIE  | TOIE    | INTE    | RBIE    | TOIF   | INTF   | RBIF      | 0000 000x                | 0000 000u                       |

| 0Ch     | PIR1   | (1)                                                                           | ADIF  | (1)     | (1)     | SSPIF   | CCP1IF | TMR2IF | TMR1IF    | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1   | (1)                                                                           | ADIE  | (1)     | (1)     | SSPIE   | CCP1IE | TMR2IE | TMR1IE    | 0000 0000                | 0000 0000                       |

| 0Eh     | TMR1L  | L Holding register for the Least Significant Byte of the 16-bit TMR1 register |       |         |         |         |        |        | xxxx xxxx | uuuu uuuu                |                                 |

| 0Fh     | TMR1H  | Holding register for the Most Significant Byte of the 16-bit TMR1 register    |       |         |         |         |        |        | xxxx xxxx | uuuu uuuu                |                                 |

| 10h     | T1CON  | _                                                                             | _     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR1ON    | 00 0000                  | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module. Note 1: These bits are unimplemented, read as '0'.

### 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Table 7-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

#### FIGURE 7-1: CCP1CON REGISTER (ADDRESS 17h)

Additional information on the CCP module is available in the  $PIC^{\textcircled{R}}$  Mid-Range MCU Reference Manual, DS33023.

# TABLE 7-1CCP MODE - TIMER<br/>RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

| U-0      | U-0                                                                                                                                                                                                 | R/W-0                                                                                             | R/W-0                                                                                                                                                    | R/W-0                                                                                                       | R/W-0                                                                                                            | R/W-0                                        | R/W-0                   |                                                                     |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------|---------------------------------------------------------------------|

|          | _                                                                                                                                                                                                   | CCP1X                                                                                             | CCP1Y                                                                                                                                                    | CCP1M3                                                                                                      | CCP1M2                                                                                                           | CCP1M1                                       | CCP1M0                  | R = Readable bit                                                    |

| bit7     |                                                                                                                                                                                                     |                                                                                                   |                                                                                                                                                          |                                                                                                             |                                                                                                                  |                                              | bit0                    | W = Writable bit<br>U = Unimplemented bit, read                     |

|          |                                                                                                                                                                                                     |                                                                                                   |                                                                                                                                                          |                                                                                                             |                                                                                                                  |                                              |                         | as '0'                                                              |

|          |                                                                                                                                                                                                     |                                                                                                   |                                                                                                                                                          |                                                                                                             |                                                                                                                  |                                              |                         | - n =Value at POR reset                                             |

| bit 7-6: | Unim                                                                                                                                                                                                | plemente                                                                                          | d: Read as                                                                                                                                               | s '0'                                                                                                       |                                                                                                                  |                                              |                         |                                                                     |

| bit 5-4: | <b>CCP1X:CCP1Y</b> : PWM Least Significant bits<br>Capture Mode: Unused<br>Compare Mode: Unused<br>PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR1L. |                                                                                                   |                                                                                                                                                          |                                                                                                             |                                                                                                                  |                                              |                         |                                                                     |

| bit 3-0: | 0000<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1010<br>1011                                                                                                                                | = Capture<br>= Capture<br>= Capture<br>= Capture<br>= Capture<br>= Compai<br>= Compai<br>= Compai | e/Compare<br>e mode, ev<br>e mode, ev<br>e mode, ev<br>e mode, ev<br>re mode, s<br>re mode, c<br>re mode, c<br>re mode, d<br>re mode, t<br>ision (if A/D | ery falling e<br>ery rising e<br>ery 4th risin<br>ery 16th ris<br>et output o<br>lear output<br>enerate sof | resets CCP<br>edge<br>dge<br>ing edge<br>ing edge<br>n match (CC<br>on match (CC<br>tware intern<br>ial event (C | CP1IF bit is<br>CCP1IF bit i<br>upt on matcl | is set)<br>h (CCP1IF bi | it is set, CCP1 pin is unaffected)<br>resets TMR1 and starts an A/D |

#### 8.4.1.1 ADDRESSING

Once the SSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) - on the falling edge of the ninth SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address the first byte would equal

'1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive repeated START condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

|    | us Bits as Data<br>sfer is Received |                    |                       | Set bit SSPIF                        |  |  |

|----|-------------------------------------|--------------------|-----------------------|--------------------------------------|--|--|

| BF | SSPOV                               | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | (SSP Interrupt occurs<br>if enabled) |  |  |

| 0  | 0                                   | Yes                | Yes                   | Yes                                  |  |  |

| 1  | 0                                   | No                 | No                    | Yes                                  |  |  |

| 1  | 1                                   | No                 | No                    | Yes                                  |  |  |

| 0  | 1                                   | No                 | No                    | Yes                                  |  |  |

#### 8.4.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

#### FIGURE 8-8: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address         R/W           SDA         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | =0Receiving Data<br>                        |                                        |            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------|------------|

| SSPIF (PIR1<3>)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Cleared in software                         | <br>                                   | Bus Master |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             | <u>+</u><br>Ⅰ                          | terminates |

| BF (SSPSTAT<0>)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>SSPBUF register is read</li> </ul> |                                        |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |                                        |            |

| SSPOV (SSPCON<6>)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                             |                                        |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bit SSPOV is set be                         | ecause the SSPBUF register is still fu | ill. 📥 🛛   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             | ACK is not se                          | ent.       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |                                        |            |

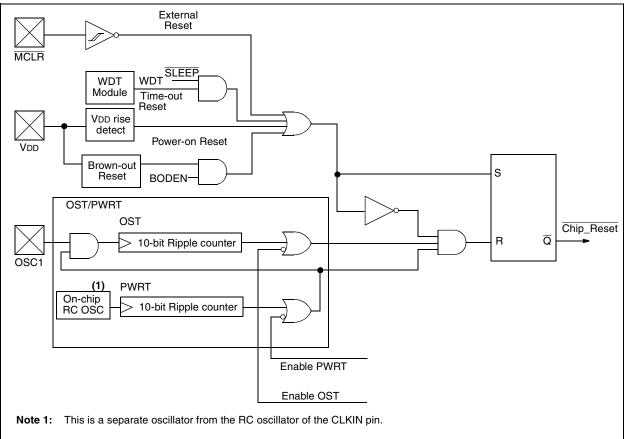

#### FIGURE 10-5: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| Register | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or Inter-<br>rupt |

|----------|------------------------------------|--------------------------|-----------------------------------|

| W        | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                         |

| INDF     | N/A                                | N/A                      | N/A                               |

| TMR0     | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                         |

| PCL      | 0000h                              | 0000h                    | PC + 1 <b>(2)</b>                 |

| STATUS   | 0001 1xxx                          | 000q quuu <sup>(3)</sup> | uuuq quuu <sup>(3)</sup>          |

| FSR      | xxxx xxxx                          | uuuu uuuu                | นนนน นนนน                         |

| PORTA    | 0x 0000                            | 0u 0000                  | uu uuuu                           |

| PORTB    | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                         |

| PORTC    | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                         |

| PCLATH   | 0 0000                             | 0 0000                   | u uuuu                            |

| INTCON   | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>              |

| PIR1     | -0 0000                            | -0 0000                  | -u uuuu <b>(1)</b>                |

| TMR1L    | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                         |

| TMR1H    | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                         |

| T1CON    | 00 0000                            | uu uuuu                  | uu uuuu                           |

| TMR2     | 0000 0000                          | 0000 0000                | uuuu uuuu                         |

| T2CON    | -000 0000                          | -000 0000                | -uuu uuuu                         |

| SSPBUF   | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                         |

| SSPCON   | 0000 0000                          | 0000 0000                | uuuu uuuu                         |

| CCPR1L   | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                         |

| CCPR1H   | XXXX XXXX                          | uuuu uuuu                | սսսս սսսս                         |

| CCP1CON  | 00 0000                            | 00 0000                  | uu uuuu                           |

| ADRES    | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                         |

| ADCON0   | 0000 00-0                          | 0000 00-0                | uuuu uu-u                         |

| OPTION   | 1111 1111                          | 1111 1111                | uuuu uuuu                         |

| TRISA    | 11 1111                            | 11 1111                  | uu uuuu                           |

| TRISB    | 1111 1111                          | 1111 1111                | uuuu uuuu                         |

| TRISC    | 1111 1111                          | 1111 1111                | uuuu uuuu                         |

| PIE1     | -0 0000                            | -0 0000                  | -u uuuu                           |

| PCON     | 0u                                 | uu                       | uu                                |

| PR2      | 1111 1111                          | 1111 1111                | 1111 1111                         |

| SSPADD   | 0000 0000                          | 0000 0000                | นนนน นนนน                         |

| SSPSTAT  | 00 0000                            | 00 0000                  | uu uuuu                           |

| ADCON1   | 000                                | 000                      | uuu                               |

TABLE 10-6INITIALIZATION CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition **Note 1:** One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 10-5 for reset value for specific condition.

#### 10.12 Watchdog Timer (WDT)

The Watchdog Timer is as a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTE (Section 10.1).

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

Note: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

**Note:** When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

#### FIGURE 10-13: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION       | RBPU  | INTEDG               | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 10-1 for operation of these bits.

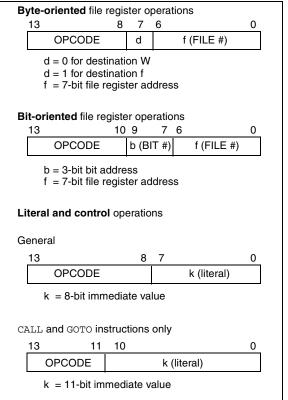

## 11.0 INSTRUCTION SET SUMMARY

Each PIC16CXXX family instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXXX family instruction set summary in Table 11-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 11-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

# TABLE 11-1OPCODE FIELD<br/>DESCRIPTIONS

| Field | Description                                                                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                        |

| W     | Working register (accumulator)                                                                                                                                              |

| b     | Bit address within an 8-bit file register                                                                                                                                   |

| k     | Literal field, constant data or label                                                                                                                                       |

| x     | Don't care location (= 0 or 1)<br>The assembler will generate code with x = 0. It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                |

| PC    | Program Counter                                                                                                                                                             |

| TO    | Time-out bit                                                                                                                                                                |

| PD    | Power-down bit                                                                                                                                                              |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- **Bit-oriented** operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Table 11-2 lists the instructions recognized by the MPASM assembler.

Figure 11-1 shows the general formats that the instructions can have.

| Note: | То   | maintain  | upward   | compatibility         | with |

|-------|------|-----------|----------|-----------------------|------|

|       | futu | re PIC160 | CXXX pro | oducts, <u>do not</u> | use  |

|       | the  | OPTION a  | nd TRIS  | instructions.         |      |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

#### FIGURE 11-1: GENERAL FORMAT FOR INSTRUCTIONS

A description of each instruction is available in the  $PIC^{\mathbb{R}}$ Mid-Range MCU Family Reference Manual, DS33023.

#### TABLE 11-2 PIC16CXXX INSTRUCTION SET

| Mnemo  |      | Description                  | Cycles  |        | 14-Bit | Opcode | )    | Status   | Notes |

|--------|------|------------------------------|---------|--------|--------|--------|------|----------|-------|

| Operan | nds  |                              |         | MSb    | MSb LS |        | LSb  | Affected |       |

|        |      | BYTE-ORIENTED FILE REGIS     | TER OPE | RATIC  | ONS    |        |      |          |       |

| ADDWF  | f, d | Add W and f                  | 1       | 00     | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF  | f, d | AND W with f                 | 1       | 00     | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF   | f    | Clear f                      | 1       | 00     | 0001   | lfff   | ffff | Z        | 2     |

| CLRW   | -    | Clear W                      | 1       | 00     | 0001   | 0xxx   | xxxx | Z        |       |

| COMF   | f, d | Complement f                 | 1       | 00     | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF   | f, d | Decrement f                  | 1       | 00     | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ | f, d | Decrement f, Skip if 0       | 1(2)    | 00     | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF   | f, d | Increment f                  | 1       | 00     | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ | f, d | Increment f, Skip if 0       | 1(2)    | 00     | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF  | f, d | Inclusive OR W with f        | 1       | 00     | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF   | f, d | Move f                       | 1       | 00     | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF  | f    | Move W to f                  | 1       | 00     | 0000   | lfff   | ffff |          |       |

| NOP    | -    | No Operation                 | 1       | 00     | 0000   | 0xx0   | 0000 |          |       |

| RLF    | f, d | Rotate Left f through Carry  | 1       | 00     | 1101   | dfff   | ffff | С        | 1,2   |

| RRF    | f, d | Rotate Right f through Carry | 1       | 00     | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF  | f, d | Subtract W from f            | 1       | 00     | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF  | f, d | Swap nibbles in f            | 1       | 00     | 1110   | dfff   | ffff |          | 1,2   |

| XORWF  | f, d | Exclusive OR W with f        | 1       | 00     | 0110   | dfff   | ffff | Z        | 1,2   |

|        |      | BIT-ORIENTED FILE REGIST     | ER OPER | RATION | IS     |        |      |          |       |

| BCF    | f, b | Bit Clear f                  | 1       | 01     | 00bb   | bfff   | ffff |          | 1,2   |

| BSF    | f, b | Bit Set f                    | 1       | 01     | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC  | f, b | Bit Test f, Skip if Clear    | 1 (2)   | 01     | 10bb   | bfff   | ffff |          | 3     |

| BTFSS  | f, b | Bit Test f, Skip if Set      | 1 (2)   | 01     | 11bb   | bfff   | ffff |          | 3     |

|        |      | LITERAL AND CONTROL          | OPERAT  | IONS   |        |        |      |          |       |

| ADDLW  | k    | Add literal and W            | 1       | 11     | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW  | k    | AND literal with W           | 1       | 11     | 1001   | kkkk   | kkkk | Z        |       |

| CALL   | k    | Call subroutine              | 2       | 10     | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT | -    | Clear Watchdog Timer         | 1       | 00     | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO   | k    | Go to address                | 2       | 10     | 1kkk   | kkkk   | kkkk |          |       |

| IORLW  | k    | Inclusive OR literal with W  | 1       | 11     | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW  | k    | Move literal to W            | 1       | 11     | 00xx   | kkkk   | kkkk |          |       |

| RETFIE | -    | Return from interrupt        | 2       | 00     | 0000   | 0000   | 1001 |          |       |

| RETLW  | k    | Return with literal in W     | 2       | 11     | 01xx   | kkkk   | kkkk |          |       |

| RETURN | -    | Return from Subroutine       | 2       | 00     | 0000   | 0000   | 1000 |          |       |

| SLEEP  | -    | Go into standby mode         | 1       | 00     | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW  | k    | Subtract W from literal      | 1       | 11     | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| XORLW  | k    | Exclusive OR literal with W  | 1       | 11     | 1010   | kkkk   | kkkk | Z        |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

### 13.0 ELECTRICAL CHARACTERISTICS - PIC16C72 SERIES

#### Absolute Maximum Ratings †

| Parameter                                                                               | PIC16C72              | PIC16CR72             |

|-----------------------------------------------------------------------------------------|-----------------------|-----------------------|

| Ambient temperature under bias                                                          | -55 to +125°C         | -55 to +125°C         |

| Storage temperature                                                                     | -65°C to +150°C       | -65°C to +150°C       |

| Voltage on any pin with respect to VSS (except VDD, $\overline{\text{MCLR}}$ , and RA4) | -0.3V to (VDD + 0.3V) | -0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to VSS                                                      | -0.3 to +7.5V         | TBD                   |

| Voltage on MCLR with respect to Vss (Note 1)                                            | -0.3 to +14V          | TBD                   |

| Voltage on RA4 with respect to Vss                                                      | -0.3 to +14V          | TBD                   |

| Total power dissipation (Note 2)                                                        | 1.0W                  | 1.0W                  |

| Maximum current out of Vss pin                                                          | 300 mA                | 300 mA                |

| Maximum current into VDD pin                                                            | 250 mA                | 250 mA                |

| Input clamp current, Iık (Vı < 0 or Vı > VDD)                                           | ± 20 mA               | $\pm$ 20 mA           |

| Output clamp current, IOK (Vo < 0 or Vo > VDD)                                          | ± 20 mA               | ± 20 mA               |

| Maximum output current sunk by any I/O pin                                              | 25 mA                 | 25 mA                 |

| Maximum output current sourced by any I/O pin                                           | 25 mA                 | 25 mA                 |

| Maximum current sunk by PORTA and PORTB (combined)                                      | 200 mA                | 200 mA                |

| Maximum current sourced by PORTA and PORTB (combined)                                   | 200 mA                | 200 mA                |

| Maximum current sunk by PORTC                                                           | 200 mA                | 200 mA                |

| Maximum current sourced by PORTC                                                        | 200 mA                | 200 mA                |

Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

2. Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\Sigma$  IOH} +  $\Sigma$  {(VDD - VOH) x IOH} +  $\Sigma$ (VOI x IOL).

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| DC CHAR      | ACTERISTICS                                      |                     |           | ure -40<br>-40 | D°C <sup>`</sup> ≤ TA<br>D°C <sup>°</sup> ≤ TA | ≤ +125°<br>≤ +85°0 | vise stated)<br><sup>2</sup> C for extended,<br>C for industrial and    |

|--------------|--------------------------------------------------|---------------------|-----------|----------------|------------------------------------------------|--------------------|-------------------------------------------------------------------------|

|              |                                                  | Operatin<br>Section | 0 0       |                |                                                |                    | C for commercial<br>DC spec Section 13.1 and                            |

| Param<br>No. | Characteristic Sym Min Typt Max Units Conditions |                     |           |                |                                                |                    | Conditions                                                              |

|              | Output High Voltage                              |                     |           |                |                                                |                    |                                                                         |

| D090         | I/O ports (Note 3)                               | Voн                 | Vdd - 0.7 | -              | -                                              | V                  | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                            |

| D090A        |                                                  |                     | Vdd - 0.7 | -              | -                                              | V                  | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                           |

| D092         | OSC2/CLKOUT (RC osc config)                      |                     | Vdd - 0.7 | -              | -                                              | V                  | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |

| D092A        |                                                  |                     | Vdd - 0.7 | -              | -                                              | V                  | IOH = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                           |

| D150*        | Open-Drain High Voltage                          | Vod                 | -         | -              | 14                                             | V                  | RA4 pin, PIC16 <b>C</b> 72/ <b>LC</b> 72                                |

|              |                                                  |                     | -         | -              | TBD                                            | V                  | RA4 pin, PIC16 <b>CR</b> 72/ <b>LCR</b> 72                              |

|              | Capacitive Loading Specs on Output<br>Pins       |                     |           |                |                                                |                    |                                                                         |

| D100         | OSC2 pin                                         | COSC2               | -         | -              | 15                                             | pF                 | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |

| D101         | All I/O pins and OSC2 (in RC mode)               | Сю                  | -         | -              | 50                                             | pF                 |                                                                         |

| D102         | SCL, SDA in I <sup>2</sup> C mode                | Cb                  | -         | -              | 400                                            | pF                 |                                                                         |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

**Note 2:** The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

Note 3: Negative current is defined as current sourced by the pin.

NOTES:

# PIC16C72 Series PIC16C72

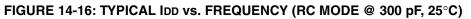

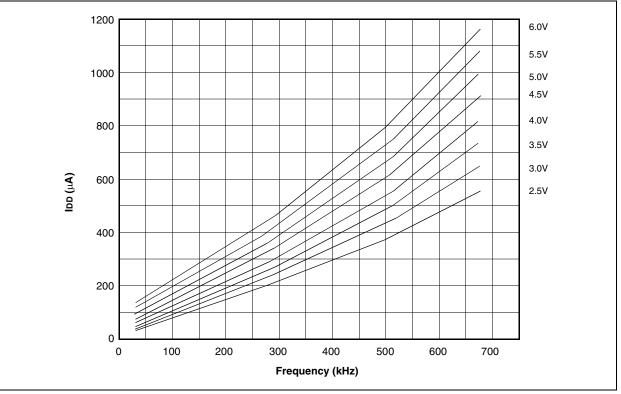

FIGURE 14-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

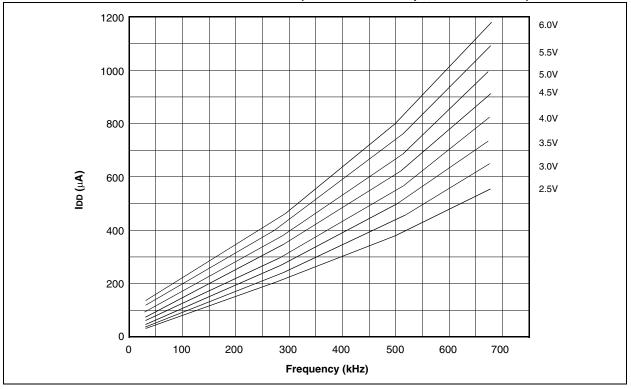

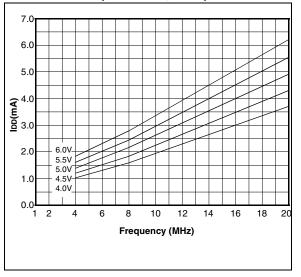

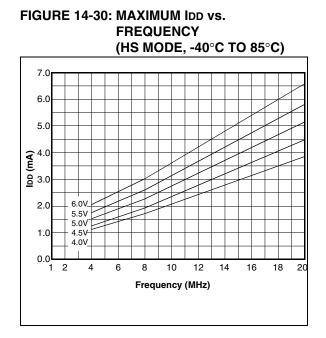

#### FIGURE 14-29: TYPICAL IDD vs. FREQUENCY (HS MODE, 25°C)

#### TABLE 14-3 TYPICAL EPROM ERASE TIME RECOMMENDATIONS

| Process<br>Technology | Wavelength<br>(Angstroms) | Intensity (μW/<br>cm2) | Distance from UV lamp<br>(inches) | Typical Time <sup>(1)</sup><br>(minutes) |

|-----------------------|---------------------------|------------------------|-----------------------------------|------------------------------------------|

| 57K                   | 2537                      | 12,000                 | 1                                 | 15 - 20                                  |

| 77K                   | 2537                      | 12,000                 | 1                                 | 20                                       |

| 90K                   | 2537                      | 12,000                 | 1                                 | 40                                       |

| 120K                  | 2537                      | 12,000                 | 1                                 | 60                                       |

Note 1: If these criteria are not met, the erase times will be different.

**Note:** Fluorescent lights and sunlight both emit ultraviolet light at the erasure wavelength. Leaving a UV erasable device's window uncovered could cause, over time, the devices memory cells to become erased. The erasure time for a fluorescent light is about three years. While sunlight requires only about one week. To prevent the memory cells from losing data an opaque label should be placed over the erasure window.

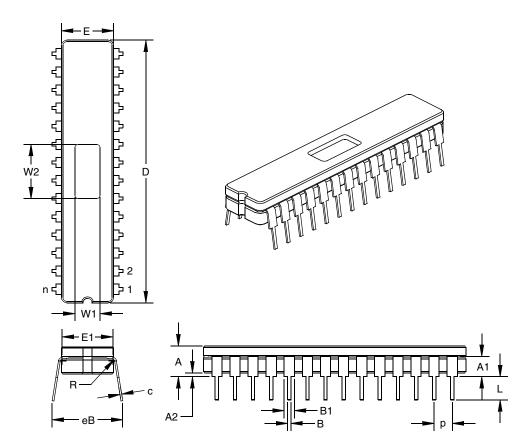

#### 16.2 <u>28-Lead Ceramic Side Brazed Dual In-Line with Window (300 mil)(JW)</u>

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                        |    |       | INCHES* |       | М     | MILLIMETERS |       |  |

|------------------------------|----|-------|---------|-------|-------|-------------|-------|--|

| Dimension Limits             |    | MIN   | NOM     | MAX   | MIN   | NOM         | MAX   |  |

| PCB Row Spacing              |    |       | 0.300   |       |       | 7.62        |       |  |

| Number of Pins               | n  |       | 28      |       |       | 28          |       |  |

| Pitch                        | р  | 0.098 | 0.100   | 0.102 | 2.49  | 2.54        | 2.59  |  |

| Lower Lead Width             | В  | 0.016 | 0.019   | 0.021 | 0.41  | 0.47        | 0.53  |  |

| Upper Lead Width             | B1 | 0.050 | 0.058   | 0.065 | 1.27  | 1.46        | 1.65  |  |

| Shoulder Radius              | R  | 0.010 | 0.013   | 0.015 | 0.25  | 0.32        | 0.38  |  |

| Lead Thickness               | С  | 0.008 | 0.010   | 0.012 | 0.20  | 0.25        | 0.30  |  |

| Top to Seating Plane         | А  | 0.170 | 0.183   | 0.195 | 4.32  | 4.64        | 4.95  |  |

| Top of Lead to Seating Plane | A1 | 0.107 | 0.125   | 0.143 | 2.72  | 3.18        | 3.63  |  |

| Base to Seating Plane        | A2 | 0.015 | 0.023   | 0.030 | 0.00  | 0.57        | 0.76  |  |

| Tip to Seating Plane         | L  | 0.135 | 0.140   | 0.145 | 3.43  | 3.56        | 3.68  |  |

| Package Length               | D  | 1.430 | 1.458   | 1.485 | 36.32 | 37.02       | 37.72 |  |

| Package Width                | Е  | 0.285 | 0.290   | 0.295 | 7.24  | 7.37        | 7.49  |  |

| Radius to Radius Width       | E1 | 0.255 | 0.270   | 0.285 | 6.48  | 6.86        | 7.24  |  |

| Overall Row Spacing          | eB | 0.345 | 0.385   | 0.425 | 8.76  | 9.78        | 10.80 |  |

| Window Width                 | W1 | 0.130 | 0.140   | 0.150 | 0.13  | 0.14        | 0.15  |  |

| Window Length                | W2 | 0.290 | 0.300   | 0.310 | 0.29  | 0.3         | 0.31  |  |

\* Controlling Parameter.

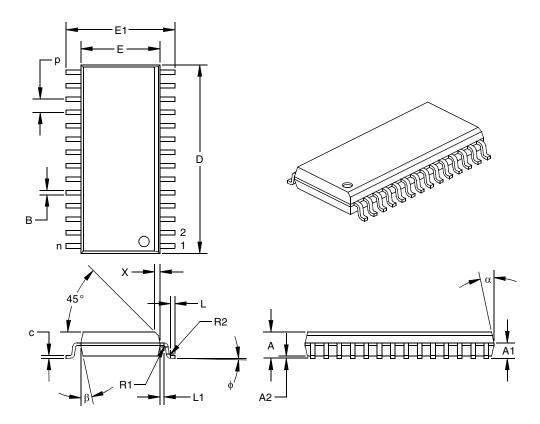

#### 16.4 <u>28-Lead Plastic Surface Mount (SOIC - Wide, 300 mil Body) (SO)</u>

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                   |                |       | INCHES* |       | М     | MILLIMETERS |       |  |

|-------------------------|----------------|-------|---------|-------|-------|-------------|-------|--|

| Dimension Limits        |                | MIN   | NOM     | MAX   | MIN   | NOM         | MAX   |  |

| Pitch                   | р              |       | 0.050   |       |       | 1.27        |       |  |

| Number of Pins          | n              |       | 28      |       |       | 28          |       |  |

| Overall Pack. Height    | А              | 0.093 | 0.099   | 0.104 | 2.36  | 2.50        | 2.64  |  |

| Shoulder Height         | A1             | 0.048 | 0.058   | 0.068 | 1.22  | 1.47        | 1.73  |  |

| Standoff                | A2             | 0.004 | 0.008   | 0.011 | 0.10  | 0.19        | 0.28  |  |

| Molded Package Length   | D <sup>‡</sup> | 0.700 | 0.706   | 0.712 | 17.78 | 17.93       | 18.08 |  |

| Molded Package Width    | E‡             | 0.292 | 0.296   | 0.299 | 7.42  | 7.51        | 7.59  |  |

| Outside Dimension       | E1             | 0.394 | 0.407   | 0.419 | 10.01 | 10.33       | 10.64 |  |

| Chamfer Distance        | Х              | 0.010 | 0.020   | 0.029 | 0.25  | 0.50        | 0.74  |  |

| Shoulder Radius         | R1             | 0.005 | 0.005   | 0.010 | 0.13  | 0.13        | 0.25  |  |

| Gull Wing Radius        | R2             | 0.005 | 0.005   | 0.010 | 0.13  | 0.13        | 0.25  |  |

| Foot Length             | L              | 0.011 | 0.016   | 0.021 | 0.28  | 0.41        | 0.53  |  |

| Foot Angle              | φ              | 0     | 4       | 8     | 0     | 4           | 8     |  |

| Radius Centerline       | L1             | 0.010 | 0.015   | 0.020 | 0.25  | 0.38        | 0.51  |  |

| Lead Thickness          | С              | 0.009 | 0.011   | 0.012 | 0.23  | 0.27        | 0.30  |  |

| Lower Lead Width        | B <sup>†</sup> | 0.014 | 0.017   | 0.019 | 0.36  | 0.42        | 0.48  |  |

| Mold Draft Angle Top    | α              | 0     | 12      | 15    | 0     | 12          | 15    |  |

| Mold Draft Angle Bottom | β              | 0     | 12      | 15    | 0     | 12          | 15    |  |

<sup>\*</sup> Controlling Parameter.

<sup>†</sup> Dimension "B" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B."

<sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."

## INDEX

# **A**

| A/D                                           |                            |

|-----------------------------------------------|----------------------------|

| ADCON0 Register                               | 3                          |

| ADCON1 Register54                             | 4                          |

| ADIF bit55                                    | 5                          |

| Analog Input Model Block Diagram              | 6                          |

| Analog-to-Digital Converter                   | 3                          |

| Block Diagram                                 | 5                          |

| Configuring Analog Port Pins57                | 7                          |

| Configuring the Interrupt55                   | 5                          |

| Configuring the Module55                      |                            |

| Conversion Clock                              |                            |

| Conversions                                   | 8                          |

| Converter Characteristics94                   | 4                          |

| GO/DONE bit58                                 | 5                          |

| Internal Sampling Switch (Rss) Impedance56    |                            |

| Sampling Requirements                         |                            |

| Source Impedance                              |                            |

| Using the CCP Trigger58                       |                            |

| Absolute Maximum Ratings77                    |                            |

| ACK                                           |                            |

| ADIE bit                                      |                            |

| ADIF bit                                      |                            |

| ADRES Register                                |                            |

| Application Notes                             | Č                          |

| AN546 (Using the Analog-to-Digital Converter) | 3                          |

| AN578 (Use of the SSP Module in the $I^2C$    | -                          |

| Multi-Master Environment)                     | 9                          |

|                                               | Č                          |

| B                                             |                            |

| -                                             |                            |

| -                                             | 7                          |

| BF                                            | 7                          |

| BF                                            |                            |

| BF                                            | 5                          |

| BF                                            | 5<br>6                     |

| BF                                            | 5<br>6<br>4                |

| BF                                            | 5<br>6<br>4<br>5           |

| BF                                            | 5<br>6<br>4<br>5<br>7      |

| BF                                            | 5<br>6<br>4<br>5<br>7<br>2 |

| BF                                            | 5645723                    |

| BF                                            | 56457233                   |

| BF                                            | 564572333                  |

| BF                                            | 5645723336                 |

| BF                                            | 56457233369                |

| BF                                            | 564572333699               |

| BF                                            | 5645723336991              |

| BF                                            | 56457233369911             |

| BF                                            | 564572333699117            |

| BF                                            | 5645723336991175           |

| BF                                            | 56457233369911755          |

| BF                                            | 564572333699117556         |

| BF                                            | 5645723336991175561        |

| BF                                            | 56457233369911755610       |

| BF                                            | 564572333699117556104      |

| BF                                            | 564572333699117556104      |

| C bit       |                | 9 |

|-------------|----------------|---|

| Capture/Com | ipare/PWM      |   |

| Capture     |                |   |

| Blo         | ock Diagram    |   |

| CC          | P1CON Register |   |

| CC          | P1IF           |   |

| CC          | PR1            |   |

| CC          | PR1H:CCPR1L    |   |

|             |                |   |

# **PIC16C72 Series**

| Mode                                      | 4 |

|-------------------------------------------|---|

| Prescaler                                 | 4 |

| CCP Timer Resources                       | 3 |

| Compare                                   |   |

| Block Diagram                             | 5 |

| Mode                                      |   |

| Software Interrupt Mode                   |   |

| Special Event Trigger                     |   |

| Special Trigger Output of CCP1            |   |

| Special Trigger Output of CCP2            |   |

| Section                                   |   |

| Special Event Trigger and A/D Conversions |   |

| Capture/Compare/PWM (CCP)                 | 5 |

| PWM Block Diagram                         | 6 |

| PWM Mode                                  |   |

| PWM, Example Frequencies/Resolutions      |   |

| CCP1IE bit                                |   |

| CCP1IF bit                                |   |

| CCPR1H Register                           |   |

| CCPR1L Register                           |   |

| CCPxM0 bit                                |   |

| CCPxM1 bit                                |   |

| CCPxM2 bit                                |   |

| CCPxM2 bit                                |   |

| CCPxX bit                                 |   |

| CCPxY bit                                 |   |

| CKE                                       |   |

| CKP                                       |   |

| Clock Polarity Select bit, CKP            |   |

| Code Examples                             | + |

|                                           | , |

| Changing Between Capture Prescalers       |   |

| 5                                         |   |

| Initializing PORTB                        |   |

| Initializing PORTC                        |   |

| Code Protection                           |   |

| Configuration Bits                        | 9 |

| D                                         |   |

## D

| 40, 43 |

|--------|

| 40, 43 |

| 9      |

|        |

| 79     |

|        |

|        |

| 17     |

|        |

### Е

| —                                      |

|----------------------------------------|

| Electrical Characteristics<br>PIC16C72 |

| External Power-on Reset Circuit 63     |

| F                                      |

| FSR Register                           |

| G                                      |

| GIE bit 68                             |

| I                                      |

| I/O Ports                              |

|                                        |

|                  | PORTA      | 19 |

|------------------|------------|----|

|                  | PORTB      |    |

|                  | PORTC      |    |

|                  | Section    |    |

| l <sup>2</sup> C |            |    |

|                  | Addressing | 48 |