Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc72-04i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

| RP1* RF | 20 (ST/ | ATUS<6:5>) |

|---------|---------|------------|

|---------|---------|------------|

$= 00 \rightarrow Bank0$

- $= 01 \rightarrow \text{Bank1}$

- =  $10 \rightarrow$  Bank2 (not implemented)

- = 11  $\rightarrow$  Bank3 (not implemented)

\* Maintain this bit clear to ensure upward compatibility with future products.

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM.

All implemented banks contain special function registers. Some "high use" special function registers from one bank may be mirrored in another bank for code reduction and quicker access (ex; the STATUS register is in Bank 0 and Bank 1).

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly through the File Select Register FSR (Section 2.5).

## FIGURE 2-2: REGISTER FILE MAP

| File      |                      |                     | File        |

|-----------|----------------------|---------------------|-------------|

| Address   | 3                    |                     | Address     |

| 00h       | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup> | 80h         |

| 01h       | TMR0                 | OPTION              | 81h         |

| 02h       | PCL                  | PCL                 | 82h         |

| 03h       | STATUS               | STATUS              | 83h         |

| 04h       | FSR                  | FSR                 | 84h         |

| 05h       | PORTA                | TRISA               | 85h         |

| 06h       | PORTB                | TRISB               | 86h         |

| 07h       | PORTC                | TRISC               | 87h         |

| 08h       |                      |                     | 88h         |

| 09h       |                      |                     | 89h         |

| 0Ah       | PCLATH               | PCLATH              | 8Ah         |

| 0Bh       | INTCON               | INTCON              | 8Bh         |

| 0Ch       | PIR1                 | PIE1                | 8Ch         |

| 0Dh       |                      |                     | 8Dh         |

| 0Eh       | TMR1L                | PCON                | 8Eh         |

| 0Fh       | TMR1H                |                     | 8Fh         |

| 10h       | T1CON                |                     | 90h         |

| 11h       | TMR2                 |                     | 91h         |

| 12h       | T2CON                | PR2                 | 92h         |

| 13h       | SSPBUF               | SSPADD              | 93h         |

| 14h       | SSPCON               | SSPSTAT             | 94h         |

| 15h       | CCPR1L               |                     | 95h         |

| 16h       | CCPR1H               |                     | 96h         |

| 17h       | CCP1CON              |                     | 97h         |

| 18h       |                      |                     | 98h         |

| 19h       |                      |                     | 99h         |

| 1Ah       |                      |                     | 9Ah         |

| 1Bh       |                      |                     | 9Bh         |

| 1Ch       |                      |                     | 9Ch         |

| 1Dh       |                      |                     | 9Dh         |

| 1Eh       | ADRES                |                     | 9Eh         |

| 1Fh       | ADCON0               | ADCON1              | 9Fh         |

| 20h       | 0                    | 0                   | A0h         |

|           | General<br>Purpose   | General<br>Purpose  |             |

|           | Register             | Register            |             |

|           |                      |                     | BFh         |

|           |                      |                     | C0h         |

|           |                      |                     |             |

| 1         |                      |                     |             |

|           |                      |                     |             |

| 7Fh       |                      |                     | FFh         |

|           | Bank 0               | Bank 1              |             |

|           |                      |                     |             |

|           | plemented data me    |                     | ead as '0'. |

| Note 1: 1 | Not a physical regis | ster.               |             |

|           |                      |                     |             |

#### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Figure 2-3, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{TO}$  and  $\overline{PD}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- Note 1: These devices do not use bits IRP and RP1 (STATUS<7:6>). Maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| R/W-0    | R/W-0                                            | R/W-0                                                                     | R-1                                  | <u>R-1</u>                                | R/W-x                                          | R/W-x                                     | R/W-x                       |                                                                                       |

|----------|--------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------|-------------------------------------------|------------------------------------------------|-------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------|

| IRP      | RP1                                              | RP0                                                                       | TO                                   | PD                                        | Z                                              | DC                                        | С                           | R = Readable bit                                                                      |

| bit7     |                                                  |                                                                           |                                      |                                           |                                                |                                           | bitO                        | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:   | 1 = Bank 2                                       | ster Bank 3<br>2, 3 (100h<br>0, 1 (00h -                                  | - 1FFh)                              | (used for i                               | ndirect addı                                   | essing)                                   |                             |                                                                                       |

| bit 6-5: | 11 = Bank<br>10 = Bank<br>01 = Bank<br>00 = Bank | < 3 (180h -<br>< 2 (100h -<br>< 1 (80h - F<br>< 0 (00h - 7<br>< is 128 by | 1FFh)<br>17Fh)<br>FFh)<br>′Fh)       | ·                                         | ed for direct                                  |                                           |                             | <sup>9</sup> bit is reserved. Always maintai                                          |

| bit 4:   |                                                  |                                                                           |                                      | struction,                                | or sleep ir                                    | struction                                 |                             |                                                                                       |

| bit 3:   |                                                  | r-down bit<br>oower-up o<br>ecution of t                                  |                                      |                                           |                                                |                                           |                             |                                                                                       |

| bit 2:   |                                                  | sult of an                                                                |                                      |                                           | peration is z                                  |                                           |                             |                                                                                       |

| bit 1:   | 1 = A carr                                       | y-out from                                                                | the 4th lo                           | w order bi                                | w, SUBLW, S<br>t of the resu<br>bit of the res | It occurred                               |                             | or borrow the polarity is reversed                                                    |

| bit 0:   | 1 = A carr<br>0 = No car<br>Note: For            | y-out from<br>rry-out from<br>borrow the<br>berand. Fo                    | the most<br>n the mos<br>polarity is | significant<br>t significar<br>s reversed |                                                | esult occur<br>result occu<br>ion is exec | red<br>irred<br>uted by ade | ding the two's complement of th<br>either the high or low order bit o                 |

## FIGURE 2-3: STATUS REGISTER (ADDRESS 03h, 83h)

# **PIC16C72 Series**

#### 2.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the peripheral interrupts.

## FIGURE 2-6: PIE1 REGISTER (ADDRESS 8Ch)

## Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

| U-0      | R/W-0                                          | U-0        | U-0         | R/W-0      | R/W-0       | R/W-0  | R/W-0  |                                                                                                                      |

|----------|------------------------------------------------|------------|-------------|------------|-------------|--------|--------|----------------------------------------------------------------------------------------------------------------------|

|          | ADIE                                           | —          | —           | SSPIE      | CCP1IE      | TMR2IE | TMR1IE | R = Readable bit                                                                                                     |

| bit7     |                                                |            |             |            |             |        | bitO   | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |

| bit 7:   | Unimplen                                       | nented: F  | Read as '0  |            |             |        |        |                                                                                                                      |

| bit 6:   | <b>ADIE</b> : A/D<br>1 = Enable<br>0 = Disable | es the A/E | ) interrupt |            | bit         |        |        |                                                                                                                      |

| bit 5-4: | Unimplen                                       | nented: R  | lead as '0' |            |             |        |        |                                                                                                                      |

| bit 3:   | <b>SSPIE</b> : Sy<br>1 = Enable<br>0 = Disable | es the SS  | P interrup  | t          | pt Enable b | bit    |        |                                                                                                                      |

| bit 2:   | <b>CCP1IE</b> : 0<br>1 = Enable<br>0 = Disable | es the CC  | P1 interru  | pt         |             |        |        |                                                                                                                      |

| bit 1:   | TMR2IE:<br>1 = Enable<br>0 = Disabl            | es the TM  | R2 to PR2   | 2 match in | •           |        |        |                                                                                                                      |

| bit 0:   | TMR1IE:<br>1 = Enable<br>0 = Disabl            | es the TM  | R1 overflo  | w interrup | ot          |        |        |                                                                                                                      |

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

## EXAMPLE 2-1: INDIRECT ADDRESSING

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDR register now will return the value of 0Ah.

**Direct Addressing** Indirect Addressing RP1:RP0 from opcode 7 6 0 IRP FSR register 0 (2) (2)bank select location select bank select location select • 00 01 10 11 00h 80h 100h 180h not used (3) (3) Data Memory(1) FFh 1FFh 7Fh 17Fh Bank 0 Bank 1 Bank 2 Bank 3 Note 1: For register file map detail see Figure 2-2. 2: Maintain RP1 and IRP as clear for upward compatibility with future products. 3: Not implemented.

## FIGURE 2-11: DIRECT/INDIRECT ADDRESSING

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | movwf<br>clrf<br>incf | FSR<br>INDF<br>FSR | ;clear INDF register<br>;inc pointer |

|----------|-----------------------|--------------------|--------------------------------------|

|          | goto                  | -                  | ;all done?<br>;NO, clear next        |

| CONTINUE |                       |                    |                                      |

|          | :                     |                    | ;YES, continue                       |

## 5.2 <u>Timer1 Oscillator</u>

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 5-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

TABLE 5-1CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type   | e Freq                                                                                                                                            | C1                    | C2           |  |  |  |  |  |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|--|--|--|--|--|--|--|--|--|

| LP         | 32 kHz                                                                                                                                            | 32 kHz 33 pF          |              |  |  |  |  |  |  |  |  |  |

|            | 100 kHz                                                                                                                                           | 15 pF                 | 15 pF        |  |  |  |  |  |  |  |  |  |

|            | 200 kHz                                                                                                                                           | 15 pF                 | 15 pF        |  |  |  |  |  |  |  |  |  |

| These      | These values are for design guidance only.                                                                                                        |                       |              |  |  |  |  |  |  |  |  |  |

| Crystals 7 | Crystals Tested:                                                                                                                                  |                       |              |  |  |  |  |  |  |  |  |  |

| 32.768 kH  | z Epson C-00                                                                                                                                      | 1R32.768K-A           | $\pm$ 20 PPM |  |  |  |  |  |  |  |  |  |

| 100 kHz    | Epson C-2 1                                                                                                                                       | Epson C-2 100.00 KC-P |              |  |  |  |  |  |  |  |  |  |

| 200 kHz    | STD XTL 20                                                                                                                                        | 0.000 kHz             | $\pm$ 20 PPM |  |  |  |  |  |  |  |  |  |

| 0          | of oscillator but also increases the start-up                                                                                                     |                       |              |  |  |  |  |  |  |  |  |  |

| 2: S       | time.<br>Since each resonator/crystal has its own<br>characteristics, the user should consult the<br>resonator/crystal manufacturer for appropri- |                       |              |  |  |  |  |  |  |  |  |  |

ate values of external components.

## 5.3 <u>Timer1 Interrupt</u>

The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

#### 5.4 <u>Resetting Timer1 using a CCP Trigger</u> <u>Output</u>

If the CCP module is configured in compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The spe | cial e | event | trigg | ers from tl | ne CC | P1  |

|-------|---------|--------|-------|-------|-------------|-------|-----|

|       | module  | will   | not   | set   | interrupt   | flag  | bit |

|       | TMR1IF  | (PIR   | 1<0>  | ·).   |             |       |     |

Timer1 must be configured for either timer or synchronized counter mode to take advantage of this feature. If Timer1 is running in asynchronous counter mode, this reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer1.

# TABLE 5-2 REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address | Name   | Bit 7   | Bit 6   | Bit 5         | Bit 4         | Bit 3          | Bit 2      | Bit 1       | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|---------|---------|---------------|---------------|----------------|------------|-------------|-----------|--------------------------|---------------------------------|

| 0Bh,8Bh | INTCON | GIE     | PEIE    | TOIE          | INTE          | RBIE           | TOIF       | INTF        | RBIF      | 0000 000x                | 0000 000u                       |

| 0Ch     | PIR1   | (1)     | ADIF    | (1)           | (1)           | SSPIF          | CCP1IF     | TMR2IF      | TMR1IF    | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1   | (1)     | ADIE    | (1)           | (1)           | SSPIE          | CCP1IE     | TMR2IE      | TMR1IE    | 0000 0000                | 0000 0000                       |

| 0Eh     | TMR1L  | Holding | registe | r for the Lea | st Significan | it Byte of the | 16-bit TMF | R1 register |           | xxxx xxxx                | uuuu uuuu                       |

| 0Fh     |        |         |         |               |               |                |            |             | xxxx xxxx | uuuu uuuu                |                                 |

| 10h     | T1CON  | _       | _       | T1CKPS1       | T1CKPS0       | T1OSCEN        | T1SYNC     | TMR1CS      | TMR1ON    | 00 0000                  | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module. Note 1: These bits are unimplemented, read as '0'.

#### 8.4.1.1 ADDRESSING

Once the SSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) - on the falling edge of the ninth SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address the first byte would equal

'1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive repeated START condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

|    | ts as Data<br>s Received |                    |                       | Set bit SSPIF                        |  |  |

|----|--------------------------|--------------------|-----------------------|--------------------------------------|--|--|

| BF | SSPOV                    | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | (SSP Interrupt occurs<br>if enabled) |  |  |

| 0  | 0                        | Yes                | Yes                   | Yes                                  |  |  |

| 1  | 0                        | No                 | No                    | Yes                                  |  |  |

| 1  | 1                        | No                 | No                    | Yes                                  |  |  |

| 0  | 1                        | No                 | No                    | Yes                                  |  |  |

## 10.0 SPECIAL FEATURES OF THE CPU

The PIC16C72 series has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-Circuit Serial Programming™

The PIC16CXXX family has a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual, DS33023.

## 10.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

## FIGURE 10-1: CONFIGURATION WORD FOR PIC16C72/R72

| CP1             | CP | 0 CP1              | CP0           | CP1         | CP0        | —        | BODEN                 | CP1    | CP0    | PWRTE      | WDTE     | FOSC1     | FOSC0        | Register:CONFIG<br>Address2007h |

|-----------------|----|--------------------|---------------|-------------|------------|----------|-----------------------|--------|--------|------------|----------|-----------|--------------|---------------------------------|

| bit13           |    |                    |               |             |            |          |                       |        |        |            |          |           | bit0         | Address2007n                    |

| bit 13-         | -8 | CP1:CF             | <b>0</b> : Co | de Pro      | otection   | n bits ( | 2)                    |        |        |            |          |           |              |                                 |

| 5-4             |    | 11 <b>= C</b>      |               |             |            |          |                       |        |        |            |          |           |              |                                 |

|                 |    |                    | •             | •           | •          |          | nory code             | •      |        |            |          |           |              |                                 |

|                 |    | 01 = Up<br>00 = Al | •             |             |            |          | mory coo              | de pro | tected |            |          |           |              |                                 |

| L.1. <b>-</b> 7 |    |                    |               | ,           |            |          | eu                    |        |        |            |          |           |              |                                 |

| bit 7:          |    | Unimpl             |               |             |            |          | (4)                   |        |        |            |          |           |              |                                 |

| bit 6:          |    | BODEN              |               |             | Reset      | Enab     | le bit <sup>(1)</sup> |        |        |            |          |           |              |                                 |

|                 |    | 1 = BOI<br>0 = BOI |               |             |            |          |                       |        |        |            |          |           |              |                                 |

| L:L 0.          |    |                    |               |             | <b>T</b> : | <b>-</b> |                       |        |        |            |          |           |              |                                 |

| bit 3:          |    | PWRTE<br>1 = PW    |               |             | Ilmer      | Enable   |                       |        |        |            |          |           |              |                                 |

|                 |    | 0 = PW             |               |             |            |          |                       |        |        |            |          |           |              |                                 |

| bit 2:          |    | WDTE:              | Watch         | ndoa T      | ïmer E     | nable    | bit                   |        |        |            |          |           |              |                                 |

|                 |    | 1 = WD             |               | •           |            |          |                       |        |        |            |          |           |              |                                 |

|                 |    | 0 = WD             | T disa        | bled        |            |          |                       |        |        |            |          |           |              |                                 |

| bit 1-0         | 0: | FOSC1              | :FOSC         | <b>:</b> Os | cillator   | Seled    | ction bits            |        |        |            |          |           |              |                                 |

|                 |    | 11 = R0            |               |             |            |          |                       |        |        |            |          |           |              |                                 |

|                 |    | 10 = HS<br>01 = X  |               |             |            |          |                       |        |        |            |          |           |              |                                 |

|                 |    | $01 = \mathbf{A}$  |               |             |            |          |                       |        |        |            |          |           |              |                                 |

|                 |    | 00 <b>–</b> El     | 00011         |             |            |          |                       |        |        |            |          |           |              |                                 |

| Note 1          |    |                    | •             |             |            |          |                       |        |        | •          | •        | , 0       | lless of the | e value of bit PWRTE.           |

|                 |    |                    |               |             |            |          |                       |        |        | n-out Res  |          |           |              |                                 |

|                 | 2: | All of th          | e CP1         | :CP0        | pairs h    | ave to   | be giver              | the s  | ame v  | alue to en | able the | code prot | tection sch  | neme listed.                    |

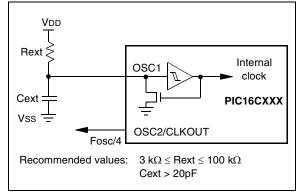

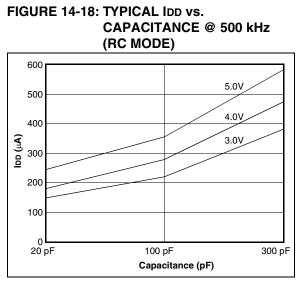

#### 10.2.3 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 10-4 shows how the R/C combination is connected to the PIC16CXXX family.

#### FIGURE 10-4: RC OSCILLATOR MODE

## 10.3 <u>Reset</u>

The PIC16CXXX family differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (normal operation)

- Brown-out Reset (BOR)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{\text{MCLR}}$  and WDT Reset, on  $\overline{\text{MCLR}}$  reset during SLEEP, and Brownout Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different reset situations as indicated in Table 10-4. These bits are used in software to determine the nature of the reset. See Table 10-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 10-5.

The PIC16C72/CR72 have a MCLR noise filter in the MCLR reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

## 10.8 <u>Time-out Sequence</u>

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 10-7, Figure 10-8, Figure 10-9 and Figure 10-10 depict timeout sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 10-9). This is useful for testing purposes or to synchronize more than one PIC16CXXX family device operating in parallel.

Table 10-5 shows the reset conditions for some special function registers, while Table 10-6 shows the reset conditions for all the registers.

## 10.9 <u>Power Control/Status Register</u> (PCON)

The Power Control/Status Register, PCON has up to two bits, depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent resets to see if bit BOR cleared, indicating a BOR occurred. The BOR bit is a "Don't Care" bit and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word).

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Oscillator Configura- | Power-up            |           | Brown-out        | Wake-up from |  |

|-----------------------|---------------------|-----------|------------------|--------------|--|

| tion                  | <b>PWRTE</b> = 0    | PWRTE = 1 | Brown-out        | SLEEP        |  |

| XT, HS, LP            | 72 ms +<br>1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                    | 72 ms               | —         | 72 ms            | —            |  |

## TABLE 10-3 TIME-OUT IN VARIOUS SITUATIONS

## TABLE 10-4 STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD |                                                         |  |

|-----|-----|----|----|---------------------------------------------------------|--|

| 0   | х   | 1  | 1  | Power-on Reset                                          |  |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |  |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |  |

| 1   | 0   | x  | x  | Brown-out Reset                                         |  |

| 1   | 1   | 0  | 1  | WDT Reset                                               |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |

| 1   | 1   | u  | u  | ICLR Reset during normal operation                      |  |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |

## TABLE 10-5 RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

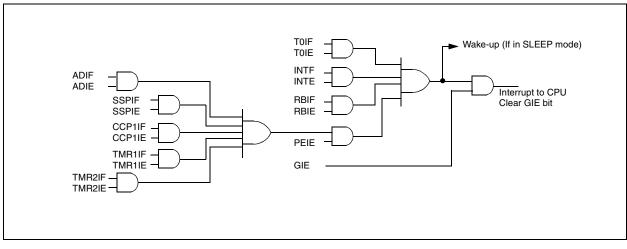

#### 10.10 Interrupts

The PIC16C72/CR72 has 8 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit

#### 10.10.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 10.13 for details on SLEEP mode.

#### 10.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 4.0)

#### 10.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 3.2)

#### FIGURE 10-11: INTERRUPT LOGIC

## 10.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, i.e., W register and STATUS register. This will have to be implemented in software.

Example 10-1 stores and restores the W and STATUS registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Executes the ISR code.

- d) Restores the STATUS register (and bank select bit).

- e) Restores the W register.

#### EXAMPLE 10-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

| MOVWF       | W_TEMP                  | ;Copy W to W_TEMP register, could be bank one or zero   |

|-------------|-------------------------|---------------------------------------------------------|

| SWAPF       | STATUS,W                | ;Swap status to be saved into W                         |

| CLRF        | STATUS                  | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF       | STATUS_TEMP             | ;Save status to bank zero STATUS_TEMP register          |

| :           |                         |                                                         |

| : Interrupt | Service Routine (ISR) - | user defined                                            |

| :           |                         |                                                         |

| SWAPF       | STATUS_TEMP,W           | ;Swap STATUS_TEMP register into W                       |

|             |                         | ;(sets bank to original state)                          |

| MOVWF       | STATUS                  | ;Move W into STATUS register                            |

| SWAPF       | W_TEMP,F                | ;Swap W_TEMP                                            |

| SWAPF       | W_TEMP,W                | ;Swap W_TEMP into W                                     |

NOTES:

# 13.0 ELECTRICAL CHARACTERISTICS - PIC16C72 SERIES

#### Absolute Maximum Ratings †

| Parameter                                                                               | PIC16C72              | PIC16CR72             |

|-----------------------------------------------------------------------------------------|-----------------------|-----------------------|

| Ambient temperature under bias                                                          | -55 to +125°C         | -55 to +125°C         |

| Storage temperature                                                                     | -65°C to +150°C       | -65°C to +150°C       |

| Voltage on any pin with respect to VSS (except VDD, $\overline{\text{MCLR}}$ , and RA4) | -0.3V to (VDD + 0.3V) | -0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to VSS                                                      | -0.3 to +7.5V         | TBD                   |

| Voltage on MCLR with respect to Vss (Note 1)                                            | -0.3 to +14V          | TBD                   |

| Voltage on RA4 with respect to Vss                                                      | -0.3 to +14V          | TBD                   |

| Total power dissipation (Note 2)                                                        | 1.0W                  | 1.0W                  |

| Maximum current out of Vss pin                                                          | 300 mA                | 300 mA                |

| Maximum current into VDD pin                                                            | 250 mA                | 250 mA                |

| Input clamp current, Iık (Vı < 0 or Vı > VDD)                                           | ± 20 mA               | $\pm$ 20 mA           |

| Output clamp current, IOK (Vo < 0 or Vo > VDD)                                          | ± 20 mA               | ± 20 mA               |

| Maximum output current sunk by any I/O pin                                              | 25 mA                 | 25 mA                 |

| Maximum output current sourced by any I/O pin                                           | 25 mA                 | 25 mA                 |

| Maximum current sunk by PORTA and PORTB (combined)                                      | 200 mA                | 200 mA                |

| Maximum current sourced by PORTA and PORTB (combined)                                   | 200 mA                | 200 mA                |

| Maximum current sunk by PORTC                                                           | 200 mA                | 200 mA                |

| Maximum current sourced by PORTC                                                        | 200 mA                | 200 mA                |

Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

2. Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\Sigma$  IOH} +  $\Sigma$  {(VDD - VOH) x IOH} +  $\Sigma$ (VOI x IOL).

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

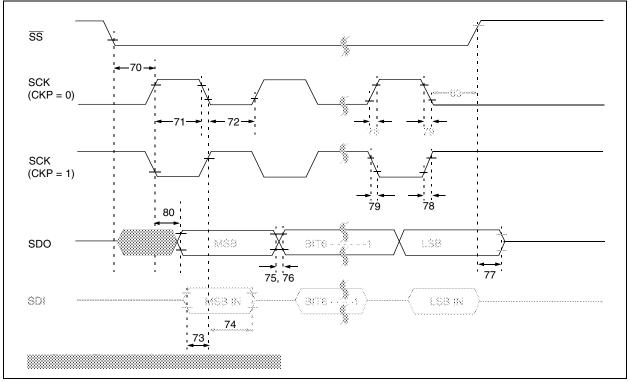

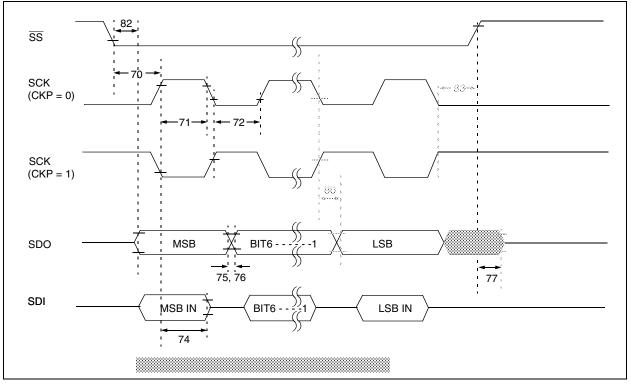

# FIGURE 13-10: SPI SLAVE MODE TIMING (CKE = 0)

# FIGURE 13-11: SPI SLAVE MODE TIMING (CKE = 1)

| Param<br>No. | Sym                   | Characteristic                             | Min      | Тур† | Max | Units | Conditions |

|--------------|-----------------------|--------------------------------------------|----------|------|-----|-------|------------|

| 70           | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                  | Тсү      | -    | —   | ns    |            |

| 71           | TscH                  | SCK input high time (slave mode)           | Tcy + 20 | _    | —   | ns    |            |

| 72           | TscL                  | SCK input low time (slave mode)            | TCY + 20 | _    | _   | ns    |            |

| 73           | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge   | 50       | -    | —   | ns    |            |

| 74           | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge    | 50       | -    | -   | ns    |            |

| 75           | TdoR                  | SDO data output rise time                  | _        | 10   | 25  | ns    |            |

| 76           | TdoF                  | SDO data output fall time                  | —        | 10   | 25  | ns    |            |

| 77           | TssH2doZ              | SS <sup>↑</sup> to SDO output hi-impedance | 10       | -    | 50  | ns    |            |

| 78           | TscR                  | SCK output rise time (master mode)         | _        | 10   | 25  | ns    |            |

| 79           | TscF                  | SCK output fall time (master mode)         | —        | 10   | 25  | ns    |            |

| 80           | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge       | —        | _    | 50  | ns    |            |

TABLE 13-8

SPI SLAVE MODE REQUIREMENTS (CKE=0) - PIC16C72

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Parameter<br>No. | Sym                   | Characteristic                                                        | Min         | Тур† | Max | Units | Conditions |

|------------------|-----------------------|-----------------------------------------------------------------------|-------------|------|-----|-------|------------|

| 70*              | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсү         | —    | —   | ns    |            |

| 71*              | TscH                  | SCK input high time (slave mode)                                      | TCY + 20    | _    | _   | ns    |            |

| 72*              | TscL                  | SCK input low time (slave mode)                                       | TCY + 20    | _    | _   | ns    |            |

| 73*              | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge                              | 100         | _    | —   | ns    |            |

| 74*              | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                               | 100         | —    | —   | ns    |            |

| 75*              | TdoR                  | SDO data output rise time                                             | —           | 10   | 25  | ns    |            |

| 76*              | TdoF                  | SDO data output fall time                                             | —           | 10   | 25  | ns    |            |

| 77*              | TssH2doZ              | SS↑ to SDO output hi-impedance                                        | 10          | _    | 50  | ns    |            |

| 78*              | TscR                  | SCK output rise time (master mode)                                    | —           | 10   | 25  | ns    |            |

| 79*              | TscF                  | SCK output fall time (master mode)                                    | _           | 10   | 25  | ns    |            |

| 80*              | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                                  | —           | —    | 50  | ns    |            |

| 81*              | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK edge                                     | Тсү         | —    | —   | ns    |            |

| 82*              | TssL2doV              | SDO data output valid after $\overline{SS}\downarrow$ edge            | —           | _    | 50  | ns    |            |

| 83*              | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                   | 1.5Tcy + 40 | _    | —   | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# TABLE 14-1RC OSCILLATORFREQUENCIES

| Cext   | Rext | Average      |        |  |

|--------|------|--------------|--------|--|

| Cext   | nexi | Fosc @ 5V, 3 | 25°C   |  |

| 22 pF  | 5k   | 4.12 MHz     | ± 1.4% |  |

|        | 10k  | 2.35 MHz     | ± 1.4% |  |

|        | 100k | 268 kHz      | ± 1.1% |  |

| 100 pF | 3.3k | 1.80 MHz     | ± 1.0% |  |

|        | 5k   | 1.27 MHz     | ± 1.0% |  |

|        | 10k  | 688 kHz      | ± 1.2% |  |

|        | 100k | 77.2 kHz     | ± 1.0% |  |

| 300 pF | 3.3k | 707 kHz      | ± 1.4% |  |

|        | 5k   | 501 kHz      | ± 1.2% |  |

|        | 10k  | 269 kHz      | ± 1.6% |  |

|        | 100k | 28.3 kHz     | ± 1.1% |  |

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

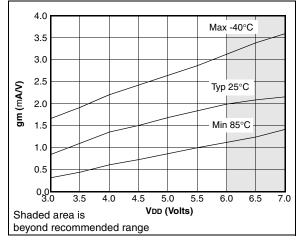

## FIGURE 14-19: TRANSCONDUCTANCE(gm) OF HS OSCILLATOR vs. VDD

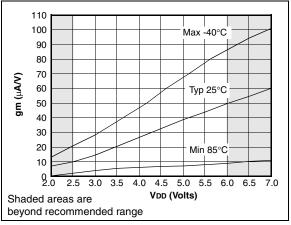

## FIGURE 14-20: TRANSCONDUCTANCE(gm) OF LP OSCILLATOR vs. VDD

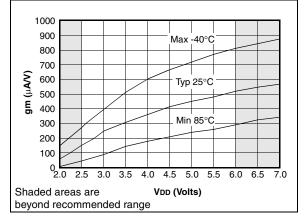

## FIGURE 14-21: TRANSCONDUCTANCE(gm) OF XT OSCILLATOR vs. VDD

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

## PIC16C72 SERIES PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.         | $\overline{\uparrow}$ $\overline{\uparrow}$ $\overline{\uparrow}$ $\overline{\uparrow}$ $\overline{-}$                                                                                                                       | Examples:         a)       PIC16C72 -04/P 301 = Commercial temp.,<br>PDIP package, 4 MHz, normal VDD limits, QTP<br>pattern #301.         b)       PIC16LC72 - 04I/SO = Industrial temp., SOIC                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device           | PIC16C72 <sup>(1)</sup> , PIC16C72T <sup>(2)</sup><br>PIC16LC72 <sup>(1)</sup> , PIC16LC72T <sup>(2)</sup><br>PIC16CR72 <sup>(1)</sup> , PIC16CR72T <sup>(2)</sup><br>PIC16LCR72 <sup>(1)</sup> , PIC16LCR72T <sup>(2)</sup> | <ul> <li>c) PIC16CC72 - 04//SO = Industrial territy., SOIC package, 200 kHz, Extended VDD limits.</li> <li>c) PIC16CR72 - 10I/P = ROM program memory, Industrial temp., PDIP package, 10MHz, normal VDD limits.</li> </ul> |

| Frequency Range  | 02 = 2 MHz<br>04 = 4 MHz<br>10 = 10 MHz<br>20 = 20 MHz                                                                                                                                                                       | Note 1: C= CMOS<br>CR= CMOS ROM<br>LC= Low Power CMOS<br>LCR= ROM Version, Extended Vdd range<br>2: T = in tape and reel - SOIC, SSOP pack-                                                                                |

| Temperature Rang | $ b^{(3)} = 0^{\circ}C \text{ to } 70^{\circ}C \text{ (Commercial)}  I = -40^{\circ}C \text{ to } +85^{\circ}C \text{ (Industrial)}  E = -40^{\circ}C \text{ to } +125^{\circ}C \text{ (Extended)} $                         | ages only.<br><b>3:</b> b = blank                                                                                                                                                                                          |

| Package          | JW = Ceramic Dual In-Line Package with Wi<br>SO = Small Outline - 300 mil<br>SP = Skinny PDIP<br>SS = Shrink Samll Outline Package - 209 m                                                                                   |                                                                                                                                                                                                                            |

| Pattern          | 3-digit Pattern Code for QTP, ROM (blank otherw                                                                                                                                                                              | ise)                                                                                                                                                                                                                       |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type (including LC devices).

# SALES AND SUPPORT

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office (see last page)

- 2. The Microchip's Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).

- Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 1998-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769669

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.