# Microchip Technology - PIC16LC72T-04/SS Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Dectano                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc72t-04-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **PIC16C72 Series**

#### 2.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the peripheral interrupts.

#### FIGURE 2-6: PIE1 REGISTER (ADDRESS 8Ch)

# Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

| U-0      | R/W-0                                          | U-0                                                                                                                                           | U-0         | R/W-0      | R/W-0       | R/W-0  | R/W-0  |                                                                                                                      |  |  |  |

|----------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------|--------|--------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

|          | ADIE                                           | —                                                                                                                                             | —           | SSPIE      | CCP1IE      | TMR2IE | TMR1IE | R = Readable bit                                                                                                     |  |  |  |

| bit7     |                                                |                                                                                                                                               |             |            |             |        | bitO   | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |  |  |  |

| bit 7:   | Unimplen                                       | nented: F                                                                                                                                     | Read as '0  |            |             |        |        |                                                                                                                      |  |  |  |

| bit 6:   | <b>ADIE</b> : A/D<br>1 = Enable<br>0 = Disable | es the A/E                                                                                                                                    | ) interrupt |            | bit         |        |        |                                                                                                                      |  |  |  |

| bit 5-4: | Unimplen                                       | nented: R                                                                                                                                     | lead as '0' |            |             |        |        |                                                                                                                      |  |  |  |

| bit 3:   | <b>SSPIE</b> : Sy<br>1 = Enable<br>0 = Disable | es the SS                                                                                                                                     | P interrup  | t          | pt Enable b | bit    |        |                                                                                                                      |  |  |  |

| bit 2:   | <b>CCP1IE</b> : 0<br>1 = Enable<br>0 = Disable | es the CC                                                                                                                                     | P1 interru  | pt         |             |        |        |                                                                                                                      |  |  |  |

| bit 1:   | 1 = Enable                                     | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit<br>1 = Enables the TMR2 to PR2 match interrupt<br>0 = Disables the TMR2 to PR2 match interrupt |             |            |             |        |        |                                                                                                                      |  |  |  |

| bit 0:   | TMR1IE:<br>1 = Enable<br>0 = Disabl            | es the TM                                                                                                                                     | R1 overflo  | w interrup | ot          |        |        |                                                                                                                      |  |  |  |

#### 2.3.1 STACK

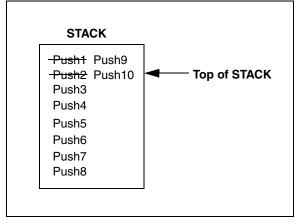

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Midrange devices have an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on). An example of the overwriting of the stack is shown in Figure 2-10.

#### FIGURE 2-10: STACK MODIFICATION

#### 2.4 <u>Program Memory Paging</u>

The CALL and GOTO instructions provide 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

**Note:** PIC16C72 Series devices ignore paging bit PCLATH<4>. The use of PCLATH<4> as a general purpose read/write bit is not recommended since this may affect upward compatibility with future products.

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

### EXAMPLE 2-1: INDIRECT ADDRESSING

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDR register now will return the value of 0Ah.

**Direct Addressing** Indirect Addressing RP1:RP0 from opcode 7 6 0 IRP FSR register 0 (2) (2)bank select location select bank select location select • 00 01 10 11 00h 80h 100h 180h not used (3) (3) Data Memory(1) FFh 1FFh 7Fh 17Fh Bank 0 Bank 1 Bank 2 Bank 3 Note 1: For register file map detail see Figure 2-2. 2: Maintain RP1 and IRP as clear for upward compatibility with future products. 3: Not implemented.

# FIGURE 2-11: DIRECT/INDIRECT ADDRESSING

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | movwf<br>clrf<br>incf | FSR<br>INDF<br>FSR | ;clear INDF register<br>;inc pointer |

|----------|-----------------------|--------------------|--------------------------------------|

|          | goto                  | -                  | ;all done?<br>;NO, clear next        |

| CONTINUE |                       |                    |                                      |

|          | :                     |                    | ;YES, continue                       |

# 3.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> Mid-Range MCU Reference Manual, DS33023.

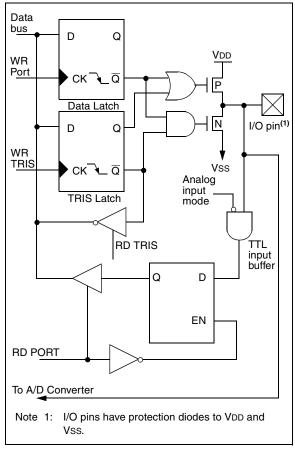

## 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, i.e., put the contents of the output latch on the selected pin.

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

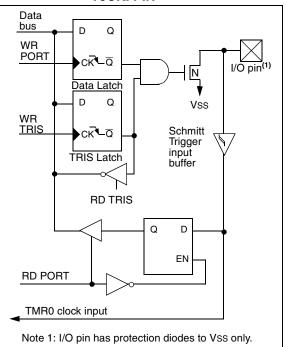

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, these pins are con-  |

|-------|-------------------------------------------|

|       | figured as analog inputs and read as '0'. |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

EXAMPLE 3-1: INITIALIZING PORTA

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| CLRF  | PORTA   |     | ; | Initialize PORTA by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISA   |     | ; | Set RA<3:0> as inputs |

|       |         |     | ; | RA<5:4> as outputs    |

|       |         |     | ; | TRISA<7:6> are always |

|       |         |     | ; | read as '0'.          |

|       |         |     |   |                       |

#### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

#### FIGURE 3-2: BLOCK DIAGRAM OF RA4/ T0CKI PIN

### FIGURE 6-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0      | R/W-0                                                             | R/W-0                  | R/W-0      | R/W-0        | R/W-0         | R/W-0   | R/W-0   |                                                                                                                      |

|----------|-------------------------------------------------------------------|------------------------|------------|--------------|---------------|---------|---------|----------------------------------------------------------------------------------------------------------------------|

| —        | TOUTPS3                                                           | TOUTPS2                | TOUTPS1    | TOUTPS0      | TMR2ON        | T2CKPS1 | T2CKPS0 | R = Readable bit                                                                                                     |

| bit 7.   | Unimalam                                                          | ented: Doo             | d aa 101   |              |               |         | bit0    | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |

| bit 7:   | Unimplem                                                          | ented: Rea             | u as u     |              |               |         |         |                                                                                                                      |

| bit 6-3: | TOUTPS3:<br>0000 = 1:1<br>0001 = 1:2<br>•<br>•<br>•<br>1111 = 1:1 | Postscale<br>Postscale |            | tput Postsca | ale Select bi | ts      |         |                                                                                                                      |

| bit 2:   | <b>TMR2ON</b> : <sup>1</sup><br>1 = Timer2<br>0 = Timer2          | is on                  | bit        |              |               |         |         |                                                                                                                      |

| bit 1-0: | <b>T2CKPS1:</b><br>00 = Presc<br>01 = Presc<br>1x = Presc         | aler is 1<br>aler is 4 | Timer2 Clc | ock Prescale | Select bits   |         |         |                                                                                                                      |

#### TABLE 6-1 **REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER**

| Address | Name   | Bit 7       | Bit 6          | Bit 5     | Bit 4     | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|-------------|----------------|-----------|-----------|---------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh | INTCON | GIE         | PEIE           | TOIE      | INTE      | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch     | PIR1   | (1)         | ADIF           | (1)       | (1)       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1   | (1)         | ADIE           | (1)       | (1)       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000                | 0000 0000                       |

| 11h     | TMR2   | Timer2 mod  | dule's registe | r         |           |         |        |         |         | 0000 0000                | 0000 0000                       |

| 12h     | T2CON  | _           | TOUTPS3        | TOUTPS2   | TOUTPS1   | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 92h     | PR2    | Timer2 Peri | od Register    | 1111 1111 | 1111 1111 |         |        |         |         |                          |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module. 2: These bits are unimplemented, read as '0'.

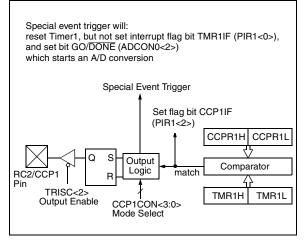

### 7.2 <u>Compare Mode</u>

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- driven High

- driven Low

- remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 7-3: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 7.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force       |

|-------|------------------------------------------------|

|       | the RC2/CCP1 compare output latch to the       |

|       | default low level. This is not the data latch. |

#### 7.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 7.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 7.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special trigger output of CCP1 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

Note: The special event trigger from the CCP1 module will not set interrupt flag bit TMR1IF (PIR1<0>).

# TABLE 7-2 REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address | Name    | Bit 7       | Bit 6                               | Bit 5        | Bit 4       | Bit 3         | Bit 2      | Bit 1       | Bit 0  | PC   | e on:<br>)R,<br>)R | all o | e on<br>other<br>sets |

|---------|---------|-------------|-------------------------------------|--------------|-------------|---------------|------------|-------------|--------|------|--------------------|-------|-----------------------|

| 0Bh,8Bh | INTCON  | GIE         | PEIE                                | TOIE         | INTE        | RBIE          | T0IF       | INTF        | RBIF   | 0000 | 000x               | 0000  | 000u                  |

| 0Ch     | PIR1    | (1)         | ADIF                                | (1)          | (1)         | SSPIF         | CCP1IF     | TMR2IF      | TMR1IF | 0000 | 0000               | 0000  | 0000                  |

| 8Ch     | PIE1    | (1)         | ADIE                                | (1)          | (1)         | SSPIE         | CCP1IE     | TMR2IE      | TMR1IE | 0000 | 0000               | 0000  | 0000                  |

| 87h     | TRISC   | PORTC Da    | ata Dire                            | ction Regis  | ter         |               |            |             |        | 1111 | 1111               | 1111  | 1111                  |

| 0Eh     | TMR1L   | Holding reg | gister fo                           | or the Least | Significant | Byte of the   | 16-bit TMF | R1 register |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 0Fh     | TMR1H   | Holding reg | gister fo                           | or the Most  | Significant | Byte of the 1 | 16-bit TMR | 1register   |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 10h     | T1CON   | —           |                                     | T1CKPS1      | T1CKPS0     | T1OSCEN       | T1SYNC     | TMR1CS      | TMR1ON | 00   | 0000               | uu    | uuuu                  |

| 15h     | CCPR1L  | Capture/Co  | Capture/Compare/PWM register1 (LSB) |              |             |               |            |             |        |      | xxxx               | uuuu  | uuuu                  |

| 16h     | CCPR1H  | Capture/Co  | Capture/Compare/PWM register1 (MSB) |              |             |               |            |             |        |      | xxxx               | uuuu  | uuuu                  |

| 17h     | CCP1CON | —           |                                     | CCP1X        | CCP1Y       | CCP1M3        | CCP1M2     | CCP1M1      | CCP1M0 | 00   | 0000               | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1. Note 1: These bits/registers are unimplemented, read as '0'. NOTES:

#### 8.4.1.1 ADDRESSING

Once the SSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) - on the falling edge of the ninth SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address the first byte would equal

'1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive repeated START condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

|    | ts as Data<br>s Received |                    |                       | Set bit SSPIF                        |

|----|--------------------------|--------------------|-----------------------|--------------------------------------|

| BF | SSPOV                    | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | (SSP Interrupt occurs<br>if enabled) |

| 0  | 0                        | Yes                | Yes                   | Yes                                  |

| 1  | 0                        | No                 | No                    | Yes                                  |

| 1  | 1                        | No                 | No                    | Yes                                  |

| 0  | 1                        | No                 | No                    | Yes                                  |

#### 8.4.2 MASTER OPERATION

Master operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear.

In master operation, the SCL and SDA lines are manipulated in firmware by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

Master operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master operation and slave modes are used, the software needs to differentiate the source(s) of the interrupt.

For more information on master operation, see AN554 - Software Implementation of  $I^2C$  Bus Master.

#### 8.4.3 MULTI-MASTER OPERATION

In multi-master operation, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

For more information on master operation, see AN578 - Use of the SSP Module in the of  $I^2C$  Multi-Master Environment.

| Address                | Name    | Bit 7              | Bit 6              | Bit 5                    | Bit 4     | Bit 3     | Bit 2    | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|------------------------|---------|--------------------|--------------------|--------------------------|-----------|-----------|----------|--------|--------|-------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                | PEIE               | TOIE                     | INTE      | RBIE      | TOIF     | INTF   | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch                    | PIR1    | (1)                | ADIF               | (1)                      | (1)       | SSPIF     | CCP1IF   | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 8Ch                    | PIE1    | (1)                | ADIE               | (1)                      | (1)       | SSPIE     | CCP1IE   | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 13h                    | SSPBUF  | Synchronou         | is Serial F        | Port Recei               | ve Buffer | /Transmit | Register |        |        | xxxx xxxx               | uuuu uuuu                       |

| 93h                    | SSPADD  | Synchronou         | ıs Serial F        | Port (I <sup>2</sup> C n | node) Ado | dress Reg | gister   |        |        | 0000 0000               | 0000 0000                       |

| 14h                    | SSPCON  | WCOL               | SSPOV              | SSPEN                    | CKP       | SSPM3     | SSPM2    | SSPM1  | SSPM0  | 0000 0000               | 0000 0000                       |

| 94h                    | SSPSTAT | SMP <sup>(2)</sup> | CKE <sup>(2)</sup> | D/A                      | Р         | S         | R/W      | UA     | BF     | 0000 0000               | 0000 0000                       |

| 87h                    | TRISC   | PORTC Dat          | ta Directio        | 1111 1111                | 1111 1111 |           |          |        |        |                         |                                 |

### TABLE 8-4REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'.

Shaded cells are not used by SSP module in SPI mode. Note 1: These bits are unimplemented, read as '0'.

2: The SMP and CKE bits are implemented on the PIC16CR72 only. On the PIC16C72, these two bits are unimplemented, read as '0'.

#### 9.4 <u>A/D Conversions</u>

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

#### 9.5 <u>Use of the CCP Trigger</u>

An A/D conversion can be started by the "special event trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the

GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

#### TABLE 9-2 REGISTERS/BITS ASSOCIATED WITH A/D

| Address | Name   | Bit 7   | Bit 6       | Bit 5 | Bit 4  | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|---------|-------------|-------|--------|------------|----------|--------|--------|--------------------------|---------------------------|

| 0Bh,8Bh | INTCON | GIE     | PEIE        | TOIE  | INTE   | RBIE       | T0IF     | INTF   | RBIF   | 0000 000x                | 0000 000u                 |

| 0Ch     | PIR1   | —       | ADIF        | _     |        | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | -0 0000                  | -0 0000                   |

| 8Ch     | PIE1   | —       | ADIE        | _     |        | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | -0 0000                  | -0 0000                   |

| 1Eh     | ADRES  | A/D Res | sult Regist | ter   | •      | •          |          |        |        | xxxx xxxx                | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1   | ADCS0       | CHS2  | CHS1   | CHS0       | GO/DONE  | —      | ADON   | 0000 00-0                | 0000 00-0                 |

| 9Fh     | ADCON1 | —       | —           | _     |        | —          | PCFG2    | PCFG1  | PCFG0  | 000                      | 000                       |

| 05h     | PORTA  |         | _           | RA5   | RA4    | RA3        | RA2      | RA1    | RA0    | 0x 0000                  | 0u 0000                   |

| 85h     | TRISA  |         | _           | PORTA | Data D | irection F | Register |        |        | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

#### 10.4 Power-On Reset (POR)

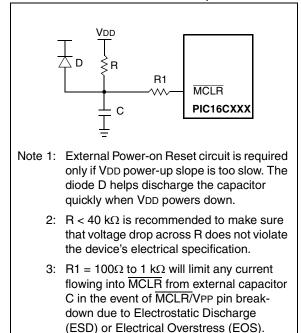

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details. For a slow rise time, see Figure 10-6.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the startup conditions.

#### FIGURE 10-6: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

## 10.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

# 10.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

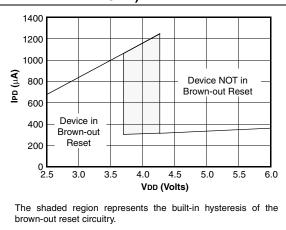

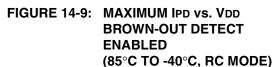

# 10.7 Brown-Out Reset (BOR)

A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V (3.8V - 4.2V range) for greater than parameter #35, the brown-out situation will reset the chip. A reset may not occur if VDD falls below 4.0V for less than parameter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms. If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer will execute a 72 ms time delay. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

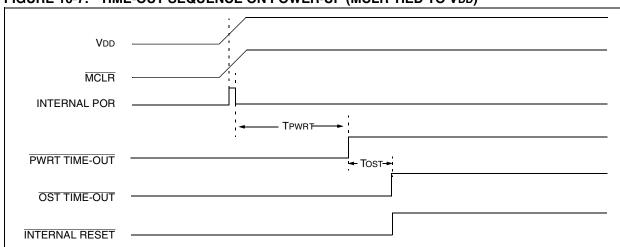

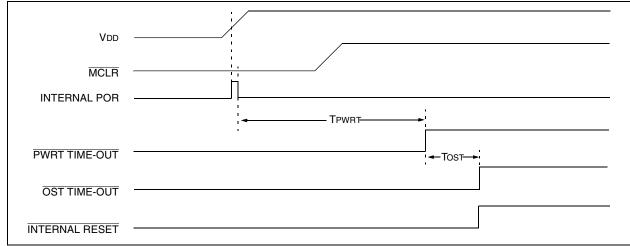

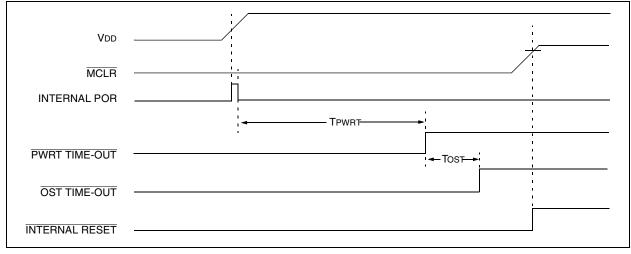

#### 10.8 <u>Time-out Sequence</u>

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 10-7, Figure 10-8, Figure 10-9 and Figure 10-10 depict timeout sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 10-9). This is useful for testing purposes or to synchronize more than one PIC16CXXX family device operating in parallel.

Table 10-5 shows the reset conditions for some special function registers, while Table 10-6 shows the reset conditions for all the registers.

#### 10.9 <u>Power Control/Status Register</u> (PCON)

The Power Control/Status Register, PCON has up to two bits, depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent resets to see if bit BOR cleared, indicating a BOR occurred. The BOR bit is a "Don't Care" bit and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word).

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Oscillator Configura- | Powe                | r-up      | Brown-out        | Wake-up from |  |

|-----------------------|---------------------|-----------|------------------|--------------|--|

| tion                  | <b>PWRTE</b> = 0    | PWRTE = 1 | Brown-out        | SLEEP        |  |

| XT, HS, LP            | 72 ms +<br>1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                    | 72 ms               | —         | 72 ms            | —            |  |

#### TABLE 10-3 TIME-OUT IN VARIOUS SITUATIONS

#### TABLE 10-4 STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | х   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | x  | x  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

### TABLE 10-5 RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

# FIGURE 10-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

## FIGURE 10-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

### FIGURE 10-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

#### 10.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

#### 10.13.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. SSP (Start/Stop) bit detect interrupt.

- 3. SSP transmit or receive in slave mode (SPI/l<sup>2</sup>C).

- 4. CCP capture mode interrupt.

- 5. A/D conversion (when A/D clock source is RC).

- 6. Special event trigger (Timer1 in asynchronous mode using an external clock).

Other peripherals cannot generate interrupts since during SLEEP, no on-chip clocks are present.

When the **SLEEP** instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 10.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

• If the interrupt occurs before the execution of a

SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

· If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the  $\overline{\text{TO}}$  bit will be set and the  $\overline{\text{PD}}$  bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

|                                      | Q1 Q2 Q3 Q4     |              | Q1 Q2 Q3 Q4  | Q1 Q2 Q3 Q4                           | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 |

|--------------------------------------|-----------------|--------------|--------------|---------------------------------------|-------------|-------------|

|                                      |                 |              |              |                                       |             |             |

|                                      | /               | Tost(2)      |              | ،<br>۱                                |             |             |

| INT pin                              | 1               |              |              | 1 1<br>1 1                            |             |             |

| INTF flag                            | 1               | Δ,           |              | Interrupt Latency                     |             |             |

| (INTCOŇ<1>)                          | +               | /            |              | (Note 2)                              |             |             |

| GIE bit                              | <u> </u>        | Processor in |              |                                       | 1           |             |

| (INTCON<7>)                          | r <b>∢</b><br>' | SLEEP        |              | 1 I                                   | 1           |             |

| INSTRUCTION FLOW                     | 1               |              |              | i i<br>i i                            | 1           |             |

| PC X PC X                            | PC+1 X          | PC+2         | PC+2         | X PC + 2                              | 0004h       | 0005h       |

| Instruction { Inst(PC) = SLEEP       | Inst(PC + 1)    | 1            | Inst(PC + 2) | · · · · · · · · · · · · · · · · · · · | Inst(0004h) | Inst(0005h) |

| Instruction<br>executed Inst(PC - 1) | SLEEP           | 1            | Inst(PC + 1) | Dummy cycle                           | Dummy cycle | Inst(0004h) |

#### FIGURE 10-14: WAKE-UP FROM SLEEP THROUGH INTERRUPT

- 3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

CLKOUT is not available in these osc modes, but shown here for timing reference.

### 10.14 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

### 10.15 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

#### In-Circuit Serial Programming<sup>™</sup> 10.16

PIC16CXXX family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For complete details of serial programming, please refer to the In-Circuit Serial Programming (ICSP™) Guide, DS30277.

# 11.0 INSTRUCTION SET SUMMARY

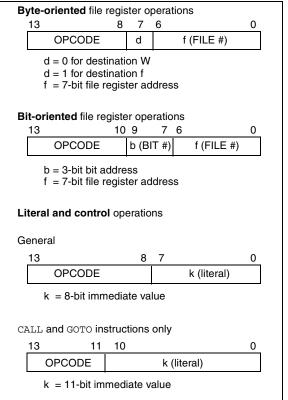

Each PIC16CXXX family instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXXX family instruction set summary in Table 11-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 11-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

# TABLE 11-1OPCODE FIELD<br/>DESCRIPTIONS

| Field | Description                                                                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                        |

| W     | Working register (accumulator)                                                                                                                                              |

| b     | Bit address within an 8-bit file register                                                                                                                                   |

| k     | Literal field, constant data or label                                                                                                                                       |

| x     | Don't care location (= 0 or 1)<br>The assembler will generate code with x = 0. It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                |

| PC    | Program Counter                                                                                                                                                             |

| TO    | Time-out bit                                                                                                                                                                |

| PD    | Power-down bit                                                                                                                                                              |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- **Bit-oriented** operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Table 11-2 lists the instructions recognized by the MPASM assembler.

Figure 11-1 shows the general formats that the instructions can have.

| Note: | То   | maintain  | upward   | compatibility         | with |

|-------|------|-----------|----------|-----------------------|------|

|       | futu | re PIC160 | CXXX pro | oducts, <u>do not</u> | use  |

|       | the  | OPTION a  | nd TRIS  | instructions.         |      |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

### FIGURE 11-1: GENERAL FORMAT FOR INSTRUCTIONS

A description of each instruction is available in the  $PIC^{\mathbb{R}}$ Mid-Range MCU Family Reference Manual, DS33023.

| Param<br>No. | Sym                   | Characteristic                             | Min      | Тур† | Max | Units | Conditions |

|--------------|-----------------------|--------------------------------------------|----------|------|-----|-------|------------|

| 70           | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                  | Тсү      | -    | —   | ns    |            |

| 71           | TscH                  | SCK input high time (slave mode)           | Tcy + 20 | _    | —   | ns    |            |

| 72           | TscL                  | SCK input low time (slave mode)            | TCY + 20 | —    | _   | ns    |            |

| 73           | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge   | 50       | -    | —   | ns    |            |

| 74           | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge    | 50       | -    | -   | ns    |            |

| 75           | TdoR                  | SDO data output rise time                  | _        | 10   | 25  | ns    |            |

| 76           | TdoF                  | SDO data output fall time                  | —        | 10   | 25  | ns    |            |

| 77           | TssH2doZ              | SS <sup>↑</sup> to SDO output hi-impedance | 10       | -    | 50  | ns    |            |

| 78           | TscR                  | SCK output rise time (master mode)         | _        | 10   | 25  | ns    |            |

| 79           | TscF                  | SCK output fall time (master mode)         | —        | 10   | 25  | ns    |            |

| 80           | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge       | —        | _    | 50  | ns    |            |

TABLE 13-8

SPI SLAVE MODE REQUIREMENTS (CKE=0) - PIC16C72

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Parameter<br>No. | Sym                   | Characteristic                                                        | Min         | Тур† | Max | Units | Conditions |

|------------------|-----------------------|-----------------------------------------------------------------------|-------------|------|-----|-------|------------|

| 70*              | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсү         | —    | —   | ns    |            |

| 71*              | TscH                  | SCK input high time (slave mode)                                      | TCY + 20    | _    | _   | ns    |            |

| 72*              | TscL                  | SCK input low time (slave mode)                                       | TCY + 20    | _    | _   | ns    |            |

| 73*              | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge                              | 100         | _    | —   | ns    |            |

| 74*              | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                               | 100         | —    | —   | ns    |            |

| 75*              | TdoR                  | SDO data output rise time                                             | —           | 10   | 25  | ns    |            |

| 76*              | TdoF                  | SDO data output fall time                                             | —           | 10   | 25  | ns    |            |

| 77*              | TssH2doZ              | SS↑ to SDO output hi-impedance                                        | 10          | _    | 50  | ns    |            |

| 78*              | TscR                  | SCK output rise time (master mode)                                    | —           | 10   | 25  | ns    |            |

| 79*              | TscF                  | SCK output fall time (master mode)                                    | —           | 10   | 25  | ns    |            |

| 80*              | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                                  | —           | —    | 50  | ns    |            |

| 81*              | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK edge                                     | Тсү         | —    | —   | ns    |            |

| 82*              | TssL2doV              | SDO data output valid after $\overline{SS}\downarrow$ edge            | —           | _    | 50  | ns    |            |

| 83*              | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                   | 1.5TCY + 40 | _    | —   | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

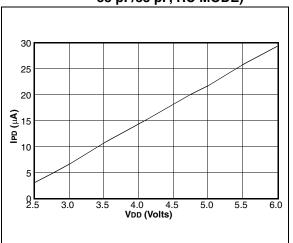

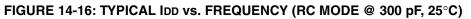

#### FIGURE 14-8: TYPICAL IPD vs. VDD BROWN-OUT DETECT ENABLED (RC MODE)

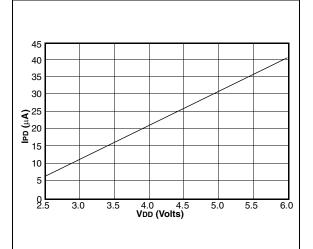

FIGURE 14-10: TYPICAL IPD vs. TIMER1 ENABLED (32 kHz, RC0/RC1 = 33 pF/33 pF, RC MODE)

#### FIGURE 14-11: MAXIMUM IPD vs. TIMER1 ENABLED (32 kHz, RC0/RC1 = 33 pF/33 pF, 85°C TO -40°C, RC MODE)

# PIC16C72 Series PIC16C72

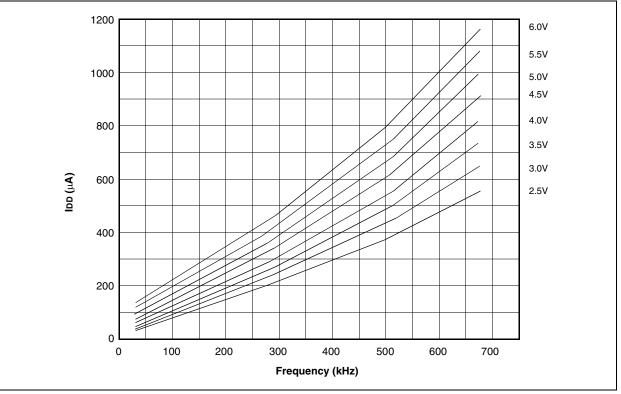

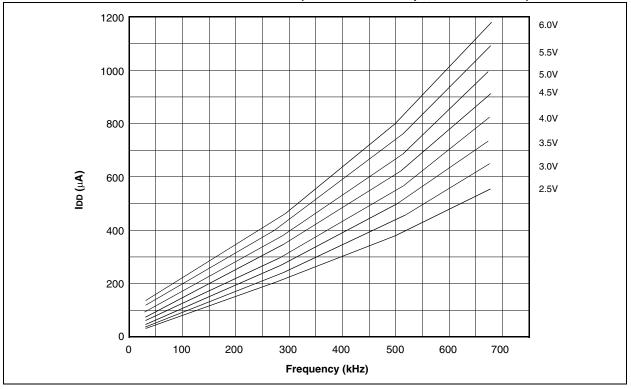

FIGURE 14-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

# READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE:                                      | Technical Publications Manager<br>Reader Response                                        | Total Pages Sent            |  |

|-------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------|--|

| Fror                                            | n: Name                                                                                  |                             |  |

|                                                 | Company                                                                                  |                             |  |

|                                                 | Address                                                                                  |                             |  |

|                                                 | City / State / ZIP / Country                                                             |                             |  |

|                                                 | Telephone: ()                                                                            | FAX: ()                     |  |

| Application (optional):                         |                                                                                          |                             |  |

| Would you like a reply?YN                       |                                                                                          |                             |  |

|                                                 | ce: 24xx010                                                                              | Literature Number: DS39016B |  |

| Questions:                                      |                                                                                          |                             |  |

| 1. What are the best features of this document? |                                                                                          |                             |  |

|                                                 |                                                                                          |                             |  |

| 2.                                              | . How does this document meet your hardware and software development needs?              |                             |  |

|                                                 |                                                                                          |                             |  |

| 3.                                              | Do you find the organization of this document easy to follow? If not, why?               |                             |  |

|                                                 |                                                                                          |                             |  |

| 4.                                              | What additions to the document do you think would enhance the structure and subject?     |                             |  |

|                                                 |                                                                                          |                             |  |

| 5.                                              | What deletions from the document could be made without affecting the overall usefulness? |                             |  |

|                                                 |                                                                                          |                             |  |

| 6.                                              | Is there any incorrect or misleading information (what and where)?                       |                             |  |

|                                                 |                                                                                          |                             |  |

| 7.                                              | How would you improve this document?                                                     |                             |  |

|                                                 |                                                                                          |                             |  |

|                                                 |                                                                                          |                             |  |