Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I²C, SPI                                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | A/D 5x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc72t-04i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 2-5: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0  | B/W-0                                                                                                                                      | B/W-0                                       | B/W-0        | B/W-0                                    | R/W-0                            | R/W-0       | R/W-x        |                                                                                                                      |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------|------------------------------------------|----------------------------------|-------------|--------------|----------------------------------------------------------------------------------------------------------------------|

| GIE    | PEIE                                                                                                                                       | TOIE                                        | INTE         | RBIE                                     | TOIF                             | INTF        | RBIF         | R = Readable bit                                                                                                     |

| bit7   |                                                                                                                                            |                                             |              |                                          |                                  |             | bitO         | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |

| bit 7: | 1 = Enab                                                                                                                                   | oal Interru<br>les all un-r<br>les all inte | nasked in    |                                          |                                  |             |              |                                                                                                                      |

| bit 6: | 1 = Enab                                                                                                                                   | ripheral In<br>les all un-r<br>les all per  | nasked pe    | eripheral ir                             | nterrupts                        |             |              |                                                                                                                      |

| bit 5: | 1 = Enab                                                                                                                                   | R0 Overflo<br>les the TN<br>les the TN      | IR0 interru  |                                          | bit                              |             |              |                                                                                                                      |

| bit 4: | INTE: RB0/INT External Interrupt Enable bit<br>1 = Enables the RB0/INT external interrupt<br>0 = Disables the RB0/INT external interrupt   |                                             |              |                                          |                                  |             |              |                                                                                                                      |

| bit 3: | <b>RBIE</b> : RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt |                                             |              |                                          |                                  |             |              |                                                                                                                      |

| bit 2: | 1 = TMR0                                                                                                                                   | R0 Overflo<br>) register I<br>) register o  | nas overflo  | owed (mus                                | t be cleare                      | d in softwa | ire)         |                                                                                                                      |

| bit 1: | 1 = The F                                                                                                                                  | RB0/INT ex                                  | cternal inte | rupt Flag b<br>errupt occi<br>errupt did | urred (must                      | be cleare   | d in softwar | e)                                                                                                                   |

| bit 0: | 1 = At lea                                                                                                                                 | st one of                                   | the RB7:R    |                                          | it<br>nanged stat<br>anged state |             | e cleared in | software)                                                                                                            |

|        |                                                                                                                                            |                                             |              |                                          |                                  |             |              |                                                                                                                      |

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### EXAMPLE 2-1: INDIRECT ADDRESSING

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDR register now will return the value of 0Ah.

**Direct Addressing** Indirect Addressing RP1:RP0 from opcode 7 6 0 IRP FSR register 0 (2) (2)bank select location select bank select location select • 00 01 10 11 00h 80h 100h 180h not used (3) (3) Data Memory(1) FFh 1FFh 7Fh 17Fh Bank 0 Bank 1 Bank 2 Bank 3 Note 1: For register file map detail see Figure 2-2. 2: Maintain RP1 and IRP as clear for upward compatibility with future products. 3: Not implemented.

#### FIGURE 2-11: DIRECT/INDIRECT ADDRESSING

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | movwf<br>clrf<br>incf | FSR<br>INDF<br>FSR | ;clear INDF register<br>;inc pointer |

|----------|-----------------------|--------------------|--------------------------------------|

|          | goto                  | -                  | ;all done?<br>;NO, clear next        |

| CONTINUE |                       |                    |                                      |

|          | :                     |                    | ;YES, continue                       |

## 3.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> Mid-Range MCU Reference Manual, DS33023.

#### 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, i.e., put the contents of the output latch on the selected pin.

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, these pins are con-  |

|-------|-------------------------------------------|

|       | figured as analog inputs and read as '0'. |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

EXAMPLE 3-1: INITIALIZING PORTA

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| CLRF  | PORTA   |     | ; | Initialize PORTA by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISA   |     | ; | Set RA<3:0> as inputs |

|       |         |     | ; | RA<5:4> as outputs    |

|       |         |     | ; | TRISA<7:6> are always |

|       |         |     | ; | read as '0'.          |

|       |         |     |   |                       |

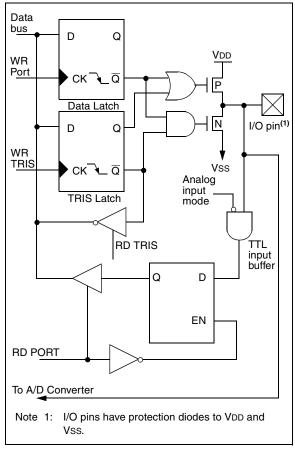

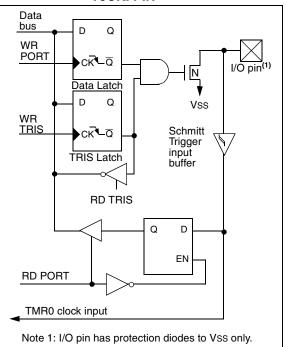

#### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

#### FIGURE 3-2: BLOCK DIAGRAM OF RA4/ T0CKI PIN

# **PIC16C72 Series**

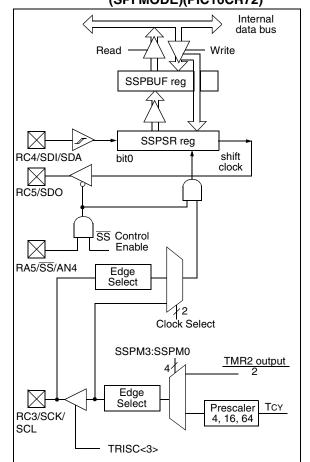

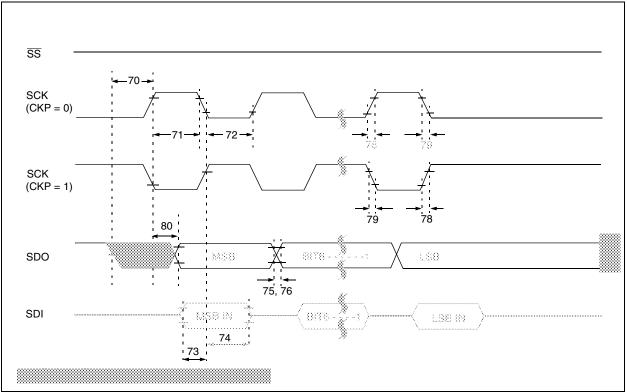

#### 8.2 SPI Mode for PIC16C72

Γ

This section contains register definitions and operational characteristics of the SPI module on the PIC16C72 device only. Additional information on SPI operation may be found in the PIC<sup>®</sup> Mid-Range MCU Reference Manual, DS33023.

1

## FIGURE 8-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h) (PIC16C72)

| U-0      | U-0                                                                                                                                                                                                                                                                                            | R-0                        | R-0                                     | R-0                      | R-0                            | R-0                       | R-0                          |                                                                                      |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------|--------------------------|--------------------------------|---------------------------|------------------------------|--------------------------------------------------------------------------------------|--|--|

|          | —                                                                                                                                                                                                                                                                                              | D/A                        | Р                                       | S                        | R/W                            | UA                        | BF                           | R = Readable bit                                                                     |  |  |

| bit7     |                                                                                                                                                                                                                                                                                                |                            |                                         |                          |                                |                           | bitO                         | W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |  |  |

| bit 7-6: | Unimpl                                                                                                                                                                                                                                                                                         | emented                    | : Read as                               | '0'                      |                                |                           |                              |                                                                                      |  |  |

| bit 5:   | 1 = Indi<br>0 = Indi                                                                                                                                                                                                                                                                           | cates that<br>cates that   | the last b<br>the last b                | yte receive              | d or transmit<br>d or transmit | ted was ad                | dress                        |                                                                                      |  |  |

| bit 4:   | 1 = Indi                                                                                                                                                                                                                                                                                       | cates that                 | node only.<br>a stop bit<br>not detecte | has been                 | cleared wher<br>detected last  | the SSP n<br>(this bit is | nodule is dis<br>'0' on RESE | abled, SSPEN is cleared)<br>T)                                                       |  |  |

| bit 3:   | <b>S</b> : Start bit ( $I^2C$ mode only. This bit is cleared when the SSP module is disabled, SSPEN is cleared)<br>1 = Indicates that a start bit has been detected last (this bit is '0' on RESET)<br>0 = Start bit was not detected last                                                     |                            |                                         |                          |                                |                           |                              |                                                                                      |  |  |

| bit 2:   | <b>R</b> / $\overline{W}$ : Read/Write bit information (I <sup>2</sup> C mode only)<br>This bit holds the R/W bit information following the last address match. This bit is valid from the address<br>match to the next start bit, stop bit, or $\overline{ACK}$ bit.<br>1 = Read<br>0 = Write |                            |                                         |                          |                                |                           |                              |                                                                                      |  |  |

| bit 1:   | <b>UA</b> : Update Address (10-bit I <sup>2</sup> C mode only)<br>1 = Indicates that the user needs to update the address in the SSPADD register<br>0 = Address does not need to be updated                                                                                                    |                            |                                         |                          |                                |                           |                              |                                                                                      |  |  |

| bit 0:   | BF: Buf                                                                                                                                                                                                                                                                                        | BF: Buffer Full Status bit |                                         |                          |                                |                           |                              |                                                                                      |  |  |

|          | <u>Receive</u> (SPI and I <sup>2</sup> C modes)<br>1 = Receive complete, SSPBUF is full<br>0 = Receive not complete, SSPBUF is empty                                                                                                                                                           |                            |                                         |                          |                                |                           |                              |                                                                                      |  |  |

|          | 1 = Trar                                                                                                                                                                                                                                                                                       |                            | ogress, S                               | SPBUF is f<br>PBUF is en |                                |                           |                              |                                                                                      |  |  |

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally a fourth pin may be used when in a slave mode of operation:

Slave Select (SS) RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master Operation (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock Edge (Output data on rising/falling edge of SCK)

- Clock Rate (master operation only)

- Slave Select Mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON register, and then set bit SSPEN. This configures the SDI, SDO, SCK, and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (master operation) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set

| Note: | When the SPI is in Slave Mode with $\overline{SS}$ pin      |

|-------|-------------------------------------------------------------|

|       | control enabled, (SSPCON<3:0> = 0100)                       |

|       | the SPI module will reset if the $\overline{SS}$ pin is set |

|       | to VDD.                                                     |

Note: If the SPI is used in Slave Mode with CKE = '1', then the  $\overline{SS}$  pin control must be enabled.

#### FIGURE 8-6: SSP BLOCK DIAGRAM (SPI MODE)(PIC16CR72)

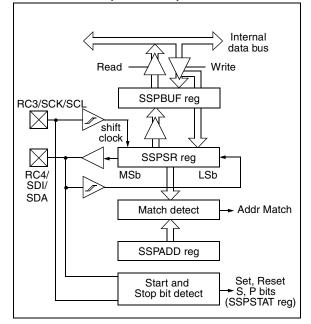

## 8.4 <u>SSP I<sup>2</sup>C Operation</u>

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/ SCK/SCL pin, which is the clock (SCL), and the RC4/ SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>).

FIGURE 8-7: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $I^2C$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Firmware controlled master operation, slave is idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

Additional information on SSP I<sup>2</sup>C operation may be found in the PIC<sup>®</sup> Mid-Range MCU Reference Manual, DS33023.

8.4.1 SLAVE MODE

In slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched or the data transfer after an address match is received, the hardware automatically will generate the acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this  $\overline{\text{ACK}}$  pulse. These are if either (or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 8-3 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register while bit SSPOV is cleared through software.

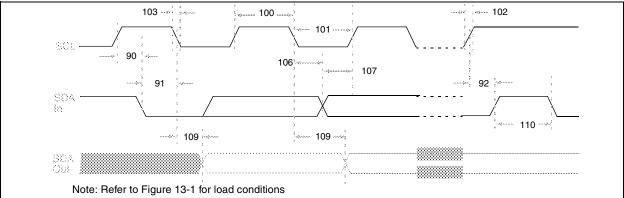

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification as well as the requirement of the SSP module is shown in timing parameter #100 and parameter #101.

NOTES:

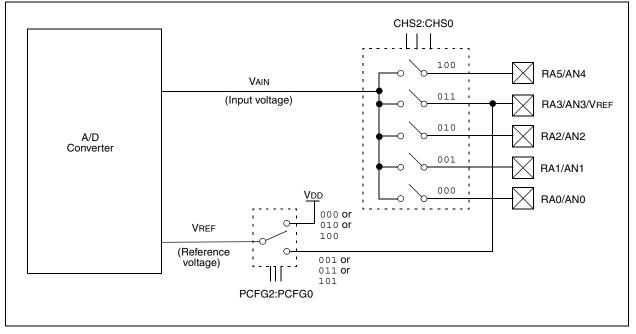

## 9.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The analog-to-digital (A/D) converter module has five inputs for the PIC16C72/R72.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

Additional information on the A/D module is available in the PIC<sup>®</sup> Mid-Range MCU Reference Manual, DS33023.

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The ADCON0 register, shown in Figure 9-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 9-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0    | R/W-0                                                                                                                                                                                       | R/W-0                  | R/W-0      | R/W-0 | R/W-0                                | U-0       | R/W-0     |                                                                                       |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|-------|--------------------------------------|-----------|-----------|---------------------------------------------------------------------------------------|--|

| ADCS1    | ADCS0                                                                                                                                                                                       | CHS2                   | CHS1       | CHS0  | GO/DONE                              |           | ADON      | R = Readable bit                                                                      |  |

| bit7     |                                                                                                                                                                                             |                        |            |       |                                      |           | bitO      | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |

| bit 7-6: | ADCS1:ADCS0: A/D Conversion Clock Select bits<br>00 = Fosc/2<br>01 = Fosc/8<br>10 = Fosc/32<br>11 = FRC (clock derived from an internal RC oscillator)                                      |                        |            |       |                                      |           |           |                                                                                       |  |

| bit 5-3: | CHS2:CHS0: Analog Channel Select bits<br>000 = channel 0, (RA0/AN0)<br>001 = channel 1, (RA1/AN1)<br>010 = channel 2, (RA2/AN2)<br>011 = channel 3, (RA3/AN3)<br>100 = channel 4, (RA5/AN4) |                        |            |       |                                      |           |           |                                                                                       |  |

| bit 2:   | GO/DONE: A/D Conversion Status bit                                                                                                                                                          |                        |            |       |                                      |           |           |                                                                                       |  |

|          |                                                                                                                                                                                             | onversion<br>onversion |            | · ·   | this bit starts t<br>bit is automati |           | ,         | are when the A/D conversion                                                           |  |

| bit 1:   | Unimpler                                                                                                                                                                                    | nented: F              | Read as '0 |       |                                      |           |           |                                                                                       |  |

| bit 0:   | <b>ADON</b> : A<br>1 = A/D c<br>0 = A/D c                                                                                                                                                   | onverter n             |            |       | l consumes no                        | operating | g current |                                                                                       |  |

## FIGURE 9-1: ADCON0 REGISTER (ADDRESS 1Fh)

The ADRES register contains the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRES register, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 9-3.

The value that is in the ADRES register is not modified for a Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 9.1. After this acquisition time has elapsed the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins / voltage reference / and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

#### FIGURE 9-3: A/D BLOCK DIAGRAM

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared OR

- Waiting for the A/D interrupt

- 6. Read A/D Result register (ADRES), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

#### 10.2 Oscillator Configurations

#### 10.2.1 OSCILLATOR TYPES

The PIC16CXXX family can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

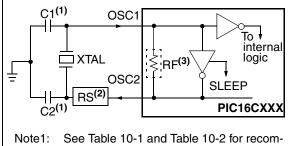

## 10.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

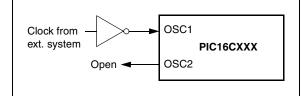

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 10-2). The PIC16CXXX family oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/ CLKIN pin (Figure 10-3).

#### FIGURE 10-2: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

- mended values of C1 and C2. 2: A series resistor (RS) may be required for

- AT strip cut crystals. 3: BE varies with the crystal chosen

- 3: RF varies with the crystal chosen.

#### FIGURE 10-3: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

#### TABLE 10-1 CERAMIC RESONATORS

| Ranges Tested: |      |      |  |  |  |  |

|----------------|------|------|--|--|--|--|

| Mode           | Freq | OSC1 |  |  |  |  |

| Mode                                                                    | Freq                          | OSC1        | OSC2        |  |  |  |

|-------------------------------------------------------------------------|-------------------------------|-------------|-------------|--|--|--|

| XT                                                                      | 455 kHz                       | 68 - 100 pF | 68 - 100 pF |  |  |  |

|                                                                         | 2.0 MHz                       | 15 - 68 pF  | 15 - 68 pF  |  |  |  |

|                                                                         | 4.0 MHz                       | 15 - 68 pF  | 15 - 68 pF  |  |  |  |

| HS                                                                      | 8.0 MHz                       | 10 - 68 pF  | 10 - 68 pF  |  |  |  |

|                                                                         | 16.0 MHz                      | 10 - 22 pF  | 10 - 22 pF  |  |  |  |

| These values are for design guidance only. See notes at bottom of page. |                               |             |             |  |  |  |

| Resonator                                                               | Resonators Used:              |             |             |  |  |  |

| 455 kHz                                                                 | Panasonic EFO-A455K04B ± 0.3% |             |             |  |  |  |

| 2.0 MHz                                                                 | Murata Erie CSA2.00MG ± 0.5%  |             |             |  |  |  |

| 4.0 MHz                                                                 | Murata Erie CSA4.00MG ± 0.5%  |             |             |  |  |  |

| 8.0 MHz                                                                 | Murata Erie                   | CSA8.00MT   | $\pm 0.5\%$ |  |  |  |

| 16.0 MHz                                                                | Murata Erie                   | CSA16.00MX  | ± 0.5%      |  |  |  |

All resonators used did not have built-in capacitors.

# TABLE 10-2CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|-----------------|------------------|------------------|

| LP       | 32 kHz          | 33 pF            | 33 pF            |

|          | 200 kHz         | 15 pF            | 15 pF            |

| ХТ       | 200 kHz         | 47-68 pF         | 47-68 pF         |

|          | 1 MHz           | 15 pF            | 15 pF            |

|          | 4 MHz           | 15 pF            | 15 pF            |

| HS       | 4 MHz           | 15 pF            | 15 pF            |

|          | 8 MHz           | 15-33 pF         | 15-33 pF         |

|          | 20 MHz          | 15-33 pF         | 15-33 pF         |

|          | -               |                  |                  |

These values are for design guidance only. See notes at bottom of page.

| Crystals Used |                        |          |  |  |  |  |

|---------------|------------------------|----------|--|--|--|--|

| 32 kHz        | Epson C-001R32.768K-A  | ± 20 PPM |  |  |  |  |

| 200 kHz       | STD XTL 200.000KHz     | ± 20 PPM |  |  |  |  |

| 1 MHz         | ECS ECS-10-13-1        | ± 50 PPM |  |  |  |  |

| 4 MHz         | ECS ECS-40-20-1        | ± 50 PPM |  |  |  |  |

| 8 MHz         | EPSON CA-301 8.000M-C  | ± 30 PPM |  |  |  |  |

| 20 MHz        | EPSON CA-301 20.000M-C | ± 30 PPM |  |  |  |  |

Note 1: Recommended values of C1 and C2 are identical to the ranges tested (Table 10-1).

- 2: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification.

#### 10.8 <u>Time-out Sequence</u>

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 10-7, Figure 10-8, Figure 10-9 and Figure 10-10 depict timeout sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 10-9). This is useful for testing purposes or to synchronize more than one PIC16CXXX family device operating in parallel.

Table 10-5 shows the reset conditions for some special function registers, while Table 10-6 shows the reset conditions for all the registers.

#### 10.9 <u>Power Control/Status Register</u> (PCON)

The Power Control/Status Register, PCON has up to two bits, depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent resets to see if bit BOR cleared, indicating a BOR occurred. The BOR bit is a "Don't Care" bit and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word).

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Oscillator Configura- | Powe                | r-up     | Brown-out        | Wake-up from |  |

|-----------------------|---------------------|----------|------------------|--------------|--|

| tion                  | PWRTE = 0PWRTE = 1  |          | Brown-out        | SLEEP        |  |

| XT, HS, LP            | 72 ms +<br>1024Tosc | 1024Tosc | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                    | 72 ms               | —        | 72 ms            | —            |  |

#### TABLE 10-3 TIME-OUT IN VARIOUS SITUATIONS

#### TABLE 10-4 STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD |                                                         |  |

|-----|-----|----|----|---------------------------------------------------------|--|

| 0   | x   | 1  | 1  | Power-on Reset                                          |  |

| 0   | x   | 0  | x  | llegal, TO is set on POR                                |  |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |  |

| 1   | 0   | x  | x  | Brown-out Reset                                         |  |

| 1   | 1   | 0  | 1  | WDT Reset                                               |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |  |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |

#### TABLE 10-5 RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

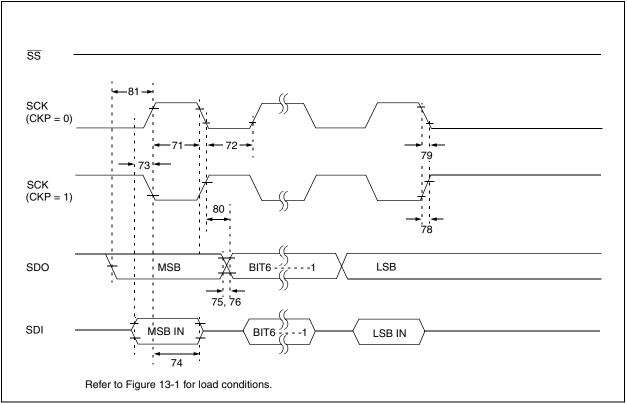

FIGURE 13-8: SPI MASTER OPERATION TIMING (CKE = 0)

© 1998-2013 Microchip Technology Inc.

## FIGURE 13-13: I<sup>2</sup>C BUS DATA TIMING

#### TABLE 13-11 I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter<br>No. | Sym     | Characte                   | eristic      | Min        | Max  | Units | Conditions                                      |  |

|------------------|---------|----------------------------|--------------|------------|------|-------|-------------------------------------------------|--|

| 100              | Тнідн   | Clock high time            | 100 kHz mode | 4.0        | _    | μs    | Device must operate at a mir<br>mum of 1.5 MHz  |  |

|                  |         |                            | 400 kHz mode | 0.6        | _    | μs    | Device must operate at a mini-<br>mum of 10 MHz |  |

|                  |         |                            | SSP Module   | 1.5Tcy     | —    |       |                                                 |  |

| 101              | TLOW    | Clock low time             | 100 kHz mode | 4.7        | _    | μs    | Device must operate at a mini<br>mum of 1.5 MHz |  |

|                  |         |                            | 400 kHz mode | 1.3        | _    | μS    | Device must operate at a mini<br>mum of 10 MHz  |  |

|                  |         |                            | SSP Module   | 1.5TCY     |      |       |                                                 |  |

| 102              | TR      | SDA and SCL rise           | 100 kHz mode | —          | 1000 | ns    |                                                 |  |

|                  |         | time                       | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF      |  |

| 103              | TF      | SDA and SCL fall time      | 100 kHz mode | —          | 300  | ns    |                                                 |  |

|                  |         |                            | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF      |  |

| 90               | TSU:STA | START condition setup time | 100 kHz mode | 4.7        |      | μs    | Only relevant for repeated START condition      |  |

|                  |         |                            | 400 kHz mode | 0.6        |      | μs    |                                                 |  |

| 91               | THD:STA | START condition hold time  | 100 kHz mode | 4.0        |      | μs    | After this period the first clo                 |  |

|                  |         |                            | 400 kHz mode | 0.6        | _    | μs    | pulse is generated                              |  |

| 106              | THD:DAT | Data input hold time       | 100 kHz mode | 0          | —    | ns    |                                                 |  |

|                  |         |                            | 400 kHz mode | 0          | 0.9  | μS    |                                                 |  |

| 107              | TSU:DAT | Data input setup time      | 100 kHz mode | 250        |      | ns    | Note 2                                          |  |

|                  |         |                            | 400 kHz mode | 100        |      | ns    |                                                 |  |

| 92               | Tsu:sto | STOP condition setup       | 100 kHz mode | 4.7        | —    | μs    |                                                 |  |

|                  |         | time                       | 400 kHz mode | 0.6        | —    | μs    |                                                 |  |

| 109              | ΤΑΑ     | Output valid from          | 100 kHz mode | —          | 3500 | ns    | Note 1                                          |  |

|                  |         | clock                      | 400 kHz mode | —          | _    | ns    |                                                 |  |

| 110              | TBUF    | Bus free time              | 100 kHz mode | 4.7        | —    | μs    | Time the bus must be free                       |  |

|                  |         |                            | 400 kHz mode | 1.3        | _    | μs    | before a new transmission car start             |  |

|                  | Cb      | Bus capacitive loading     |              | —          | 400  | pF    |                                                 |  |

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

Note 2: A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz)S I<sup>2</sup>C-bus system, but the requirement tsu;DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

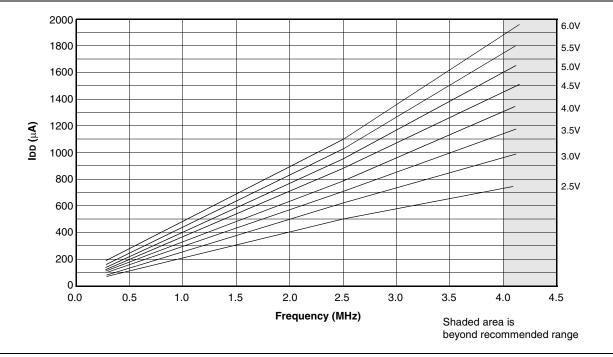

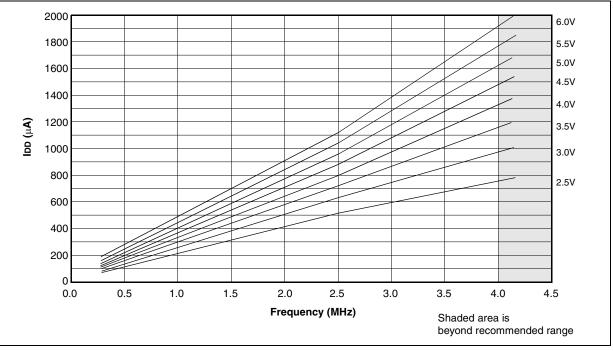

## FIGURE 14-12: TYPICAL IDD vs. FREQUENCY (RC MODE @ 22 pF, 25°C)

NOTES:

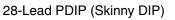

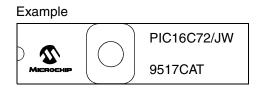

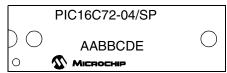

## 16.0 PACKAGING INFORMATION

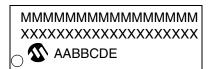

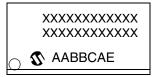

## 16.1 Package Marking Information

28-Lead Side Brazed Skinny Windowed

#### Example

#### 28-Lead SOIC

#### 28-Lead SSOP

## Example

### Example

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                        | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ł       | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                              |  |  |

© 1998-2013 Microchip Technology Inc.

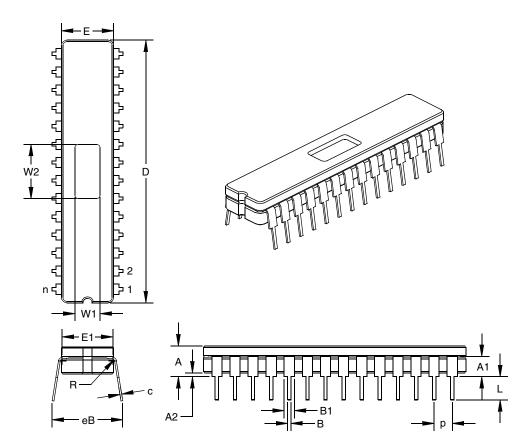

#### 16.2 <u>28-Lead Ceramic Side Brazed Dual In-Line with Window (300 mil)(JW)</u>

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                        |    | INCHES* |       |       | М     | ILLIMETERS | 6     |

|------------------------------|----|---------|-------|-------|-------|------------|-------|

| Dimension Limits             |    | MIN     | NOM   | MAX   | MIN   | NOM        | MAX   |

| PCB Row Spacing              |    |         | 0.300 |       |       | 7.62       |       |

| Number of Pins               | n  |         | 28    |       |       | 28         |       |

| Pitch                        | р  | 0.098   | 0.100 | 0.102 | 2.49  | 2.54       | 2.59  |

| Lower Lead Width             | В  | 0.016   | 0.019 | 0.021 | 0.41  | 0.47       | 0.53  |

| Upper Lead Width             | B1 | 0.050   | 0.058 | 0.065 | 1.27  | 1.46       | 1.65  |

| Shoulder Radius              | R  | 0.010   | 0.013 | 0.015 | 0.25  | 0.32       | 0.38  |

| Lead Thickness               | С  | 0.008   | 0.010 | 0.012 | 0.20  | 0.25       | 0.30  |

| Top to Seating Plane         | А  | 0.170   | 0.183 | 0.195 | 4.32  | 4.64       | 4.95  |

| Top of Lead to Seating Plane | A1 | 0.107   | 0.125 | 0.143 | 2.72  | 3.18       | 3.63  |

| Base to Seating Plane        | A2 | 0.015   | 0.023 | 0.030 | 0.00  | 0.57       | 0.76  |

| Tip to Seating Plane         | L  | 0.135   | 0.140 | 0.145 | 3.43  | 3.56       | 3.68  |

| Package Length               | D  | 1.430   | 1.458 | 1.485 | 36.32 | 37.02      | 37.72 |

| Package Width                | Е  | 0.285   | 0.290 | 0.295 | 7.24  | 7.37       | 7.49  |

| Radius to Radius Width       | E1 | 0.255   | 0.270 | 0.285 | 6.48  | 6.86       | 7.24  |

| Overall Row Spacing          | eB | 0.345   | 0.385 | 0.425 | 8.76  | 9.78       | 10.80 |

| Window Width                 | W1 | 0.130   | 0.140 | 0.150 | 0.13  | 0.14       | 0.15  |

| Window Length                | W2 | 0.290   | 0.300 | 0.310 | 0.29  | 0.3        | 0.31  |

\* Controlling Parameter.

NOTES:

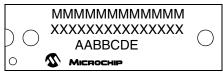

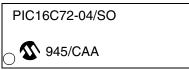

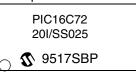

## PIC16C72 SERIES PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.         | $\overline{\uparrow}$ $\overline{\uparrow}$ $\overline{\uparrow}$ $\overline{\uparrow}$ $\overline{-}$                                                                                                                       | Examples:         a)       PIC16C72 -04/P 301 = Commercial temp.,<br>PDIP package, 4 MHz, normal VDD limits, QTP<br>pattern #301.         b)       PIC16LC72 - 04I/SO = Industrial temp., SOIC                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device           | PIC16C72 <sup>(1)</sup> , PIC16C72T <sup>(2)</sup><br>PIC16LC72 <sup>(1)</sup> , PIC16LC72T <sup>(2)</sup><br>PIC16CR72 <sup>(1)</sup> , PIC16CR72T <sup>(2)</sup><br>PIC16LCR72 <sup>(1)</sup> , PIC16LCR72T <sup>(2)</sup> | <ul> <li>c) PIC16C072 - 04//SO = Industrial territy., SOIC package, 200 kHz, Extended VDD limits.</li> <li>c) PIC16CR72 - 10I/P = ROM program memory, Industrial temp., PDIP package, 10MHz, normal VDD limits.</li> </ul> |

| Frequency Range  | 02 = 2 MHz<br>04 = 4 MHz<br>10 = 10 MHz<br>20 = 20 MHz                                                                                                                                                                       | Note 1: C= CMOS<br>CR= CMOS ROM<br>LC= Low Power CMOS<br>LCR= ROM Version, Extended Vdd range<br>2: T = in tape and reel - SOIC, SSOP pack-                                                                                |

| Temperature Rang | $ b^{(3)} = 0^{\circ}C \text{ to } 70^{\circ}C \text{ (Commercial)}  I = -40^{\circ}C \text{ to } +85^{\circ}C \text{ (Industrial)}  E = -40^{\circ}C \text{ to } +125^{\circ}C \text{ (Extended)} $                         | ages only.<br><b>3:</b> b = blank                                                                                                                                                                                          |

| Package          | JW = Ceramic Dual In-Line Package with Wi<br>SO = Small Outline - 300 mil<br>SP = Skinny PDIP<br>SS = Shrink Samll Outline Package - 209 m                                                                                   |                                                                                                                                                                                                                            |

| Pattern          | 3-digit Pattern Code for QTP, ROM (blank otherw                                                                                                                                                                              | ise)                                                                                                                                                                                                                       |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type (including LC devices).

## SALES AND SUPPORT

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office (see last page)

- 2. The Microchip's Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).

- Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.