# Altera - EP2A25F672C8 Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            |                                                           |

| Number of Logic Elements/Cells | -                                                         |

| Total RAM Bits                 |                                                           |

| Number of I/O                  | 492                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                           |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 672-BBGA, FCBGA                                           |

| Supplier Device Package        | 672-FBGA (27x27)                                          |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep2a25f672c8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 1. APEX II Device Features |           |           |           |           |

|----------------------------------|-----------|-----------|-----------|-----------|

| Feature                          | EP2A15    | EP2A25    | EP2A40    | EP2A70    |

| Maximum gates                    | 1,900,000 | 2,750,000 | 3,000,000 | 5,250,000 |

| Typical gates                    | 600,000   | 900,000   | 1,500,000 | 3,000,000 |

| LEs                              | 16,640    | 24,320    | 38,400    | 67,200    |

| RAM ESBs                         | 104       | 152       | 160       | 280       |

| Maximum RAM bits                 | 425,984   | 622,592   | 655,360   | 1,146,880 |

| True-LVDS channels               | 36 (1)    | 36 (1)    | 36 (1)    | 36 (1)    |

| Flexible-LVDS™ channels (2)      | 56        | 56        | 88        | 88        |

| True-LVDS PLLs (3)               | 4         | 4         | 4         | 4         |

| General-purpose PLL outputs (4)  | 8         | 8         | 8         | 8         |

| Maximum user I/O pins            | 492       | 612       | 735       | 1,060     |

### Notes to Table 1:

(1) Each device has 36 input channels and 36 output channels.

(2) EP2A15 and EP2A25 devices have 56 input and 56 output channels; EP2A40 and EP2A70 devices have 88 input and 88 output channels.

(3) PLL: phase-locked loop. True-LVDS PLLs are dedicated to implement True-LVDS functionality.

(4) Two internal outputs per PLL are available. Additionally, the device has one external output per PLL pair (two external outputs per device).

# ...and More Features

### I/O features

- Up to 380 Gbps of I/O capability

- 1-Gbps True-LVDS, LVPECL, PCML, and HyperTransport support on 36 input and 36 output channels that feature clock synchronization circuitry and independent clock multiplication and serialization/deserialization factors

- Common networking and communications bus I/O standards such as RapidIO, CSIX, Utopia IV, and POS-PHY Level 4 enabled

- 400-megabits per second (Mbps) Flexible-LVDS and HyperTransport support on up to 88 input and 88 output channels (input channels also support LVPECL)

- Support for high-speed external memories, including ZBT, QDR, and DDR SRAM, and SDR and DDR SDRAM

- Compliant with peripheral component interconnect Special Interest Group (PCI SIG) *PCI Local Bus Specification, Revision 2.2* for 3.3-V operation at 33 or 66 MHz and 32 or 64 bits

- Compliant with 133-MHz PCI-X specifications

- Support for other advanced I/O standards, including AGP, CTT, SSTL-3 and SSTL-2 Class I and II, GTL+, and HSTL Class I and II

- Six dedicated registers in each I/O element (IOE): two input registers, two output registers, and two output-enable registers

- Programmable bus hold feature

- Programmable pull-up resistor on I/O pins available during user mode

# General Description

APEX II devices integrate high-speed differential I/O support using the True-LVDS interface. The dedicated serializer, deserializer, and CDS circuitry in the True-LVDS interface support the LVDS, LVPECL, HyperTransport, and PCML I/O standards. Flexible-LVDS pins located in regular user I/O banks offer additional differential support, increasing the total device bandwidth. This circuitry, together with enhanced IOEs and support for numerous I/O standards, allows APEX II devices to meet high-speed interface requirements.

APEX II devices also include other high-performance features such as bidirectional dual-port RAM, CAM, general-purpose PLLs, and numerous global clocks.

# Configuration

The logic, circuitry, and interconnects in the APEX II architecture are configured with CMOS SRAM elements. APEX II devices are reconfigurable and are 100% tested prior to shipment. As a result, test vectors do not have to be generated for fault coverage. Instead, the designer can focus on simulation and design verification. In addition, the designer does not need to manage inventories of different ASIC designs; APEX II devices can be configured on the board for the specific functionality required.

APEX II devices are configured at system power-up with data either stored in an Altera configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable configuration devices, which configure APEX II devices via a serial data stream. The enhanced configuration devices can configure any APEX II device in under 100 ms. Moreover, APEX II devices contain an optimized interface that permits microprocessors to configure APEX II devices serially or in parallel, synchronously or asynchronously. This interface also enables microprocessors to treat APEX II devices as memory and to configure the device by writing to a virtual memory location, simplifying reconfiguration.

APEX II devices also support a new byte-wide, synchronous configuration scheme at speeds of up to 66 MHz using EPC16 configuration devices or a microprocessor. This parallel configuration reduces configuration time by using eight data lines to send configuration data versus one data line in serial configuration.

APEX II devices support multi-voltage configuration; device configuration can be performed at 3.3 V and 2.5 V or 1.8 V.

After an APEX II device has been configured, it can be reconfigured incircuit by resetting the device and loading new data. Real-time changes can be made during system operation, enabling innovative reconfigurable computing applications.

## Software

APEX II devices are supported by the Altera Quartus II development system: a single, integrated package that offers hardware description language (HDL) and schematic design entry, compilation and logic synthesis, full simulation and worst-case timing analysis, SignalTap logic analysis, and device configuration. The Quartus II software runs on Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800 workstations.

The Quartus II software includes the LogicLock incremental design feature. The LogicLock feature allows the designer to make pin and timing assignments, verify functionality and performance, and then set constraints to lock down the placement and performance of a specific block of logic using LogicLock constraints. Constraints set by the LogicLock function guarantee repeatable placement when implementing a block of logic in a current project or exporting the block to another project. The constraints set by the LogicLock feature can lock down logic to a fixed location in the device. The LogicLock feature can also lock the logic down to a floating location, and the Quartus II software determines the best relative placement of the block to meet design requirements. Adding additional logic to a project will not affect the performance of blocks locked down with LogicLock constraints.

The Quartus II software provides NativeLink interfaces to other industrystandard PC- and UNIX workstation-based EDA tools. For example, designers can open the Quartus II software from within third-party design tools. The Quartus II software also contains built-in optimized synthesis libraries; synthesis tools can use these libraries to optimize designs for APEX II devices. For example, the Synopsys Design Compiler library, supplied with the Quartus II development system, includes DesignWare functions optimized for the APEX II architecture.

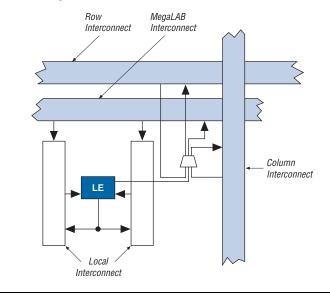

Functional<br/>DescriptionAPEX II devices incorporate LUT-based logic, product-term-based logic,<br/>memory, and high-speed I/O standards into one device. Signal<br/>interconnections within APEX II devices (as well as to and from device<br/>pins) are provided by the FastTrack interconnect—a series of fast,<br/>continuous row and column channels that run the entire length and width<br/>of the device.

Each I/O pin is fed by an IOE located at the end of each row and column of the FastTrack interconnect. Each IOE contains a bidirectional I/O buffer and six registers that can be used for registering input, output, and output-enable signals. When used with a dedicated clock pin, these registers provide exceptional performance and interface support with external memory devices such as DDR SDRAM and ZBT and QDR SRAM devices.

IOEs provide a variety of features such as: 3.3-V, 64-bit, 66-MHz PCI compliance, 3.3-V, 64-bit, 133-MHz PCI-X compliance, Joint Test Action Group (JTAG) boundary-scan test (BST) support, output drive strength control, slew-rate control, tri-state buffers, bus-hold circuitry, programmable pull-up resistors, programmable input and output delays, and open-drain outputs.

APEX II devices offer enhanced I/O support, including support for 1.5 V, 1.8 V, 2.5 V, 3.3 V, LVCMOS, LVTTL, HSTL, LVDS, LVPECL, HyperTransport, PCML, 3.3-V PCI, PCI-X, GTL+, SSTL-2, SSTL-3, CTT, and 3.3-V AGP I/O standards. High-speed (up to 1.0 Gbps) differential transfers are supported with True-LVDS circuitry for LVDS, LVPECL, HyperTransport, and PCML I/O standards. The optional CDS feature corrects any clock-to-data skew at the True-LVDS receiver channels, allowing for flexible board topologies. Up to 88 Flexible-LVDS channels support differential transfer at up to 400 Mbps (DDR) for LVDS and HyperTransport I/O standards.

An ESB can implement many types of memory, including Dual-Port+ RAM, CAM, ROM, and FIFO functions. Embedding the memory directly into the die improves performance and reduces die area compared to distributed-RAM implementations. The abundance of cascadable ESBs ensures that the APEX II device can implement multiple wide memory blocks for high-density designs. The ESB's high speed ensures it can implement small memory blocks without any speed penalty. The abundance of ESBs, in conjunction with the ability for one ESB to implement two separate memory blocks, ensures that designers can create as many different-sized memory blocks as the system requires.

Figure 1 shows an overview of the APEX II device.

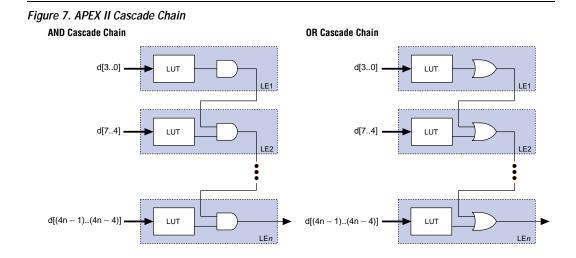

### Cascade Chain

With the cascade chain, the APEX II architecture can implement functions with a very wide fan-in. Adjacent LUTs can compute portions of a function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR (via DeMorgan's inversion) to connect the outputs of adjacent LEs. Each additional LE provides four more inputs to the effective width of a function, with a short cascade delay. The Quartus II Compiler can create cascade chain logic automatically during the design process, or the designer can create it manually during design entry.

Cascade chains longer than 10 LEs are implemented automatically by linking LABs together. For enhanced fitting, a long cascade chain skips alternate LABs in a MegaLAB structure. A cascade chain longer than one LAB skips either from an even-numbered LAB to the next even-numbered LAB, or from an odd-numbered LAB to the next odd-numbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure. Figure 7 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in.

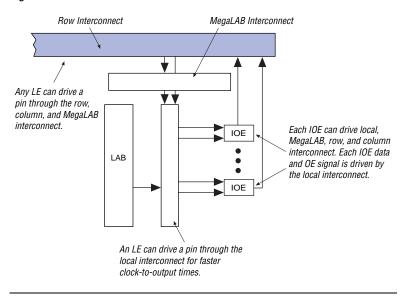

Figure 11. Driving the FastTrack Interconnect

APEX II devices feature FastRow<sup>TM</sup> lines for quickly routing input signals with high fan-out. Column I/O pins can drive the FastRow interconnect, which routes signals directly into the local interconnect without having to drive through the MegaLAB interconnect. FastRow lines traverse two MegaLAB structures. The FastRow interconnect drives the four MegaLABs in the top row and the four MegaLABs in the bottom row of the device. The FastRow interconnect drives all local interconnects in the appropriate MegaLABs. Column pins using the FastRow interconnect achieve a faster set-up time, because the signal does not need to use a MegaLab interconnect line to reach the destination LE. Figure 12 shows the FastRow interconnect.

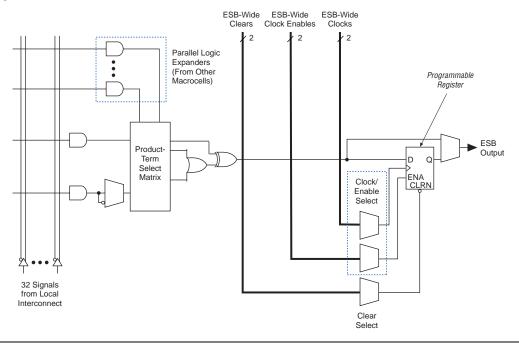

For registered functions, each macrocell register can be programmed individually to implement D, T, JK, or SR operation with programmable clock control. The register can be bypassed for combinatorial operation. During design entry, the designer specifies the desired register type; the Quartus II software then selects the most efficient register operation for each registered function to optimize resource utilization. The Quartus II software or other synthesis tools can also select the most efficient register operation automatically when synthesizing HDL designs.

Each programmable register can be clocked by one of two ESB-wide clocks. The ESB-wide clocks can be generated from device dedicated clock pins, global signals, or local interconnect. Each clock also has an associated clock enable, generated from the local interconnect. The clock and clock enable signals are related for a particular ESB; any macrocell using a clock also uses the associated clock enable.

If both the rising and falling edges of a clock are used in an ESB, both ESB-wide clock signals are used.

By combining multiple ESBs, the Quartus II software implements larger memory blocks automatically. For example, two  $256 \times 16$  RAM blocks can be combined to form a  $256 \times 32$  RAM block, and two  $512 \times 8$  RAM blocks can be combined to form a  $512 \times 16$  RAM block. Memory performance does not degrade for memory blocks up to 4,096 words deep. Each ESB can implement a 4,096-word-deep memory; the ESBs are used in parallel, eliminating the need for any external control logic that would increase delays. To create a high-speed memory block more than 4,096-words deep, the Quartus II software automatically combines ESBs with LE control logic.

# Input/Output Clock Mode

The ESB implements input/output clock mode for both dual-port and bidirectional dual-port memory. An ESB using input/output clock mode can use up to two clocks. On each of the two ports, A or B, one clock controls all registers for inputs into the ESB: data input, WREN, read address, and write address. The other clock controls the ESB data output registers. Each ESB port, A or B, also supports independent read clock enable, write clock enable, and asynchronous clear signals. Input/output clock mode is commonly used for applications where the reads and writes occur at the same system frequency, but require different clock enable signals for the input and output registers. Figure 19 shows the ESB in input/output clock mode.

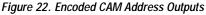

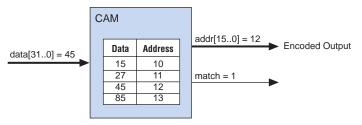

CAM can generate outputs in three different modes: single-match mode, multiple-match mode, and fast multiple-match mode. In each mode, the ESB outputs the matched data's location as an encoded or unencoded address. When encoded, the ESB outputs an encoded address of the data's location. For instance, if the data is located in address 12, the ESB output is 12. When unencoded, each ESB port uses its 16 outputs to show the location of the data over two clock cycles. In this case, if the data is located in address 12, the 12th output line goes high. Figures 21 and 22 show the encoded CAM outputs and unencoded CAM outputs, respectively.

### Notes to Figures 22 and 23:

- (1) For an unencoded output, the ESB only supports 31 input data bits. One input bit is used by the select line to choose one of the two banks of 16 outputs.

- (2) If the select input is a 1, then CAM outputs odd words between 1 through 15. If the select input is a 0, CAM outputs even words between 0 through 14.

In single-match mode, it takes two clock cycles to write into CAM, but only one clock cycle to read from CAM. In this mode, both encoded and unencoded outputs are available without external logic. Single-match mode is better suited for designs without duplicate data in the memory.

Figure 26. Row IOE Connection to the Interconnect

Figure 27 shows how a column IOE connects to the interconnect.

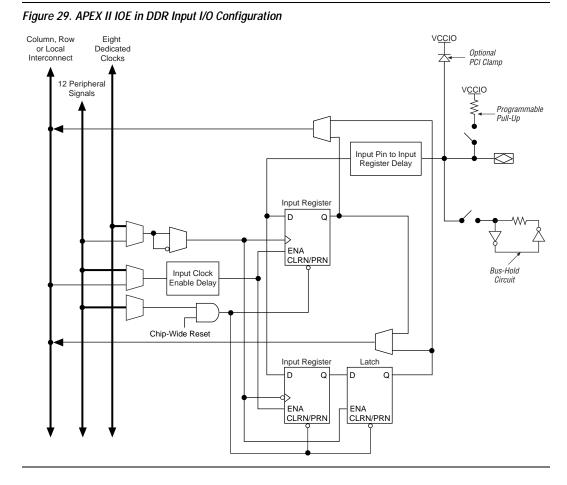

When using the IOE for DDR inputs, the two input registers are used to clock double rate input data on alternating edges. An input latch is also used within the IOE for DDR input acquisition. The latch holds the data that is present during the clock high times. This allows both bits of data to be synchronous to the same clock edge (either rising or falling). Figure 29 shows an IOE configured for DDR input.

When using the IOE for DDR outputs, the two output registers are configured to clock two data paths from LEs on rising clock edges. These register outputs are multiplexed by the clock to drive the output pin at a  $\times$ 2 rate. One output register clocks the first bit out on the clock high time, while the other output register clocks the second bit out on the clock low time. Figure 30 shows the IOE configured for DDR output.

Each bank can support multiple standards with the same  $V_{\rm CCIO}$  for input and output pins. Each bank can support one voltage-referenced I/O standard, but it can support multiple I/O standards with the same  $V_{\rm CCIO}$  voltage level. For example, when  $V_{\rm CCIO}$  is 3.3 V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs. When the True-LVDS banks are not used for LVDS I/O pins, they support all of the other I/O standards except HSTL Class II output.

# True-LVDS Interface

APEX II devices contain dedicated circuitry for supporting differential standards at speeds up to 1.0 Gbps. APEX II devices have dedicated differential buffers and circuitry to support LVDS, LVPECL, HyperTransport, and PCML I/O standards. Four dedicated high-speed PLLs (separate from the general-purpose PLLs) multiply reference clocks and drive high-speed differential serializer/deserializer channels. In addition, CDS circuitry at each receiver channel corrects any fixed clock-to-data skew. All APEX II devices support 36 input channels, 36 output channels, two dedicated receiver PLLs, and two dedicated transmitter PLLs.

The True-LVDS circuitry supports the following standards and applications:

- RapidIO

- POS-PHY Level 4

- Utopia IV

- HyperTransport

APEX II devices support source-synchronous interfacing with LVDS, LVPECL,PCML, or HyperTransport signaling at up to 1 Gbps. Serial channels are transmitted and received along with a low-speed clock. The receiving device then multiplies the clock by a factor of 1, 2, or 4 to 10. The serialization/deserialization rate can be any number from 1, 2, or 4 to 10 and does not have to equal the clock multiplication value.

For example, an 840-Mbps LVDS channel can be received along with an 84-MHz clock. The 84-MHz clock is multiplied by 10 to drive the serial shift register, but the register can be clocked out in parallel at 8- or 10-bits wide at 84 or 105 MHz. See Figures 32 and 33.

### Note to Figure 35:

(1) *n* represents the prescale divider for the PLL input. *m* represents the multiplier. *k* and *v* represent the different post scale dividers for the two possible PLL outputs. *m* and *k* are integers that range from 1 to 160. *n* and *v* are integers that range from 1 to 16.

## Advanced ClockBoost Multiplication & Division

APEX II PLLs include circuitry that provides clock synthesis for eight internal outputs and two external outputs using  $m/(n \times \text{output} \text{ divider})$  scaling. When a PLL is locked, the locked output clock aligns to the rising edge of the input clock. The closed loop equation for Figure 35 gives an output frequency  $f_{\text{clock0}} = (m/(n \times k))f_{\text{IN}}$  and  $f_{\text{clock1}} = (m/(n \times v))f_{\text{IN}}$ . These equations allow the multiplication or division of clocks by a programmable number. The Quartus II software automatically chooses the appropriate scaling factors according to the frequency, multiplication, and division values entered.

A single PLL in an APEX II device allows for multiple user-defined multiplication and division ratios that are not possible even with multiple delay-locked loops (DLLs). For example, if a frequency scaling factor of 3.75 is needed for a given input clock, a multiplication factor of 15 and a division factor of 4 can be entered. This advanced multiplication scaling can be performed with a single PLL, making it unnecessary to cascade PLL outputs.

## External Clock Outputs

APEX II devices have two low-jitter external clocks available for external clock sources. Other devices on the board can use these outputs as clock sources.

There are three modes for external clock outputs.

- Zero Delay Buffer: The external clock output pin is phase aligned with the clock input pin for zero delay. Multiplication, programmable phase shift, and time delay shift are not allowed in this configuration. The MegaWizard interface for altclklock should be used to verify possible clock settings.

- External Feedback: The external feedback input pin is phase aligned with clock input pin. By aligning these clocks, you can actively remove clock delay and skew between devices. This mode has the same restrictions as zero delay buffer mode.

- Normal Mode: The external clock output pin will have phase delay relative to the clock input pin. If an internal clock is used in this mode, the IOE register clock will be phase aligned to the input clock pin. Multiplication is allowed with the normal mode.

| Table 31. SSTL-2 Class I Specifications |                           |                                      |                         |                  |                         |       |  |  |  |

|-----------------------------------------|---------------------------|--------------------------------------|-------------------------|------------------|-------------------------|-------|--|--|--|

| Symbol                                  | Parameter                 | Conditions                           | Minimum                 | Typical          | Maximum                 | Units |  |  |  |

| V <sub>CCIO</sub>                       | Output supply voltage     |                                      | 2.375                   | 2.5              | 2.625                   | V     |  |  |  |

| V <sub>TT</sub>                         | Termination voltage       |                                      | V <sub>REF</sub> - 0.04 | V <sub>REF</sub> | V <sub>REF</sub> + 0.04 | V     |  |  |  |

| V <sub>REF</sub>                        | Reference voltage         |                                      | 1.15                    | 1.25             | 1.35                    | V     |  |  |  |

| V <sub>IH</sub>                         | High-level input voltage  |                                      | V <sub>REF</sub> + 0.18 |                  | 3.0                     | V     |  |  |  |

| V <sub>IL</sub>                         | Low-level input voltage   |                                      | -0.3                    |                  | V <sub>REF</sub> - 0.18 | V     |  |  |  |

| V <sub>OH</sub>                         | High-level output voltage | I <sub>OH</sub> = -7.6 mA<br>(10)    | V <sub>TT</sub> + 0.57  |                  |                         | V     |  |  |  |

| V <sub>OL</sub>                         | Low-level output voltage  | I <sub>OL</sub> = 7.6 mA <i>(10)</i> |                         |                  | V <sub>TT</sub> – 0.57  | V     |  |  |  |

# Table 32. SSTL-2 Class II Specifications

| Symbol            | Parameter                 | Conditions                         | Minimum                 | Typical          | Maximum                 | Units |

|-------------------|---------------------------|------------------------------------|-------------------------|------------------|-------------------------|-------|

| V <sub>CCIO</sub> | Output supply voltage     |                                    | 2.3                     | 2.5              | 2.7                     | V     |

| V <sub>TT</sub>   | Termination voltage       |                                    | $V_{REF} - 0.04$        | V <sub>REF</sub> | V <sub>REF</sub> + 0.04 | V     |

| V <sub>REF</sub>  | Reference voltage         |                                    | 1.15                    | 1.25             | 1.35                    | V     |

| V <sub>IH</sub>   | High-level input voltage  |                                    | V <sub>REF</sub> + 0.18 |                  | V <sub>CCIO</sub> + 0.3 | V     |

| V <sub>IL</sub>   | Low-level input voltage   |                                    | -0.3                    |                  | V <sub>REF</sub> - 0.18 | V     |

| V <sub>OH</sub>   | High-level output voltage | I <sub>OH</sub> = -15.2 mA<br>(10) | V <sub>TT</sub> + 0.76  |                  |                         | V     |

| V <sub>OL</sub>   | Low-level output voltage  | I <sub>OL</sub> = 15.2 mA<br>(10)  |                         |                  | V <sub>TT</sub> – 0.76  | V     |

| Symbol            | Parameter                 | Conditions                   | Minimum                | Typical          | Maximum                 | Units |

|-------------------|---------------------------|------------------------------|------------------------|------------------|-------------------------|-------|

| V <sub>CCIO</sub> | Output supply voltage     |                              | 3.0                    | 3.3              | 3.6                     | V     |

| V <sub>TT</sub>   | Termination voltage       |                              | $V_{REF} - 0.05$       | V <sub>REF</sub> | V <sub>REF</sub> + 0.05 | V     |

| V <sub>REF</sub>  | Reference voltage         |                              | 1.3                    | 1.5              | 1.7                     | V     |

| V <sub>IH</sub>   | High-level input voltage  |                              | V <sub>REF</sub> + 0.2 |                  | $V_{CCIO} + 0.3$        | V     |

| V <sub>IL</sub>   | Low-level input voltage   |                              | -0.3                   |                  | V <sub>REF</sub> - 0.2  | V     |

| V <sub>OH</sub>   | High-level output voltage | I <sub>OH</sub> = -8 mA (10) | V <sub>TT</sub> + 0.6  |                  |                         | V     |

| V <sub>OL</sub>   | Low-level output voltage  | I <sub>OL</sub> = 8 mA (10)  |                        |                  | V <sub>TT</sub> – 0.6   | V     |

| Table 40. C                       | CTT I/O Specifications                                 |                                               |                        |         |                        |       |

|-----------------------------------|--------------------------------------------------------|-----------------------------------------------|------------------------|---------|------------------------|-------|

| Symbol                            | Parameter                                              | Conditions                                    | Minimum                | Typical | Maximum                | Units |

| V <sub>CCIO</sub>                 | Output supply voltage                                  |                                               | 3.0                    | 3.3     | 3.6                    | V     |

| V <sub>TT</sub> /V <sub>REF</sub> | Termination and input reference voltage                |                                               | 1.35                   | 1.5     | 1.65                   | V     |

| V <sub>IH</sub>                   | High-level input voltage                               |                                               | V <sub>REF</sub> + 0.2 |         |                        | V     |

| V <sub>IL</sub>                   | Low-level input voltage                                |                                               |                        |         | V <sub>REF</sub> - 0.2 | V     |

| I <sub>I</sub>                    | Input pin leakage current                              | $0 < V_{IN} < V_{CCIO}$                       | -10                    |         | 10                     | μA    |

| V <sub>OH</sub>                   | High-level output voltage                              | I <sub>OH</sub> = -8 mA                       | V <sub>REF</sub> + 0.4 |         |                        | V     |

| V <sub>OL</sub>                   | Low-level output voltage                               | I <sub>OL</sub> = 8 mA                        |                        |         | V <sub>REF</sub> - 0.4 | V     |

| Ι <sub>Ο</sub>                    | Output leakage current (when output is high <i>Z</i> ) | GND ð V <sub>OUT</sub> ð<br>V <sub>CCIO</sub> | -10                    |         | 10                     | μA    |

| Parameter                  | Conditions                                     |       | V <sub>CCIO</sub> Level |       |      |       |      |       |      |    |

|----------------------------|------------------------------------------------|-------|-------------------------|-------|------|-------|------|-------|------|----|

|                            |                                                | 1.5 V |                         | 1.8 V |      | 2.5 V |      | 3.3 V |      | 1  |

|                            |                                                | Min   | Max                     | Min   | Max  | Min   | Max  | Min   | Мах  |    |

| Low sustaining<br>current  | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) |       |                         | 30    |      | 50    |      | 70    |      | μA |

| High sustaining<br>current | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) |       |                         | -30   |      | -50   |      | -70   |      | μA |

| Low overdrive current      | 0 V < V <sub>IN</sub> <<br>V <sub>CCIO</sub>   |       |                         |       | 200  |       | 300  |       | 500  | μA |

| High overdrive<br>current  | 0 V < V <sub>IN</sub> <<br>V <sub>CCIO</sub>   |       |                         |       | -200 |       | -300 |       | -500 | μA |

### Notes to Tables 20 - 41:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 20 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2 V or overshoot to 4.6 V for input currents less than 100 mA and periods shorter than 20 ns.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) V<sub>CCIO</sub> maximum and minimum conditions for LVPECL, LVDS, RapidIO, and PCML are shown in parentheses.

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before  $V_{CCINT}$  and  $V_{CCIO}$  are powered.

- (7) Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 1.5$  V, and  $V_{CCIO} = 1.5$  V, 1.8 V, 2.5 V, and 3.3 V.

- (8) This value is specified for normal device operation. The value may vary during power-up.

- (9) Pin pull-up resistance values will lower if an external source drives the pin higher than  $V_{CCIO}$ .

- (10) Drive strength is programmable according to values in Table 9 on page 48.

- (11)  $V_{REF}$  specifies the center point of the switching range.

| Symbol            | Parameter                                                                | Conditions              | Minimum | Typical | Maximum | Units |

|-------------------|--------------------------------------------------------------------------|-------------------------|---------|---------|---------|-------|

| V <sub>CCIO</sub> | I/O supply voltage                                                       |                         | 3.135   | 3.3     | 3.465   | V     |

| V <sub>OD</sub>   | Differential output voltage                                              | R <sub>L</sub> = 100 Ω  | 250     |         | 850 (1) | mV    |

| $\Delta V_{OD}$   | Change in V <sub>OD</sub> between high and low                           | R <sub>L</sub> = 100 Ω  |         |         | 50      | mV    |

| V <sub>OS</sub>   | Output Offset voltage                                                    | R <sub>L</sub> = 100 Ω  | 1.125   | 1.25    | 1.375   | V     |

| $\Delta V_{OS}$   | Change in V <sub>OS</sub> between high and low                           | R <sub>L</sub> = 100 Ω  |         |         | 50      | mV    |

| V <sub>TH</sub>   | Differential input threshold                                             | V <sub>CM</sub> = 1.2 V | -100    |         | 100     | mV    |

| V <sub>IN</sub>   | Receiver input voltage range                                             |                         | 0.0     |         | 2.4     | V     |

| R <sub>L</sub>    | Receiver differential input<br>resistor (external to<br>APEX II devices) |                         | 90      | 100     | 110     | Ω     |

| Symbol            | Parameter                            | Conditions | Minimum                    | Typical           | Maximum                    | Units |

|-------------------|--------------------------------------|------------|----------------------------|-------------------|----------------------------|-------|

| V <sub>CCIO</sub> | I/O supply voltage                   |            | 3.135                      | 3.3               | 3.465                      | V     |

| V <sub>IL</sub>   | Low-level input voltage              |            |                            |                   | V <sub>CCIO</sub> –<br>0.3 | V     |

| V <sub>IH</sub>   | High-level input voltage             |            | V <sub>CCIO</sub>          |                   |                            | V     |

| V <sub>OL</sub>   | Low-level output voltage             |            | V <sub>CCIO</sub> –<br>0.6 |                   | V <sub>CCIO</sub> –<br>0.3 | V     |

| V <sub>OH</sub>   | High-level output voltage            |            | V <sub>CCIO</sub>          |                   | V <sub>CCIO</sub> –<br>0.3 | V     |

| V <sub>T</sub>    | Output termination voltage           |            |                            | V <sub>CCIO</sub> |                            | V     |

| V <sub>OD</sub>   | Differential output voltage          |            | 300                        | 450               | 600                        | mV    |

| t <sub>R</sub>    | Rise time (20 to 80%)                |            | 85                         |                   | 325                        | ps    |

| t <sub>F</sub>    | Fall time (20 to 80%)                |            | 85                         |                   | 325                        | ps    |

| R <sub>O</sub>    | Output load                          |            |                            | 100               |                            | Ω     |

| RL                | Receiver differential input resistor |            | 45                         | 50                | 55                         | Ω     |

| Table 49. APEX II f <sub>MAX</sub> Routing Delays |                                                                                                                              |  |  |  |  |  |  |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Symbol                                            | Parameter                                                                                                                    |  |  |  |  |  |  |

| t <sub>F1-4</sub>                                 | Fan-out delay estimate using local interconnect; use to estimate routing delay for a signal with fan-out of 1 to 4           |  |  |  |  |  |  |

| t <sub>F5-20</sub>                                | Fan-out delay estimate using MegaLab interconnect; use to estimate routing delay for a signal with fan-out of 5 to 20        |  |  |  |  |  |  |

| t <sub>F20+</sub>                                 | Fan-out delay estimate using FastTrack interconnect; use to estimate routing delay for a signal with fan-out greater than 20 |  |  |  |  |  |  |

| Table 57. EP2A25        | f <sub>MAX</sub> ESB Timil | ng Paramete | rs      |                |        |                |    |  |

|-------------------------|----------------------------|-------------|---------|----------------|--------|----------------|----|--|

| Symbol                  | -7 Speed Grade             |             | -8 Spee | -8 Speed Grade |        | -9 Speed Grade |    |  |

|                         | Min                        | Мах         | Min     | Мах            | Min    | Мах            |    |  |

| t <sub>ESBARC</sub>     |                            | 1.28        |         | 1.47           |        | 1.69           | ns |  |

| t <sub>ESBSRC</sub>     |                            | 2.49        |         | 2.86           |        | 3.29           | ns |  |

| t <sub>ESBAWC</sub>     |                            | 2.20        |         | 2.53           |        | 2.91           | ns |  |

| t <sub>ESBSWC</sub>     |                            | 3.02        |         | 3.47           |        | 3.99           | ns |  |

| t <sub>ESBWASU</sub>    | 0.07                       |             | 0.07    |                | 0.09   |                | ns |  |

| t <sub>ESBWAH</sub>     | 0.15                       |             | 0.18    |                | 0.20   |                | ns |  |

| t <sub>ESBWDSU</sub>    | 0.37                       |             | 0.43    |                | 0.49   |                | ns |  |

| t <sub>ESBWDH</sub>     | 0.16                       |             | 0.18    |                | 0.21   |                | ns |  |

| t <sub>ESBRASU</sub>    | 0.84                       |             | 0.96    |                | 1.11   |                | ns |  |

| t <sub>ESBRAH</sub>     | 0.00                       |             | 0.00    |                | 0.00   |                | ns |  |

| t <sub>ESBWESU</sub>    | 0.14                       |             | 0.16    |                | 0.19   |                | ns |  |

| t <sub>ESBDATASU</sub>  | - 0.02                     |             | - 0.03  |                | - 0.03 |                | ns |  |

| t <sub>ESBWADDRSU</sub> | - 0.40                     |             | - 0.46  |                | - 0.53 |                | ns |  |

| t <sub>ESBRADDRSU</sub> | - 0.38                     |             | - 0.44  |                | - 0.51 |                | ns |  |

| t <sub>ESBDATAC01</sub> |                            | 1.30        |         | 1.50           |        | 1.72           | ns |  |

| t <sub>ESBDATACO2</sub> |                            | 1.84        |         | 2.12           |        | 2.44           | ns |  |

| t <sub>ESBDD</sub>      |                            | 2.42        |         | 2.78           |        | 3.19           | ns |  |

| t <sub>PD</sub>         |                            | 1.69        |         | 1.94           |        | 2.23           | ns |  |

| t <sub>PTERMSU</sub>    | 1.10                       |             | 1.26    |                | 1.45   |                | ns |  |

| t <sub>PTERMCO</sub>    |                            | 0.82        |         | 0.94           |        | 1.08           | ns |  |

| Table 58. EP2A25 f <sub>MAX</sub> Routing Delays |                |     |                |     |                |     |      |  |

|--------------------------------------------------|----------------|-----|----------------|-----|----------------|-----|------|--|

| Symbol                                           | -7 Speed Grade |     | -8 Speed Grade |     | -9 Speed Grade |     | Unit |  |

|                                                  | Min            | Max | Min            | Max | Min            | Max |      |  |

| t <sub>F1-4</sub>                                | 0.19           |     | 0.21           |     | 0.25           |     | ns   |  |

| t <sub>F5-20</sub>                               | 0.65           |     | 0.75           |     | 0.86           |     | ns   |  |

| t <sub>F20+</sub>                                | 1.11           |     | 1.27           |     | 1.46           |     | ns   |  |

| Symbol             | -7 Speed Grade |      | -8 Speed Grade |      | -9 Speed Grade |      | Unit |

|--------------------|----------------|------|----------------|------|----------------|------|------|

|                    | Min            | Мах  | Min            | Мах  | Min            | Max  | 1    |

| t <sub>INSU</sub>  | 2.27           |      | 2.45           |      | 2.64           |      | ns   |

| t <sub>INH</sub>   | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| <sup>t</sup> оитсо | 2.00           | 4.57 | 2.00           | 4.89 | 2.00           | 5.24 | ns   |

| t <sub>xz</sub>    |                | 5.87 |                | 6.42 |                | 7.01 | ns   |

| t <sub>zx</sub>    |                | 5.87 |                | 6.42 |                | 7.01 | ns   |

| tINSUPLL           | 1.23           |      | 1.35           |      | 1.47           |      | ns   |

|                    | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| toutcopll          | 0.50           | 2.89 | 0.50           | 3.10 | 0.50           | 3.33 | ns   |

| t <sub>XZPLL</sub> |                | 4.18 |                | 4.62 |                | 5.09 | ns   |

| tZXPLL             |                | 4.18 | İ              | 4.62 |                | 5.09 | ns   |

| Table 72. EP2A        | 40 External T  | iming Parame | eters for Row  | I/O Pins |                |      |      |

|-----------------------|----------------|--------------|----------------|----------|----------------|------|------|

| Symbol                | -7 Speed Grade |              | -8 Speed Grade |          | -9 Speed Grade |      | Unit |

|                       | Min            | Max          | Min            | Max      | Min            | Мах  | 1    |

| t <sub>INSU</sub>     | 1.57           |              | 1.72           |          | 1.88           |      | ns   |

| t <sub>INH</sub>      | 0.00           |              | 0.00           |          | 0.00           |      | ns   |

| t <sub>оитсо</sub>    | 2.00           | 4.90         | 2.00           | 5.24     | 2.00           | 5.61 | ns   |

| t <sub>xz</sub>       |                | 6.47         |                | 6.98     |                | 7.53 | ns   |

| t <sub>ZX</sub>       |                | 6.47         |                | 6.98     |                | 7.53 | ns   |

|                       | 1.15           |              | 1.26           |          | 1.38           |      | ns   |

| t <sub>INHPLL</sub>   | 0.00           |              | 0.00           |          | 0.00           |      | ns   |

| t <sub>OUTCOPLL</sub> | 0.50           | 2.60         | 0.50           | 2.82     | 0.50           | 3.06 | ns   |

| t <sub>XZPLL</sub>    |                | 4.17         |                | 4.56     |                | 4.97 | ns   |

| t <sub>ZXPLL</sub>    |                | 4.17         |                | 4.56     |                | 4.97 | ns   |

| Table 75. EP2A        | 70 External Ti | ming Parame | eters for Colu | mn I/O Pins |                |      |      |

|-----------------------|----------------|-------------|----------------|-------------|----------------|------|------|

| Symbol                | -7 Speed Grade |             | -8 Speed Grade |             | -9 Speed Grade |      | Unit |

|                       | Min            | Мах         | Min            | Мах         | Min            | Max  | 1    |

| t <sub>INSU</sub>     | 2.79           |             | 2.99           |             | 3.22           |      | ns   |

| t <sub>INH</sub>      | 0.00           |             | 0.00           |             | 0.00           |      | ns   |

| t <sub>оитсо</sub>    | 2.00           | 4.91        | 2.00           | 5.24        | 2.00           | 5.60 | ns   |

| t <sub>XZ</sub>       |                | 6.16        |                | 6.71        |                | 7.32 | ns   |

| t <sub>ZX</sub>       |                | 6.16        |                | 6.71        |                | 7.32 | ns   |

| tINSUPLL              | 1.19           |             | 1.30           |             | 1.43           |      | ns   |

| t <sub>INHPLL</sub>   | 0.00           |             | 0.00           |             | 0.00           |      | ns   |

| t <sub>OUTCOPLL</sub> | 0.50           | 2.67        | 0.50           | 2.86        | 0.50           | 3.08 | ns   |

| t <sub>XZPLL</sub>    |                | 3.92        |                | 4.34        |                | 4.79 | ns   |

| t <sub>ZXPLL</sub>    |                | 3.92        |                | 4.34        |                | 4.79 | ns   |