## Intel - EP2A40F1020I8 Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                 |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 3840                                                     |

| Number of Logic Elements/Cells | 38400                                                    |

| Total RAM Bits                 | 655360                                                   |

| Number of I/O                  | 735                                                      |

| Number of Gates                | 3000000                                                  |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 1020-BBGA                                                |

| Supplier Device Package        | 1020-FBGA (33x33)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2a40f1020i8 |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 1. APEX II Device Features |           |           |           |           |

|----------------------------------|-----------|-----------|-----------|-----------|

| Feature                          | EP2A15    | EP2A25    | EP2A40    | EP2A70    |

| Maximum gates                    | 1,900,000 | 2,750,000 | 3,000,000 | 5,250,000 |

| Typical gates                    | 600,000   | 900,000   | 1,500,000 | 3,000,000 |

| LEs                              | 16,640    | 24,320    | 38,400    | 67,200    |

| RAM ESBs                         | 104       | 152       | 160       | 280       |

| Maximum RAM bits                 | 425,984   | 622,592   | 655,360   | 1,146,880 |

| True-LVDS channels               | 36 (1)    | 36 (1)    | 36 (1)    | 36 (1)    |

| Flexible-LVDS™ channels (2)      | 56        | 56        | 88        | 88        |

| True-LVDS PLLs (3)               | 4         | 4         | 4         | 4         |

| General-purpose PLL outputs (4)  | 8         | 8         | 8         | 8         |

| Maximum user I/O pins            | 492       | 612       | 735       | 1,060     |

#### Notes to Table 1:

(1) Each device has 36 input channels and 36 output channels.

(2) EP2A15 and EP2A25 devices have 56 input and 56 output channels; EP2A40 and EP2A70 devices have 88 input and 88 output channels.

(3) PLL: phase-locked loop. True-LVDS PLLs are dedicated to implement True-LVDS functionality.

(4) Two internal outputs per PLL are available. Additionally, the device has one external output per PLL pair (two external outputs per device).

# ...and More Features

#### I/O features

- Up to 380 Gbps of I/O capability

- 1-Gbps True-LVDS, LVPECL, PCML, and HyperTransport support on 36 input and 36 output channels that feature clock synchronization circuitry and independent clock multiplication and serialization/deserialization factors

- Common networking and communications bus I/O standards such as RapidIO, CSIX, Utopia IV, and POS-PHY Level 4 enabled

- 400-megabits per second (Mbps) Flexible-LVDS and HyperTransport support on up to 88 input and 88 output channels (input channels also support LVPECL)

- Support for high-speed external memories, including ZBT, QDR, and DDR SRAM, and SDR and DDR SDRAM

- Compliant with peripheral component interconnect Special Interest Group (PCI SIG) *PCI Local Bus Specification, Revision 2.2* for 3.3-V operation at 33 or 66 MHz and 32 or 64 bits

- Compliant with 133-MHz PCI-X specifications

- Support for other advanced I/O standards, including AGP, CTT, SSTL-3 and SSTL-2 Class I and II, GTL+, and HSTL Class I and II

- Six dedicated registers in each I/O element (IOE): two input registers, two output registers, and two output-enable registers

- Programmable bus hold feature

- Programmable pull-up resistor on I/O pins available during user mode

#### Normal Mode

The normal mode is suitable for general logic applications, combinatorial functions, or wide decoding functions that can take advantage of a cascade chain. In normal mode, four data inputs from the LAB local interconnect and the carry-in are inputs to a four-input LUT. The Quartus II Compiler automatically selects the carry-in or the DATA3 signal as one of the inputs to the LUT. The LUT output can be combined with the cascade-in signal to form a cascade chain through the cascade-out signal. LEs in normal mode support packed registers.

#### **Arithmetic Mode**

The arithmetic mode is ideal for implementing adders, accumulators, and comparators. An LE in arithmetic mode uses two 3-input LUTs. One LUT computes a three-input function; the other generates a carry output. As shown in Figure 8, the first LUT uses the carry-in signal and two data inputs from the LAB local interconnect to generate a combinatorial or registered output. For example, when implementing an adder, this output is the sum of three signals: DATA1, DATA2, and carry-in. The second LUT uses the same three signals to generate a carry-out signal, thereby creating a carry chain. The arithmetic mode also supports simultaneous use of the cascade chain. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The Quartus II software implements parameterized functions that use the arithmetic mode automatically where appropriate; the designer does not need to specify how the carry chain will be used.

#### **Counter Mode**

The counter mode offers clock enable, counter enable, synchronous up/down control, synchronous clear, and synchronous load options. The counter enable and synchronous up/down control signals are generated from the data inputs of the LAB local interconnect. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. Consequently, if any of the LEs in an LAB use the counter mode, other LEs in that LAB must be used as part of the same counter or be used for a combinatorial function. The Quartus II software automatically places any registers that are not used by the counter into other LABs.

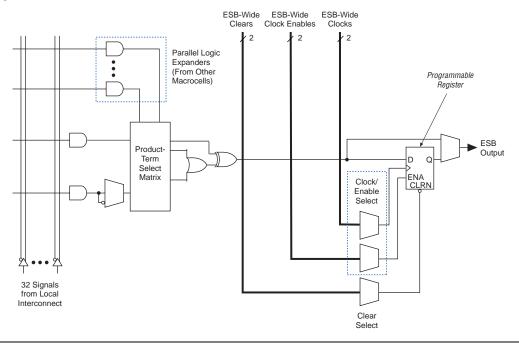

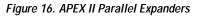

For registered functions, each macrocell register can be programmed individually to implement D, T, JK, or SR operation with programmable clock control. The register can be bypassed for combinatorial operation. During design entry, the designer specifies the desired register type; the Quartus II software then selects the most efficient register operation for each registered function to optimize resource utilization. The Quartus II software or other synthesis tools can also select the most efficient register operation automatically when synthesizing HDL designs.

Each programmable register can be clocked by one of two ESB-wide clocks. The ESB-wide clocks can be generated from device dedicated clock pins, global signals, or local interconnect. Each clock also has an associated clock enable, generated from the local interconnect. The clock and clock enable signals are related for a particular ESB; any macrocell using a clock also uses the associated clock enable.

If both the rising and falling edges of a clock are used in an ESB, both ESB-wide clock signals are used.

# Embedded System Block

The ESB can implement various types of memory blocks, including Dual-Port+ RAM (bidirectional dual-port RAM), dual- and single-port RAM, ROM, FIFO, and CAM blocks.

The ESB includes input and output registers; the input registers synchronize writes, and the output registers can pipeline designs to improve system performance. The ESB offers a bidirectional, dual-port mode, which supports any combination of two port operations: two reads, two writes, or one read and one write at two different clock frequencies. Figure 17 shows the ESB block diagram.

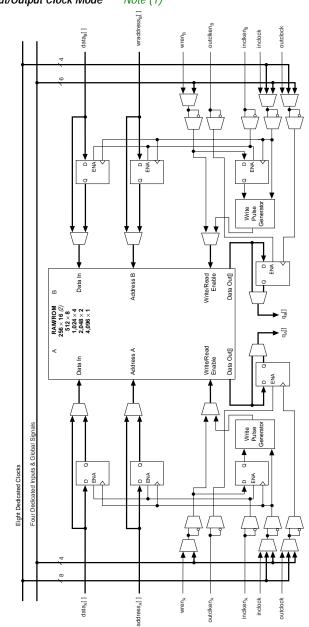

## Figure 19. ESB in Input/Output Clock Mode Note (1)

#### Notes to Figure 19:

- (1) All registers can be cleared asynchronously by ESB local interconnect signals, global signals, or the chip-wide reset.

- (2) This configuration is not supported for bidirectional dual-port configuration.

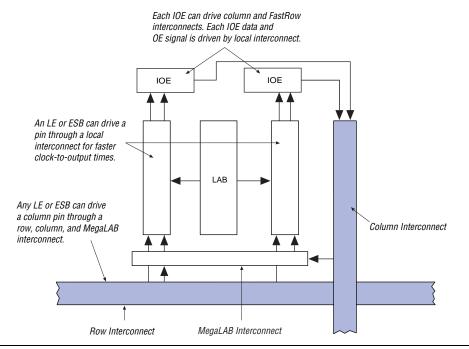

FastRow interconnects connect a column I/O pin directly to the LAB local interconnect within two MegaLAB structures. This feature provides fast setup times for pins that drive high fan-outs with complex logic, such as PCI designs. For fast bidirectional I/O timing, LE registers using local routing can improve setup times and OE timing.

APEX II devices have a peripheral control bus made up of 12 signals that drive the IOE control signals. The peripheral bus is composed of six output enables, OE[5:0] and six clock enables, CE[5:0]. These twelve signals can be driven from internal logic or from the Fast I/O signals. Table 7 lists the peripheral control signal destinations.

| able 7. Peripheral Control Bus Destinations |                    |  |  |  |  |  |

|---------------------------------------------|--------------------|--|--|--|--|--|

| Peripheral Bus                              | I/O Control Signal |  |  |  |  |  |

| Output Enable 0 [OE0]                       | OE                 |  |  |  |  |  |

| Output Enable 1 [OE1]                       | OE                 |  |  |  |  |  |

| Output Enable 2 [OE2]                       | OE                 |  |  |  |  |  |

| Output Enable 3 [OE3]                       | OE                 |  |  |  |  |  |

| Output Enable 4 [OE4]                       | OE                 |  |  |  |  |  |

| Output Enable 5 [OE5]                       | OE                 |  |  |  |  |  |

| Clock Enable 0 [CE0]                        | CE, CLK            |  |  |  |  |  |

| Clock Enable 1 [CE1]                        | CE, OE             |  |  |  |  |  |

| Clock Enable 2 [CE2]                        | CE, CLK            |  |  |  |  |  |

| Clock Enable 3 [CE3]                        | CE, OE             |  |  |  |  |  |

| Clock Enable 4 [CE4]                        | CE, CLR            |  |  |  |  |  |

| Clock Enable 5 [CE5]                        | CE, CLR            |  |  |  |  |  |

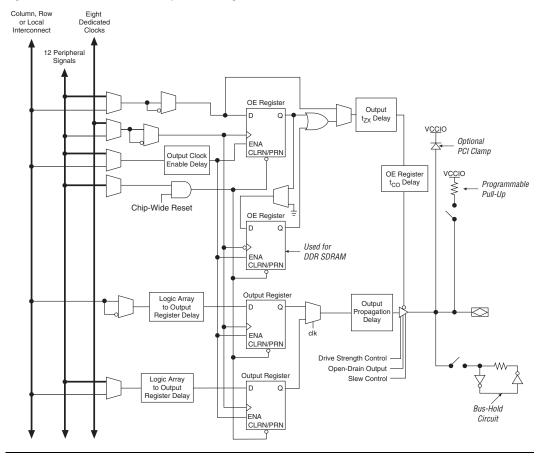

In normal bidirectional operation, the input register can be used for input data requiring fast setup times. The input register can have its own clock input and clock enable separate from the OE and output registers. The output register can be used for data requiring fast clock-to-output performance. The OE register can be used for fast clock-to-output enable timing. The OE and output register share the same clock source and the same clock enable source from local interconnect in the associated LAB, fast global signals, or row global signals. Figure 28 shows the IOE in bidirectional configuration.

Figure 30. APEX II IOE in DDR Output I/O Configuration

The APEX II IOE operates in bidirectional DDR mode by combining the DDR input and DDR output configurations.

APEX II I/O pins transfer data on a DDR bidirectional bus to support DDR SDRAM at 167 MHz (334 Mbps). The negative-edge-clocked OE register is used to hold the OE signal inactive until the falling edge of the clock. This is done to meet DDR SDRAM timing requirements. QDR SRAMs are also supported with DDR I/O pins on separate read and write ports.

#### Bus Hold

Each APEX II device I/O pin provides an optional bus-hold feature. When this feature is enabled for an I/O pin, the bus-hold circuitry weakly holds the signal at its last driven state. By holding the last driven state of the pin until the next input signal is present, the bus-hold feature eliminates the need to add external pull-up or pull-down resistors to hold a signal level when the bus is tri-stated. The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. This feature can be selected individually for each I/O pin. The bus-hold output will drive no higher than  $V_{\rm CCIO}$  to prevent overdriving signals. If the bus-hold feature is enabled, the programmable pull-up option cannot be used. The bus-hold feature should also be disabled if open-drain outputs are used with the GTL+I/O standard.

The bus-hold circuitry weakly pulls the signal level to the last driven state through a resistor with a nominal resistance ( $R_{BH}$ ) of approximately 7 k $\Omega$ . Table 41 on page 74 gives specific sustaining current that will be driven through this resistor and overdrive current that will identify the next driven input level. This information is provided for each  $V_{CCIO}$  voltage level.

The bus-hold circuitry is active only after configuration. When going into user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

## Programmable Pull-Up Resistor

Each APEX II device I/O pin provides an optional programmable pull-up resistor during user mode. When this feature is enabled for an I/O pin, the pull-up resistor (typically 25 k $\Omega$ ) weakly holds the output to the V<sub>CCIO</sub> level of the bank that the output pin resides in.

#### **Dedicated Fast I/O Pins**

APEX II devices incorporate dedicated bidirectional pins for signals with high internal fanout, such as PCI control signals. These pins are called dedicated fast I/O pins (FAST1, FAST2, FAST3, and FAST4) and can drive the four global fast lines throughout the device, ideal for fast clock, clock enable, preset, clear, or high fanout logic signal distribution. The dedicated fast I/O pins have one output register and one OE register, but they do not have input registers. The dedicated fast lines can also be driven by a LE local interconnect to generate internal global signals.

## Advanced I/O Standard Support

APEX II device IOEs support the following I/O standards:

- LVTTL

- LVCMOS

- **1.5-V**

- **1.8-V**

- 2.5-V

- 3.3-V PCI

- 3.3-V PCI-X

- 3.3-V AGP (1×, 2×)

- LVDS

- LVPECL

- PCML

- HyperTransport

- GTL+

- HSTL class I and II

- SSTL-3 class I and II

- SSTL-2 class I and II

- CTT

- Differential HSTL

Pre-programmed CDS may also be used to resolve clock-to-data skew greater than 50% of the bit period. However, internal logic must be used to implement the byte alignment circuitry for this operation.

## Flexible-LVDS I/O Pins

A subset of pins in the top two I/O banks supports interfacing with Flexible-LVDS, LVPECL, and HyperTransport inputs. These Flexible-LVDS input pins include dedicated LVDS, LVPECL, and HyperTransport input buffers. A subset of pins in the bottom two I/O banks supports interfacing with Flexible-LVDS and HyperTransport outputs. These Flexible-LVDS output pins include dedicated LVDS and HyperTransport output buffers. The Flexible-LVDS pins do not require any external components except for 100- $\Omega$  termination resistors on receiver channels. These pins do not contain dedicated serialization/deserialization circuitry; therefore, internal logic is used to perform serialization/deserialization functions.

The EP2A15 and EP2A25 devices support 56 input and 56 output Flexible-LVDS channels. The EP2A40 and larger devices support 88 input and 88 output Flexible-LVDS channels. All APEX II devices support the Flexible-LVDS interface up to 400 Mbps (DDR) per channel. Flexible-LVDS pins along with the True-LVDS pins provide up to 144-Gbps total device bandwidth. Table 13 shows the Flexible-LVDS timing specification.

| Table 13. | APEX II Flexible-LVDS Timing Sp     | ecificatio | n           |       |       |       |     |      |   |

|-----------|-------------------------------------|------------|-------------|-------|-------|-------|-----|------|---|

| Symbol    | Timing Parameter Definition         |            | Speed Grade |       |       |       |     |      |   |

|           |                                     | -          | -7          |       | -7 -8 |       | -9  |      | ] |

|           |                                     | Min        | Max         | Min   | Max   | Min   | Max |      |   |

| Data Rate | Maximum operating speed             |            | 400         |       | 311   |       | 311 | Mbps |   |

| TCCS      | Transmitter channel-to-channel skew |            | 700         |       | 900   |       | 900 | ps   |   |

| SW        | Receiver sampling window            | 1,100      |             | 1,400 |       | 1,400 |     | ps   |   |

# MultiVolt I/O Interface

The APEX II architecture supports the MultiVolt I/O interface feature, which allows APEX II devices in all packages to interface with systems of different supply voltages. The devices have one set of  $V_{CC}$  pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).

Signals can be driven into APEX II devices before and during power-up without damaging the device. In addition, APEX II devices do not drive out during power-up. Once operating conditions are reached and the device is configured, APEX II devices operate as specified by the user.

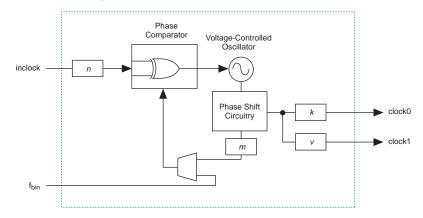

General-Purpose PLLs APEX II devices have ClockLock, ClockBoost, and ClockShift features, which use four general-purpose PLLs (separate from the four dedicated True-LVDS PLLs) to provide clock management and clock-frequency synthesis. These PLLs allow designers to increase performance and provide clock-frequency synthesis. The PLL reduces the clock delay within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The PLLs, which provide programmable multiplication, allow the designer to distribute a low-speed clock and multiply that clock on-device. APEX II devices include a high-speed clock tree: unlike ASICs, the user does not have to design and optimize the clock tree. The PLLs work in conjunction with the APEX II device's high-speed clock to provide significant improvements in system performance and bandwidth.

> The PLLs in APEX II devices are enabled through the Quartus II software. External devices are not required to use these features. Table 15 shows the general-purpose PLL features for APEX II devices. Figure 35 shows an APEX II general-purpose PLL.

| Table 15. APEX                                                                                                    | Table 15. APEX II General-Purpose PLL Features |   |   |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---|---|--|--|--|--|--|--|--|

| Number of PLLs     ClockBoost<br>Feature     Number of External<br>Clock Outputs     Number of<br>Feedback Inputs |                                                |   |   |  |  |  |  |  |  |  |

| 4                                                                                                                 | $m/(n \times k, v)$                            | 8 | 2 |  |  |  |  |  |  |  |

Figure 35. APEX II General-Purpose PLL Note (1)

For more information, see the following documents:

Application Note 39 (IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

Jam Programming & Test Language Specification

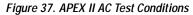

Generic Testing

Each APEX II device is functionally tested. Complete testing of each configurable static random access memory (SRAM) bit and all logic functionality ensures 100% yield. AC test measurements for APEX II devices are made under conditions equivalent to those shown in Figure 37. Multiple test patterns can be used to configure devices during all stages of the production flow. AC test criteria include:

- Power supply transients can affect AC measurements.

- Simultaneous transitions of multiple outputs should be avoided for accurate measurement.

- Threshold tests must not be performed under AC conditions.

- Large-amplitude, fast-ground-current transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground, significant reductions in observable noise immunity can result.

# Operating Conditions

APEX II devices are offered in both commercial and industrial grades. However, industrial-grade devices may have limited speed-grade availability.

| Table 28. 3.3-V PCI Specifications |                           |                             |                             |         |                             |       |  |  |  |  |

|------------------------------------|---------------------------|-----------------------------|-----------------------------|---------|-----------------------------|-------|--|--|--|--|

| Symbol                             | Parameter                 | Conditions                  | Minimum                     | Typical | Maximum                     | Units |  |  |  |  |

| V <sub>CCIO</sub>                  | Output supply voltage     |                             | 3.0                         | 3.3     | 3.6                         | V     |  |  |  |  |

| V <sub>IH</sub>                    | High-level input voltage  |                             | 0.5 	imes V <sub>CCIO</sub> |         | V <sub>CCIO</sub> +<br>0.5  | V     |  |  |  |  |

| V <sub>IL</sub>                    | Low-level input voltage   |                             | -0.5                        |         | 0.3 	imes V <sub>CCIO</sub> | V     |  |  |  |  |

| I <sub>I</sub>                     | Input pin leakage current | $0 < V_{IN} < V_{CCIO}$     | -10                         |         | 10                          | μΑ    |  |  |  |  |

| V <sub>OH</sub>                    | High-level output voltage | I <sub>OUT</sub> = -500 μA  | $0.9 \times V_{CCIO}$       |         |                             | V     |  |  |  |  |

| V <sub>OL</sub>                    | Low-level output voltage  | I <sub>OUT</sub> = 1,500 μA |                             |         | 0.1 	imes V <sub>CCIO</sub> | V     |  |  |  |  |

| Table 29. F       | PCI-X Specifications      |                             |                             |         |                             |       |

|-------------------|---------------------------|-----------------------------|-----------------------------|---------|-----------------------------|-------|

| Symbol            | Parameter                 | Conditions                  | Minimum                     | Typical | Maximum                     | Units |

| V <sub>CCIO</sub> | Output supply voltage     |                             | 3.0                         |         | 3.6                         | V     |

| V <sub>IH</sub>   | High-level input voltage  |                             | 0.5 	imes V <sub>CCIO</sub> |         | V <sub>CCIO</sub> +<br>0.5  | V     |

| V <sub>IL</sub>   | Low-level input voltage   |                             | -0.5                        |         | $0.35 	imes V_{CCIO}$       | V     |

| V <sub>IPU</sub>  | Input pull-up voltage     |                             | 0.7 	imes V <sub>CCIO</sub> |         |                             | V     |

| IIL               | Input leakage current     | $0 < V_{IN} < V_{CCIO}$     | -10                         |         | 10                          | μA    |

| V <sub>OH</sub>   | High-level output voltage | I <sub>OUT</sub> = -500 μA  | 0.9 	imes V <sub>CCIO</sub> |         |                             | V     |

| V <sub>OL</sub>   | Low-level output voltage  | I <sub>OUT</sub> = 1,500 μA |                             |         | 0.1 	imes V <sub>CCIO</sub> | V     |

| L <sub>PIN</sub>  | Pin inductance            |                             |                             |         | 15                          | nH    |

| Table 30. G      | Table 30. GTL+ I/O Specifications |                                     |                        |         |                        |       |  |  |  |  |  |

|------------------|-----------------------------------|-------------------------------------|------------------------|---------|------------------------|-------|--|--|--|--|--|

| Symbol           | Parameter                         | Conditions                          | Minimum                | Typical | Maximum                | Units |  |  |  |  |  |

| V <sub>TT</sub>  | Termination voltage               |                                     | 1.35                   | 1.5     | 1.65                   | V     |  |  |  |  |  |

| V <sub>REF</sub> | Reference voltage                 |                                     | 0.88                   | 1.0     | 1.12                   | V     |  |  |  |  |  |

| V <sub>IH</sub>  | High-level input voltage          |                                     | V <sub>REF</sub> + 0.1 |         |                        | V     |  |  |  |  |  |

| V <sub>IL</sub>  | Low-level input voltage           | 1                                   |                        |         | V <sub>REF</sub> – 0.1 | V     |  |  |  |  |  |

| V <sub>OL</sub>  | Low-level output voltage          | I <sub>OL</sub> = 36 mA <i>(10)</i> |                        |         | 0.65                   | V     |  |  |  |  |  |

| Symbol            | Parameter                                                                | Conditions              | Minimum | Typical | Maximum | Units |

|-------------------|--------------------------------------------------------------------------|-------------------------|---------|---------|---------|-------|

| V <sub>CCIO</sub> | I/O supply voltage                                                       |                         | 3.135   | 3.3     | 3.465   | V     |

| V <sub>OD</sub>   | Differential output voltage                                              | R <sub>L</sub> = 100 Ω  | 250     |         | 850 (1) | mV    |

| $\Delta V_{OD}$   | Change in V <sub>OD</sub> between high and low                           | R <sub>L</sub> = 100 Ω  |         |         | 50      | mV    |

| V <sub>OS</sub>   | Output Offset voltage                                                    | R <sub>L</sub> = 100 Ω  | 1.125   | 1.25    | 1.375   | V     |

| $\Delta V_{OS}$   | Change in V <sub>OS</sub> between high and low                           | R <sub>L</sub> = 100 Ω  |         |         | 50      | mV    |

| V <sub>TH</sub>   | Differential input threshold                                             | V <sub>CM</sub> = 1.2 V | -100    |         | 100     | mV    |

| V <sub>IN</sub>   | Receiver input voltage range                                             |                         | 0.0     |         | 2.4     | V     |

| R <sub>L</sub>    | Receiver differential input<br>resistor (external to<br>APEX II devices) |                         | 90      | 100     | 110     | Ω     |

| Symbol            | Parameter                            | Conditions | Minimum                    | Typical           | Maximum                    | Units |

|-------------------|--------------------------------------|------------|----------------------------|-------------------|----------------------------|-------|

| V <sub>CCIO</sub> | I/O supply voltage                   |            | 3.135                      | 3.3               | 3.465                      | V     |

| V <sub>IL</sub>   | Low-level input voltage              |            |                            |                   | V <sub>CCIO</sub> –<br>0.3 | V     |

| V <sub>IH</sub>   | High-level input voltage             |            | V <sub>CCIO</sub>          |                   |                            | V     |

| V <sub>OL</sub>   | Low-level output voltage             |            | V <sub>CCIO</sub> –<br>0.6 |                   | V <sub>CCIO</sub> –<br>0.3 | V     |

| V <sub>OH</sub>   | High-level output voltage            |            | V <sub>CCIO</sub>          |                   | V <sub>CCIO</sub> –<br>0.3 | V     |

| V <sub>T</sub>    | Output termination voltage           |            |                            | V <sub>CCIO</sub> |                            | V     |

| V <sub>OD</sub>   | Differential output voltage          |            | 300                        | 450               | 600                        | mV    |

| t <sub>R</sub>    | Rise time (20 to 80%)                |            | 85                         |                   | 325                        | ps    |

| t <sub>F</sub>    | Fall time (20 to 80%)                |            | 85                         |                   | 325                        | ps    |

| R <sub>O</sub>    | Output load                          |            |                            | 100               |                            | Ω     |

| RL                | Receiver differential input resistor |            | 45                         | 50                | 55                         | Ω     |

#### APEX II Programmable Logic Device Family Data Sheet

| Table 54. EP2A15 f | MAX Routing D  | Delays |                |     |         |      |    |

|--------------------|----------------|--------|----------------|-----|---------|------|----|

| Symbol             | -7 Speed Grade |        | -8 Speed Grade |     | -9 Spee | Unit |    |

|                    | Min            | Max    | Min            | Max | Min     | Мах  |    |

| t <sub>F1-4</sub>  | 0.19           |        | 0.21           |     | 0.25    |      | ns |

| t <sub>F5-20</sub> | 0.64           |        | 0.73           |     | 0.84    |      | ns |

| t <sub>F20+</sub>  | 1.18           |        | 1.35           |     | 1.56    |      | ns |

| Symbol             | -7 Speed Grade |     | -8 Spee | -8 Speed Grade |      | -9 Speed Grade |    |

|--------------------|----------------|-----|---------|----------------|------|----------------|----|

|                    | Min            | Мах | Min     | Мах            | Min  | Мах            |    |

| t <sub>CH</sub>    | 1.00           |     | 1.15    |                | 1.32 |                | ns |

| t <sub>CL</sub>    | 1.00           |     | 1.15    |                | 1.32 |                | ns |

| t <sub>CLRP</sub>  | 0.13           |     | 0.15    |                | 0.17 |                | ns |

| t <sub>PREP</sub>  | 0.13           |     | 0.15    |                | 0.17 |                | ns |

| t <sub>ESBCH</sub> | 1.00           |     | 1.15    |                | 1.32 |                | ns |

| t <sub>ESBCL</sub> | 1.00           |     | 1.15    |                | 1.32 |                | ns |

| t <sub>ESBWP</sub> | 1.12           |     | 1.28    |                | 1.48 |                | ns |

| t <sub>ESBRP</sub> | 0.88           |     | 1.02    |                | 1.17 |                | ns |

| Table 56. | EP2A25 f <sub>MAX</sub> LE | Timing | Parameters |

|-----------|----------------------------|--------|------------|

|-----------|----------------------------|--------|------------|

| Symbol           | -7 Speed Grade |      | -8 Speed Grade |      | -9 Speed Grade |      | Unit |

|------------------|----------------|------|----------------|------|----------------|------|------|

|                  | Min            | Max  | Min            | Max  | Min            | Мах  |      |

| t <sub>SU</sub>  | 0.25           |      | 0.29           |      | 0.33           |      | ns   |

| t <sub>H</sub>   | 0.25           |      | 0.29           |      | 0.33           |      | ns   |

| t <sub>CO</sub>  |                | 0.18 |                | 0.20 |                | 0.23 | ns   |

| t <sub>LUT</sub> |                | 0.53 |                | 0.61 |                | 0.70 | ns   |

| Table 61. EP2A40        | f <sub>MAX</sub> ESB Timi | ng Parameter | rs             |      |                |      |      |

|-------------------------|---------------------------|--------------|----------------|------|----------------|------|------|

| Symbol                  | -7 Speed Grade            |              | -8 Speed Grade |      | -9 Speed Grade |      | Unit |

|                         | Min                       | Мах          | Min            | Мах  | Min            | Мах  | 1    |

| t <sub>ESBARC</sub>     |                           | 2.28         |                | 2.62 |                | 3.01 | ns   |

| t <sub>ESBSRC</sub>     |                           | 2.23         |                | 2.56 |                | 2.95 | ns   |

| t <sub>ESBAWC</sub>     |                           | 3.13         |                | 3.60 |                | 4.13 | ns   |

| t <sub>ESBSWC</sub>     |                           | 2.76         |                | 3.18 |                | 3.65 | ns   |

| t <sub>ESBWASU</sub>    | 1.19                      |              | 1.37           |      | 1.57           |      | ns   |

| t <sub>ESBWAH</sub>     | 0.00                      |              | 0.00           |      | 0.00           |      | ns   |

| t <sub>ESBWDSU</sub>    | 1.44                      |              | 1.66           |      | 1.91           |      | ns   |

| t <sub>ESBWDH</sub>     | 0.00                      |              | 0.00           |      | 0.00           |      | ns   |

| t <sub>ESBRASU</sub>    | 1.88                      |              | 2.17           |      | 2.49           |      | ns   |

| t <sub>ESBRAH</sub>     | 0.00                      |              | 0.00           |      | 0.00           |      | ns   |

| t <sub>ESBWESU</sub>    | 1.60                      |              | 1.85           |      | 2.12           |      | ns   |

| t <sub>ESBDATASU</sub>  | 0.74                      |              | 0.85           |      | 0.98           |      | ns   |

| t <sub>ESBWADDRSU</sub> | 0.82                      |              | 0.94           |      | 1.08           |      | ns   |

| t <sub>ESBRADDRSU</sub> | 0.73                      |              | 0.84           |      | .97            |      | ns   |

| t <sub>ESBDATAC01</sub> |                           | 1.09         |                | 1.25 |                | 1.44 | ns   |

| t <sub>ESBDATACO2</sub> |                           | 1.73         |                | 1.99 |                | 2.29 | ns   |

| t <sub>ESBDD</sub>      |                           | 3.26         |                | 3.75 |                | 4.32 | ns   |

| t <sub>PD</sub>         |                           | 1.55         |                | 1.78 |                | 2.05 | ns   |

| t <sub>PTERMSU</sub>    | 0.99                      |              | 1.13           |      | 1.30           |      | ns   |

| t <sub>PTERMCO</sub>    |                           | 0.79         |                | 0.90 |                | 1.04 | ns   |

| Table 62. EP2A40 f <sub>MAX</sub> Routing Delays |         |         |         |         |                |     |      |  |  |

|--------------------------------------------------|---------|---------|---------|---------|----------------|-----|------|--|--|

| Symbol                                           | -7 Spee | d Grade | -8 Spee | d Grade | -9 Speed Grade |     | Unit |  |  |

|                                                  | Min     | Max     | Min     | Max     | Min            | Мах |      |  |  |

| t <sub>F1-4</sub>                                | 0.17    |         | 0.19    |         | 0.22           |     | ns   |  |  |

| t <sub>F5-20</sub>                               | 1.12    |         | 1.28    |         | 1.48           |     | ns   |  |  |

| t <sub>F20+</sub>                                | 1.49    |         | 1.72    |         | 1.98           |     | ns   |  |  |

| Symbol             | -7 Speed Grade |     | -8 Speed Grade |     | -9 Speed Grade |     | Unit |

|--------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                    | Min            | Мах | Min            | Max | Min            | Мах |      |

| t <sub>CH</sub>    | 0.89           |     | 1.33           |     | 1.88           |     | ns   |

| t <sub>CL</sub>    | 0.89           |     | 1.33           |     | 1.88           |     | ns   |

| t <sub>CLRP</sub>  | 0.12           |     | 0.14           |     | 0.16           |     | ns   |

| t <sub>PREP</sub>  | 0.12           |     | 0.14           |     | 0.16           |     | ns   |

| t <sub>ESBCH</sub> | 0.89           |     | 1.33           |     | 1.88           |     | ns   |

| t <sub>ESBCL</sub> | 0.89           |     | 1.33           |     | 1.88           |     | ns   |

| t <sub>ESBWP</sub> | 1.05           |     | 1.20           |     | 1.38           |     | ns   |

| t <sub>ESBRP</sub> | 0.78           |     | 0.90           |     | 1.03           |     | ns   |

| Table 64. EP2A70 f <sub>MAX</sub> LE Timing Parameters |         |         |                |      |                |      |      |  |  |

|--------------------------------------------------------|---------|---------|----------------|------|----------------|------|------|--|--|

| Symbol                                                 | -7 Spee | d Grade | -8 Speed Grade |      | -9 Speed Grade |      | Unit |  |  |

|                                                        | Min     | Max     | Min            | Max  | Min            | Мах  |      |  |  |

| t <sub>SU</sub>                                        | 0.30    |         | 0.34           |      | 0.39           |      | ns   |  |  |

| t <sub>H</sub>                                         | 0.30    |         | 0.34           |      | 0.39           |      | ns   |  |  |

| t <sub>CO</sub>                                        |         | 0.22    |                | 0.25 |                | 0.29 | ns   |  |  |

| t <sub>LUT</sub>                                       |         | 0.66    |                | 0.76 |                | 0.87 | ns   |  |  |

| Table 76. APEX II    | Selectable     | I/O Standards | Input Adde     | r Delays |         |        |    |

|----------------------|----------------|---------------|----------------|----------|---------|--------|----|

| Symbol               | -7 Speed Grade |               | -8 Speed Grade |          | -9 Spee | Unit   |    |

|                      | Min            | Max           | Min            | Мах      | Min     | Max    |    |

| LVCMOS               |                | 0.00          |                | 0.00     |         | 0.00   | ns |

| LVTTL                |                | 0.00          |                | 0.00     |         | 0.00   | ns |

| 1.5 V                |                | 0.10          |                | 0.11     |         | 0.12   | ns |

| 1.8 V                |                | 0.00          |                | 0.00     |         | 0.00   | ns |

| 2.5 V                |                | 0.00          |                | 0.00     |         | 0.00   | ns |

| 3.3-V PCI            |                | 0.00          |                | 0.00     |         | 0.00   | ns |

| 3.3-V PCI-X          |                | 0.00          |                | 0.00     |         | 0.00   | ns |

| GTL+                 |                | - 0.20        |                | - 0.22   |         | - 0.24 | ns |

| SSTL-3 Class I       |                | - 0.17        |                | - 0.19   |         | - 0.20 | ns |

| SSTL-3 Class II      |                | - 0.17        |                | - 0.19   |         | - 0.20 | ns |

| SSTL-2 Class I       |                | - 0.24        |                | - 0.26   |         | - 0.29 | ns |

| SSTL-2 Class II      |                | - 0.24        |                | - 0.26   |         | - 0.29 | ns |

| HSTL Class I         |                | - 0.03        |                | - 0.03   |         | - 0.03 | ns |

| HSTL Class II        |                | - 0.03        |                | - 0.03   |         | - 0.03 | ns |

| LVDS                 |                | - 0.23        |                | - 0.26   |         | - 0.28 | ns |

| LVPECL               |                | - 0.23        |                | - 0.26   |         | - 0.28 | ns |

| PCML                 |                | - 0.23        |                | - 0.26   |         | - 0.28 | ns |

| CTT                  |                | 0.00          |                | 0.00     |         | 0.00   | ns |

| 3.3-V AGP 1×         |                | 0.00          |                | 0.00     |         | 0.00   | ns |

| 3.3-V AGP 2×         |                | 0.00          |                | 0.00     |         | 0.00   | ns |

| HyperTransport       |                | - 0.23        |                | - 0.26   |         | - 0.28 | ns |

| Differential<br>HSTL |                | - 0.23        |                | - 0.26   |         | - 0.28 | ns |

# Revision<br/>HistoryThe information contained in the APEX II Programmable Logic Device<br/>Family Data Sheet version 3.0 supersedes information published in<br/>previous versions. The following changes were made to the APEX II<br/>Programmable Logic Device Family Data Sheet version 3.0:

- Changed the value from 624 to 400 Mbps throughout the document.

- Deleted the pin count (612) for the EP2A25 device in the 1,020-pin FineLine BGA package (see Table 3).

- Added Table 13.

- Changed the maximum value of 3.6 to 2.4 in Table 20.

- Updated Tables 60 through 67 and Tables 72 through 75.

- Updated Figures 25, 28, and 30.

- Added *Note (1)* to Figure 13.

- Added Figure 43.

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Customer Marketing: (408) 544-7104 Literature Services: lit\_req@altera.com

Copyright © 2002 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending

applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Altera Corporation