#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                      |

|---------------------------------|-------------------------------------------------------------|

| Core Processor                  | ARM920T                                                     |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 150MHz                                                      |

| Co-Processors/DSP               | -                                                           |

| RAM Controllers                 | SDRAM                                                       |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | LCD                                                         |

| Ethernet                        |                                                             |

| SATA                            | -                                                           |

| USB                             | USB 1.x (1)                                                 |

| Voltage - I/O                   | 1.8V, 3.0V                                                  |

| Operating Temperature           | -30°C ~ 70°C (TA)                                           |

| Security Features               | -                                                           |

| Package / Case                  | 225-LFBGA                                                   |

| Supplier Device Package         | 225-MAPBGA (13x13)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9328mxldvp15 |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

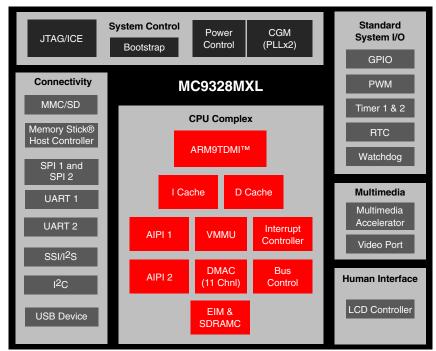

Introduction

Figure 1. i.MXL Functional Block Diagram

## 1.1 Features

To support a wide variety of applications, the processor offers a robust array of features, including the following:

- ARM920T<sup>TM</sup> Microprocessor Core

- AHB to IP Bus Interfaces (AIPIs)

- External Interface Module (EIM)

- SDRAM Controller (SDRAMC)

- DPLL Clock and Power Control Module

- Two Universal Asynchronous Receiver/Transmitters (UART 1 and UART 2)

- Serial Peripheral Interface (SPI)

- Two General-Purpose 32-bit Counters/Timers

- Watchdog Timer

- Real-Time Clock/Sampling Timer (RTC)

- LCD Controller (LCDC)

- Pulse-Width Modulation (PWM) Module

- Universal Serial Bus (USB) Device

- Multimedia Card and Secure Digital (MMC/SD) Host Controller Module

- Memory Stick<sup>®</sup> Host Controller (MSHC)

- Direct Memory Access Controller (DMAC)

- Synchronous Serial Interface and an Inter-IC Sound (SSI/I<sup>2</sup>S) Module

- Inter-IC (I<sup>2</sup>C) Bus Module

\_\_\_\_\_

| Table 3. MC9328MXLMC9328MXS | Signal Multiplexing | Scheme ( | Continued) |

|-----------------------------|---------------------|----------|------------|

|                             |                     |          |            |

|                       | 225         | 256         | Р      | rimary |             | Alterna          | ite | GP   | OIO         |             |     |       |         |

|-----------------------|-------------|-------------|--------|--------|-------------|------------------|-----|------|-------------|-------------|-----|-------|---------|

| I/O Supply<br>Voltage | BGA<br>Ball | BGA<br>Ball | Signal | Dir    | Pull-<br>Up | Signal           | Dir | Mux  | Pull<br>-Up | AIN BIN     | BIN | AOUT  | Default |

| NVDD1                 | N4          | P3          | EB0    | 0      |             |                  |     |      |             |             |     |       |         |

| NVDD1                 | M4          | N3          | D10    | I/O    | 69K         |                  |     |      |             |             |     |       |         |

| NVDD1                 | P4          | P1          | A3     | 0      |             |                  |     |      |             |             |     |       |         |

| NVDD1                 | R3          | N2          | EB1    | 0      |             |                  |     |      |             |             |     |       |         |

| NVDD1                 | N5          | P2          | D9     | I/O    | 69K         |                  |     |      |             |             |     |       |         |

| NVDD1                 | R4          | R1          | EB2    | 0      |             |                  |     |      |             |             |     |       |         |

| NVDD1                 | P5          | T2          | A2     | 0      |             |                  |     |      |             |             |     |       |         |

| NVDD1                 | M5          | R2          | EB3    | 0      |             |                  |     |      |             |             |     |       |         |

| NVDD1                 | N6          | R5          | D8     | I/O    | 69K         |                  |     |      |             |             |     |       |         |

| NVDD1                 | R5          | Т3          | OE     | 0      |             |                  |     |      |             |             |     |       |         |

| NVDD1                 | P6          | R3          | A1     | 0      |             |                  |     | 1    |             | ł           |     |       |         |

| NVDD1                 | L7          | T4          | CS5    | 0      |             |                  |     | PA23 | 69K         | 1           |     |       | PA23    |

| NVDD1                 | R6          | N4          | D7     | I/O    | 69K         |                  |     |      |             |             |     |       |         |

| NVDD1                 | M7          | R4          | CS4    | 0      |             |                  |     | PA22 | 69K         |             |     |       | PA22    |

| NVDD1                 | R7          | N5          | A0     | 0      |             |                  |     | PA21 | 69K         |             |     |       | A0      |

| NVDD1                 | N7          | P4          | CS3    | 0      |             | CSD1             |     |      |             |             |     |       | CSD1    |

| NVDD1                 | P7          | P5          | D6     | I/O    | 69K         |                  |     |      |             |             |     |       |         |

| NVDD1                 | K3          | T5          | CS2    | 0      |             | CSD0             |     |      |             |             |     |       | CSD0    |

| NVDD1                 | R8          | M5          | SDCLK  | 0      |             |                  |     |      |             |             |     |       |         |

| NVDD1                 | M8          | Т6          | CS1    | 0      |             |                  |     |      |             |             |     |       |         |

| NVDD1                 | N8          | T7          | CS0    | 0      |             |                  |     |      |             |             |     |       |         |

| NVDD1                 | P8          | R6          | D5     | I/O    | 69K         |                  |     |      |             |             |     |       |         |

| NVDD1                 | L9          | P6          | ECB    | Ι      |             | ETMTRAC<br>EPKT7 |     | PA20 | 69K         |             |     |       | ECB     |

| NVDD1                 | R9          | N6          | D4     | I/O    | 69K         |                  |     |      |             |             |     |       |         |

| NVDD1                 | R10         | R7          | LBA    | 0      |             | ETMTRAC<br>EPKT6 |     | PA19 | 69K         |             |     |       | LBA     |

| NVDD1                 | R11         | P8          | D3     | I/O    | 69K         |                  |     |      |             |             |     |       |         |

| NVDD1                 | M9          | R8          | BCLK   |        |             | ETMTRAC<br>EPKT5 |     | PA18 | 69K         |             |     |       | BCLK    |

| NVDD1                 | L8          | P7          | D2     | I/O    | 69K         |                  |     |      |             |             |     |       |         |

| NVDD1                 | N9          | N7          | PA17   |        |             | ETMTRAC<br>EPKT4 |     | PA17 | 69K         | SPI2_<br>SS |     | DTACK | PA17    |

| NVDD1                 | K10         | N8          | D1     | I/O    | 69K         |                  |     |      |             |             |     |       |         |

| NVDD1                 | M10         | M7          | RW     |        |             |                  |     |      |             |             |     |       |         |

| NVDD1                 | P10         | Т8          | MA11   | 0      |             |                  |     |      |             |             |     |       |         |

| NVDD1                 | P9          | M8          | MA10   | 0      |             |                  |     |      |             |             |     |       |         |

| NVDD1                 | N10         | R9          | D0     | I/O    | 69K         |                  |     |      |             |             |     |       |         |

| NVDD1                 | R12         | P9          | DQM3   | 0      |             |                  |     |      |             |             |     |       |         |

Signals and Connections

| 1/0.0                 | 225         | 256         | Pr               | imary |             | Alterna       | Alternate |      | OIO         |               |     |                |         |

|-----------------------|-------------|-------------|------------------|-------|-------------|---------------|-----------|------|-------------|---------------|-----|----------------|---------|

| I/O Supply<br>Voltage | BGA<br>Ball | BGA<br>Ball | Signal           | Dir   | Pull-<br>Up | Signal        | Dir       | Mux  | Pull<br>-Up | AIN           | BIN | AOUT           | Default |

| NVDD2                 | D11         | G14         | LP/HSYN<br>C     | 0     |             |               |           | PD13 | 69K         |               |     |                | PD13    |

| NVDD2                 | E11         | G13         | ACD/OE           | 0     |             |               |           | PD12 | 69K         |               |     |                | PD12    |

| NVDD2                 | C10         | G12         | CONTRA<br>ST     | 0     |             |               |           | PD11 | 69K         |               |     |                | PD11    |

| NVDD2                 | B11         | F16         | SPL_SPR          | 0     |             | UART2_D<br>SR | 0         | PD10 | 69K         | SPI2_<br>TXD  |     |                | PD10    |

| NVDD2                 | A12         | H10         | PS               | 0     |             | UART2_RI      | 0         | PD9  | 69K         |               |     | SPI2_<br>RXD_1 | PD9     |

| NVDD2                 | F10         | G11         | CLS              | 0     |             | UART2_D<br>CD | 0         | PD8  | 69K         | SPI2_<br>SS   |     |                | PD8     |

| NVDD2                 | A11         | F12         | REV              | 0     |             | UART2_D<br>TR | Ι         | PD7  | 69K         | SPI2_<br>SCLK |     |                | PD7     |

| NVDD2                 | B10         | F15         | LSCLK            | 0     |             |               |           | PD6  | 69K         |               |     |                | PD6     |

| NVDD3                 | D10         | G9          | SPI1_MO<br>SI    | I/O   |             |               |           | PC17 | 69K         |               |     |                | PC17    |

| NVDD3                 | E10         | F9          | SPI1_MIS<br>O    | I/O   |             |               |           | PC16 | 69K         |               |     |                | PC16    |

| NVDD3                 | В9          | E9          | SPI1_SS          | I/O   |             |               |           | PC15 | 69K         |               |     |                | PC15    |

| NVDD3                 | A10         | B9          | SPI1_SCL<br>K    | I/O   |             |               |           | PC14 | 69K         |               |     |                | PC14    |

| NVDD3                 | A9          | D9          | SPI1_SPI<br>_RDY | I/O   |             |               |           | PC13 | 69K         |               |     | DMA_REQ        | PC13    |

| NVDD3                 | E8          | A9          | UART1_R<br>XD    | Ι     |             |               |           | PC12 | 69K         |               |     |                | PC12    |

| NVDD3                 | B8          | C9          | UART1_T<br>XD    | 0     |             |               |           | PC11 | 69K         |               |     |                | PC11    |

| NVDD3                 | C9          | A8          | UART1_R<br>TS    | I     |             |               |           | PC10 | 69K         |               |     |                | PC10    |

| NVDD3                 | E9          | G8          | UART1_C<br>TS    | 0     |             |               |           | PC9  | 69K         |               |     |                | PC9     |

| NVDD3                 | A8          | B8          | SSI_TXCL<br>K    | I/O   |             |               |           | PC8  | 69K         |               |     |                | PC8     |

| NVDD3                 | C8          | F8          | SSI_TXFS         | I/O   |             |               |           | PC7  | 69K         |               |     |                | PC7     |

| NVDD3                 | F9          | E8          | SSI_TXDA<br>T    | 0     |             |               |           | PC6  | 69K         |               |     |                | PC6     |

| NVDD3                 | B7          | D8          | SSI_RXD<br>AT    | I     |             |               |           | PC5  | 69K         |               |     |                | PC5     |

| NVDD3                 | F8          | B7          | SSI_RXCL<br>K    | Ι     |             |               |           | PC4  | 69K         |               |     |                | PC4     |

| NVDD3                 | A7          | C8          | SSI_RXFS         | Ι     |             |               |           | PC3  | 69K         |               |     |                | PC3     |

| NVDD4                 | C7          | C7          | UART2_R<br>XD    | I     |             |               |           | PB31 | 69K         |               |     |                | PB31    |

### Table 3. MC9328MXLMC9328MXS Signal Multiplexing Scheme (Continued)

# **4** Functional Description and Application Information

This section provides the electrical information including and timing diagrams for the individual modules of the i.MXL.

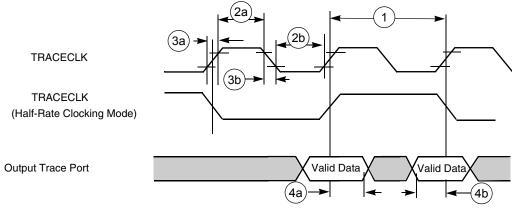

## 4.1 Embedded Trace Macrocell

All registers in the ETM9 are programmed through a JTAG interface. The interface is an extension of the ARM920T processor's TAP controller, and is assigned scan chain 6. The scan chain consists of a 40-bit shift register comprised of the following:

- 32-bit data field

- 7-bit address field

- A read/write bit

The data to be written is scanned into the 32-bit data field, the address of the register into the 7-bit address field, and a 1 into the read/write bit.

A register is read by scanning its address into the address field and a 0 into the read/write bit. The 32-bit data field is ignored. A read or a write takes place when the TAP controller enters the UPDATE-DR state. The timing diagram for the ETM9 is shown in Figure 2. See Table 9 for the ETM9 timing parameters used in Figure 2.

Figure 2. Trace Port Timing Diagram

| Table 9. Trace Port Timing | Diagram Parameter Table |

|----------------------------|-------------------------|

|----------------------------|-------------------------|

| Ref No. | Parameter       | 1.8 ±   | 0.1 V | 3.0 ±   | Unit    |      |

|---------|-----------------|---------|-------|---------|---------|------|

| nei No. | Falameter       | Minimum |       | Minimum | Maximum | Onit |

| 1       | CLK frequency   | 0       | 85    | 0       | 100     | MHz  |

| 2a      | Clock high time | 1.3     | -     | 2       | -       | ns   |

| 2b      | Clock low time  | 3       | -     | 2       | -       | ns   |

| 3a      | Clock rise time | -       | 4     | -       | 3       | ns   |

| 3b      | Clock fall time | _       | 3     | _       | 3       | ns   |

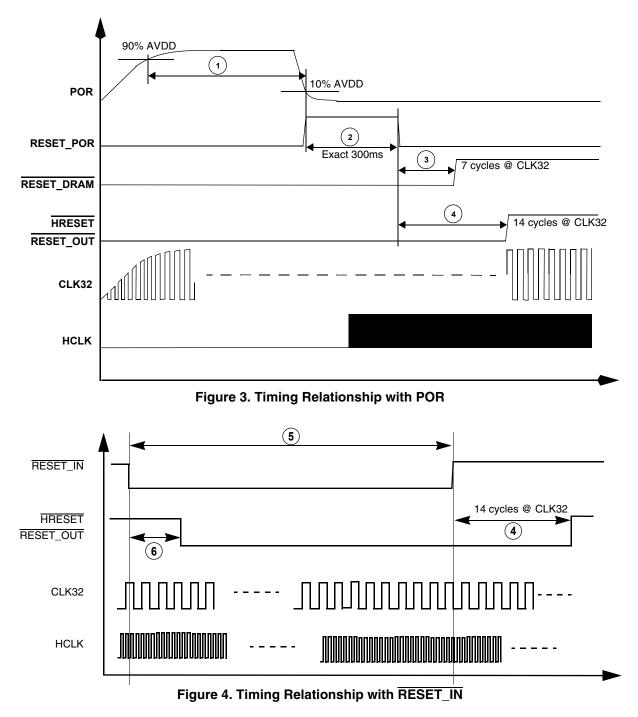

## 4.3 Reset Module

The timing relationships of the Reset module with the POR and RESET\_IN are shown in Figure 3 and Figure 4.

## NOTE

Be aware that NVDD must ramp up to at least 1.8V before QVDD is powered up to prevent forward biasing.

**Functional Description and Application Information**

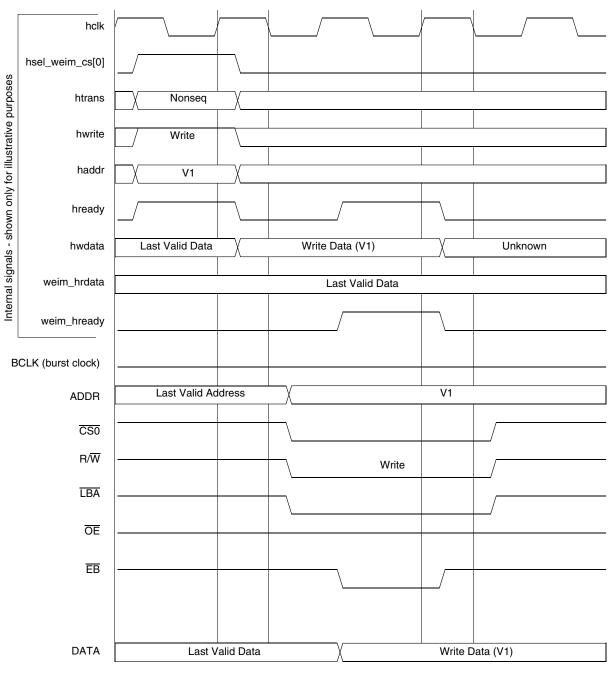

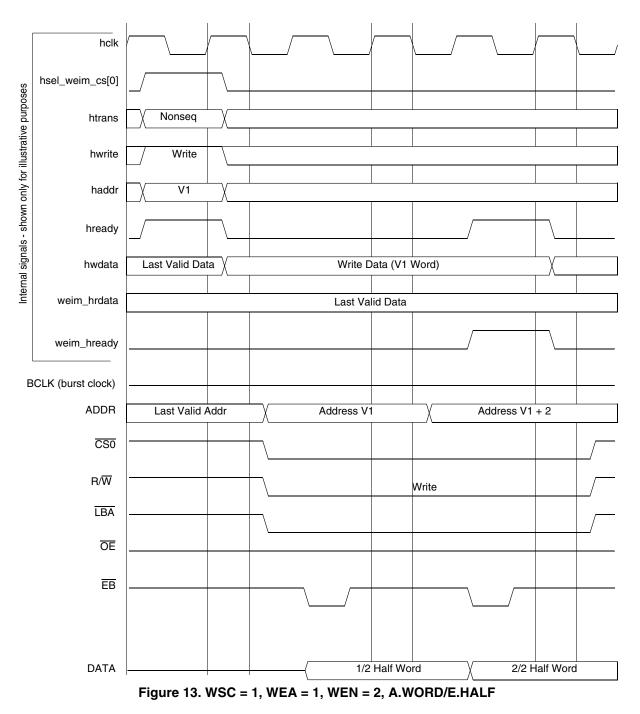

Figure 11. WSC = 1, WEA = 1, WEN = 1, A.HALF/E.HALF

**Functional Description and Application Information**

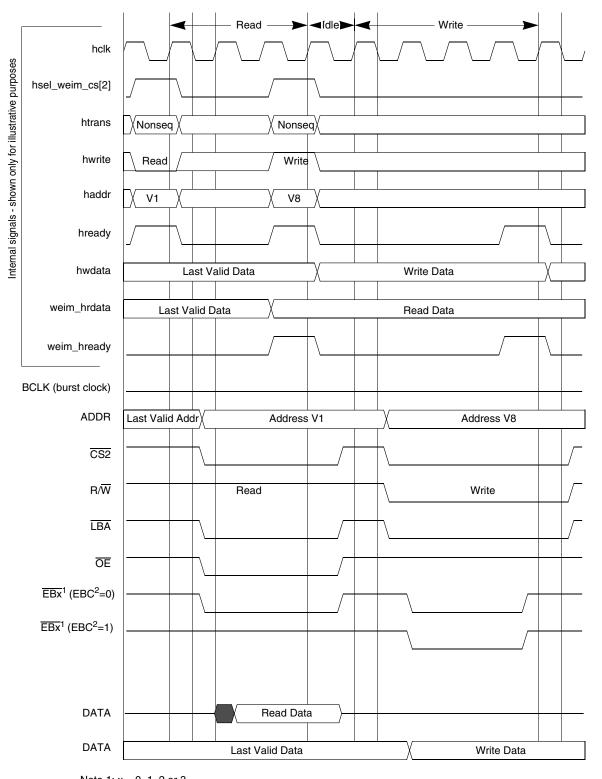

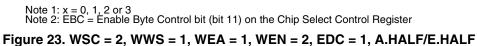

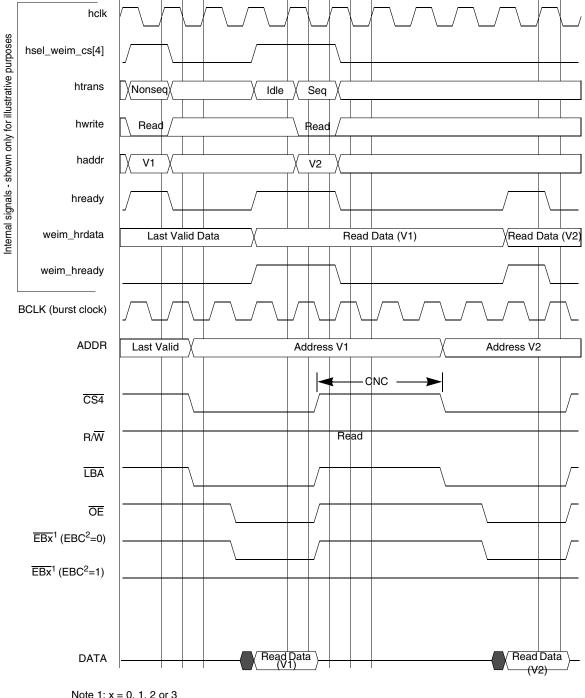

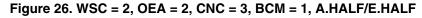

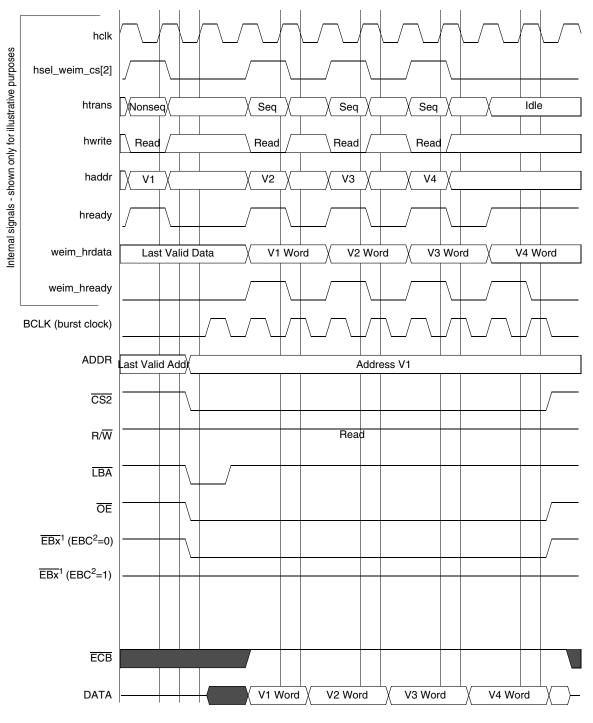

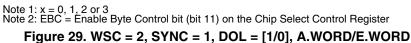

Note 1: x = 0, 1, 2 or 3 Note 2: EBC = Enable Byte Control bit (bit 11) on the Chip Select Control Register

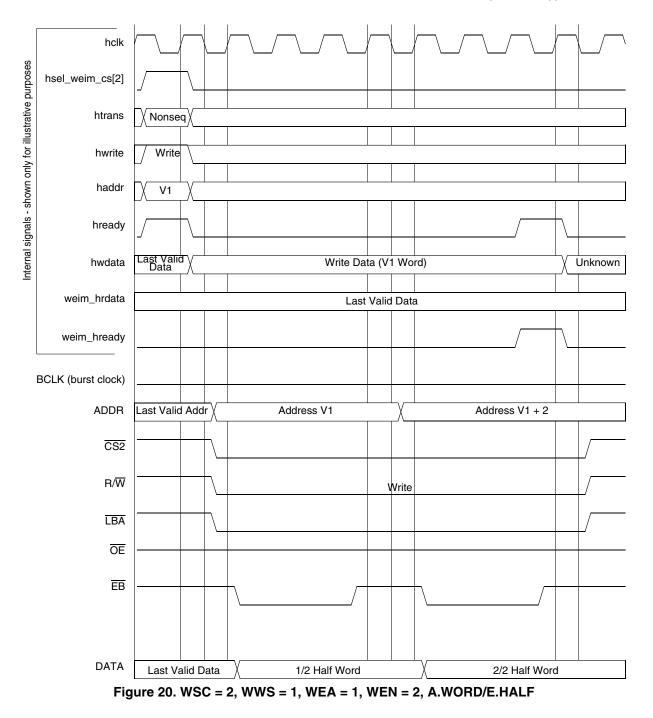

**Functional Description and Application Information**

Functional Description and Application Information

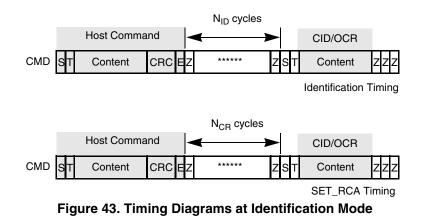

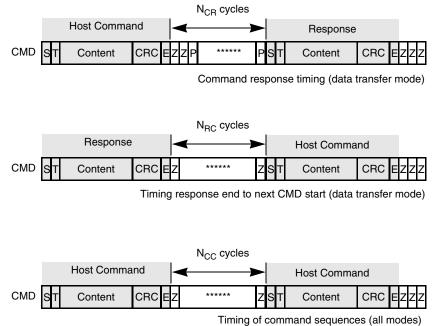

After a card receives its RCA, it switches to data transfer mode. As shown on the first diagram in Figure 44, SD\_CMD lines in this mode are driven with push-pull drivers. The command is followed by a period of two Z bits (allowing time for direction switching on the bus) and then by P bits pushed up by the responding card. The other two diagrams show the separating periods  $N_{RC}$  and  $N_{CC}$ .

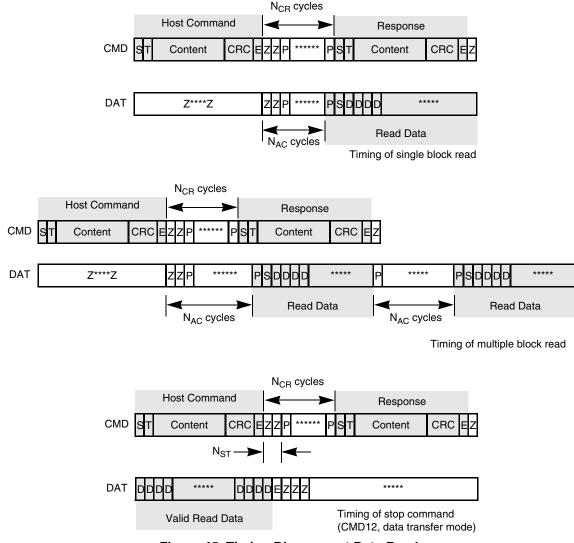

Figure 45 shows basic read operation timing. In a read operation, the sequence starts with a single block read command (which specifies the start address in the argument field). The response is sent on the SD\_CMD lines as usual. Data transmission from the card starts after the access time delay  $N_{AC}$ , beginning from the last bit of the read command. If the system is in multiple block read mode, the card sends a continuous flow of data blocks with distance  $N_{AC}$  until the card sees a stop transmission command. The data stops two clock cycles after the end bit of the stop command.

**Functional Description and Application Information**

Figure 45. Timing Diagrams at Data Read

Figure 46 shows the basic write operation timing. As with the read operation, after the card response, the data transfer starts after  $N_{WR}$  cycles. The data is suffixed with CRC check bits to allow the card to check for transmission errors. The card sends back the CRC check result as a CC status token on the data line. If there was a transmission error, the card sends a negative CRC status (101); otherwise, a positive CRC status (010) is returned. The card expects a continuous flow of data blocks if it is configured to multiple block mode, with the flow terminated by a stop transmission command.

| Ref No. | Parameter                            | 1.8 ±   | 0.1 V   | 3.0 ±   | Unit    |      |

|---------|--------------------------------------|---------|---------|---------|---------|------|

| ner No. | Falameter                            | Minimum | Maximum | Minimum | Maximum | Onit |

| 1       | Hold time (repeated) START condition | 182     | _       | 160     | -       | ns   |

| 2       | Data hold time                       | 0       | 171     | 0       | 150     | ns   |

| 3       | Data setup time                      | 11.4    | _       | 10      | -       | ns   |

| 4       | HIGH period of the SCL clock         | 80      | _       | 120     | -       | ns   |

| 5       | LOW period of the SCL clock          | 480     | _       | 320     | -       | ns   |

| 6       | Setup time for STOP condition        | 182.4   | _       | 160     | _       | ns   |

### Table 32. I<sup>2</sup>C Bus Timing Parameter Table

## 4.13 Synchronous Serial Interface

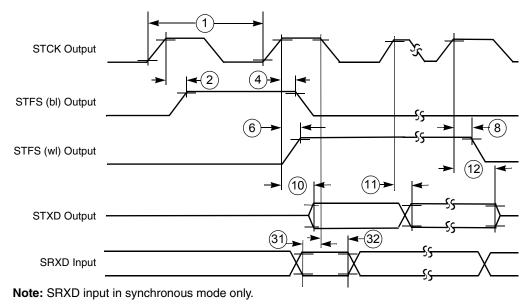

The transmit and receive sections of the SSI can be synchronous or asynchronous. In synchronous mode, the transmitter and the receiver use a common clock and frame synchronization signal. In asynchronous mode, the transmitter and receiver each have their own clock and frame synchronization signals. Continuous or gated clock mode can be selected. In continuous mode, the clock runs continuously. In gated clock mode, the clock functions only during transmission. The internal and external clock timing diagrams are shown in Figure 60 through Figure 62.

Normal or network mode can also be selected. In normal mode, the SSI functions with one data word of I/O per frame. In network mode, a frame can contain between 2 and 32 data words. Network mode is typically used in star or ring-time division multiplex networks with other processors or codecs, allowing interface to time division multiplexed networks without additional logic. Use of the gated clock is not allowed in network mode. These distinctions result in the basic operating modes that allow the SSI to communicate with a wide variety of devices.

Figure 59. SSI Transmitter Internal Clock Timing Diagram

| Ref No. | Boremeter                                   | 1.8 ±          | 0.1 V        | 3.0 ±                | 0.3 V   | Unit |

|---------|---------------------------------------------|----------------|--------------|----------------------|---------|------|

| Ref No. | Parameter                                   | Minimum        | Maximum      | Minimum              | Maximum | Unit |

| 18      | STCK high to STFS (bl) high <sup>3</sup>    | _              | 92.8         | 0                    | 81.4    | ns   |

| 19      | SRCK high to SRFS (bl) high <sup>3</sup>    | -              | 92.8         | 0                    | 81.4    | ns   |

| 20      | STCK high to STFS (bl) low <sup>3</sup>     | -              | 92.8         | 0                    | 81.4    | ns   |

| 21      | SRCK high to SRFS (bl) low <sup>3</sup>     | -              | 92.8         | 0                    | 81.4    | ns   |

| 22      | STCK high to STFS (wl) high <sup>3</sup>    | -              | 92.8         | 0                    | 81.4    | ns   |

| 23      | SRCK high to SRFS (wl) high <sup>3</sup>    | -              | 92.8         | 0                    | 81.4    | ns   |

| 24      | STCK high to STFS (wl) low <sup>3</sup>     | -              | 92.8         | 0                    | 81.4    | ns   |

| 25      | SRCK high to SRFS (wl) low <sup>3</sup>     | -              | 92.8         | 0                    | 81.4    | ns   |

| 26      | STCK high to STXD valid from high impedance | 18.01          | 28.16        | 15.8                 | 24.7    | ns   |

| 27a     | STCK high to STXD high                      | 8.98           | 18.13        | 7.0                  | 15.9    | ns   |

| 27b     | STCK high to STXD low                       | 9.12           | 18.24        | 8.0                  | 16.0    | ns   |

| 28      | STCK high to STXD high impedance            | 18.47          | 28.5         | 16.2                 | 25.0    | ns   |

| 29      | SRXD setup time before SRCK low             | 1.14           | -            | 1.0                  | _       | ns   |

| 30      | SRXD hole time after SRCK low               | 0              | -            | 0                    | -       | ns   |

|         | Synchronous Internal Clock Oper             | ration (Port C | Primary Fund | ction <sup>2</sup> ) |         |      |

| 31      | SRXD setup before STCK falling              | 15.4           | _            | 13.5                 | _       | ns   |

| 32      | SRXD hold after STCK falling                | 0              | _            | 0                    | _       | ns   |

|         | Synchronous External Clock Ope              | ration (Port C | Primary Fun  | ction <sup>2</sup> ) | 1       |      |

| 33      | SRXD setup before STCK falling              | 1.14           | _            | 1.0                  | _       | ns   |

| 34      | SRXD hold after STCK falling                | 0              | -            | 0                    | -       | ns   |

### Table 33. SSI (Port C Primary Function) Timing Parameter Table (Continued)

<sup>1</sup> All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

<sup>2</sup> There are 2 sets of I/O signals for the SSI module. They are from Port C primary function (pad 257 to pad 261) and Port B alternate function (pad 283 to pad 288). When SSI signals are configured as outputs, they can be viewed both at Port C primary function and Port B alternate function. When SSI signals are configured as input, the SSI module selects the input based on status of the FMCR register bits in the Clock controller module (CRM). By default, the input are selected from Port C primary function.

<sup>3</sup> bl = bit length; wl = word length.

| Ref | <b>D</b>                                    | 1.8 ±                       | 0.1 V          | 3.0 ±             | 0.3 V   |      |

|-----|---------------------------------------------|-----------------------------|----------------|-------------------|---------|------|

| No. | Parameter                                   | Minimum                     | Maximum        | Minimum           | Maximum | Unit |

|     | Internal Clock Operati                      | on <sup>1</sup> (Port B Alt | ernate Functio | on <sup>2</sup> ) |         |      |

| 1   | STCK/SRCK clock period <sup>1</sup>         | 95                          | _              | 83.3              | _       | ns   |

| 2   | STCK high to STFS (bl) high <sup>3</sup>    | 1.7                         | 4.8            | 1.5               | 4.2     | ns   |

| 3   | SRCK high to SRFS (bl) high <sup>3</sup>    | -0.1                        | 1.0            | -0.1              | 1.0     | ns   |

| 4   | STCK high to STFS (bl) low <sup>3</sup>     | 3.08                        | 5.24           | 2.7               | 4.6     | ns   |

| 5   | SRCK high to SRFS (bl) low <sup>3</sup>     | 1.25                        | 2.28           | 1.1               | 2.0     | ns   |

| 6   | STCK high to STFS (wl) high <sup>3</sup>    | 1.71                        | 4.79           | 1.5               | 4.2     | ns   |

| 7   | SRCK high to SRFS (wl) high <sup>3</sup>    | -0.1                        | 1.0            | -0.1              | 1.0     | ns   |

| 8   | STCK high to STFS (wl) low <sup>3</sup>     | 3.08                        | 5.24           | 2.7               | 4.6     | ns   |

| 9   | SRCK high to SRFS (wI) low <sup>3</sup>     | 1.25                        | 2.28           | 1.1               | 2.0     | ns   |

| 10  | STCK high to STXD valid from high impedance | 14.93                       | 16.19          | 13.1              | 14.2    | ns   |

| 11a | STCK high to STXD high                      | 1.25                        | 3.42           | 1.1               | 3.0     | ns   |

| 11b | STCK high to STXD low                       | 2.51                        | 3.99           | 2.2               | 3.5     | ns   |

| 12  | STCK high to STXD high impedance            | 12.43                       | 14.59          | 10.9              | 12.8    | ns   |

| 13  | SRXD setup time before SRCK low             | 20                          | _              | 17.5              | _       | ns   |

| 14  | SRXD hold time after SRCK low               | 0                           | _              | 0                 | _       | ns   |

|     | External Clock Operat                       | tion (Port B Alt            | ernate Functio | on <sup>2</sup> ) |         |      |

| 15  | STCK/SRCK clock period <sup>1</sup>         | 92.8                        | _              | 81.4              | _       | ns   |

| 16  | STCK/SRCK clock high period                 | 27.1                        | _              | 40.7              | _       | ns   |

| 17  | STCK/SRCK clock low period                  | 61.1                        | _              | 40.7              | _       | ns   |

| 18  | STCK high to STFS (bl) high <sup>3</sup>    | _                           | 92.8           | 0                 | 81.4    | ns   |

| 19  | SRCK high to SRFS (bl) high <sup>3</sup>    | _                           | 92.8           | 0                 | 81.4    | ns   |

| 20  | STCK high to STFS (bl) low <sup>3</sup>     | _                           | 92.8           | 0                 | 81.4    | ns   |

| 21  | SRCK high to SRFS (bl) low <sup>3</sup>     | _                           | 92.8           | 0                 | 81.4    | ns   |

| 22  | STCK high to STFS (wl) high <sup>3</sup>    | _                           | 92.8           | 0                 | 81.4    | ns   |

| 23  | SRCK high to SRFS (wl) high <sup>3</sup>    | _                           | 92.8           | 0                 | 81.4    | ns   |

| 24  | STCK high to STFS (wl) low <sup>3</sup>     | _                           | 92.8           | 0                 | 81.4    | ns   |

| 25  | SRCK high to SRFS (wl) low <sup>3</sup>     | _                           | 92.8           | 0                 | 81.4    | ns   |

| 26  | STCK high to STXD valid from high impedance | 18.9                        | 29.07          | 16.6              | 25.5    | ns   |

| 27a | STCK high to STXD high                      | 9.23                        | 20.75          | 8.1               | 18.2    | ns   |

| 27b | STCK high to STXD low                       | 10.60                       | 21.32          | 9.3               | 18.7    | ns   |

### Table 34. SSI (Port B Alternate Function) Timing Parameter Table

|                                                                                | •                                |                | -               | -                      | -       |      |  |

|--------------------------------------------------------------------------------|----------------------------------|----------------|-----------------|------------------------|---------|------|--|

| Ref                                                                            | Parameter                        | 1.8 ±          | 0.1 V           | 3.0 ±                  | Unit    |      |  |

| No.                                                                            | Falameter                        | Minimum        | Maximum         | Minimum                | Maximum | Onit |  |

| 28                                                                             | STCK high to STXD high impedance | 17.90          | 29.75           | 15.7                   | 26.1    | ns   |  |

| 29                                                                             | SRXD setup time before SRCK low  | 1.14           | -               | 1.0                    | -       | ns   |  |

| 30                                                                             | SRXD hold time after SRCK low    | 0              | _               | 0                      | -       | ns   |  |

|                                                                                | Synchronous Internal Clock C     | Operation (Por | t B Alternate F | unction <sup>2</sup> ) |         |      |  |

| 31                                                                             | SRXD setup before STCK falling   | 18.81          | -               | 16.5                   | -       | ns   |  |

| 32                                                                             | SRXD hold after STCK falling     | 0              | -               | 0                      | -       | ns   |  |

| Synchronous External Clock Operation (Port B Alternate Function <sup>2</sup> ) |                                  |                |                 |                        |         |      |  |

| 33                                                                             | SRXD setup before STCK falling   | 1.14           | -               | 1.0                    | _       | ns   |  |

| 34                                                                             | 34 SRXD hold after STCK falling  |                | _               | 0                      | _       | ns   |  |

### Table 34. SSI (Port B Alternate Function) Timing Parameter Table (Continued)

<sup>1</sup> All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

<sup>2</sup> There are 2 set of I/O signals for the SSI module. They are from Port C primary function (pad 257 to pad 261) and Port B alternate function (pad 283 to pad 288). When SSI signals are configured as outputs, they can be viewed both at Port C primary function and Port B alternate function. When SSI signals are configured as inputs, the SSI module selects the input based on FMCR register bits in the Clock controller module (CRM). By default, the input are selected from Port C primary function.

<sup>3</sup> bl = bit length; wl = word length.

## 4.14 CMOS Sensor Interface

The CMOS Sensor Interface (CSI) module consists of a control register to configure the interface timing, a control register for statistic data generation, a status register, interface logic, a  $32 \times 32$  image data receive FIFO, and a  $16 \times 32$  statistic data FIFO.

## 4.14.1 Gated Clock Mode

Figure 63 shows the timing diagram when the CMOS sensor output data is configured for negative edge and the CSI is programmed to received data on the positive edge. Figure 64 shows the timing diagram when the CMOS sensor output data is configured for positive edge and the CSI is programmed to received data in negative edge. The parameters for the timing diagrams are listed in Table 35.

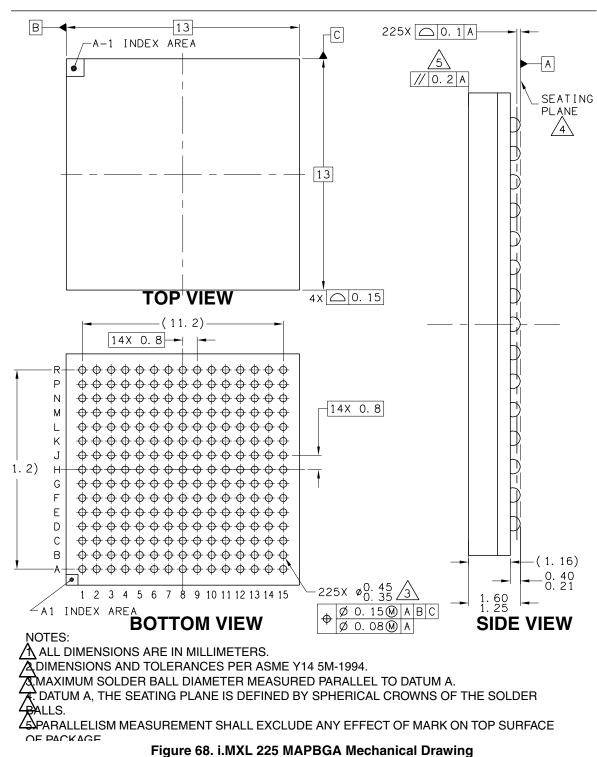

## 5.2 MAPBGA 225 Package Dimensions

Figure 68 illustrates the 225 MAPBGA 13 mm × 13 mm package.

### Case Outline 1304B

Product Documentation

# 6 **Product Documentation**

## 6.1 Revision History

Table 39 provides revision history for this release. This history includes technical content revisions only and not stylistic or grammatical changes.

| Location                                              | Revision                                                                                                                                                                                                                                                                |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2 on page 4<br>Signal Names and<br>Descriptions | <ul> <li>Added the DMA_REQ signal to table.</li> <li>Corrected signal name from USBD_OE to USBD_ROE</li> </ul>                                                                                                                                                          |

| Table 3 on page 9<br>Signal Multiplex Table i.MXL     | <ul> <li>Added Signal Multiplex table from Reference Manual with the following changes:</li> <li>Changed I/O Supply Voltage,PB31–20, from NVDD3 to NVDD4</li> <li>Added 225 BGA column.</li> <li>Removed 69K pull-up resistor from EB1, EB2, and added to D9</li> </ul> |

| Table 10 on page 21                                   | Changed first and second parameters descriptions:<br>From: Reference Clock freq range, To: DPLL input clock freq range<br>From: Double clock freq range, To: DPLL output freq range                                                                                     |

| Table 3 on page 9                                     | Added Signal Multiplex table.                                                                                                                                                                                                                                           |

### Table 39. i.MXL Data Sheet Revision History Rev. 8

## 6.2 Reference Documents

The following documents are required for a complete description of the MC9328MXL and are necessary to design properly with the device. Especially for those not familiar with the ARM920T processor or previous i.MX processor products, the following documents are helpful when used in conjunction with this document.

ARM Architecture Reference Manual (ARM Ltd., order number ARM DDI 0100)

ARM9DT1 Data Sheet Manual (ARM Ltd., order number ARM DDI 0029)

ARM Technical Reference Manual (ARM Ltd., order number ARM DDI 0151C)

EMT9 Technical Reference Manual (ARM Ltd., order number DDI O157E)

MC9328MXL Product Brief (order number MC9328MXLP)

MC9328MXL Reference Manual (order number MC9328MXLRM)

The Freescale manuals are available on the Freescale Semiconductors Web site at http://www.freescale.com/imx. These documents may be downloaded directly from the Freescale Web site, or printed versions may be ordered. The ARM Ltd. documentation is available from http://www.arm.com.

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-521-6274 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: MC9328MXL Rev. 8 12/2006 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. ARM and the ARM POWERED logo are the registered trademarks of ARM Limited. ARM9, ARM920T, and ARM9TDMI are the trademarks of ARM Limited. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2006. All rights reserved.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.