#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Details                         |                                                            |

|---------------------------------|------------------------------------------------------------|

| Product Status                  | Active                                                     |

| Core Processor                  | ARM920T                                                    |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 150MHz                                                     |

| Co-Processors/DSP               | -                                                          |

| RAM Controllers                 | SDRAM                                                      |

| Graphics Acceleration           | Νο                                                         |

| Display & Interface Controllers | LCD                                                        |

| Ethernet                        | -                                                          |

| SATA                            | -                                                          |

| USB                             | USB 1.x (1)                                                |

| Voltage - I/O                   | 1.8V, 3.0V                                                 |

| Operating Temperature           | 0°C ~ 70°C (TA)                                            |

| Security Features               | -                                                          |

| Package / Case                  | 225-LFBGA                                                  |

| Supplier Device Package         | 225-MAPBGA (13x13)                                         |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9328mxlvp15 |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

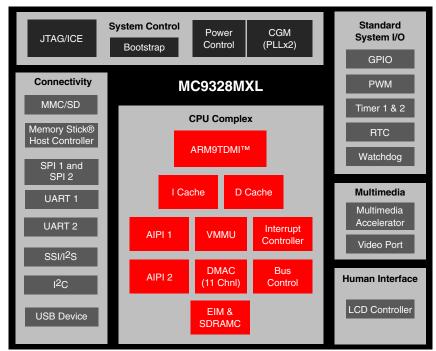

Introduction

Figure 1. i.MXL Functional Block Diagram

## 1.1 Features

To support a wide variety of applications, the processor offers a robust array of features, including the following:

- ARM920T<sup>TM</sup> Microprocessor Core

- AHB to IP Bus Interfaces (AIPIs)

- External Interface Module (EIM)

- SDRAM Controller (SDRAMC)

- DPLL Clock and Power Control Module

- Two Universal Asynchronous Receiver/Transmitters (UART 1 and UART 2)

- Serial Peripheral Interface (SPI)

- Two General-Purpose 32-bit Counters/Timers

- Watchdog Timer

- Real-Time Clock/Sampling Timer (RTC)

- LCD Controller (LCDC)

- Pulse-Width Modulation (PWM) Module

- Universal Serial Bus (USB) Device

- Multimedia Card and Secure Digital (MMC/SD) Host Controller Module

- Memory Stick<sup>®</sup> Host Controller (MSHC)

- Direct Memory Access Controller (DMAC)

- Synchronous Serial Interface and an Inter-IC Sound (SSI/I<sup>2</sup>S) Module

- Inter-IC (I<sup>2</sup>C) Bus Module

## Table 2. i.MXL Signal Descriptions (Continued)

| Signal Name | Function/Notes                                                                                                                                                                                                                                                                           |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Bootstrap                                                                                                                                                                                                                                                                                |

| BOOT [3:0]  | System Boot Mode Select—The operational system boot mode of the i.MXL processor upon system reset is determined by the settings of these pins.                                                                                                                                           |

|             | SDRAM Controller                                                                                                                                                                                                                                                                         |

| SDBA [4:0]  | SDRAM non-interleave mode bank address multiplexed with address signals A [15:11]. These signals are logically equivalent to core address p_addr [25:21] in SDRAM cycles.                                                                                                                |

| SDIBA [3:0] | SDRAM interleave addressing mode bank address multiplexed with address signals A [19:16]. These signals are logically equivalent to core address p_addr [12:9] in SDRAM cycles.                                                                                                          |

| MA [11:10]  | SDRAM address signals                                                                                                                                                                                                                                                                    |

| MA [9:0]    | SDRAM address signals which are multiplexed with address signals A [10:1]. MA [9:0] are selected on SDRAM cycles.                                                                                                                                                                        |

| DQM [3:0]   | SDRAM data enable                                                                                                                                                                                                                                                                        |

| CSD0        | SDRAM Chip-select signal which is multiplexed with the $\overline{CS2}$ signal. These two signals are selectable by programming the system control register.                                                                                                                             |

| CSD1        | SDRAM Chip-select signal which is multiplexed with $\overline{CS3}$ signal. These two signals are selectable by programming the system control register. By default, $\overline{CSD1}$ is selected, so it can be used as boot chip-select by properly configuring BOOT [3:0] input pins. |

| RAS         | SDRAM Row Address Select signal                                                                                                                                                                                                                                                          |

| CAS         | SDRAM Column Address Select signal                                                                                                                                                                                                                                                       |

| SDWE        | SDRAM Write Enable signal                                                                                                                                                                                                                                                                |

| SDCKE0      | SDRAM Clock Enable 0                                                                                                                                                                                                                                                                     |

| SDCKE1      | SDRAM Clock Enable 1                                                                                                                                                                                                                                                                     |

| SDCLK       | SDRAM Clock                                                                                                                                                                                                                                                                              |

| RESET_SF    | Not Used                                                                                                                                                                                                                                                                                 |

|             | Clocks and Resets                                                                                                                                                                                                                                                                        |

| EXTAL16M    | Crystal input (4 MHz to 16 MHz), or a 16 MHz oscillator input when the internal oscillator circuit is shut down.                                                                                                                                                                         |

| XTAL16M     | Crystal output                                                                                                                                                                                                                                                                           |

| EXTAL32K    | 32 kHz crystal input                                                                                                                                                                                                                                                                     |

| XTAL32K     | 32 kHz crystal output                                                                                                                                                                                                                                                                    |

| CLKO        | Clock Out signal selected from internal clock signals.                                                                                                                                                                                                                                   |

| RESET_IN    | Master Reset—External active low Schmitt trigger input signal. When this signal goes active, all modules (except the reset module and the clock control module) are reset.                                                                                                               |

| RESET_OUT   | Reset Out—Internal active low output signal from the Watchdog Timer module and is asserted from the following sources: Power-on reset, External reset (RESET_IN), and Watchdog time-out.                                                                                                 |

| POR         | Power On Reset—Internal active high Schmitt trigger input signal. The POR signal is normally generated by an external RC circuit designed to detect a power-up event.                                                                                                                    |

|                       | 225         | 256         | Pi             | imary |             | Altern | ate | GP   | 10          |     |              |                |         |

|-----------------------|-------------|-------------|----------------|-------|-------------|--------|-----|------|-------------|-----|--------------|----------------|---------|

| I/O Supply<br>Voltage | BGA<br>Ball | BGA<br>Ball | Signal         | Dir   | Pull-<br>Up | Signal | Dir | Mux  | Pull<br>-Up | AIN | BIN          | AOUT           | Default |

| NVDD2                 | H13         | N13         | CSI_PIXC<br>LK | I     |             |        |     | PA14 | 69K         |     |              |                | PA14    |

| NVDD2                 | G14         | M13         | CSI_HSY<br>NC  | I     |             |        |     | PA13 | 69K         |     |              |                | PA13    |

| NVDD2                 | H12         | M14         | CSI_VSY<br>NC  | I     |             |        |     | PA12 | 69K         |     |              |                | PA12    |

| NVDD2                 | G13         | N14         | CSI_D7         | Ι     |             |        |     | PA11 | 69K         |     |              |                | PA11    |

| NVDD2                 | J10         | M15         | CSI_D6         | Ι     |             |        |     | PA10 | 69K         |     |              |                | PA10    |

| NVDD2                 | G15         | M16         | CSI_D5         | Ι     |             |        |     | PA9  | 69K         |     |              |                | PA9     |

| NVDD2                 | F15         | M12         | CSI_D4         | Ι     |             |        |     | PA8  | 69K         |     |              |                | PA8     |

| NVDD2                 | G12         | L16         | CSI_D3         | Ι     |             |        |     | PA7  | 69K         |     |              |                | PA7     |

| NVDD2                 | F14         | L15         | CSI_D2         | Ι     |             |        |     | PA6  | 69K         |     |              |                | PA6     |

| NVDD2                 | H11         | L14         | CSI_D1         | Ι     |             |        |     | PA5  | 69K         |     |              |                | PA5     |

| NVDD2                 | E14         | L13         | CSI_D0         | Ι     |             |        |     | PA4  | 69K         |     |              |                | PA4     |

| NVDD2                 | E15         | L12         | CSI_MCL<br>K   | 0     |             |        |     | PA3  | 69K         |     |              |                | PA3     |

| NVDD2                 | G11         | L11         | PWMO           | 0     |             |        |     | PA2  | 69K         |     |              |                | PA2     |

| NVDD2                 | E13         | L10         | TIN            | ļ     |             |        |     | PA1  | 69K         |     |              | SPI2_<br>RXD_0 | PA1     |

| NVDD2                 | D14         | K15         | TMR2OUT        | 0     |             |        |     | PD31 | 69K         |     | SPI2_<br>TXD |                | PD31    |

| NVDD2                 | F13         | K16         | LD15           | 0     |             |        |     | PD30 | 69K         |     |              |                | PD30    |

| NVDD2                 | F12         | K14         | LD14           | 0     |             |        |     | PD29 | 69K         |     |              |                | PD29    |

| NVDD2                 | D15         | K13         | LD13           | 0     |             |        |     | PD28 | 69K         |     |              |                | PD28    |

| NVDD2                 | C14         | K12         | LD12           | 0     |             |        |     | PD27 | 69K         |     |              |                | PD27    |

| NVDD2                 | D13         | J14         | LD11           | 0     |             |        |     | PD26 | 69K         |     |              |                | PD26    |

| NVDD2                 | E12         | K11         | LD10           | 0     |             |        |     | PD25 | 69K         |     |              |                | PD25    |

| NVDD2                 | C13         | H15         | LD9            | 0     |             |        |     | PD24 | 69K         |     |              |                | PD24    |

| NVDD2                 | C12         | J13         | LD8            | 0     |             |        |     | PD23 | 69K         |     |              |                | PD23    |

| NVDD2                 | B15         | J12         | LD7            | 0     |             |        |     | PD22 | 69K         |     |              |                | PD22    |

| NVDD2                 | B14         | J11         | LD6            | 0     |             |        |     | PD21 | 69K         |     |              |                | PD21    |

| NVDD2                 | A15         | H14         | LD5            | 0     |             |        |     | PD20 | 69K         |     |              |                | PD20    |

| NVDD2                 | A14         | H13         | LD4            | 0     |             |        | 1   | PD19 | 69K         |     | 1            |                | PD19    |

| NVDD2                 | B13         | H16         | LD3            | 0     |             |        |     | PD18 | 69K         |     |              |                | PD18    |

| NVDD2                 | A13         | H12         | LD2            | 0     |             |        | 1   | PD17 | 69K         |     | 1            |                | PD17    |

| NVDD2                 | D12         | G16         | LD1            | 0     |             |        | 1   | PD16 | 69K         |     | 1            |                | PD16    |

| NVDD2                 | B12         | H11         | LD0            | 0     |             |        |     | PD15 | 69K         |     |              |                | PD15    |

| NVDD2                 | C11         | G15         | FLM/VSY<br>NC  | 0     |             |        |     | PD14 | 69K         |     |              |                | PD14    |

### Table 3. MC9328MXLMC9328MXS Signal Multiplexing Scheme (Continued)

| Ref | Parameter                                                                                         | 1.8 ±             | 0.1 V | 3.0 ±             | 0.3 V | Unit               |

|-----|---------------------------------------------------------------------------------------------------|-------------------|-------|-------------------|-------|--------------------|

| No. | Falanetei                                                                                         | Min               | Max   | Min               | Max   | Onic               |

| 1   | Width of input POWER_ON_RESET                                                                     | note <sup>1</sup> | _     | note <sup>1</sup> | _     | _                  |

| 2   | Width of internal POWER_ON_RESET<br>(CLK32 at 32 kHz)                                             | 300               | 300   | 300               | 300   | ms                 |

| 3   | 7K to 32K-cycle stretcher for SDRAM reset                                                         | 7                 | 7     | 7                 | 7     | Cycles of<br>CLK32 |

| 4   | 14K to 32K-cycle stretcher for internal system reset<br>HRESERT and output reset at pin RESET_OUT | 14                | 14    | 14                | 14    | Cycles of<br>CLK32 |

| 5   | Width of external hard-reset RESET_IN                                                             | 4                 | -     | 4                 | _     | Cycles of<br>CLK32 |

| 6   | 4K to 32K-cycle qualifier                                                                         | 4                 | 4     | 4                 | 4     | Cycles of<br>CLK32 |

<sup>1</sup> POR width is dependent on the 32 or 32.768 kHz crystal oscillator start-up time. Design margin should allow for crystal tolerance, i.MX chip variations, temperature impact, and supply voltage influence. Through the process of supplying crystals for use with CMOS oscillators, crystal manufacturers have developed a working knowledge of start-up time of their crystals. Typically, start-up times range from 400 ms to 1.2 seconds for this type of crystal.

If an external stable clock source (already running) is used instead of a crystal, the width of POR should be ignored in calculating timing for the start-up process.

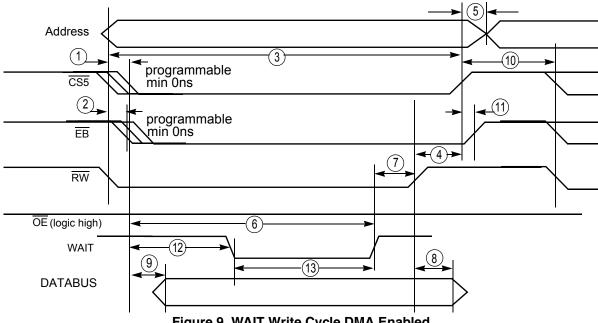

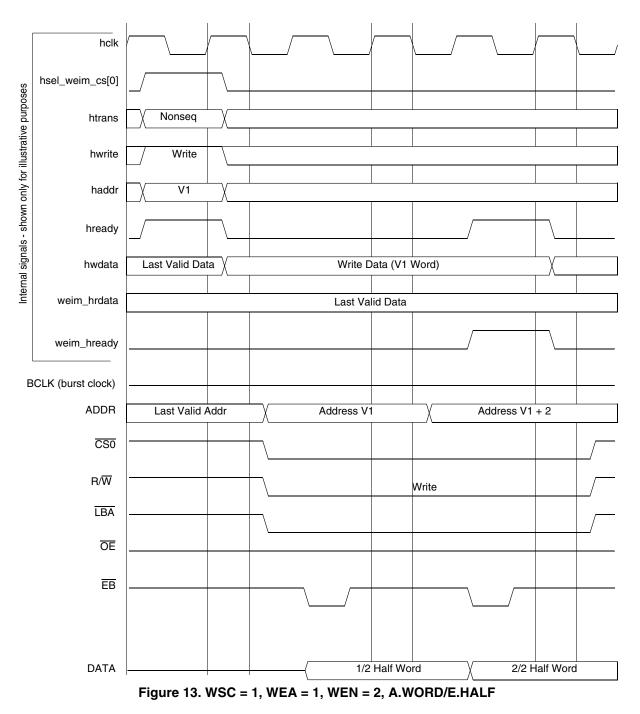

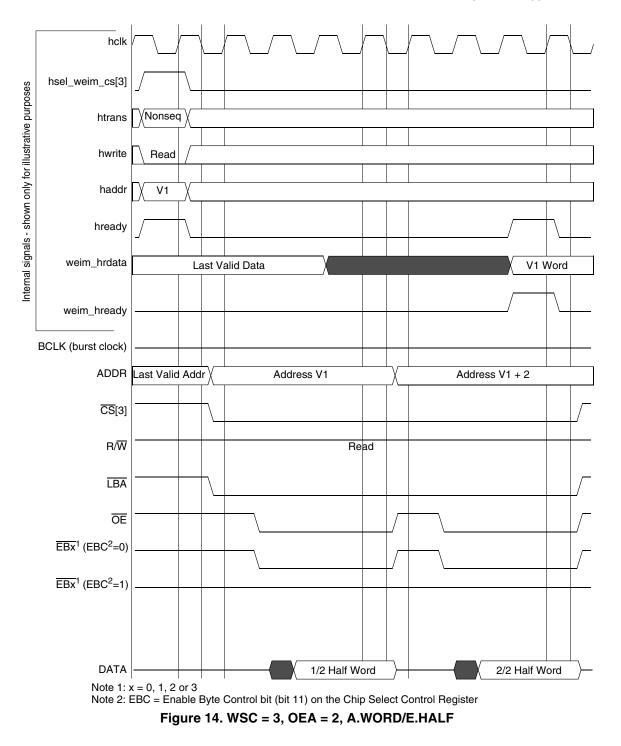

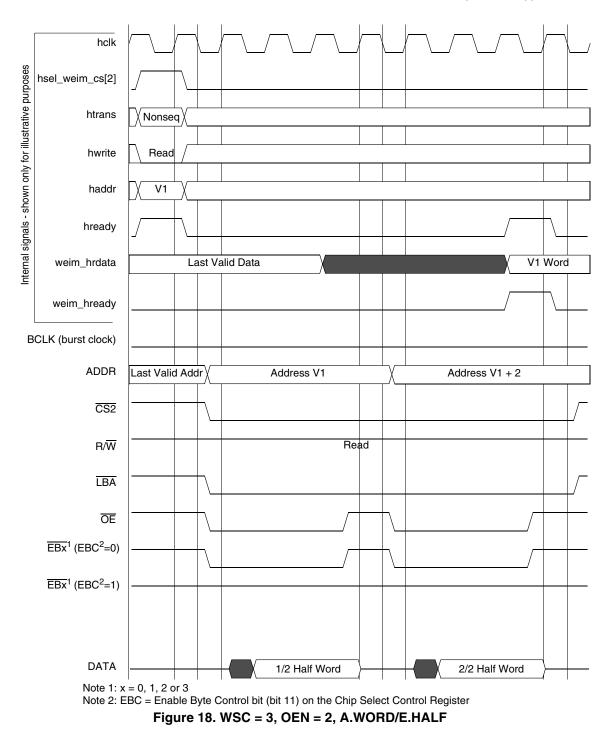

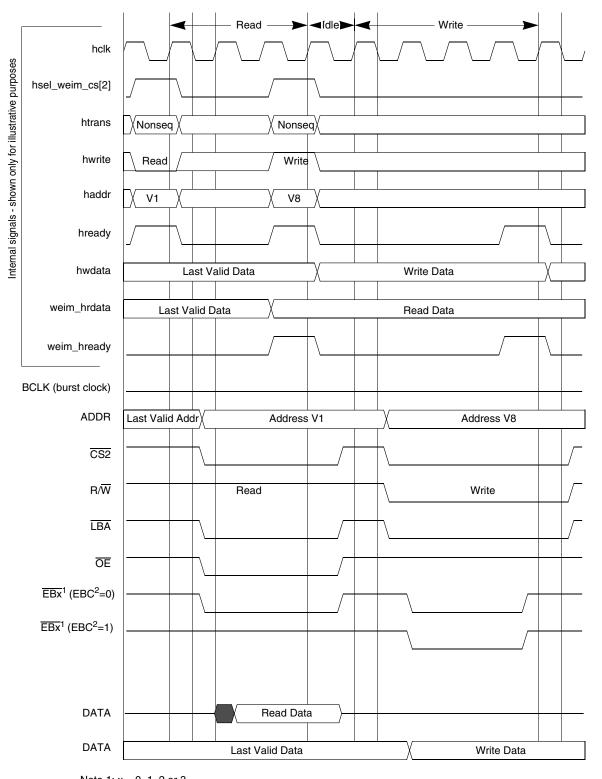

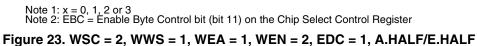

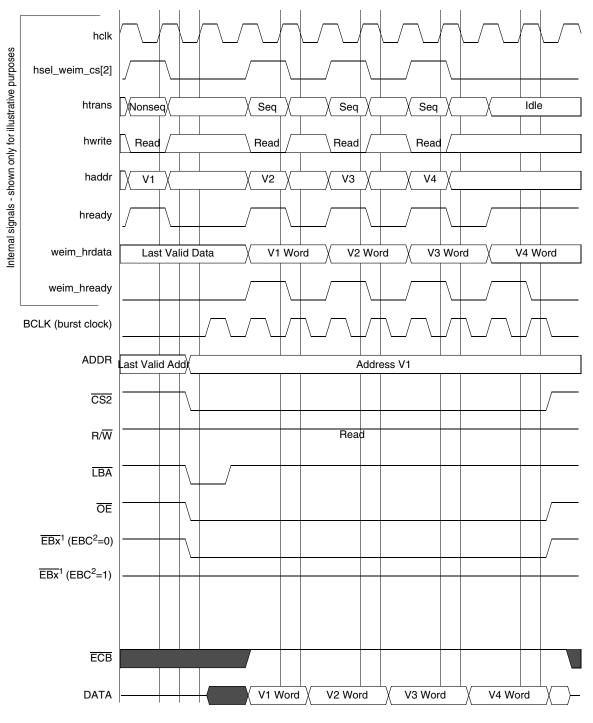

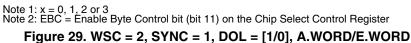

## 4.4 External Interface Module

The External Interface Module (EIM) handles the interface to devices external to the i.MXL processor, including the generation of chip-selects for external peripherals and memory. The timing diagram for the EIM is shown in Figure 5, and Table 12 defines the parameters of signals.

### Table 15. WAIT Write Cycle without DMA: WSC = 111111, DTACK\_SEL=1, HCLK=96MHz (Continued)

| Number | Characteristic                      | 3.0 ± 0.3 V |          |        |  |  |

|--------|-------------------------------------|-------------|----------|--------|--|--|

| Number |                                     | Minimum     | Maximum  | — Unit |  |  |

| 7      | Wait asserted to RW negated         | T+2.66      | 2T+7.96  | ns     |  |  |

| 8      | Data hold timing after RW negated   | 2T+0.03     | -        | ns     |  |  |

| 9      | Data ready after CS5 is asserted    | _           | Т        | ns     |  |  |

| 10     | EB negated after CS5 is negated     | 0.5T        | 0.5T+0.5 | ns     |  |  |

| 11     | Wait becomes low after CS5 asserted | 0           | 1019T    | ns     |  |  |

| 12     | Wait pulse width                    | 1T          | 1020T    | ns     |  |  |

Note:

1. T is the system clock period. (For 96 MHz system clock, T=10.42 ns)

2. CS5 assertion can be controlled by CSA bits. EB assertion can also be programmable by WEA bits in CS5L register.

3. Address becomes valid and  $\overline{RW}$  asserts at the start of write access cycle.

4. The external wait input requirement is eliminated when  $\overline{CS5}$  is programmed to use internal wait state.

#### WAIT Write Cycle DMA Enabled 4.4.2.4

Figure 9. WAIT Write Cycle DMA Enabled

**Functional Description and Application Information**

**Functional Description and Application Information**

**Functional Description and Application Information**

Functional Description and Application Information

Functional Description and Application Information

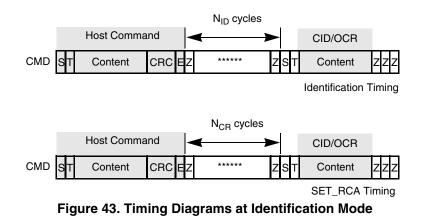

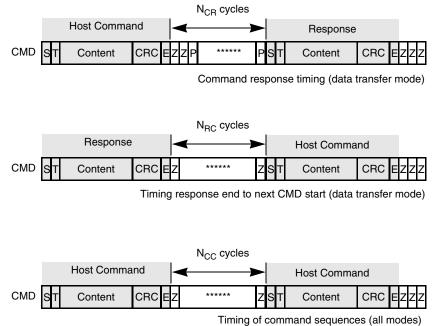

After a card receives its RCA, it switches to data transfer mode. As shown on the first diagram in Figure 44, SD\_CMD lines in this mode are driven with push-pull drivers. The command is followed by a period of two Z bits (allowing time for direction switching on the bus) and then by P bits pushed up by the responding card. The other two diagrams show the separating periods  $N_{RC}$  and  $N_{CC}$ .

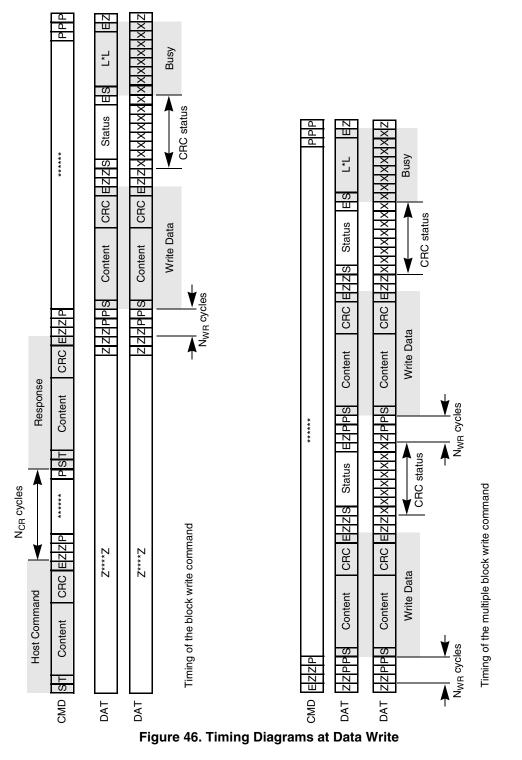

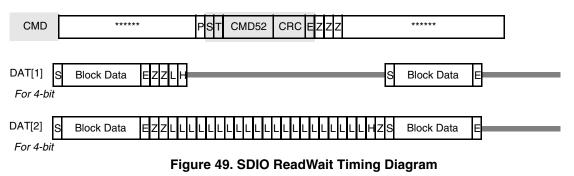

Figure 45 shows basic read operation timing. In a read operation, the sequence starts with a single block read command (which specifies the start address in the argument field). The response is sent on the SD\_CMD lines as usual. Data transmission from the card starts after the access time delay  $N_{AC}$ , beginning from the last bit of the read command. If the system is in multiple block read mode, the card sends a continuous flow of data blocks with distance  $N_{AC}$  until the card sees a stop transmission command. The data stops two clock cycles after the end bit of the stop command.

The stop transmission command may occur when the card is in different states. Figure 47 shows the different scenarios on the bus.

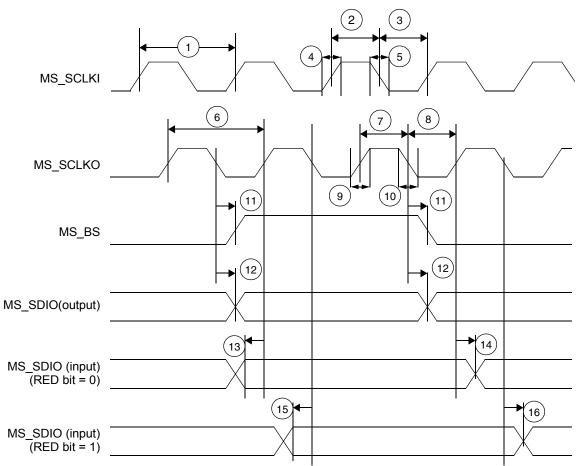

## 4.8 Memory Stick Host Controller

The Memory Stick protocol requires three interface signal line connections for data transfers: MS\_BS, MS\_SDIO, and MS\_SCLKO. Communication is always initiated by the MSHC and operates the bus in either four-state or two-state access mode.

The MS\_BS signal classifies data on the SDIO into one of four states (BS0, BS1, BS2, or BS3) according to its attribute and transfer direction. BS0 is the INT transfer state, and during this state no packet transmissions occur. During the BS1, BS2, and BS3 states, packet communications are executed. The BS1, BS2, and BS3 states are regarded as one packet length and one communication transfer is always completed within one packet length (in four-state access mode).

The Memory Stick usually operates in four state access mode and in BS1, BS2, and BS3 bus states. When an error occurs during packet communication, the mode is shifted to two-state access mode, and the BS0 and BS1 bus states are automatically repeated to avoid a bus collision on the SDIO.

**Functional Description and Application Information**

Figure 50. MSHC Signal Timing Diagram

| Ref | Parameter                              | 3.0 ±   | Unit    |      |

|-----|----------------------------------------|---------|---------|------|

| No. | Falameter                              | Minimum | Maximum | Onit |

| 1   | MS_SCLKI frequency                     | -       | 25      | MHz  |

| 2   | MS_SCLKI high pulse width              | 20      | _       | ns   |

| 3   | MS_SCLKI low pulse width               | 20      | _       | ns   |

| 4   | MS_SCLKI rise time                     | _       | 3       | ns   |

| 5   | MS_SCLKI fall time                     | -       | 3       | ns   |

| 6   | MS_SCLKO frequency <sup>1</sup>        | -       | 25      | MHz  |

| 7   | MS_SCLKO high pulse width <sup>1</sup> | 20      | -       | ns   |

| 8   | MS_SCLKO low pulse width <sup>1</sup>  | 15      | -       | ns   |

| 9   | MS_SCLKO rise time <sup>1</sup>        | -       | 5       | ns   |

| 10  | MS_SCLKO fall time <sup>1</sup>        | _       | 5       | ns   |

| 11  | MS_BS delay time <sup>1</sup>          | _       | 3       | ns   |

| Table 25 | . MSHC | Signal | Timing | Parameter | Table |

|----------|--------|--------|--------|-----------|-------|

|----------|--------|--------|--------|-----------|-------|

**Functional Description and Application Information**

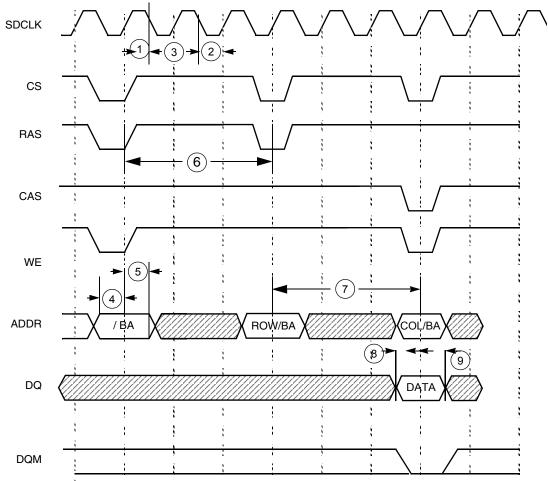

Figure 53. SDRAM Write Cycle Timing Diagram

| Ref No. | Parameter                           | 1.8 ±                        | 0.1 V   | 3.0 ±             | Unit    |      |

|---------|-------------------------------------|------------------------------|---------|-------------------|---------|------|

| nei NO. | Falanelei                           | Minimum                      | Maximum | Minimum           | Maximum | Unit |

| 1       | SDRAM clock high-level width        | 2.67                         | -       | 4                 | _       | ns   |

| 2       | SDRAM clock low-level width         | 6                            | -       | 4                 | -       | ns   |

| 3       | SDRAM clock cycle time              | 11.4                         | -       | 10                | _       | ns   |

| 4       | Address setup time                  | 3.42                         | -       | 3                 | -       | ns   |

| 5       | Address hold time                   | 2.28                         | -       | 2                 | -       | ns   |

| 6       | Precharge cycle period <sup>1</sup> | t <sub>RP</sub> <sup>2</sup> | -       | t <sub>RP2</sub>  | -       | ns   |

| 7       | Active to read/write command delay  | t <sub>RCD2</sub>            | -       | t <sub>RCD2</sub> | -       | ns   |

| 8       | Data setup time                     | 4.0                          | -       | 2                 | -       | ns   |

| 9       | Data hold time                      | 2.28                         | -       | 2                 | -       | ns   |

### Table 28. SDRAM Write Timing Parameter Table

<sup>1</sup> Precharge cycle timing is included in the write timing diagram.

<sup>2</sup>  $t_{RP}$  and  $t_{RCD}$  = SDRAM clock cycle time. These settings can be found in the *MC9328MXL reference manual*.

| Ref No. | Parameter                            | 1.8 ±   | 0.1 V   | 3.0 ±   | Unit    |      |

|---------|--------------------------------------|---------|---------|---------|---------|------|

| ner No. | Falameter                            | Minimum | Maximum | Minimum | Maximum | Unit |

| 1       | Hold time (repeated) START condition | 182     | _       | 160     | -       | ns   |

| 2       | Data hold time                       | 0       | 171     | 0       | 150     | ns   |

| 3       | Data setup time                      | 11.4    | _       | 10      | -       | ns   |

| 4       | HIGH period of the SCL clock         | 80      | _       | 120     | -       | ns   |

| 5       | LOW period of the SCL clock          | 480     | _       | 320     | -       | ns   |

| 6       | Setup time for STOP condition        | 182.4   | _       | 160     | _       | ns   |

### Table 32. I<sup>2</sup>C Bus Timing Parameter Table

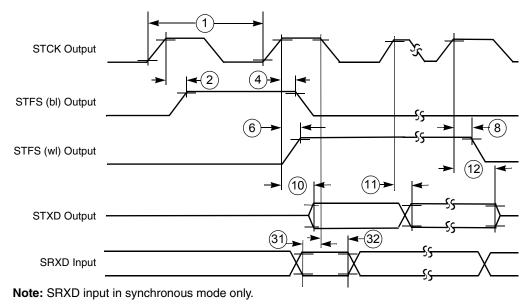

## 4.13 Synchronous Serial Interface

The transmit and receive sections of the SSI can be synchronous or asynchronous. In synchronous mode, the transmitter and the receiver use a common clock and frame synchronization signal. In asynchronous mode, the transmitter and receiver each have their own clock and frame synchronization signals. Continuous or gated clock mode can be selected. In continuous mode, the clock runs continuously. In gated clock mode, the clock functions only during transmission. The internal and external clock timing diagrams are shown in Figure 60 through Figure 62.

Normal or network mode can also be selected. In normal mode, the SSI functions with one data word of I/O per frame. In network mode, a frame can contain between 2 and 32 data words. Network mode is typically used in star or ring-time division multiplex networks with other processors or codecs, allowing interface to time division multiplexed networks without additional logic. Use of the gated clock is not allowed in network mode. These distinctions result in the basic operating modes that allow the SSI to communicate with a wide variety of devices.

Figure 59. SSI Transmitter Internal Clock Timing Diagram

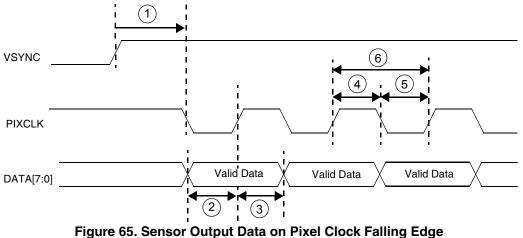

The limitation on pixel clock rise time / fall time are not specified. It should be calculated from the hold time and setup time, according to:

### Rising-edge latch data

max rise time allowed = (positive duty cycle - hold time) max fall time allowed = (negative duty cycle - setup time)

In most of case, duty cycle is 50 / 50, therefore

max rise time = (period / 2 - hold time) max fall time = (period / 2 - setup time)

For example: Given pixel clock period = 10ns, duty cycle = 50 / 50, hold time = 1ns, setup time = 1ns.

positive duty cycle = 10 / 2 = 5ns => max rise time allowed = 5 - 1 = 4ns negative duty cycle = 10 / 2 = 5ns => max fall time allowed = 5 - 1 = 4ns

Falling-edge latch data

max fall time allowed = (negative duty cycle - hold time) max rise time allowed = (positive duty cycle - setup time)

## 4.14.2 Non-Gated Clock Mode

Figure 65 shows the timing diagram when the CMOS sensor output data is configured for negative edge and the CSI is programmed to received data on the positive edge. Figure 66 shows the timing diagram when the CMOS sensor output data is configured for positive edge and the CSI is programmed to received data in negative edge. The parameters for the timing diagrams are listed in Table 36.

CSI Latches Data on Pixel Clock Rising Edge

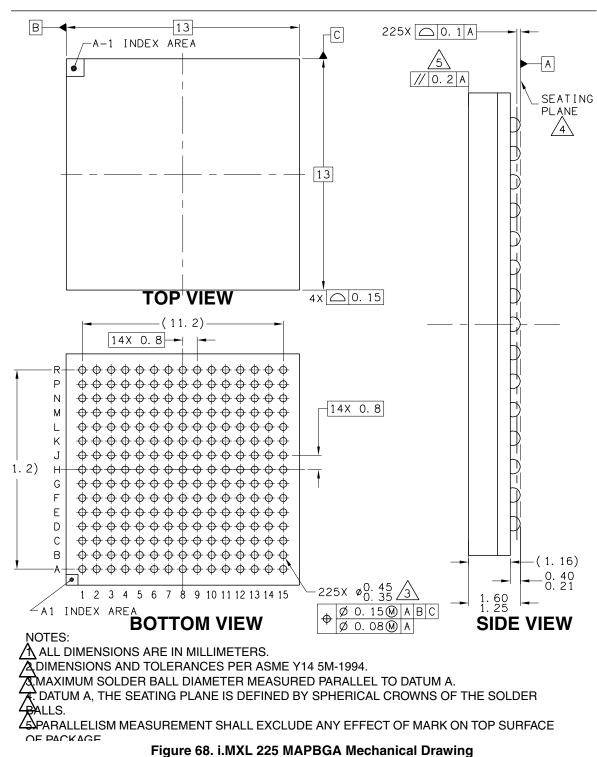

## 5.2 MAPBGA 225 Package Dimensions

Figure 68 illustrates the 225 MAPBGA 13 mm × 13 mm package.

### Case Outline 1304B

Product Documentation

# 6 **Product Documentation**

## 6.1 Revision History

Table 39 provides revision history for this release. This history includes technical content revisions only and not stylistic or grammatical changes.

| Location                                              | Revision                                                                                                                                                                                                                                                                |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2 on page 4<br>Signal Names and<br>Descriptions | <ul> <li>Added the DMA_REQ signal to table.</li> <li>Corrected signal name from USBD_OE to USBD_ROE</li> </ul>                                                                                                                                                          |

| Table 3 on page 9<br>Signal Multiplex Table i.MXL     | <ul> <li>Added Signal Multiplex table from Reference Manual with the following changes:</li> <li>Changed I/O Supply Voltage,PB31–20, from NVDD3 to NVDD4</li> <li>Added 225 BGA column.</li> <li>Removed 69K pull-up resistor from EB1, EB2, and added to D9</li> </ul> |

| Table 10 on page 21                                   | Changed first and second parameters descriptions:<br>From: Reference Clock freq range, To: DPLL input clock freq range<br>From: Double clock freq range, To: DPLL output freq range                                                                                     |

| Table 3 on page 9                                     | Added Signal Multiplex table.                                                                                                                                                                                                                                           |

### Table 39. i.MXL Data Sheet Revision History Rev. 8

## 6.2 Reference Documents

The following documents are required for a complete description of the MC9328MXL and are necessary to design properly with the device. Especially for those not familiar with the ARM920T processor or previous i.MX processor products, the following documents are helpful when used in conjunction with this document.

ARM Architecture Reference Manual (ARM Ltd., order number ARM DDI 0100)

ARM9DT1 Data Sheet Manual (ARM Ltd., order number ARM DDI 0029)

ARM Technical Reference Manual (ARM Ltd., order number ARM DDI 0151C)

EMT9 Technical Reference Manual (ARM Ltd., order number DDI O157E)

MC9328MXL Product Brief (order number MC9328MXLP)

MC9328MXL Reference Manual (order number MC9328MXLRM)

The Freescale manuals are available on the Freescale Semiconductors Web site at http://www.freescale.com/imx. These documents may be downloaded directly from the Freescale Web site, or printed versions may be ordered. The ARM Ltd. documentation is available from http://www.arm.com.