Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | F <sup>2</sup> MC-8FX                                                          |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 16MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, SIO, UART/USART                                              |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                        |

| Number of I/O              | 71                                                                             |

| Program Memory Size        | 20KB (20K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 496 x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                    |

| Data Converters            | A/D 4x8/10b                                                                    |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-LQFP                                                                        |

| Supplier Device Package    | 80-LQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f314epmc-g-sne2 |

| (Continued)     |                                                                                                                                                                                           |                   | 1                 | 1                                     | 1                                       |                |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|---------------------------------------|-----------------------------------------|----------------|--|--|--|

| Part number     |                                                                                                                                                                                           |                   |                   |                                       |                                         |                |  |  |  |

|                 | MB95F314E                                                                                                                                                                                 | MB95F316E         | MB95F318E         | MB95F314L                             | MB95F316L                               | MB95F318L      |  |  |  |

| Parameter       |                                                                                                                                                                                           |                   |                   |                                       |                                         |                |  |  |  |

|                 | 2 channels                                                                                                                                                                                |                   |                   |                                       |                                         |                |  |  |  |

|                 |                                                                                                                                                                                           | n ha configurad   | oc on "O hit timo | $\times$ 2 channels" o                | r a "16 hit timor \                     | ∠ 1 obannol"   |  |  |  |

| 8/16-bit        |                                                                                                                                                                                           |                   |                   | $\times$ 2 channels of PWM function a |                                         |                |  |  |  |

| composite timer |                                                                                                                                                                                           |                   |                   | clocks (seven t                       |                                         |                |  |  |  |

|                 | <ul> <li>It can output</li> </ul>                                                                                                                                                         |                   |                   | (001011                               | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                |  |  |  |

|                 | <ul> <li>COM output:</li> </ul>                                                                                                                                                           | •                 |                   |                                       |                                         |                |  |  |  |

|                 | <ul> <li>SEG output:</li> </ul>                                                                                                                                                           | ` '               |                   |                                       |                                         |                |  |  |  |

|                 | <ul> <li>LCD drive po</li> </ul>                                                                                                                                                          |                   |                   |                                       |                                         |                |  |  |  |

|                 | <ul> <li>40 SEG × 4 C</li> </ul>                                                                                                                                                          | COM: 160 pixels   | s can be display  | red                                   |                                         |                |  |  |  |

|                 | <ul> <li>Duty LCD mo</li> </ul>                                                                                                                                                           |                   |                   |                                       |                                         |                |  |  |  |

|                 | Operate in L0                                                                                                                                                                             |                   | de                |                                       |                                         |                |  |  |  |

|                 | Blinking funct                                                                                                                                                                            |                   | OD aluitura       |                                       |                                         |                |  |  |  |

|                 | Internal divide                                                                                                                                                                           | er resistor for L | CD drive          |                                       |                                         |                |  |  |  |

|                 | 1 channel                                                                                                                                                                                 |                   |                   |                                       |                                         |                |  |  |  |

| 16-bit reload   | Two clock modes and two counter operating modes can be selected                                                                                                                           |                   |                   |                                       |                                         |                |  |  |  |

|                 | <ul> <li>Square waveform output</li> <li>Count clock: it can be selected from internal clocks (seven types) and external clocks.</li> </ul>                                               |                   |                   |                                       |                                         |                |  |  |  |

|                 | <ul> <li>Count clock. It can be selected from internal clocks (seven types) and external clocks.</li> <li>Counter operating mode: reload mode or one-shot mode can be selected</li> </ul> |                   |                   |                                       |                                         |                |  |  |  |

|                 | By configuring the 16-bit reload timer and the 8/16-bit composite timer ch. 1, event counter                                                                                              |                   |                   |                                       |                                         |                |  |  |  |

|                 | function can be implemented. When the event counter function is used, the 16-bit reload timer                                                                                             |                   |                   |                                       |                                         |                |  |  |  |

|                 | and the 8/16-bit composite timer ch. 1 are unavailable.                                                                                                                                   |                   |                   |                                       |                                         |                |  |  |  |

|                 | 2 channels                                                                                                                                                                                |                   |                   |                                       |                                         |                |  |  |  |

| 8/16-bit PPG    | • Each channel of the PPG can be used as "8-bit PPG $\times$ 2 channels" or "16-bit PPG $\times$ 1 channel"                                                                               |                   |                   |                                       |                                         |                |  |  |  |

|                 | Counter operating clock: Eight selectable clock sources                                                                                                                                   |                   |                   |                                       |                                         |                |  |  |  |

|                 | Count clock: Four selectable clock sources (125 ms, 250 ms, 500 ms or 1 s)                                                                                                                |                   |                   |                                       |                                         |                |  |  |  |

| Watch counter   | • Counter value can be set from 0 to 63. (Capable of counting for 1 minute when selecting                                                                                                 |                   |                   |                                       |                                         |                |  |  |  |

|                 | clock source of 1 second and setting counter value to 60)                                                                                                                                 |                   |                   |                                       |                                         |                |  |  |  |

| <br> External   | 8 channels                                                                                                                                                                                |                   |                   |                                       |                                         |                |  |  |  |

| interrupt       | <ul> <li>Interrupt by edge detection (The rising edge, falling edge, or both edges can be selected.)</li> </ul>                                                                           |                   |                   |                                       |                                         |                |  |  |  |

|                 | It can be used to wake up the device from the standby mode.                                                                                                                               |                   |                   |                                       |                                         |                |  |  |  |

|                 | • 1-wire serial                                                                                                                                                                           |                   |                   | مام)                                  |                                         |                |  |  |  |

|                 | It supports serial writing. (asynchronous mode)                                                                                                                                           |                   |                   |                                       |                                         |                |  |  |  |

|                 | Eight different time intervals can be selected.<br>(62.5 ms, 125 ms, 250 ms, 500 ms, 1 s, 2 s, 4 s, 8 s)                                                                                  |                   |                   |                                       |                                         |                |  |  |  |

|                 | 1                                                                                                                                                                                         |                   |                   |                                       |                                         | /a.va.a.aa./   |  |  |  |

|                 |                                                                                                                                                                                           | , ,               | mming, Embed      | ded Algorithm,                        | program/erase/                          | erase-suspend/ |  |  |  |

|                 | erase-resume commands.  It has a flag indicating the completion of the operation of Embedded Algorithm.                                                                                   |                   |                   |                                       |                                         |                |  |  |  |

| riash memory    |                                                                                                                                                                                           |                   |                   | operation of En                       | iboadoa / ligoi li                      |                |  |  |  |

|                 | <ul><li>Number of program/erase cycles: 100000</li><li>Data retention time: 20 years</li></ul>                                                                                            |                   |                   |                                       |                                         |                |  |  |  |

|                 | Flash security feature for protecting the content of the Flash memory                                                                                                                     |                   |                   |                                       |                                         |                |  |  |  |

| Standby mode    | Sleep mode, st                                                                                                                                                                            | op mode, watch    | n mode, time-ba   | se timer mode                         |                                         |                |  |  |  |

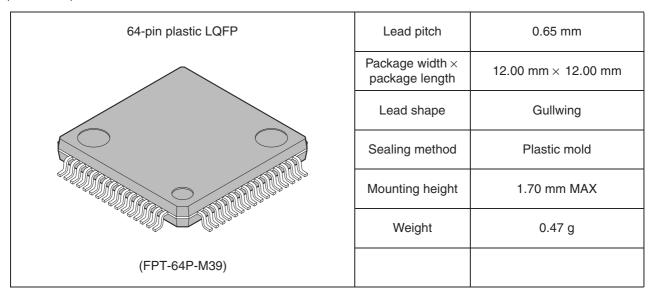

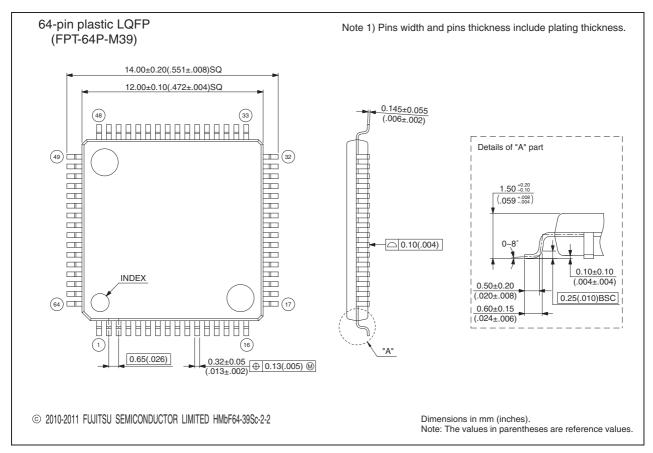

| Package         |                                                                                                                                                                                           |                   | FPT-8             | DP-M37                                |                                         |                |  |  |  |

|                 |                                                                                                                                                                                           |                   |                   |                                       |                                         |                |  |  |  |

#### • MB95370L Series

| Part number                             |                                                                                                                                                                                                                                                                                                                                                         |                                                   |                                                       |                  |                 |                  |  |  |  |  |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------|------------------|-----------------|------------------|--|--|--|--|--|

| rait ilumber                            | MB95F374E                                                                                                                                                                                                                                                                                                                                               | MB95F376E                                         | MB95F378E                                             | MB95F374L        | MB95F376L       | MB95F378L        |  |  |  |  |  |

| Parameter                               |                                                                                                                                                                                                                                                                                                                                                         |                                                   |                                                       |                  |                 |                  |  |  |  |  |  |

| Туре                                    |                                                                                                                                                                                                                                                                                                                                                         | Flash memory product                              |                                                       |                  |                 |                  |  |  |  |  |  |

| Clock                                   |                                                                                                                                                                                                                                                                                                                                                         |                                                   |                                                       |                  |                 |                  |  |  |  |  |  |

|                                         | It supervises th                                                                                                                                                                                                                                                                                                                                        | e main clock os                                   | scillation.                                           |                  |                 |                  |  |  |  |  |  |

| Flash memory capacity                   | 20 Kbyte                                                                                                                                                                                                                                                                                                                                                |                                                   |                                                       |                  |                 |                  |  |  |  |  |  |

| RAM capacity                            | 496 bytes                                                                                                                                                                                                                                                                                                                                               | 1008 bytes                                        | 2032 bytes                                            | 496 bytes        | 1008 bytes      | 2032 bytes       |  |  |  |  |  |

| Low-voltage<br>detection reset          |                                                                                                                                                                                                                                                                                                                                                         | Yes                                               |                                                       |                  | No              |                  |  |  |  |  |  |

| Reset input                             |                                                                                                                                                                                                                                                                                                                                                         |                                                   | Dedi                                                  | cated            |                 |                  |  |  |  |  |  |

| CPU functions                           | <ul> <li>Number of ba</li> <li>Instruction bit</li> <li>Instruction let</li> <li>Data bit lengt</li> <li>Minimum inst</li> <li>Interrupt proc</li> </ul>                                                                                                                                                                                                | t length<br>ngth<br>h<br>ruction executio         | : 8 bits<br>: 1 to 3<br>: 1, 8 ar<br>on time : 61.5 n | nd 16 bits       |                 |                  |  |  |  |  |  |

| Inurnasa I/( )                          | <ul><li>I/O ports (Ma</li><li>CMOS I/O: 5:</li><li>N-ch open dr</li></ul>                                                                                                                                                                                                                                                                               | 2                                                 |                                                       |                  |                 |                  |  |  |  |  |  |

| Time-base timer                         | Interval time: 0                                                                                                                                                                                                                                                                                                                                        | .256 ms - 8.3 s                                   | (external clock                                       | frequency = 4 M  | 1Hz)            |                  |  |  |  |  |  |

| Hardware/<br>software<br>watchdog timer |                                                                                                                                                                                                                                                                                                                                                         | tion clock at 10                                  | MHz: 105 ms (I<br>ed as the sourc                     |                  | ardware watchd  | log timer.       |  |  |  |  |  |

| Wild register                           | It can be used                                                                                                                                                                                                                                                                                                                                          | to replace three                                  | bytes of data.                                        |                  |                 |                  |  |  |  |  |  |

|                                         | <ul><li>1 channel</li><li>Master/Slave</li><li>Bus error fun</li><li>Detecting trai</li><li>Start conditio</li><li>Built-in wake-</li></ul>                                                                                                                                                                                                             | ction and arbitransmitting direction repeated gen | ation function<br>on function                         | ection functions |                 |                  |  |  |  |  |  |

| UART/SIO                                | <ul> <li>It has a full of generator and</li> <li>It uses the NI</li> <li>LSB-first data</li> <li>Clock-asynch</li> </ul>                                                                                                                                                                                                                                | ·                                                 |                                                       |                  |                 |                  |  |  |  |  |  |

| 8/10-bit A/D                            | 4 channels                                                                                                                                                                                                                                                                                                                                              |                                                   |                                                       |                  |                 |                  |  |  |  |  |  |

| converter                               | 8-bit or 10-bit re                                                                                                                                                                                                                                                                                                                                      | esolution can be                                  | e selected.                                           |                  |                 |                  |  |  |  |  |  |

|                                         | 2 channels                                                                                                                                                                                                                                                                                                                                              | a la a a a Constant                               | IIO 1:2:2:                                            | O ala a          | - III O I-11 II | ed alagana i III |  |  |  |  |  |

| composite timer                         | <ul> <li>Each timer can be configured as an "8-bit timer × 2 channels" or a "16-bit timer × 1 channel".</li> <li>It has built-in timer function, PWC function, PWM function and input capture function.</li> <li>Count clock: it can be selected from internal clocks (seven types) and external clocks.</li> <li>It can output square wave.</li> </ul> |                                                   |                                                       |                  |                 |                  |  |  |  |  |  |

#### **■ PIN DESCRIPTION (MB95370L Series)**

| Pin no. | Pin name | I/O circuit type* | Function                                                                                                                                        |  |  |  |

|---------|----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | AVcc     | _                 | A/D converter power supply pin                                                                                                                  |  |  |  |

| 2       | P16      | Н                 | General-purpose I/O port                                                                                                                        |  |  |  |

| 2       | PPG10    | 11                | 8/16-bit PPG ch. 1 output pin                                                                                                                   |  |  |  |

| 3       | P15      | Н                 | General-purpose I/O port                                                                                                                        |  |  |  |

| 3       | PPG11    | П                 | 8/16-bit PPG ch. 1 output pin                                                                                                                   |  |  |  |

|         | P14      |                   | General-purpose I/O port                                                                                                                        |  |  |  |

|         | UCK0     |                   | UART/SIO ch. 0 clock I/O pin                                                                                                                    |  |  |  |

| 4       | EC0      | Н                 | 8/16-bit composite timer ch. 0 clock input pin The pin can also be used as the event counter input pin when the event counter function is used. |  |  |  |

|         | TI0      |                   | 16-bit reload timer ch. 0 input pin                                                                                                             |  |  |  |

|         | P13      |                   | General-purpose I/O port                                                                                                                        |  |  |  |

| 5       | ADTG     | Н                 | A/D trigger input (ADTG) pin                                                                                                                    |  |  |  |

|         | TO01     |                   | 8/16-bit composite timer ch. 0 output pin                                                                                                       |  |  |  |

| 6       | P12      | С                 | General-purpose I/O port                                                                                                                        |  |  |  |

| 6       | DBG      |                   | DBG input pin                                                                                                                                   |  |  |  |

| 7       | P11      | Н                 | General-purpose I/O port                                                                                                                        |  |  |  |

| 7       | UO0      |                   | UART/SIO ch. 0 data output pin                                                                                                                  |  |  |  |

| 8       | P10      | G                 | General-purpose I/O port                                                                                                                        |  |  |  |

| 0       | UI0      | G                 | UART/SIO ch. 0 data input pin                                                                                                                   |  |  |  |

| 0       | P24      | 1                 | General-purpose I/O port                                                                                                                        |  |  |  |

| 9       | SDA0     | '                 | I <sup>2</sup> C data I/O pin                                                                                                                   |  |  |  |

| 10      | P23      | 1                 | General-purpose I/O port                                                                                                                        |  |  |  |

| 10      | SCL0     | '                 | I <sup>2</sup> C clock I/O pin                                                                                                                  |  |  |  |

| 11      | P22      | Н                 | General-purpose I/O port                                                                                                                        |  |  |  |

| 11      | TO00     | П                 | 8/16-bit composite timer ch. 0 output pin                                                                                                       |  |  |  |

| 12      | P21      | Н                 | General-purpose I/O port                                                                                                                        |  |  |  |

| 12      | PPG01    | П                 | 8/16-bit PPG ch. 0 output pin                                                                                                                   |  |  |  |

| 10      | P20      | Ш                 | General-purpose I/O port                                                                                                                        |  |  |  |

| 13      | PPG00    | Н                 | 8/16-bit PPG ch. 0 output pin                                                                                                                   |  |  |  |

| 14      | X0       | Α                 | Main clock oscillation pin                                                                                                                      |  |  |  |

| 15      | X1       | Α                 | Main clock oscillation pin                                                                                                                      |  |  |  |

| 16      | Vss      | _                 | Power supply pin (GND)                                                                                                                          |  |  |  |

| 17      | Vcc      | _                 | Power supply pin                                                                                                                                |  |  |  |

| 10      | P90      | Б                 | General-purpose I/O port                                                                                                                        |  |  |  |

| 18      | V3       | R                 | LCDC drive power supply pin                                                                                                                     |  |  |  |

| Pin no.    | Pin name | I/O circuit type* | Function                                       |

|------------|----------|-------------------|------------------------------------------------|

|            | P07      |                   | General-purpose I/O port                       |

| 56         | INT07    | Q                 | External interrupt input pin                   |

| 56         | SEG28    | Q                 | LCDC SEG output pin                            |

|            | UCK1     |                   | UART/SIO ch. 1 clock I/O pin                   |

|            | P06      |                   | General-purpose I/O port                       |

| E7         | INT06    | Q                 | External interrupt input pin                   |

| 57         | SEG29    | Q                 | LCDC SEG output pin                            |

|            | TO11     |                   | 8/16-bit composite timer ch. 1 output pin      |

|            | P05      |                   | General-purpose I/O port                       |

| F0         | INT05    | 0                 | External interrupt input pin                   |

| 58         | SEG30    | Q                 | LCDC SEG output pin                            |

|            | TO10     |                   | 8/16-bit composite timer ch. 1 output pin      |

|            | P04      |                   | General-purpose I/O port                       |

| <b>5</b> 0 | INT04    | 0                 | External interrupt input pin                   |

| 58         | SEG31    | Q                 | LCDC SEG output pin                            |

|            | EC1      |                   | 8/16-bit composite timer ch. 1 clock input pin |

|            | P03      |                   | General-purpose I/O port                       |

| 60         | INT03    | J                 | External interrupt input pin                   |

|            | AN03     |                   | A/D analog input pin                           |

|            | P02      |                   | General-purpose I/O port                       |

| 61         | INT02    | J                 | External interrupt input pin                   |

|            | AN02     |                   | A/D analog input pin                           |

|            | P01      |                   | General-purpose I/O port                       |

| 62         | INT01    | J                 | External interrupt input pin                   |

|            | AN01     |                   | A/D analog input pin                           |

|            | P00      |                   | General-purpose I/O port                       |

| 63         | INT00    | J                 | External interrupt input pin                   |

|            | AN00     |                   | A/D analog input pin                           |

| 64         | AVss     | _                 | A/D converter power supply pin (GND)           |

<sup>\*:</sup> For the I/O circuit types, see "■ I/O CIRCUIT TYPE".

| Address              | Register abbreviation | Register name                                               | R/W | Initial value |

|----------------------|-----------------------|-------------------------------------------------------------|-----|---------------|

| 0026н                | PDRE                  | Port E data register                                        | R/W | 0000000В      |

| 0027н                | DDRE                  | Port E direction register                                   | R/W | 0000000В      |

| 0028н,<br>0029н      | _                     | (Disabled)                                                  | _   | _             |

| 002Ан                | PDRG                  | Port G data register                                        | R/W | 0000000В      |

| 002Вн                | DDRG                  | Port G direction register                                   | R/W | 0000000В      |

| 002Сн                | PUL0                  | Port 0 pull-up register                                     | R/W | 0000000В      |

| 002Dн                | PUL1                  | Port 1 pull-up register                                     | R/W | 0000000В      |

| 002Ен                | PUL2                  | Port 2 pull-up register                                     | R/W | 0000000В      |

| 002Fн,<br>0030н      | _                     | (Disabled)                                                  | _   | _             |

| 0031н                | PUL5                  | Port 5 pull-up register                                     | R/W | 0000000В      |

| 0032н,<br>0033н      | _                     | (Disabled)                                                  | _   | _             |

| 0034н                | PUL9                  | Port 9 pull-up register                                     | R/W | 0000000В      |

| 0035н                | PULG                  | Port G pull-up register                                     | R/W | 0000000В      |

| 0036н                | T01CR1                | 8/16-bit composite timer 01 status control register 1 ch. 0 | R/W | 0000000В      |

| 0037н                | T00CR1                | 8/16-bit composite timer 00 status control register 1 ch. 0 | R/W | 0000000В      |

| 0038н                | T11CR1                | 8/16-bit composite timer 11 status control register 1 ch. 1 | R/W | 0000000В      |

| 0039н                | T10CR1                | 8/16-bit composite timer 10 status control register 1 ch. 1 | R/W | 0000000В      |

| 003Ан                | PC01                  | 8/16-bit PPG01 control register ch. 0                       | R/W | 0000000В      |

| 003Вн                | PC00                  | 8/16-bit PPG00 control register ch. 0                       | R/W | 0000000В      |

| 003Сн                | PC11                  | 8/16-bit PPG11 control register ch. 1                       | R/W | 0000000В      |

| 003Dн                | PC10                  | 8/16-bit PPG10 control register ch. 1                       | R/W | 0000000В      |

| 003Ен                | TMCSRH                | 16-bit reload timer control status register upper ch. 0     | R/W | 0000000В      |

| 003Fн                | TMCSRL                | 16-bit reload timer control status register lower ch. 0     | R/W | 0000000В      |

| 0040н<br>to          |                       | (Dischlad)                                                  |     |               |

| оо47н                | _                     | (Disabled)                                                  |     | _             |

| 0048н                | EIC00                 | External interrupt circuit control register ch. 0/ch. 1     | R/W | 0000000В      |

| 0049н                | EIC10                 | External interrupt circuit control register ch. 2/ch. 3     | R/W | 00000000В     |

| 004Ан                | EIC20                 | External interrupt circuit control register ch. 4/ch. 5     | R/W | 0000000       |

| 004Вн                | EIC30                 | External interrupt circuit control register ch. 6/ch. 7     | R/W | 0000000В      |

| 004Сн,<br>004Dн      | _                     | (Disabled)                                                  | _   | _             |

| 004Ен                | LVDR                  | LVD reset voltage selection ID register                     | R/W | 0000000В      |

| 004Fн                | LVDC                  | LVD control register                                        | R/W | Х000000Хв     |

| 0050н<br>to<br>0055н | _                     | (Disabled)                                                  | _   | _             |

| Address                | Register abbreviation | Register name                                                             | R/W | Initial value |

|------------------------|-----------------------|---------------------------------------------------------------------------|-----|---------------|

| 0F89н                  |                       |                                                                           |     |               |

| to<br>0F91⊦            | _                     | (Disabled)                                                                | _   | _             |

| 0F92н                  | T01CR0                | 8/16-bit composite timer 01 status control register 0 ch. 0               | R/W | 0000000В      |

| 0F93н                  | T00CR0                | 8/16-bit composite timer 00 status control register 0 ch. 0               | R/W | 0000000В      |

| 0F94н                  | T01DR                 | 8/16-bit composite timer 01 data register ch. 0                           | R/W | 0000000В      |

| 0F95н                  | T00DR                 | 8/16-bit composite timer 00 data register ch. 0                           | R/W | 0000000В      |

| 0F96н                  | TMCR0                 | 8/16-bit composite timer 00/01 timer mode control register ch. 0          | R/W | 0000000В      |

| 0F97н                  | T11CR0                | 8/16-bit composite timer 11 status control register 0 ch. 1               | R/W | 0000000В      |

| 0F98н                  | T10CR0                | 8/16-bit composite timer 10 status control register 0 ch. 1               | R/W | 0000000В      |

| 0F99н                  | T11DR                 | 8/16-bit composite timer 11 data register ch. 1                           | R/W | 0000000В      |

| <b>0</b> F9 <b>A</b> н | T10DR                 | 8/16-bit composite timer 10 data register ch. 1                           | R/W | 0000000В      |

| 0F9Вн                  | TMCR1                 | 8/16-bit composite timer 10/11 timer mode control register ch. 1          | R/W | 0000000В      |

| 0F9Cн                  | PPS01                 | 8/16-bit PPG01 cycle setting buffer register ch. 0                        | R/W | 11111111В     |

| 0F9Dн                  | PPS00                 | 8/16-bit PPG00 cycle setting buffer register ch. 0                        | R/W | 11111111в     |

| <b>0</b> F9Ен          | PDS01                 | 8/16-bit PPG01 duty setting buffer register ch. 0                         | R/W | 11111111в     |

| 0F9Fн                  | PDS00                 | 8/16-bit PPG00 duty setting buffer register ch. 0                         | R/W | 11111111В     |

| 0FA0н                  | PPS11                 | 8/16-bit PPG11 cycle setting buffer register ch. 1                        | R/W | 11111111В     |

| <b>0FA1</b> н          | PPS10                 | 8/16-bit PPG10 cycle setting buffer register ch. 1                        | R/W | 11111111В     |

| 0FA2н                  | PDS11                 | 8/16-bit PPG11 duty setting buffer register ch. 1                         | R/W | 11111111В     |

| 0FАЗн                  | PDS10                 | 8/16-bit PPG10 duty setting buffer register ch. 1                         | R/W | 11111111В     |

| 0FA4н                  | PPGS                  | 8/16-bit PPG start register                                               | R/W | 0000000В      |

| 0FA5н                  | REVC                  | 8/16-bit PPG output inversion register                                    | R/W | 0000000В      |

| 0FA6н                  | TMRH0                 | 16-bit reload timer timer register upper                                  | R/W | 0000000В      |

| ОГАОН                  | TMRLRH0               | 16-bit reload timer reload register upper                                 | R/W | 0000000В      |

| 0FA7н                  | TMRL0                 | 16-bit reload timer timer register lower                                  | R/W | 0000000В      |

| ОГА/Н                  | TMRLRL0               | 16-bit reload timer reload register lower                                 | R/W | 0000000В      |

| 0FA8н<br>to<br>0FBDн   | _                     | (Disabled)                                                                | _   | _             |

| 0FBEн                  | PSSR0                 | UART/SIO dedicated baud rate generator prescaler selecting register ch. 0 | R/W | 00000000в     |

| 0ГВГн                  | BRSR0                 | UART/SIO dedicated baud rate generator baud rate setting register ch. 0   | R/W | 00000000в     |

| 0ГС0н                  | PSSR1                 | UART/SIO dedicated baud rate generator prescaler selecting register ch. 1 | R/W | 0000000       |

| 0FС1н                  | BRSR1                 | UART/SIO dedicated baud rate generator baud rate setting register ch. 1   | R/W | 0000000       |

| 0FC2н                  | _                     | (Disabled)                                                                | _   |               |

| 0FС3н                  | AIDRL                 | A/D input disable register (lower)                                        | R/W | 0000000В      |

| 0FC4н                  | LCDCC                 | LCDC control register                                                     | R/W | 00010000в     |

#### (Continued)

| Address              | Register abbreviation | Register name                                | R/W | Initial value |

|----------------------|-----------------------|----------------------------------------------|-----|---------------|

| 0FС5н                | LCDCE1                | LCDC enable register 1                       | R/W | 00110000в     |

| 0FС6н                | LCDCE2                | LCDC enable register 2                       | R/W | 0000000В      |

| 0FС7н                | LCDCE3                | LCDC enable register 3                       | R/W | 0000000в      |

| 0FC8н                | LCDCE4                | LCDC enable register 4                       | R/W | 0000000в      |

| 0FС9н                | LCDCE5                | LCDC enable register 5                       | R/W | 0000000В      |

| 0FCAн                | _                     | (Disabled)                                   | _   | _             |

| 0FCBн                | LCDCB1                | LCDC blinking setting register 1             | R/W | 0000000в      |

| 0FCCн                | LCDCB2                | LCDC blinking setting register 2             | R/W | 0000000В      |

| 0FCDн<br>to<br>0FDCн | LCDRAM                | LCDC display RAM                             | R/W | 0000000в      |

| 0FDDн<br>to<br>0FE1н | _                     | (Disabled)                                   | _   | _             |

| 0FE2н                | EVCR                  | Event counter control register               | R/W | 0000000в      |

| 0FE3н                | WCDR                  | Watch counter data register                  | R/W | 00111111в     |

| 0FE4н                | CRTH                  | Main CR clock trimming register (upper)      | R/W | 0XXXXXXXB     |

| 0FE5н                | CRTL                  | Main CR clock trimming register (lower)      | R/W | 00XXXXXXB     |

| 0FE6н<br>to<br>0FE8н | _                     | (Disabled)                                   | _   | _             |

| 0FE9н                | CMCR                  | Clock monitoring control register            | R/W | ХХ000000в     |

| 0FEAн                | CMDR                  | Clock monitoring data register               | R   | 0000000в      |

| 0FEBн                | WDTH                  | Watchdog timer selection ID register (upper) | R   | XXXXXXXX      |

| 0FECн                | WDTL                  | Watchdog timer selection ID register (lower) | R   | XXXXXXXX      |

| 0FEDн                | _                     | (Disabled)                                   | _   | _             |

| 0FEEн                | ILSR                  | Input level select register                  | R/W | 0000000в      |

| 0FEFн                | WICR                  | Interrupt pin control register               | R/W | 01000000в     |

| 0FF0н<br>to<br>0FFFн | _                     | (Disabled)                                   | -   | _             |

• R/W access symbols

R/W : Readable / Writable

R : Read only

#### • Initial value symbols

0 : The initial value of this bit is "0".1 : The initial value of this bit is "1".

X : The initial value of this bit is indeterminate.

Note: Do not write to an address that is "(Disabled)". If a "(Disabled)" address is read, an indeterminate value is returned.

#### (Continued)

- \*5: Applicable to the following pins: P00 to P07, P10, P11, P13 to P16, P20 to P22, P40 to P43, P50 to P53, P60 to P67, P90 to P95, PA0 to PA3, PB0 to PB7, PC0 to PC7, PE0 to PE7, PG0

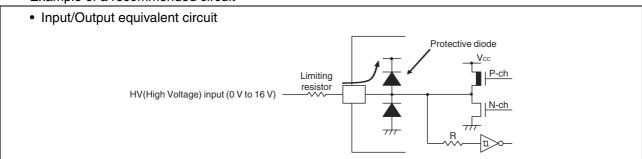

- Use under recommended operating conditions.

- Use with DC voltage (current).

- The HV (High Voltage) signal is an input signal exceeding the Vcc voltage. Always connect a limiting resistor between the HV (High Voltage) signal and the microcontroller before applying the HV (High Voltage) signal.

- The value of the limiting resistance should be set so that when the HV (High Voltage) signal is applied the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

- When the microcontroller drive current is low, such as in low power consumption modes, the HV (High Voltage) input potential may pass through the protective diode to increase the potential of the Vcc pin, and thus affects other devices.

- If the HV (High Voltage) signal is input when the microcontroller power supply is off (not fixed at 0 V), since power is supplied from the pins, incomplete operations may be executed.

- If the HV (High Voltage) input is input after power-on, since power is supplied from the pins, the voltage of power supply may not be sufficient to enable a power-on reset.

- Do not leave the HV (High Voltage) input pin unconnected.

- Example of a recommended circuit

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

$(V_{CC} = 3.0 \text{ V} \pm 10\%, \text{ Vss} = 0.0 \text{ V}, \text{ T}_{A} = -40^{\circ}\text{C to} +85^{\circ}\text{C})$

| _                      |         |                                      | ,                                                                                                                  | = 3.0 V. | Value | vss = 0.0 |      | = -40°C to +85°C) |

|------------------------|---------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------|-------|-----------|------|-------------------|

| Parameter              | Symbol  | Pin name                             | Condition                                                                                                          | Min      | Typ⁺⁵ | Max       | Unit | Remarks           |

|                        | Iccis   |                                      | F <sub>CL</sub> = 32 kHz<br>F <sub>MPL</sub> = 16 kHz<br>Subsleep mode<br>(divided by 2)<br>T <sub>A</sub> = +25°C | _        | 11.2  | 16.5      | μΑ   |                   |

|                        | Ісст    |                                      | F <sub>CL</sub> = 32 kHz<br>Watch mode<br>Main stop mode<br>T <sub>A</sub> = +25°C                                 | _        | 6.7   | 9         | μΑ   |                   |

|                        | Iccmpll |                                      | F <sub>CH</sub> = 4 MHz<br>F <sub>MP</sub> = 10 MHz<br>Main PLL mode<br>(multiplied by 2.5)                        | _        | 10.1  | 19.2      | mA   |                   |

|                        | ICCMPLL | Vcc<br>(External clock<br>operation) | F <sub>CH</sub> = 6.4 MHz<br>F <sub>MP</sub> = 16 MHz<br>Main PLL mode<br>(multiplied by 2.5)                      | _        | 16.2  | 30.7      | mA   |                   |

| Power supply current*4 | Іссмск  |                                      | F <sub>CRH</sub> = 12.5 MHz<br>F <sub>MP</sub> = 12.5 MHz<br>Main CR clock mode                                    | _        | 7.9   | 13.2      | mA   |                   |

|                        | Iccscr  |                                      | Sub-CR clock mode<br>(divided by 2)<br>T <sub>A</sub> = +25°C                                                      | _        | 77.8  | 138.5     | μΑ   |                   |

|                        | Істѕ    |                                      | FcH = 32 MHz<br>Time-base timer<br>mode<br>TA = +25°C                                                              | _        | 4.3   | 7.4       | mA   |                   |

|                        | Іссн    |                                      | Substop mode<br>T <sub>A</sub> = +25°C                                                                             | _        | 1     | 5         | μA   |                   |

|                        | la      | AVcc                                 | Current<br>consumption for<br>A/D conversion at<br>16 MHz                                                          | _        | 0.8   | 1.9       | mA   |                   |

|                        | Іан     |                                      | Current<br>consumption for<br>stopping A/D<br>conversion at<br>16 MHz                                              | _        | 1     | 5         | μΑ   |                   |

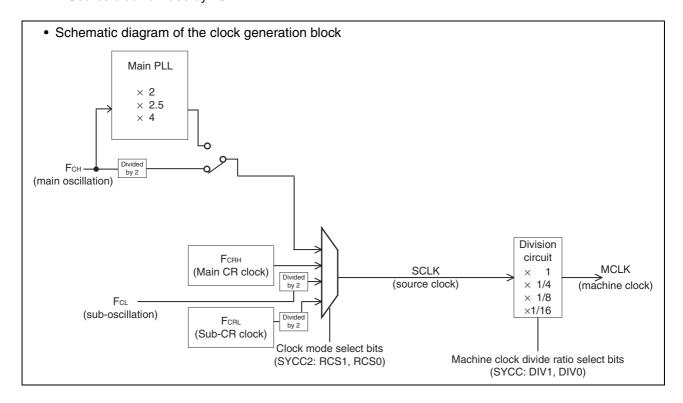

- \*2: This is the operating clock of the microcontroller. A machine clock can be selected from the following.

- Source clock (no division)

- Source clock divided by 4

- Source clock divided by 8

- Source clock divided by 16

#### (3) External Reset

$(V_{CC} = 3.0 \text{ V} \pm 10\%, \text{ Vss} = 0.0 \text{ V}, \text{ T}_{A} = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                 | Symbol        | Value                                      |     | Unit  | Remarks                                                              |

|---------------------------|---------------|--------------------------------------------|-----|-------|----------------------------------------------------------------------|

| Parameter                 | Syllibol      | Min                                        | Max | Oilit | nemarks                                                              |

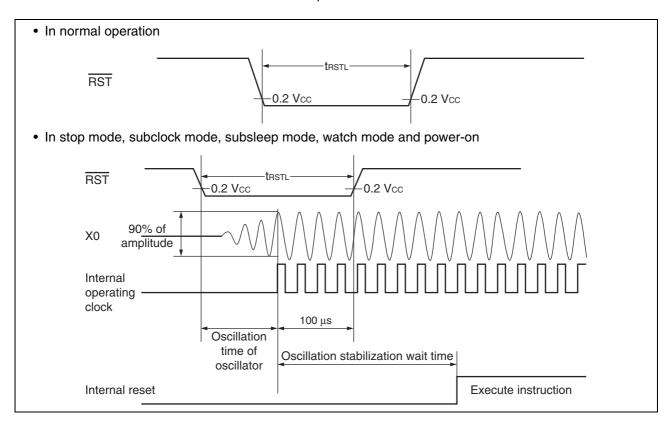

|                           | <b>t</b> rstl | 2 tmcLK*1                                  | _   | ns    | In normal operation                                                  |

| RST "L" level pulse width |               | Oscillation time of the oscillator*2 + 100 | -   | μs    | In stop mode, subclock mode, subsleep mode, watch mode, and power-on |

|                           |               | 100                                        | _   | μs    | In time-base timer mode                                              |

<sup>\*1:</sup> See "(2) Source Clock/Machine Clock" for tmclk.

<sup>\*2:</sup> The oscillation time of an oscillator is the time for it to reach 90% of its amplitude. The crystal oscillator has an oscillation time of between several ms and tens of ms. The ceramic oscillator has an oscillation time of between hundreds of µs and several ms. The external clock has an oscillation time of 0 ms. The CR oscillator clock has an oscillation time of between several µs and several ms.

#### (4) Power-on Reset

$(Vss = 0.0 V, T_A = -40^{\circ}C to +85^{\circ}C)$

| Parameter                | Symbol Condition |           | Value |     | Unit  | Remarks                  |

|--------------------------|------------------|-----------|-------|-----|-------|--------------------------|

| raidilietei              | Symbol           | Condition | Min   | Max | Oille | nemarks                  |

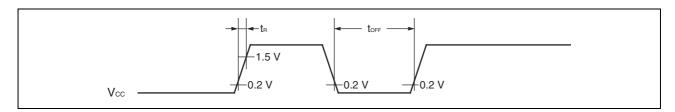

| Power supply rising time | <b>t</b> R       | _         | _     | 50  | ms    |                          |

| Power supply cutoff time | toff             | _         | 1     | _   | ms    | Wait time until power-on |

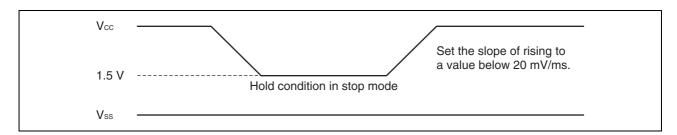

Note: A sudden change of power supply voltage may activate the power-on reset function. When changing the power supply voltage during the operation, set the slope of rising to a value below within 20 mV/ms as shown below.

#### (8) I2C Timing

$(Vcc = 3.0 V\pm 10\%, AVss = Vss = 0.0 V, T_A = -40^{\circ}C to +85^{\circ}C)$

|                                                                            |         |               |                                 | Value   |        |       |       |      |  |

|----------------------------------------------------------------------------|---------|---------------|---------------------------------|---------|--------|-------|-------|------|--|

| Parameter                                                                  | Symbol  | nbol Pin name | Conditions                      | Standar | d-mode | Fast- | mode  | Unit |  |

|                                                                            |         |               |                                 | Min     | Max    | Min   | Max   |      |  |

| SCL clock frequency                                                        | fscL    | SCL0          |                                 | 0       | 100    | 0     | 400   | kHz  |  |

| (Repeat) Start condition hold time SDA ↓ → SCL ↓                           | thd;sta | SCL0,<br>SDA0 |                                 | 4.0     | _      | 0.6   | _     | μs   |  |

| SCL clock<br>"L" width                                                     | tLOW    | SCL0          |                                 | 4.7     | _      | 1.3   | _     | μs   |  |

| SCL clock<br>"H" width                                                     | tніgн   | SCL0          |                                 | 4.0     | _      | 0.6   | _     | μs   |  |

| (Repeat) Start condition setup time SCL ↑ → SDA ↓                          | tsu;sta | SCL0,<br>SDA0 |                                 | 4.7     | _      | 0.6   | _     | μs   |  |

| Data hold time SCL $\downarrow \rightarrow$ SDA $\downarrow \uparrow$      | thd;dat | SCL0,<br>SDA0 | $R = 1.7 kΩ$ , $C = 50 pF^{*1}$ | 0       | 3.45*2 | 0     | 0.9*3 | μs   |  |

| Data setup time SDA $\downarrow \uparrow \rightarrow$ SCL $\uparrow$       | tsu;dat | SCL0,<br>SDA0 |                                 | 0.25    | _      | 0.1   | _     | μs   |  |

| Stop condition setup time SCL $\uparrow \rightarrow$ SDA $\uparrow$        | tsu;sто | SCL0,<br>SDA0 |                                 | 4.0     | _      | 0.6   | _     | μs   |  |

| Bus free<br>time<br>between<br>stop<br>condition<br>and start<br>condition | tвиғ    | SCL0,<br>SDA0 |                                 | 4.7     | _      | 1.3   | _     | μs   |  |

<sup>\*1:</sup> R represents the pull-up resistor of the SCL0 and SDA0 lines, and C the load capacitor of the SCL0 and SDA0 lines.

<sup>\*2:</sup> The maximum thd; DAT in the Standard-mode is applicable only when the time during which the device is holding the SCL signal at "L" (tLow) does not extend.

<sup>\*3:</sup> A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, provided that the condition of  $t_{SU;DAT} \ge 250$  ns is fulfilled.

(Vcc = 3.0 V±10%, AVss = Vss = 0.0 V, TA =  $-40^{\circ}$ C to  $+85^{\circ}$ C)

|                                                                         |               | 1             |                            | Value*2                  |                         |                        |                                                                                                                                                                   |             |  |  |                                     |   |    |             |

|-------------------------------------------------------------------------|---------------|---------------|----------------------------|--------------------------|-------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|-------------------------------------|---|----|-------------|

| Parameter                                                               | Symbol        | Pin name      | Conditions                 | Min                      | Max                     | Unit                   | Remarks                                                                                                                                                           |             |  |  |                                     |   |    |             |

| SCL clock<br>"L" width                                                  | tLOW          | SCL0          |                            |                          |                         |                        |                                                                                                                                                                   |             |  |  | (2 + nm / 2) t <sub>MCLK</sub> - 20 | _ | ns | Master mode |

| SCL clock<br>"H" width                                                  | <b>t</b> ніgн | SCL0          |                            |                          | (nm / 2)tмсцк – 20      | (nm / 2)tmcLK + 20     | ns                                                                                                                                                                | Master mode |  |  |                                     |   |    |             |

| Start<br>condition<br>hold time                                         | thd;sta       | SCL0,<br>SDA0 |                            | (-1 + nm / 2) tмськ - 20 | (-1 + nm)tmclk + 20     | ns                     | Master mode Maximum value is applied when m, n = 1, 8. Otherwise, the minimum value is applied.                                                                   |             |  |  |                                     |   |    |             |

| Stop<br>condition<br>setup time                                         | tsu;sto       | SCL0,<br>SDA0 |                            |                          | (1 + nm / 2) tmcLk - 20 | (1 + nm / 2)tmcLk + 20 | ns                                                                                                                                                                | Master mode |  |  |                                     |   |    |             |

| Start<br>condition<br>setup time                                        | tsu;sta       | SCL0,<br>SDA0 |                            | (1 + nm / 2)tmcLk - 20   | (1 + nm / 2)tmcLk + 20  | ns                     | Master mode                                                                                                                                                       |             |  |  |                                     |   |    |             |

| Bus free time<br>between<br>stop<br>condition<br>and start<br>condition | tвиғ          | SCL0,<br>SDA0 | R = 1.7 kΩ,<br>C = 50 pF*1 | (2 nm + 4)tмсLк - 20     | _                       | ns                     |                                                                                                                                                                   |             |  |  |                                     |   |    |             |

| Data hold<br>time                                                       | thd;dat       | SCL0,<br>SDA0 | ]                          | 3 tмськ — 20             | _                       | ns                     | Master mode                                                                                                                                                       |             |  |  |                                     |   |    |             |

| Data setup<br>time                                                      | tsu;dat       | SCL0,<br>SDA0 |                            | (-2 + nm / 2)tмсLк – 20  | (-1 + nm / 2)tмсLк + 20 | ns                     | Master mode When assuming that "L" of SCL is not extended, the minimum value is applied to first bit of continuous data. Otherwise, the maximum value is applied. |             |  |  |                                     |   |    |             |

(Vcc = 3.0 V±10%, AVss = Vss = 0.0 V, Ta =  $-40^{\circ}$ C to  $+85^{\circ}$ C)

|                                                                     |                 | 1             |                                                      | $Value^{*2}$                                       |                        |      |                                                                                                       |

|---------------------------------------------------------------------|-----------------|---------------|------------------------------------------------------|----------------------------------------------------|------------------------|------|-------------------------------------------------------------------------------------------------------|

| Parameter                                                           | Symbol          | Pin name      | Conditions                                           | Min Max                                            |                        | Unit | Remarks                                                                                               |

| Setup time<br>between<br>clearing<br>interrupt<br>and SCL<br>rising | tsu;int         | SCL0          | $R = 1.7 \text{ k}\Omega$ , $C = 50 \text{ pF}^{*1}$ | (nm / 2)tмсLк — 20                                 | (1 + nm / 2)tmclk + 20 | ns   | Minimum value is applied to interrupt at 9th SCL↓. Maximum value is applied to interrupt at 8th SCL↓. |

| SCL clock<br>"L" width                                              | tLOW            | SCL0          |                                                      | 4 tmclk - 20                                       | _                      | ns   | At reception                                                                                          |

| SCL clock<br>"H" width                                              | tніgн           | SCL0          |                                                      | 4 tmclk - 20                                       | _                      | ns   | At reception                                                                                          |

| Start<br>condition<br>detection                                     | thd;sta         | SCL0,<br>SDA0 |                                                      | 2 tmcLK — 20                                       | _                      | ns   | Not detected<br>when 1 tmclk<br>is used at<br>reception                                               |

| Stop<br>condition<br>detection                                      | <b>t</b> su;sто | SCL0,<br>SDA0 |                                                      | 2 tmcLK — 20                                       | _                      | ns   | Not detected<br>when 1 tmclk<br>is used at<br>reception                                               |

| Restart<br>condition<br>detection<br>condition                      | tsu;sta         | SCL0,<br>SDA0 |                                                      | 2 tmcLK — 20                                       | _                      | ns   | Not detected<br>when 1 tmclk<br>is used at<br>reception                                               |

| Bus free<br>time                                                    | <b>t</b> BUF    | SCL0,<br>SDA0 |                                                      | 2 tmclk - 20                                       | _                      | ns   | At reception                                                                                          |

| Data hold time                                                      | thd;dat         | SCL0,<br>SDA0 |                                                      | 2 tmcLK - 20                                       | _                      | ns   | At slave<br>transmission<br>mode                                                                      |

| Data setup<br>time                                                  | tsu;dat         | SCL0,<br>SDA0 |                                                      | tLOW - 3 tMCLK - 20                                | _                      | ns   | At slave<br>transmission<br>mode                                                                      |

| Data hold time                                                      | thd;dat         | SCL0,<br>SDA0 |                                                      | 0                                                  | _                      | ns   | At reception                                                                                          |

| Data setup<br>time                                                  | <b>t</b> su;dat | SCL0,<br>SDA0 |                                                      | tмськ — 20                                         | 20 —                   |      | At reception                                                                                          |

| SDA↓→<br>SCL↑<br>(at wakeup<br>function)                            | <b>t</b> wakeup | SCL0,<br>SDA0 |                                                      | Oscillation stabilization wait time + 2 tmclk - 20 | _                      | ns   |                                                                                                       |

#### 6. Flash Memory Program/Erase Characteristics

| Parameter                              | Value  |       |        | Unit  | Remarks                                                               |  |

|----------------------------------------|--------|-------|--------|-------|-----------------------------------------------------------------------|--|

| Farameter                              | Min    | Тур   | Max    | Ollit | nemarks                                                               |  |

| Sector erase time<br>(2 Kbyte sector)  | _      | 0.2*1 | 0.5*2  | s     | The time of programming 00 <sub>H</sub> prior to erasure is excluded. |  |

| Sector erase time<br>(16 Kbyte sector) | _      | 0.5*1 | 7.5*2  | s     | The time of programming 00 <sub>H</sub> prior to erasure is excluded. |  |

| Byte programming time                  | _      | 21    | 6100*2 | μs    | System-level overhead is excluded.                                    |  |

| Program/erase cycle                    | 100000 | _     | _      | cycle |                                                                       |  |