# Microchip Technology - PIC16F1619-E/SO Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 20-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1619-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name               | Function | Input<br>Type | Output<br>Type | Description                                           |

|--------------------|----------|---------------|----------------|-------------------------------------------------------|

| OUT <sup>(2)</sup> | C1OUT    | _             | CMOS           | Comparator output.                                    |

|                    | C2OUT    | —             | CMOS           | Comparator output.                                    |

|                    | CCP1     | —             | CMOS           | Capture/Compare/PWM1 output.                          |

|                    | CCP2     | —             | CMOS           | Capture/Compare/PWM2 output.                          |

|                    | PWM3OUT  | _             | CMOS           | PWM3 output.                                          |

|                    | PWM4OUT  | —             | CMOS           | PWM4 output.                                          |

|                    | CWG1A    | —             | CMOS           | Complementary Output Generator Output A.              |

|                    | CWG1B    | _             | CMOS           | Complementary Output Generator Output B.              |

|                    | CWG1C    | —             | CMOS           | Complementary Output Generator Output C.              |

|                    | CWG1D    | —             | CMOS           | Complementary Output Generator Output D.              |

|                    | SDO      | _             | CMOS           | SPI data output.                                      |

|                    | SCK      | _             | CMOS           | SPI clock output.                                     |

|                    | TX/CK    | _             | CMOS           | EUSART asynchronous TX data/synchronous clock output. |

|                    | DT       | —             | CMOS           | EUSART synchronous data output.E                      |

|                    | CLC10UT  | _             | CMOS           | Configurable Logic Cell 1 source output.              |

|                    | CLC2OUT  |               | CMOS           | Configurable Logic Cell 2 source output.              |

|                    | ZCD10UT  |               | CMOS           | Zero-Cross Detect output.                             |

| VDD                | Vdd      | Power         | _              | Positive supply.                                      |

| Vss                | Vss      | Power         | _              | Ground reference.                                     |

#### **TABLE 1-2:** PIC16(L)F1615 PINOUT DESCRIPTION (CONTINUED)

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain

Schmitt Trigger input with I<sup>2</sup>C<sup>™</sup> TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  =

HV = High Voltage XTAL = Crystal

levels Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-1.

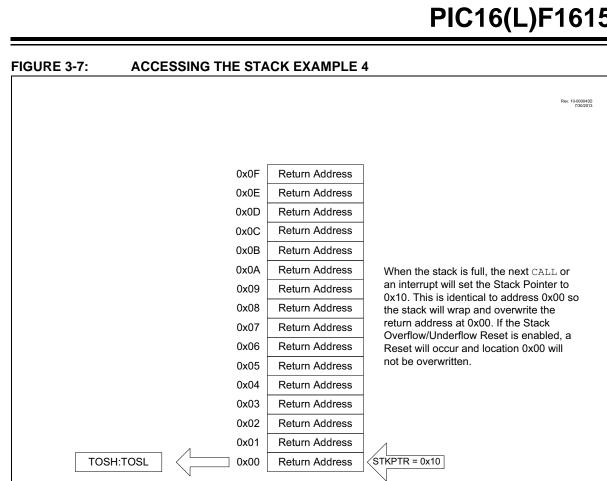

#### 3.5.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

#### 3.6 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

# 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Internal access to the program memory is unaffected by any code protection setting.

# 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4 "Write Protection"** for more information.

# 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

# 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC12(L)F1612/16(L)F161X Memory Programming Specification*" (DS40001720).

# 6.1 Power-On Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 6.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms timeout on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

## 6.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- BOR is always on

- BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 6-2 for more information.

|            | BOIL OF ERATIN |             |          |                                                                     |  |

|------------|----------------|-------------|----------|---------------------------------------------------------------------|--|

| BOREN<1:0> | SBOREN         | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |  |

| 11         | Х              | Х           | Active   | Waits for BOR ready <sup>(1)</sup><br>(BORRDY = 1)                  |  |

| 1.0        | 37             | Awake       | Active   | Waits for BOR ready                                                 |  |

| 10         | Х              | Sleep       | Disabled | (BORRDY = 1)                                                        |  |

| 01         | 1              | х           | Active   | Waits for BOR ready <sup>(1)</sup><br>(BORRDY = 1)                  |  |

|            | 0              | х           | Disabled | Begins immediately                                                  |  |

| 00         | Х              | Х           | Disabled | (BORRDY = x)                                                        |  |

TABLE 6-1:BOR OPERATING MODES

**Note 1:** In these specific cases, "release of POR" and "wake-up from Sleep," there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

# 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold. BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

#### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

| Name       | Bit 7   | Bit 6  | Bit 5     | Bit 4     | Bit 3  | Bit 2     | Bit 1     | Bit 0   | Register<br>on Page |

|------------|---------|--------|-----------|-----------|--------|-----------|-----------|---------|---------------------|

| INTCON     | GIE     | PEIE   | TMR0IE    | INTE      | IOCIE  | TMR0IF    | INTF      | IOCIF   | 105                 |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS    | TMR0SE    | PSA    | PS<2:0>   |           |         | 230                 |

| PIE1       | TMR1GIE | ADIE   | RCIE      | TXIE      | SSP1IE | CCP1IE    | TMR2IE    | TMR1IE  | 106                 |

| PIE2       | OSFIE   | C2IE   | C1IE      | —         | BCL1IE | TMR6IE    | TMR4IE    | CCP2IE  | 107                 |

| PIE3       | —       | _      | CWGIE     | ZCDIE     | CLC4IE | CLC3IE    | CLC2IE    | CLC1IE  | 108                 |

| PIE4       | SCANIE  | CRCIE  | SMT2PWAIE | SMT2PRAIE | SMT2IE | SMT1PWAIE | SMT1PRAIE | SMT1IF  | 109                 |

| PIE5       | TMR3GIE | TMR3IE | TMR5GIE   | TMR5IE    | -      | AT1IE     | PID1EIE   | PID1DIE | 110                 |

| PIR1       | TMR1GIF | ADIF   | RCIF      | TXIF      | SSP1IF | CCP1IF    | TMR2IF    | TMR1IF  | 111                 |

| PIR2       | OSFIF   | C2IF   | C1IF      | —         | BCL1IF | TMR6IF    | TMR4IF    | CCP2IF  | 112                 |

| PIR3       | —       | _      | CWGIF     | ZCDIF     | CLC4IF | CLC3IF    | CLC2IF    | CLC1IF  | 113                 |

| PIR4       | SCANIF  | CRCIF  | SMT2PWAIF | SMT2PRAIF | SMT2IF | SMT1PWAIF | SMT1PRAIF | SMT1IF  | 114                 |

| PIR5       | TMR3GIF | TMR3IF | TMR5GIF   | TMR5IF    | _      | AT1IF     | PID1EIF   | PID1DIF | 115                 |

TABLE 7-1:

SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

| W-0/0            | W-0/0    | W-0/0             | W-0/0       | W-0/0          | W-0/0            | W-0/0            | W-0/0       |

|------------------|----------|-------------------|-------------|----------------|------------------|------------------|-------------|

|                  |          | Prog              | gram Memory | Control Regist | er 2             |                  |             |

| bit 7            |          |                   |             |                |                  |                  | bit 0       |

|                  |          |                   |             |                |                  |                  |             |

| Legend:          |          |                   |             |                |                  |                  |             |

| R = Readable     | bit      | W = Writable      | bit         | U = Unimpler   | nented bit, read | l as '0'         |             |

| S = Bit can onl  | y be set | x = Bit is unkr   | nown        | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |          | '0' = Bit is clea | ared        |                |                  |                  |             |

# REGISTER 10-6: PMCON2: PROGRAM MEMORY CONTROL 2 REGISTER

#### bit 7-0 Flash Memory Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the PMCON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes.

#### TABLE 10-3: SUMMARY OF REGISTERS ASSOCIATED WITH FLASH PROGRAM MEMORY

| Name   | Bit 7                             | Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |        |      |            |        |      |       |     |  |

|--------|-----------------------------------|-------------------------------------------|--------|------|------------|--------|------|-------|-----|--|

| INTCON | GIE                               | PEIE                                      | TMR0IE | INTE | IOCIE      | TMR0IF | INTF | IOCIF | 105 |  |

| PMCON1 | (1)                               | CFGS LWLO FREE WRERR WREN WR RD           |        |      |            |        |      |       |     |  |

| PMCON2 | Program Memory Control Register 2 |                                           |        |      |            |        |      |       |     |  |

| PMADRL |                                   |                                           |        | PMAD | RL<7:0>    |        |      |       | 141 |  |

| PMADRH | (1)                               |                                           |        | F    | PMADRH<6:0 | >      |      |       | 141 |  |

| PMDATL | PMDATL<7:0>                       |                                           |        |      |            |        |      |       | 141 |  |

| PMDATH | _                                 | _                                         |        |      | PMDAT      | H<5:0> |      |       | 141 |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Flash program memory.

Note 1: Unimplemented, read as '1'.

#### TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH FLASH PROGRAM MEMORY

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4   | Bit 11/3 | Bit 10/2   | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|------------|----------|------------|-----------|---------|---------------------|

|         | 13:8 | _       | _       | FCMEN    | IESO       | CLKOUTEN | BOREN<1:0> |           | _       | <u> </u>            |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | —          | —        | FOSC<2:0>  |           |         | 69                  |

|         | 13:8 | _       | _       | LVP      | DEBUG      | LPBOR    | BORV       | STVREN    | PLLEN   | 74                  |

| CONFIG2 | 7:0  | ZCD     | _       | _        | —          | —        | PPS1WAY    | WRT<      | <1:0>   | 71                  |

|         | 13:8 | _       | _       | V        | VDTCCS<2:( | )>       | W          | DTCWS<2:0 | >       | 70                  |

| CONFIG3 | 7:0  | _       | WDTE    | E<1:0>   |            | WI       | DTCPS<4:0> | •         |         | 72                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Flash program memory.

# REGISTER 11-3: CRCDATH: CRC DATA HIGH BYTE REGISTER

| R/W-x/x              | R/W-x/x | R/W-x/x              | R/W-x/x | R/W-x/x           | R/W-x/x              | R/W-x/x                | R/W-x/x |

|----------------------|---------|----------------------|---------|-------------------|----------------------|------------------------|---------|

|                      |         |                      | DAT<    | :15:8>            |                      |                        |         |

| bit 7                |         |                      |         |                   |                      |                        | bit 0   |

|                      |         |                      |         |                   |                      |                        |         |

| Legend:              |         |                      |         |                   |                      |                        |         |

| R = Readable bit     |         | W = Writable bit     |         | U = Unimplemer    | nted bit, read as '0 | ,                      |         |

| u = Bit is unchanged |         | x = Bit is unknown   |         | -n/n = Value at F | OR and BOR/Valu      | ue at all other Resets | 6       |

| '1' = Bit is set     |         | '0' = Bit is cleared |         |                   |                      |                        |         |

bit 7-0 DAT<15:8>: CRC Input/Output Data bits

## REGISTER 11-4: CRCDATL: CRC DATA LOW BYTE REGISTER

| R/W-x/x             | R/W-x/x | R/W-x/x            | R/W-x/x | R/W-x/x           | R/W-x/x              | R/W-x/x              | R/W-x/x |

|---------------------|---------|--------------------|---------|-------------------|----------------------|----------------------|---------|

|                     |         |                    | DAT     | <7:0>             |                      |                      |         |

| bit 7               |         |                    |         |                   |                      |                      | bit     |

|                     |         |                    |         |                   |                      |                      |         |

| Legend:             |         |                    |         |                   |                      |                      |         |

| R = Readable bit    |         | W = Writable bit   |         | U = Unimplemer    | nted bit, read as '0 | 3                    |         |

| u = Bit is unchange | d       | x = Bit is unknown |         | -n/n = Value at F | OR and BOR/Valu      | ue at all other Rese | ets     |

bit 7-0

'1' = Bit is set

**DAT<7:0>**: CRC Input/Output Data bits Writing to this register fills the shifter.

'0' = Bit is cleared

#### REGISTER 11-5: CRCACCH: CRC ACCUMULATOR HIGH BYTE REGISTER

| R/W-0/0            | R/W-0/0 | R/W-0/0              | R/W-0/0 | R/W-0/0           | R/W-0/0              | R/W-0/0             | R/W-0/0 |

|--------------------|---------|----------------------|---------|-------------------|----------------------|---------------------|---------|

|                    |         |                      | ACC     | <15:8>            |                      |                     |         |

| bit 7              |         |                      |         |                   |                      |                     | bit 0   |

|                    |         |                      |         |                   |                      |                     |         |

| Legend:            |         |                      |         |                   |                      |                     |         |

| R = Readable bit   |         | W = Writable bit     |         | U = Unimpleme     | nted bit, read as '0 | ,                   |         |

| u = Bit is unchang | ed      | x = Bit is unknown   |         | -n/n = Value at F | POR and BOR/Val      | ue at all other Res | ets     |

| '1' = Bit is set   |         | '0' = Bit is cleared |         |                   |                      |                     |         |

bit 7-0 ACC<15:8>: CRC Accumulator Register bits

Writing to this register writes to the CRC accumulator register. Reading from this register reads the CRC accumulator.

#### REGISTER 11-6: CRCACCL: CRC ACCUMULATOR LOW BYTE REGISTER

| R/W-0/0            | R/W-0/0 | R/W-0/0              | R/W-0/0 | R/W-0/0           | R/W-0/0              | R/W-0/0             | R/W-0/0 |

|--------------------|---------|----------------------|---------|-------------------|----------------------|---------------------|---------|

|                    |         |                      | ACO     | C<7:0>            |                      |                     |         |

| bit 7              |         |                      |         |                   |                      |                     | bit 0   |

|                    |         |                      |         |                   |                      |                     |         |

| Legend:            |         |                      |         |                   |                      |                     |         |

| R = Readable bit   |         | W = Writable bit     |         | U = Unimpleme     | nted bit, read as '0 | ,                   |         |

| u = Bit is unchang | ed      | x = Bit is unknown   |         | -n/n = Value at F | OR and BOR/Val       | ue at all other Res | ets     |

| '1' = Bit is set   |         | '0' = Bit is cleared |         |                   |                      |                     |         |

bit 7-0

ACC<7:0>: CRC Accumulator Register bits Writing to this register writes to the CRC accumulator register through the CRC write bus. Reading from this register reads the CRC accumulator.

# 15.3 Register Definitions: FVR Control

| R/W-0/0              | R-q/q                                     | R/W-0/0                                                                                | R/W-0/0                                                  | R/W-0/0                            | R/W-0/0                                                                      | R/W-0/0          | R/W-0/0              |

|----------------------|-------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------|------------------|----------------------|

| FVREN <sup>(1)</sup> | FVRRDY <sup>(2)</sup>                     | TSEN <sup>(3)</sup>                                                                    | TSRNG <sup>(3)</sup>                                     | CDAFV                              | ′R<1:0> <sup>(1)</sup>                                                       | ADFVR            | <1:0> <sup>(1)</sup> |

| bit 7                |                                           |                                                                                        | 1                                                        |                                    |                                                                              |                  | bit                  |

|                      |                                           |                                                                                        |                                                          |                                    |                                                                              |                  |                      |

| Legend:              |                                           |                                                                                        |                                                          |                                    |                                                                              |                  |                      |

| R = Readable         |                                           | W = Writable                                                                           | bit                                                      |                                    | mented bit, read                                                             |                  |                      |

| u = Bit is unch      | anged                                     | x = Bit is unk                                                                         | nown                                                     | -n/n = Value                       | at POR and BO                                                                | R/Value at all o | ther Resets          |

| '1' = Bit is set     |                                           | '0' = Bit is cle                                                                       | ared                                                     | q = Value de                       | pends on condit                                                              | ion              |                      |

| bit 7                | 1 = Fixed Vo                              | d Voltage Refe<br>Itage Referenc<br>Itage Referenc                                     | e is enabled                                             | bit <sup>(1)</sup>                 |                                                                              |                  |                      |

| bit 6                | 1 = Fixed Vo                              | ed Voltage Re<br>Itage Referenc<br>Itage Referenc                                      | e output is rea                                          | ady for use                        | enabled                                                                      |                  |                      |

| bit 5                | 1 = Tempera                               | erature Indicate<br>ture Indicator i<br>ture Indicator i                               | s enabled                                                | )                                  |                                                                              |                  |                      |

| bit 4                | 1 = VOUT = V                              | perature Indica<br>/DD - 4VT (Higł<br>/DD - 2VT (Low                                   | n Range)                                                 | lection bit <sup>(3)</sup>         |                                                                              |                  |                      |

| bit 3-2              | 11 = Compar<br>10 = Compar<br>01 = Compar | ator FVR Buffe                                                                         | er Gain is 4x, v<br>er Gain is 2x, v<br>er Gain is 1x, v | vith output Vcc<br>vith output Vcc | bits <sup>(1)</sup><br>DAFVR = 4x VFVR<br>DAFVR = 2x VFVR<br>DAFVR = 1x VFVR | <sub>(</sub> (4) |                      |

| bit 1-0              | 11 = ADC FV<br>10 = ADC FV<br>01 = ADC FV | : ADC FVR Bu<br>'R Buffer Gain<br>'R Buffer Gain<br>'R Buffer Gain<br>'R Buffer is off | is 4x, with out<br>is 2x, with out                       | put Vadfvr = 2<br>put Vadfvr = 2   | 2x V <sub>FVR</sub> (4)                                                      |                  |                      |

|                      | minimize currer<br>the Buffer Gair        |                                                                                        |                                                          | R is disabled, t                   | he FVR buffers                                                               | should be turne  | ed off by clea       |

|                      |                                           |                                                                                        |                                                          | Javiana                            |                                                                              |                  |                      |

# **REGISTER 15-1:** FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

- 2: FVRRDY is always '1' for the PIC16LF1615/9 devices.

- 3: See Section16.0 "Temperature Indicator Module" for additional information.

- 4: Fixed Voltage Reference output cannot exceed VDD.

#### TABLE 15-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|---------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | ′R<1:0> | ADFVF | R<1:0> | 194                 |

**Legend:** Shaded cells are unused by the Fixed Voltage Reference module.

| R/W-x/u        | R/W-x/u | R/W-x/u      | R/W-x/u | R/W-x/u      | R/W-x/u          | R/W-x/u  | R/W-x/u |

|----------------|---------|--------------|---------|--------------|------------------|----------|---------|

| —              | _       |              | _       | _            | —                | ADRE     | S<9:8>  |

| bit 7          |         |              | •       |              | •                |          | bit 0   |

|                |         |              |         |              |                  |          |         |

| Legend:        |         |              |         |              |                  |          |         |

| R = Readable b | bit     | W = Writable | bit     | U = Unimpler | nented bit, read | l as '0' |         |

# REGISTER 17-6: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7-2 Reserved: Do not use.

bit 1-0 **ADRES<9:8>**: ADC Result Register bits Upper two bits of 10-bit conversion result

## REGISTER 17-7: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ADRES   | 6<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower eight bits of 10-bit conversion result

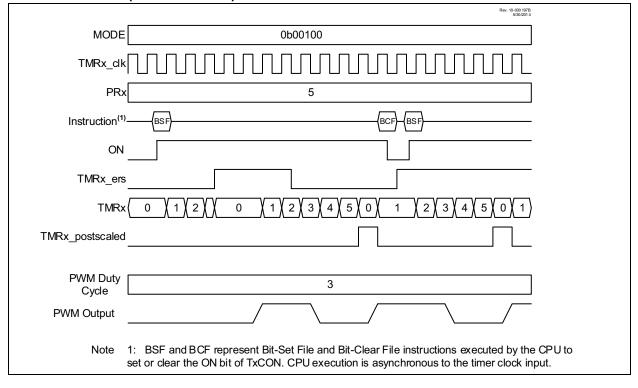

#### 23.5.2 HARDWARE GATE MODE

The Hardware Gate modes operate the same as the Software Gate mode except the TMRx\_ers external signal can also gate the timer. When used with the CCP the gating extends the PWM period. If the timer is stopped when the PWM output is high then the duty cycle is also extended.

When MODE<4:0> = 00001 then the timer is stopped when the external signal is high. When MODE<4:0> = 00010 then the timer is stopped when the external signal is low.

Figure 23-5 illustrates the Hardware Gating mode for MODE<4:0> = 00001 in which a high input level starts the counter.

| FIGURE 23-5:  | HARDWARE GATE MODE TIMING DIAGRAM ( | MODE = 00001) |  |

|---------------|-------------------------------------|---------------|--|

| 1 IGUNE 23-J. | TARDWARE GATE WODE TIMING DIAGRAM   |               |  |

|                                 | Rev:10.0001688<br>55000014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MODE                            | 0b00001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| TMRx_clk                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| TMRx_ers                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| PRx                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| TMRx                            | $0 \qquad \begin{pmatrix} 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 1 \\ 1 \\ 2 \\ 1 \\ 1 \\ 1 \\ 2 \\ 1 \\ 1 \\ 1$ |  |

| TMRx_postscaled                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| PWM Duty<br>Cycle<br>PWM Output | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

#### 23.5.3 EDGE-TRIGGERED HARDWARE LIMIT MODE

In Hardware Limit mode the timer can be reset by the TMRx\_ers external signal before the timer reaches the period count. Three types of Resets are possible:

- Reset on rising or falling edge

- (MODE<4:0>= 00011)

- Reset on rising edge (MODE<4:0> = 00100)

- Reset on falling edge (MODE<4:0> = 00101)

When the timer is used in conjunction with the CCP in PWM mode then an early Reset shortens the period and restarts the PWM pulse after a two-clock delay. Refer to Figure 23-6.

#### FIGURE 23-6: EDGE-TRIGGERED HARDWARE LIMIT MODE TIMING DIAGRAM (MODE = 00100)

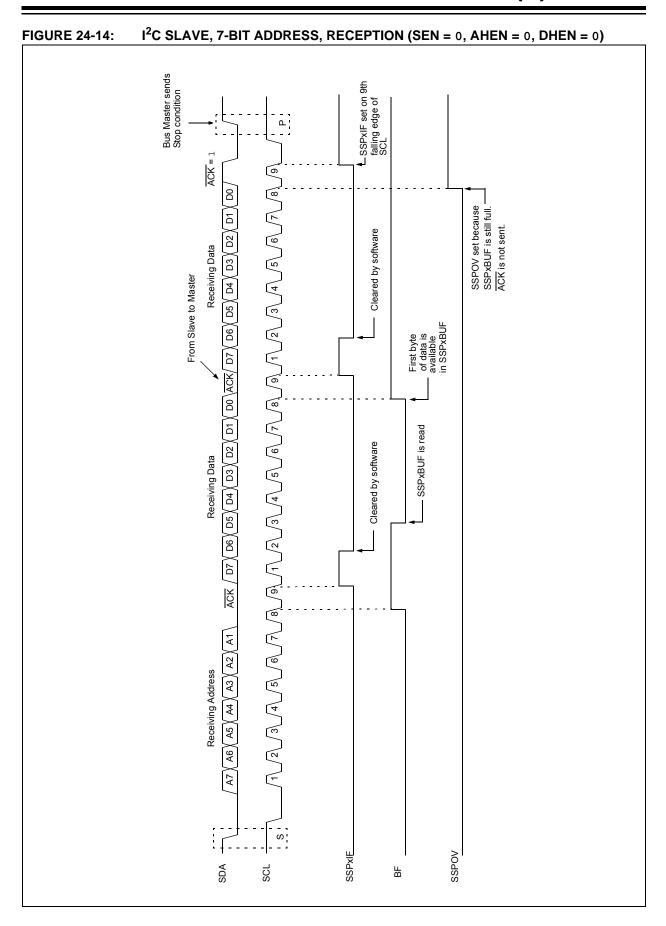

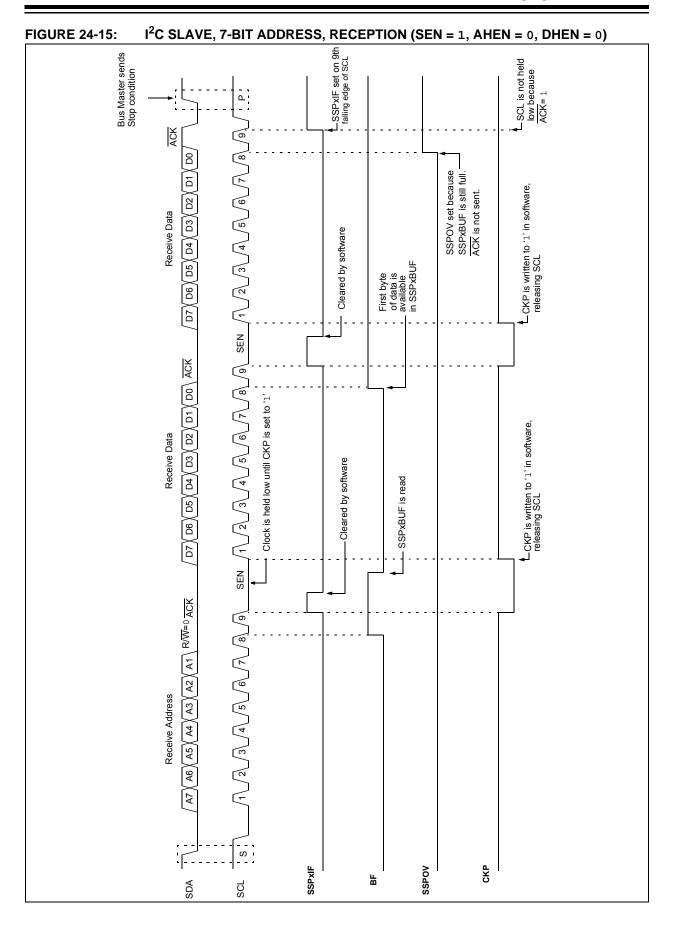

#### 24.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 24-4.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See **Section 24.5.6.2** "**10bit Addressing Mode**" for more detail.

#### 24.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 7-bit Addressing mode. Figure 24-14 and Figure 24-15 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $I^2C$  communication.

- 1. Start bit detected.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit clear is received.

- 4. The slave pulls SDA low sending an ACK to the master, and sets SSPxIF bit.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCL line.

- 8. The master clocks out a data byte.

- Slave drives SDA low sending an ACK to the master, and sets SSPxIF bit.

- 10. Software clears SSPxIF.

- 11. Software reads the received byte from SSPxBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSPxSTAT, and the bus goes idle.

# 24.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the eighth falling edge of SCL. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus<sup>™</sup> that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 24-16 displays a module using both address and data holding. Figure 24-17 includes the operation with the SEN bit of the SSPxCON2 register set.

- 1. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 2. Matching address with R/W bit clear is clocked in. SSPxIF is set and CKP cleared after the eighth falling edge of SCL.

- 3. Slave clears the SSPxIF.

- Slave can look at the ACKTIM bit of the SSPxCON3 register to determine if the SSPxIF was after or before the ACK.

- 5. Slave reads the address value from SSPxBUF, clearing the BF flag.

- 6. Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPxIF is set after an  $\overline{ACK}$ , not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPxIF.

Note: SSPxIF is still set after the 9th falling edge of SCL even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSPxIF not set

- 11. SSPxIF set and CKP cleared after eighth falling edge of SCL for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPxCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPxBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

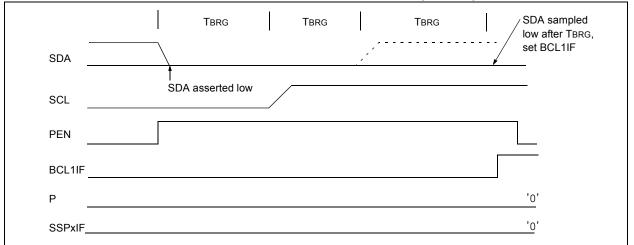

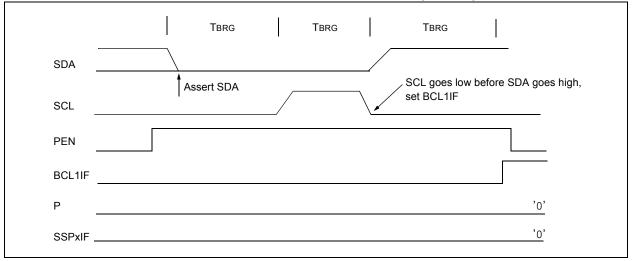

#### 24.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to zero. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 24-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 24-39).

## FIGURE 24-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 24-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

| <b>TABLE 28-2:</b> | SUMMARY OF REGISTERS ASSOCIATED WITH CWG |

|--------------------|------------------------------------------|

|--------------------|------------------------------------------|

| Name       | Bit 7    | Bit 6  | Bit 5  | Bit 4    | Bit 3   | Bit 2     | Bit 1 | Bit 0 | Register<br>on Page |

|------------|----------|--------|--------|----------|---------|-----------|-------|-------|---------------------|

| CWG1AS0    | SHUTDOWN | REN    | LSBD   | <1:0>    | LSAC    | <1:0>     | _     | _     | 391                 |

| CWG1AS1    | —        | TMR6AS | TMR4AS | TMR2AS   | _       | C2AS      | C1AS  | INAS  | 392                 |

| CWG1CLKCON | _        | _      | _      | _        | _       | _         | _     | CS    | 394                 |

| CWG1CON0   | EN       | LD     | _      | _        | _       | MODE<2:0> |       |       | 393                 |

| CWG1CON1   | _        | _      | IN     | _        | POLD    | POLC      | POLB  | POLA  | 389                 |

| CWG1DBF    | _        | _      |        |          | DBF     | <5:0>     |       |       | 390                 |

| CWG1DBR    | _        | _      |        | DBR<5:0> |         |           |       |       |                     |

| CWG1ISM    | _        | _      | _      | _        | IS<3:0> |           |       |       | 394                 |

| CWG10C0N0  | OVRD     | OVRC   | OVRB   | OVRA     | STRD    | STRC      | STRB  | STRA  | 393                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by CWG.

#### 30.6.11 WINDOWED COUNTER MODE

This mode counts pulses on the SMTx\_signal input, within a window dictated by the SMTxWIN input. It begins counting upon seeing a rising edge of the SMTxWIN input, updates the SMTxCPW register on a falling edge of the SMTxWIN input, and updates the SMTxCPR register on each rising edge of the SMTxWIN input beyond the first. See Figure 30-21 and Figure 30-22.

| R/W/HC-0/0       | R/W/HC-0/0                                        | R/W/HC-0/0                                                  | U-0           | U-0            | R-0/0            | R-0/0          | R-0/0        |

|------------------|---------------------------------------------------|-------------------------------------------------------------|---------------|----------------|------------------|----------------|--------------|

| CPRUP            | CPWUP                                             | RST                                                         |               |                | TS               | WS             | AS           |

| bit 7            |                                                   |                                                             |               |                |                  |                | bit 0        |

|                  |                                                   |                                                             |               |                |                  |                |              |

| Legend:          |                                                   |                                                             |               |                |                  |                |              |

| HC = Bit is clea | -                                                 | are                                                         |               |                | et by hardware   |                |              |

| R = Readable     | bit                                               | W = Writable                                                | bit           | •              | mented bit, read |                |              |

| u = Bit is unch  | anged                                             | x = Bit is unkr                                             | iown          | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |                                                   | '0' = Bit is clea                                           | ared          | q = Value dep  | pends on condi   | tion           |              |

| bit 7            | 1 = Request u<br>0 = SMTxCPF                      | Manual Perio<br>update to SMT<br>Rx registers up            | CPRx register | rs<br>te       |                  |                |              |

| bit 6            | 1 = Request ເ                                     | T Manual Pulse<br>update to SMT<br>N registers upo          | CPW register  | S              |                  |                |              |

| bit 5            | 1 = Request F                                     | anual Timer Re<br>Reset to SMTx<br>R registers upd          | TMR registers | e              |                  |                |              |

| bit 4-3          | Unimplemen                                        | ted: Read as '                                              | כ'            |                |                  |                |              |

| bit 2            | 1 = SMT time                                      | Value Status b<br>r is incrementir<br>r is not increme      | ng            |                |                  |                |              |

| bit 1            | <b>WS:</b> SMTxWI<br>1 = SMT wind<br>0 = SMT wind | •                                                           | bit           |                |                  |                |              |

| bit 0            | 1 = SMT acqu                                      | nal Value Statu<br>uisition is in pro<br>uisition is not in | gress         |                |                  |                |              |

# REGISTER 30-3: SMTxSTAT: SMT STATUS REGISTER

Г

# REGISTER 32-26: PIDxACCLH: PID ACCUMULATOR LOW HIGH REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | ACC     | <15:8>         |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | mented bit, read | l as '0'         |             |

| u = Bit is uncha | anged   | x = Bit is unkn   | iown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    | q = Value dep  | pends on condit  | ion              |             |

bit 7-0 **ACC<15:8>:** Bits <15:8> of ACC. ACC is the accumulator register in which all of the multiplier results for the PID are accumulated before being written to the output.

## REGISTER 32-27: PIDxACCLL: PID ACCUMULATOR LOW LOW REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ACC     | <7:0>   |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

# bit 7-0 ACC<7:0>: Bits <7:0> of ACC. ACC is the accumulator register in which all of the multiplier results for the PID are accumulated before being written to the output.

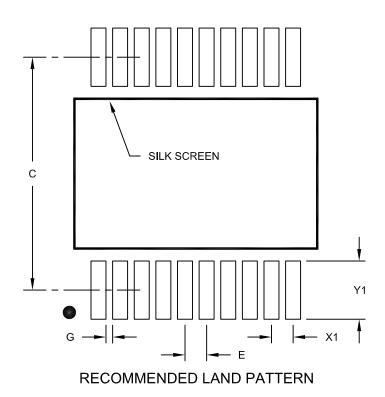

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |      |      |

|--------------------------|-------------|----------|------|------|

| Dimension Limits         |             | MIN      | NOM  | MAX  |

| Contact Pitch            | E           | 0.65 BSC |      |      |

| Contact Pad Spacing      | С           |          | 7.20 |      |

| Contact Pad Width (X20)  | X1          |          |      | 0.45 |

| Contact Pad Length (X20) | Y1          |          |      | 1.75 |

| Distance Between Pads    | G           | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A