Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1619-e-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Up to 17 I/O Pins and One Input-only Pin:

- Individually programmable pull-ups

- Slew rate control

- Interrupt-on-change with edge-select

- Two High Current Drive pins

- Peripheral Pin Select (PPS):

- Enables pin mapping of digital I/O

## **Intelligent Analog Peripherals**

- 10-Bit Analog-to-Digital Converter (ADC):

- Up to 12 external channels

- Conversion available during Sleep

- Two Comparators (COMP):

- Low-Power/High-Speed mode

- Up to three external inverting inputs

- Fixed Voltage Reference at non-inverting input(s)

- Comparator outputs externally accessible

- 8-Bit Digital-to-Analog Converter (DAC):

- 8-bit resolution, rail-to-rail

- Positive Reference Selection

- Voltage Reference:

- Fixed Voltage Reference (FVR): 1.024V, 2.048V and 4.096V output levels

- Zero-Cross Detect (ZCD):

- Detect when AC signal on pin crosses ground

- Two High-Current Drive Pins:

- 100mA @ 5V

## **Clocking Structure**

- 16 MHz Internal Oscillator:

- ±1% at calibration

- Selectable frequency range from 32 MHz to 31 kHz

- 31 kHz Low-Power Internal Oscillator

- 4x Phase-Locked Loop (PLL):

- For up to 32 MHz internal operation

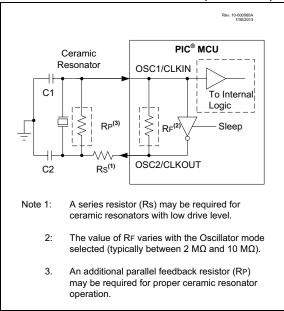

- External Oscillator Block with:

- Three external clock modes up to 32 MHz

- One crystal resonator mode up to 32 MHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if peripheral clock stops

- Two-Speed Oscillator Start-up

- · Oscillator Start-up Timer (OST)

| 0/1 | 20-Pin PDIP, SOIC, SSOP | 20-Pin UQFN | A/D  | Reference | Comparator       | Timers                                      | ССР                 | CWG                                | ZCD    | CLC                   | EUSART              | SMT                    | Angular Timer       | MSSP                 | MWG | High Current I/O | Interrupt  | Bull-up | Basic       |

|-----|-------------------------|-------------|------|-----------|------------------|---------------------------------------------|---------------------|------------------------------------|--------|-----------------------|---------------------|------------------------|---------------------|----------------------|-----|------------------|------------|---------|-------------|

| RA0 | 19                      | 16          | AN0  | DAC10UT   | C1IN+            | _                                           |                     | _                                  | _      | _                     |                     | —                      | _                   | —                    | _   | —                | IOC        | Y       | ICSPDAT     |

| RA1 | 18                      | 15          | AN1  | VREF+     | C1IN0-<br>C2IN0- | _                                           |                     | —                                  | —      | _                     |                     | —                      | _                   | —                    | —   | —                | IOC        | Y       | ICSPCLK     |

| RA2 | 17                      | 14          | AN2  | -         |                  | T0CKI <sup>(1)</sup>                        |                     | CWG1IN <sup>(1)</sup>              | ZCD1IN | -                     | -                   | _                      |                     | -                    | -   | -                | INT<br>IOC | Y       | —           |

| RA3 | 4                       | 1           | _    | —         |                  | T6IN <sup>(1)</sup>                         |                     | —                                  | _      | —                     | _                   | SMTWIN2 <sup>(1)</sup> | _                   | —                    | _   | _                | IOC        | Y       | MCLR<br>VPP |

| RA4 | 3                       | 20          | AN3  | _         |                  | T1G <sup>(1)</sup>                          |                     | _                                  | _      | _                     |                     | SMTSIG1(1)             | _                   | _                    | _   | _                | IOC        | Y       | CLKOUT      |

| RA5 | 2                       | 19          | —    | _         |                  | T1CKI <sup>(1)</sup><br>T2IN <sup>(1)</sup> |                     | —                                  | _      | CLCIN3 <sup>(1)</sup> | _                   | SMTWIN1 <sup>(1)</sup> | _                   | —                    | _   | —                | IOC        | Y       | CLKIN       |

| RB4 | 13                      | 10          | AN10 | —         | _                | _                                           | _                   | _                                  | —      | _                     | _                   | _                      | _                   | SDI(1)               | _   | _                | IOC        | Y       | —           |

| RB5 | 12                      | 9           | AN11 | _         | -                | _                                           | _                   | _                                  | _      | _                     | RX <sup>(1,3)</sup> | _                      |                     | _                    | _   | —                | IOC        | Y       | _           |

| RB6 | 11                      | 8           | _    | _         | -                | _                                           | _                   | _                                  | _      | _                     | -                   | _                      | _                   | SCK <sup>(1,3)</sup> | _   | -                | IOC        | Υ       | —           |

| RB7 | 10                      | 7           |      | _         |                  | —                                           |                     | —                                  | _      | —                     | CK <sup>(1)</sup>   | —                      | _                   | —                    | _   | —                | IOC        | Y       | —           |

| RC0 | 16                      | 13          | AN4  | —         | C2IN+            | T5CKI <sup>(1)</sup>                        | —                   | _                                  | _      | _                     | _                   | _                      | —                   | _                    | _   | _                | IOC        | Y       | —           |

| RC1 | 15                      | 12          | AN5  | —         | C1IN1-<br>C2IN1- | T4IN <sup>(1)</sup>                         | _                   | —                                  | -      | CLCIN2 <sup>(2)</sup> | -                   | SMTSIG2 <sup>(1)</sup> |                     | —                    | -   | -                | IOC        | Y       | -           |

| RC2 | 14                      | 11          | AN6  | —         | C1IN2-<br>C2IN2- | _                                           | _                   | —                                  | -      | -                     | _                   | —                      | —                   | —                    | -   | —                | IOC        | Y       | —           |

| RC3 | 7                       | 4           | AN7  | —         | C1IN3-<br>C2IN3- | T5G <sup>(1)</sup>                          | CCP2 <sup>(1)</sup> | —                                  | _      | CLCIN0 <sup>(1)</sup> | _                   | —                      | ATCC <sup>(1)</sup> | —                    | _   | —                | IOC        | Y       | -           |

| RC4 | 6                       | 3           | _    | _         | _                | T3G <sup>(1)</sup>                          | _                   | _                                  | —      | CLCIN1 <sup>(1)</sup> | _                   | _                      | _                   | _                    | —   | HIC4             | IOC        | Y       | —           |

| RC5 | 5                       | 2           | _    | —         | _                | T3CKI <sup>(1)</sup>                        | CCP1 <sup>(1)</sup> | —                                  | _      | —                     | _                   | —                      | ATIN <sup>(1)</sup> | —                    | _   | HIC5             | IOC        | Y       | _           |

| RC6 | 8                       | 5           | AN8  | _         | _                | _                                           | _                   | _                                  | _      | _                     | —                   | _                      | _                   | SS <sup>(1)</sup>    | _   | _                | IOC        | Y       | _           |

| RC7 | 9                       | 6           | AN9  | _         |                  | _                                           |                     | _                                  | _      | _                     |                     | _                      |                     | —                    | _   | _                | IOC        | Y       | _           |

| Vdd | 1                       | 18          | _    | _         | _                | —                                           |                     | _                                  | _      | _                     | _                   | _                      |                     | _                    | _   | _                | _          | _       | _           |

| Vss | 20                      | 17          | _    | _         |                  | _                                           |                     | _                                  | _      | _                     |                     | _                      |                     | —                    | _   | —                |            | _       | _           |

|     |                         |             |      |           |                  |                                             |                     | vith the PPS in<br>cted as a digit |        |                       | e PPS out           | tput selection re      | gisters.            |                      |     |                  |            |         |             |

#### TABLE 4: 20-PIN ALLOCATION TABLE (PIC16(L)F1619)

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers.

These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections. 3:

## 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

## 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h, Configuration Word 2 at 8008h, and Configuration 3 at 8009h.

| Note: | The DEBUG bit in Configuration Words is     |  |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | managed automatically by device             |  |  |  |  |  |  |  |  |  |  |

|       | development tools including debuggers       |  |  |  |  |  |  |  |  |  |  |

|       | and programmers. For normal device          |  |  |  |  |  |  |  |  |  |  |

|       | operation, this bit should be maintained as |  |  |  |  |  |  |  |  |  |  |

|       | a '1'.                                      |  |  |  |  |  |  |  |  |  |  |

#### 5.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Poweron Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see **Section5.4** "**Two-Speed Clock Start-up Mode**").

## **11.7 Configuring the CRC**

The following steps illustrate how to properly configure the CRC.

- Determine if the automatic Program Memory scan will be used with the Scanner or manual calculation through the SFR interface and perform the actions specified in Section11.4 "CRC Data Sources", depending on which decision was made.

- 2. If desired, seed a starting CRC value into the CRCACCH/L registers.

- 3. Program the CRCXORH/L registers with the desired generator polynomial.

- Program the DLEN<3:0> bits of the CRCCON1 register with the length of the data word - 1 (refer to Example 11-1). This determines how many times the shifter will shift into the accumulator for each data word.

- Program the PLEN<3:0> bits of the CRCCON1 register with the length of the polynomial - 2 (refer to Example 11-1).

- 6. Determine whether shifting in trailing zeros is desired and set the ACCM bit of CRCCON0 register appropriately.

- 7. Likewise, determine whether the MSb or LSb should be shifted first and write the SHIFTM bit of CRCCON0 register appropriately.

- 8. Write the CRCGO bit of the CRCCON0 register to begin the shifting process.

- 9a. If manual SFR entry is used, monitor the FULL bit of CRCCON0 register. When FULL = 0, another word of data can be written to the CRCDATH/L registers, keeping in mind that CRCDATH should be written first if the data has >8 bits, as the shifter will begin upon the CRCDATL register being written.

- 9b. If the scanner is used, the scanner will automatically stuff words into the CRCDATH/L registers as needed, as long as the SCANGO bit is set.

- 10a. If using the Flash memory scanner, monitor the SCANIF (or the SCANGO bit) for the scanner to finish pushing information into the CRCDATA registers. After the scanner is completed, monitor the CRCIF (or the BUSY bit) to determine that the CRC has been completed and the check value can be read from the CRCACC registers. If both the interrupt flags are set (or both BUSY and SCANGO bits are cleared), the completed CRC calculation can be read from the CRCACCH/L registers.

- 10b.If manual entry is used, monitor the CRCIF (or BUSY bit) to determine when the CRCACC registers will hold the check value.

## 11.8 Program Memory Scan Configuration

If desired, the Program Memory Scan module may be used in conjunction with the CRC module to perform a CRC calculation over a range of program memory addresses. In order to set up the Scanner to work with the CRC you need to perform the following steps:

- Set the EN bit to enable the module. This can be performed at any point preceding the setting of the SCANGO bit, but if it gets disabled, all internal states of the Scanner are reset (registers are unaffected).

- Choose which memory access mode is to be used (see Section11.10 "Scanning Modes") and set the MODE bits of the SCANCON0 register appropriately.

- 3. Based on the memory access mode, set the INTM bits of the SCANCON0 register to the appropriate interrupt mode (see Section11.10.5 "Interrupt Interaction")

- 4. Set the SCANLADRL/H and SCANHADRL/H registers with the beginning and ending locations in memory that are to be scanned.

- 5. Begin the scan by setting the SCANGO bit in the SCANCON0 register. The scanner will wait (CRCGO must be set) for the signal from the CRC that it is ready for the first Flash memory location, then begin loading data into the CRC. It will continue to do so until it either hits the configured end address or an address that is unimplemented on the device, at which point the SCANGO bit will clear, Scanner functions will cease, and the SCANIF interrupt will be triggered. Alternately, the SCANGO bit can be cleared in software if desired.

## 11.9 Scanner Interrupt

The scanner will trigger an interrupt when the SCANGO bit transitions from 1 to 0. The SCANIF interrupt flag of PIR4 is set when the last memory location is reached and the data is entered into the CRCDATA registers. The SCANIF bit can only be cleared in software. The SCAN interrupt enable is the SCANIE bit of the PIE4 register.

## 11.10 Scanning Modes

The memory scanner can scan in four modes: Burst, Peek, Concurrent, and Triggered. These modes are controlled by the MODE bits of the SCANCON0 register. The four modes are summarized in Table 11-1.

## 11.10.1 BURST MODE

When MODE = 01, the scanner is in Burst mode. In Burst mode, CPU operation is stalled beginning with the operation after the one that sets the SCANGO bit, and the scan begins, using the instruction clock to execute.

## **REGISTER 12-19: LATC: PORTC DATA LATCH REGISTER**

| R/W-x/u              | R/W-x/u              | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| LATC7 <sup>(1)</sup> | LATC6 <sup>(1)</sup> | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7                |                      |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-0 | LATC<7:0>: RC<7:0> Output Latch Value bits <sup>(1)</sup> |

|---------|-----------------------------------------------------------|

|         | 1 = PORTC pin configured as an input (tri-stated)         |

|         | 0 = PORTC pin configured as an output                     |

**Note 1:** LATC<7:6> on PIC16(L)F1619 only.

2: Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

### REGISTER 12-20: ANSELC: PORTC ANALOG SELECT REGISTER

| R/W-1/1              | R/W-1/1              | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|-----|-----|---------|---------|---------|---------|

| ANSC7 <sup>(1)</sup> | ANSC6 <sup>(1)</sup> | —   | —   | ANSC3   | ANSC2   | ANSC1   | ANSC0   |

| bit 7                |                      |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 **ANSC<7:6>**: Analog Select between Analog or Digital Function on Pins RC<7:6>, respectively<sup>(1)</sup> 1 = Analog input. Pin is assigned as analog input<sup>(2)</sup>. Digital input buffer disabled.

- 0 = Digital I/O. Pin is assigned to port or digital special function.

- bit 5-4 Unimplemented: Read as '0'

bit 3-0 **ANSC<3:0>**: Analog Select between Analog or Digital Function on Pins RC<3:0>, respectively 1 = Analog input. Pin is assigned as analog input<sup>(2)</sup>. Digital input buffer disabled. 0 = Digital I/O. Pin is assigned to port or digital special function.

Note 1: ANSC<7:6> on PIC16(L)F1619 only.

2: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

## 14.6 Register Definitions: Interrupt-on-Change Control

#### **REGISTER 14-1:** IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| U-0                                     | U-0 | R/W-0/0            | R/W-0/0 | R/W-0/0                                               | R/W-0/0            | R/W-0/0 | R/W-0/0 |  |

|-----------------------------------------|-----|--------------------|---------|-------------------------------------------------------|--------------------|---------|---------|--|

| _                                       | —   | IOCAP5             | IOCAP4  | IOCAP3                                                | IOCAP2             | IOCAP1  | IOCAP0  |  |

| bit 7                                   |     |                    |         | -                                                     |                    |         | bit 0   |  |

|                                         |     |                    |         |                                                       |                    |         |         |  |

| Legend:                                 |     |                    |         |                                                       |                    |         |         |  |

| R = Readable bit                        |     | W = Writable bi    | t       | U = Unimplem                                          | ented bit, read as | '0'     |         |  |

| u = Bit is unchanged x = Bit is unknown |     |                    |         | -n/n = Value at POR and BOR/Value at all other Resets |                    |         |         |  |

| '1' = Bit is set                        |     | '0' = Bit is clear | ed      |                                                       |                    |         |         |  |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0

bit 5-0

bit 5-0

IOCAP<5:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 14-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

IOCAN<5:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

## REGISTER 14-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| —     | —   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-6 Unimplemented: Read as '0'

IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

1 = An enabled change was detected on the associated pin.

Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

0 = No change was detected, or the user cleared the detected change.

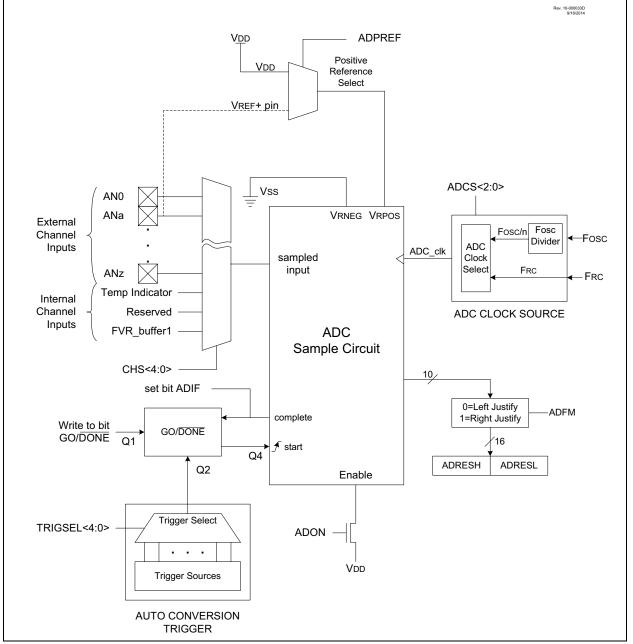

## 17.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 17-1 shows the block diagram of the ADC. The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

© 2014-2016 Microchip Technology Inc.

# PIC16(L)F1615/9

| iiiii<br>Optionsi                                   | ·<br>•      |                          |                               |                                                                                             |                                              |                 |                                                                                   |                                                  |             |          | <br>             |

|-----------------------------------------------------|-------------|--------------------------|-------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------|-----------------|-----------------------------------------------------------------------------------|--------------------------------------------------|-------------|----------|------------------|

| 80%<br>81%9 = 0<br>63%8 = 0                         |             |                          |                               |                                                                                             |                                              |                 |                                                                                   |                                                  |             |          | 5<br>5<br>7<br>7 |

|                                                     |             |                          |                               |                                                                                             |                                              |                 |                                                                                   |                                                  |             |          | ·<br>·<br>·      |

| 9403.<br>(52409 = 1<br>(53635 = 63)<br>(49468 = 63) |             |                          | ,                             |                                                                                             |                                              |                 | ,                                                                                 |                                                  |             |          |                  |

| Verite to<br>SSEVELA<br>Verifi<br>SCR9              |             |                          |                               | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 |                                              | :<br>X 822 3    | :<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>: |                                                  |             |          |                  |

|                                                     |             |                          | , /                           | . /                                                                                         | <br><br>///////////////////                  | ,               | ,                                                                                 | - / S                                            |             |          | 4<br>5<br>5      |

|                                                     |             | - 1987<br>- 1987<br>- 19 | : "//////<br>:<br>:<br>:<br>: |                                                                                             | , ''//////<br>,<br>,<br>,<br>,<br>,          | . ''//////<br>: | e "///////<br>e<br>e                                                              | , ''//////<br>, ''/y                             |             |          | *<br>1           |

| - Starropile                                        |             |                          | s 49.<br>s 49.<br>s<br>s      |                                                                                             | , //-<br>                                    |                 | с<br>с<br>ч<br>ч<br>ч                                                             |                                                  |             |          |                  |

| SSPAIF<br>Recence<br>Filse                          | ;<br>•<br>• |                          | )<br>2<br>4<br>4              | :<br>;<br>;                                                                                 | (<br>;<br>;<br>;                             |                 | )<br>2<br>4<br>4                                                                  | ;<br>;<br>;<br>;                                 | <pre></pre> |          |                  |

| SSECTOR<br>SSECTOR                                  | :<br>:<br>: | :<br>;<br>;<br>;         | c<br>c<br>c                   | < :                                                                                         | )<br>/<br>////////////////////////////////// | :<br>:<br>:     | c<br>c<br>c                                                                       | ,<br>,<br>,<br>, , , , , , , , , , , , , , , , , | >           | <u> </u> |                  |

| White Collision<br>detective active                 |             |                          |                               |                                                                                             |                                              |                 |                                                                                   |                                                  |             |          | ·····            |

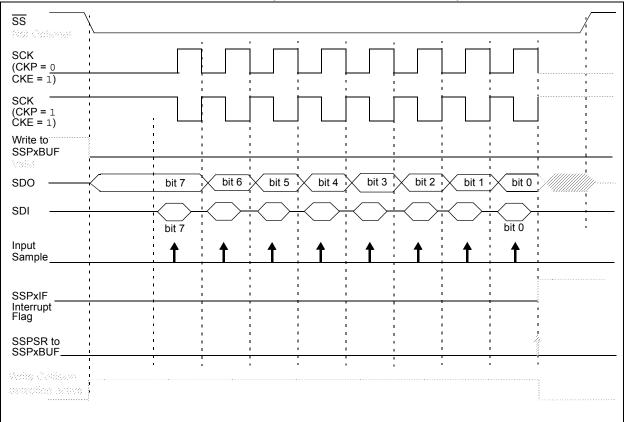

### FIGURE 24-10: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

| R/W-x/u          | R/W-x/u                                                              | R/W-x/u                           | R/W-x/u        | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|----------------------------------------------------------------------|-----------------------------------|----------------|----------------|------------------|------------------|-------------|

| LCxG3D4T         | LCxG3D4N                                                             | LCxG3D3T                          | LCxG3D3N       | LCxG3D2T       | LCxG3D2N         | LCxG3D1T         | LCxG3D1N    |

| bit 7            |                                                                      |                                   |                |                |                  |                  | bit 0       |

|                  |                                                                      |                                   |                |                |                  |                  |             |

| Legend:          |                                                                      |                                   |                |                |                  |                  |             |

| R = Readable I   | bit                                                                  | W = Writable                      | bit            | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is uncha | anged                                                                | x = Bit is unkr                   | nown           | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |                                                                      | '0' = Bit is clea                 | ared           |                |                  |                  |             |

| bit 7            |                                                                      | Gate 3 Data 4 1                   | ,              | rted) bit      |                  |                  |             |

|                  |                                                                      | gated into lcxg<br>not gated into |                |                |                  |                  |             |

| bit 6            | LCxG3D4N:                                                            | Gate 3 Data 4 I                   | Negated (inver | rted) bit      |                  |                  |             |

|                  |                                                                      | gated into Icxo<br>not gated into |                |                |                  |                  |             |

| bit 5            | LCxG3D3T: Gate 3 Data 3 True (non-inverted) bit                      |                                   |                |                |                  |                  |             |

|                  |                                                                      | gated into lcxg<br>not gated into |                |                |                  |                  |             |

| bit 4            | LCxG3D3N:                                                            | Gate 3 Data 3 I                   | Negated (inver | rted) bit      |                  |                  |             |

|                  |                                                                      | gated into Icxo<br>not gated into |                |                |                  |                  |             |

| bit 3            | LCxG3D2T: G                                                          | Gate 3 Data 2 1                   | rue (non-invei | rted) bit      |                  |                  |             |

|                  |                                                                      | gated into lcxg<br>not gated into |                |                |                  |                  |             |

| bit 2            | LCxG3D2N:                                                            | Gate 3 Data 2 I                   | Negated (inver | rted) bit      |                  |                  |             |

|                  | 1 = lcxd2N is gated into lcxg3<br>0 = lcxd2N is not gated into lcxg3 |                                   |                |                |                  |                  |             |

| bit 1            | LCxG3D1T: Gate 3 Data 1 True (non-inverted) bit                      |                                   |                |                |                  |                  |             |

|                  | 1 = Icxd1T is gated into Icxg3                                       |                                   |                |                |                  |                  |             |

|                  | 0 = Icxd1T is not gated into Icxg3                                   |                                   |                |                |                  |                  |             |

| bit 0            |                                                                      | Gate 3 Data 1                     | •              | rted) bit      |                  |                  |             |

|                  |                                                                      | gated into lcxg<br>not gated into |                |                |                  |                  |             |

|                  |                                                                      |                                   |                |                |                  |                  |             |

## REGISTER 29-9: CLCxGLS2: GATE 3 LOGIC SELECT REGISTER

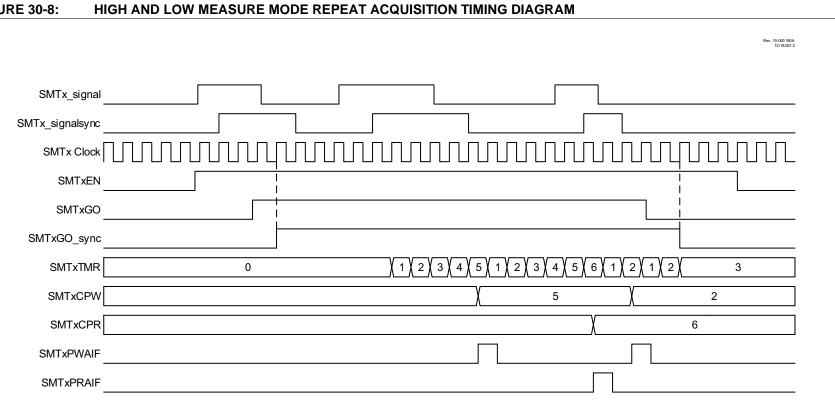

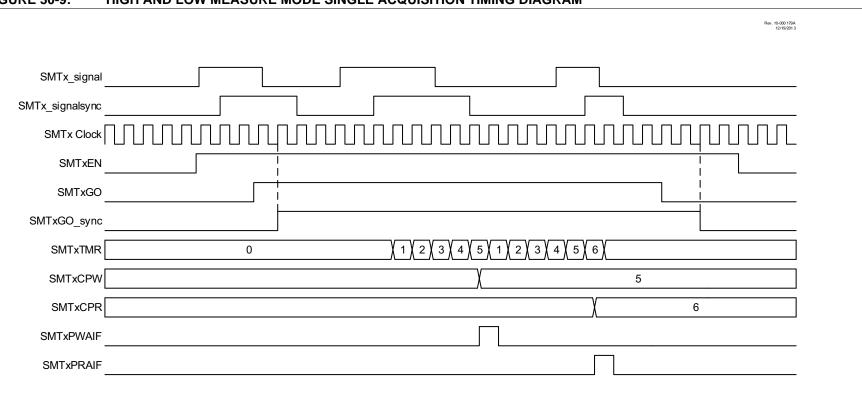

## FIGURE 30-8:

## FIGURE 30-9: HIGH AND LOW MEASURE MODE SINGLE ACQUISITION TIMING DIAGRAM

PIC16(L)F1615/9

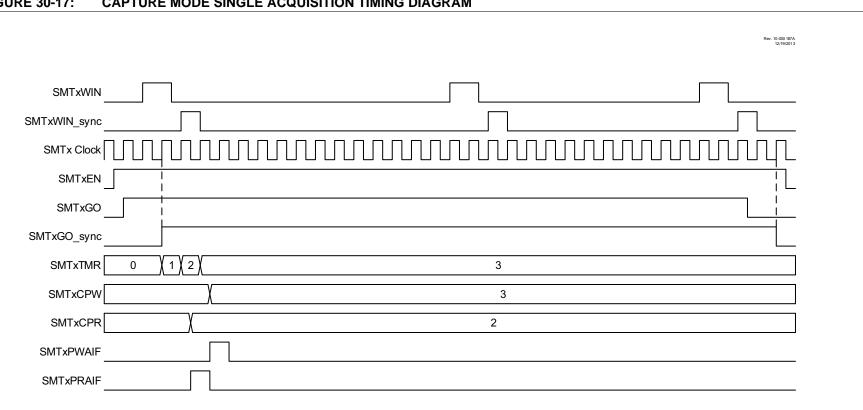

## FIGURE 30-17: CAPTURE MODE SINGLE ACQUISITION TIMING DIAGRAM

PIC16(L)F1615/9

#### 30.6.11 WINDOWED COUNTER MODE

This mode counts pulses on the SMTx\_signal input, within a window dictated by the SMTxWIN input. It begins counting upon seeing a rising edge of the SMTxWIN input, updates the SMTxCPW register on a falling edge of the SMTxWIN input, and updates the SMTxCPR register on each rising edge of the SMTxWIN input beyond the first. See Figure 30-21 and Figure 30-22.

## 30.8 Register Definitions: SMT Control

Long bit name prefixes for the Signal Measurement Timer peripherals are shown in Table 30-2. Refer to Section 1.1 "Register and Bit Naming Conventions" for more information.

TABLE 30-2:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| SMT1       | SMT1            |

| SMT2       | SMT2            |

### REGISTER 30-1: SMTxCON0: SMT CONTROL REGISTER 0

| R/W-0/0           | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------------------|-----|---------|---------|---------|---------|---------|---------|

| EN <sup>(1)</sup> | —   | STP     | WPOL    | SPOL    | CPOL    | SMTxP   | S<1:0>  |

| bit 7             |     |         |         |         |         |         | bit 0   |

| Legend:                                                                                                                                                                          |                                                                                                                                                                                                        |                                            |                                                       |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------|--|--|--|

| R = Readable bit                                                                                                                                                                 |                                                                                                                                                                                                        | W = Writable bit                           | U = Unimplemented bit, read as '0'                    |  |  |  |

| u = Bit is u                                                                                                                                                                     | unchanged                                                                                                                                                                                              | x = Bit is unknown                         | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |

| '1' = Bit is                                                                                                                                                                     | set                                                                                                                                                                                                    | '0' = Bit is cleared                       |                                                       |  |  |  |

| bit 7                                                                                                                                                                            | 1 = SMT is                                                                                                                                                                                             |                                            | e reset, clock requests are disabled                  |  |  |  |

| bit 6                                                                                                                                                                            | Unimplem                                                                                                                                                                                               | ented: Read as '0'                         |                                                       |  |  |  |

| bit 5                                                                                                                                                                            |                                                                                                                                                                                                        | Counter Halt Enable bit<br>TxTMR = SMTxPR: |                                                       |  |  |  |

| <ul> <li>1 = Counter remains SMTxPR; period match interrupt occurs when clocked</li> <li>0 = Counter resets to 24'h000000; period match interrupt occurs when clocked</li> </ul> |                                                                                                                                                                                                        |                                            |                                                       |  |  |  |

| bit 4 WPOL: SMTxWIN Input Polarity Control bit<br>1 = SMTxWIN signal is active-low/falling edge enabled<br>0 = SMTxWIN signal is active-high/rising edge enabled                 |                                                                                                                                                                                                        |                                            |                                                       |  |  |  |

| bit 3                                                                                                                                                                            | <b>SPOL:</b> SMTxSIG Input Polarity Control bit<br>1 = SMTx_signal is active-low/falling edge enabled<br>0 = SMTx_signal is active-high/rising edge enabled                                            |                                            |                                                       |  |  |  |

| bit 2                                                                                                                                                                            | <b>CPOL:</b> SMT Clock Input Polarity Control bit<br>1 = SMTxTMR increments on the falling edge of the selected clock signal<br>0 = SMTxTMR increments on the rising edge of the selected clock signal |                                            |                                                       |  |  |  |

| bit 1-0                                                                                                                                                                          | SMTxPS<1:0>: SMT Prescale Select bits<br>11 = Prescaler = 1:8<br>10 = Prescaler = 1:4<br>01 = Prescaler = 1:2<br>00 = Prescaler = 1:1                                                                  |                                            |                                                       |  |  |  |

#### **Note 1:** Setting EN to '0' does not affect the register contents.

| R/W-x/1          | R/W-x/1 | R/W-x/1            | R/W-x/1 | R/W-x/1                                     | R/W-x/1          | R/W-x/1  | R/W-x/1      |

|------------------|---------|--------------------|---------|---------------------------------------------|------------------|----------|--------------|

|                  |         |                    | SMTxF   | PR<7:0>                                     |                  |          |              |

| bit 7            |         |                    |         |                                             |                  |          | bit 0        |

|                  |         |                    |         |                                             |                  |          |              |

| Legend:          |         |                    |         |                                             |                  |          |              |

| R = Readable     | bit     | W = Writable bit   |         | U = Unimpler                                | nented bit, read | d as '0' |              |

| u = Bit is unch  | anged   | x = Bit is unkno   | own     | -n/n = Value at POR and BOR/Value at all ot |                  |          | other Resets |

| '1' = Bit is set |         | '0' = Bit is clear | red     |                                             |                  |          |              |

### REGISTER 30-18: SMTxPRL: SMT PERIOD REGISTER - LOW BYTE

bit 7-0 SMTxPR<7:0>: Significant bits of the SMT Timer Value for Period Match – Low Byte

#### REGISTER 30-19: SMTxPRH: SMT PERIOD REGISTER - HIGH BYTE

| R/W-x/1      | R/W-x/1     | R/W-x/1 | R/W-x/1 | R/W-x/1 | R/W-x/1 | R/W-x/1 | R/W-x/1 |

|--------------|-------------|---------|---------|---------|---------|---------|---------|

| SMTxPR<15:8> |             |         |         |         |         |         |         |

| bit 7        | bit 7 bit 0 |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxPR<15:8>: Significant bits of the SMT Timer Value for Period Match – High Byte

## REGISTER 30-20: SMTxPRU: SMT PERIOD REGISTER – UPPER BYTE

| R/W-x/1      | R/W-x/1 | R/W-x/1          | R/W-x/1 | R/W-x/1      | R/W-x/1         | R/W-x/1  | R/W-x/1 |

|--------------|---------|------------------|---------|--------------|-----------------|----------|---------|

|              |         |                  | SMTxPF  | ?<23:16>     |                 |          |         |

| bit 7        |         |                  |         |              |                 |          | bit 0   |

|              |         |                  |         |              |                 |          |         |

| Legend:      |         |                  |         |              |                 |          |         |

| R = Readable | hit     | W = Writable bit | ł       | =   Inimpler | mented hit read | 1 26 '0' |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxPR<23:16>: Significant bits of the SMT Timer Value for Period Match – Upper Byte

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

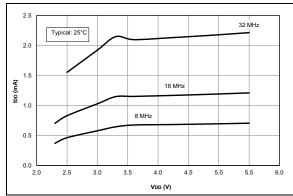

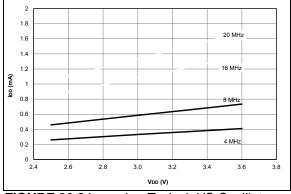

FIGURE 36-19: IDD Typical, HFINTOSC Mode, PIC16F1615/9 Only.

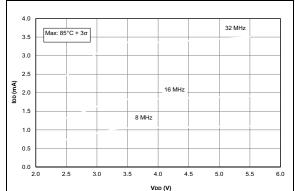

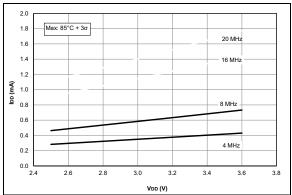

FIGURE 36-20: IDD Maximum, HFINTOSC Mode, PIC16F1615/9 Only.

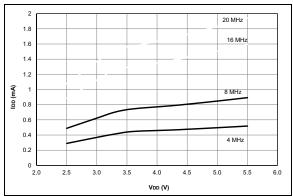

**FIGURE 36-21:** IDD Typical, HS Oscillator, 25°C, PIC16LF1615/9 Only.

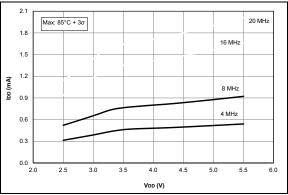

FIGURE 36-22: IDD Maximum, HS Oscillator, PIC16LF1615/9 Only.

**FIGURE 36-23:** IDD Typical, HS Oscillator, 25°C, PIC16F1615/9 Only.

FIGURE 36-24: IDD Maximum, HS Oscillator, PIC16F1615/9 Only.

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

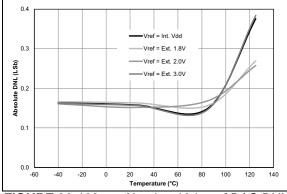

**FIGURE 36-103:** Absolute Value of DAC DNL Error, VDD = 3.0V, VREF = VDD.

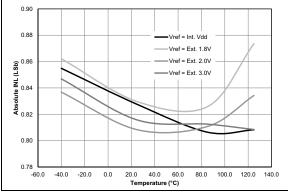

**FIGURE 36-104:** Absolute Value of DAC INL Error, VDD = 3.0V, VREF = VDD.

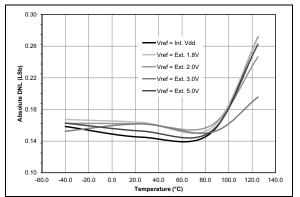

**FIGURE 36-105:** Absolute Value of DAC DNL Error, VDD = 5.0V, VREF = VDD, PIC16F1615/9 Only.

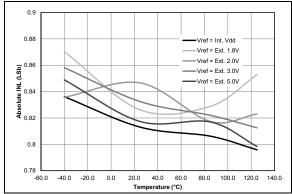

FIGURE 36-106: Absolute Value of DAC INL Error, VDD = 5.0V, VREF = VDD, PIC16F1615/9 Only.

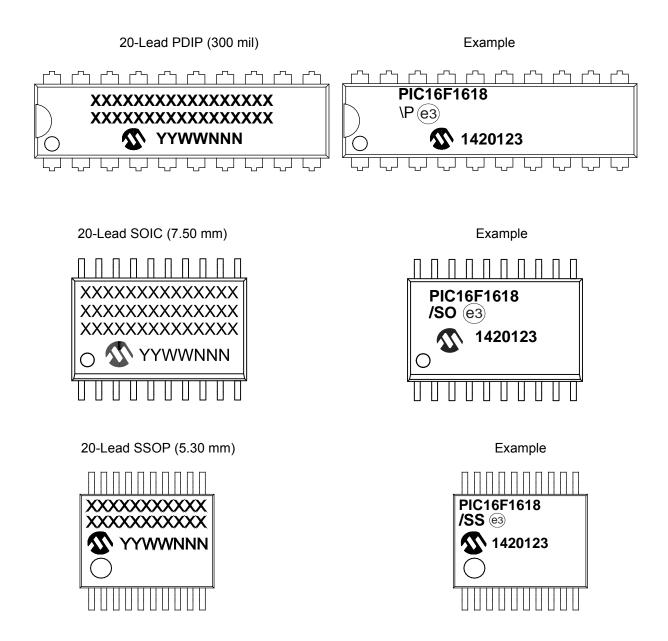

## 38.1 Package Marking Information (Continued)

For the most current package drawings, please see the Microchip Packaging Specification located at

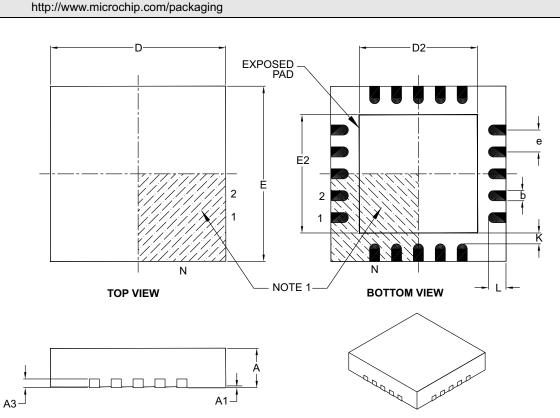

### 20-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

Units MILLIMETERS Dimension Limits MIN NOM MAX Number of Pins Ν 20 Pitch 0.50 BSC е **Overall Height** А 0.80 0.90 1.00 Standoff A1 0.00 0.02 0.05 Contact Thickness A3 0.20 REF Overall Width 4.00 BSC Е Exposed Pad Width E2 2.60 2.70 2.80 **Overall Length** D 4.00 BSC Exposed Pad Length D2 2.60 2.70 2.80 Contact Width 0.18 0.25 0.30 b Contact Length L 0.30 0.40 0.50 Contact-to-Exposed Pad Κ 0.20 \_ \_

#### Notes:

Note:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-126B