# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 20-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1619-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet Revision History597

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

## TABLE 3-11:PIC16(L)F1615/9 MEMORYMAP, BANK 30

|         | •             |                                                 |

|---------|---------------|-------------------------------------------------|

|         |               | Bank 30                                         |

|         | F0Ch          |                                                 |

|         | F0Dh          |                                                 |

|         | F0Eh          |                                                 |

|         | F0Fh          | CLCDATA                                         |

|         | F10h          | CLC1CON                                         |

|         | F11h          | CLC1POL                                         |

|         | F12h          | CLC1SEL0                                        |

|         | F13h          | CLC1SEL1                                        |

|         | F14h          | CLC1SEL2                                        |

|         | F15h          | CLC1SEL3                                        |

|         | F16h          | CLC1GLS0                                        |

|         | F17h          | CLC1GLS1                                        |

|         | F1711<br>F18h | CLC1GLS2                                        |

|         |               | CLC1GLS3                                        |

|         | F19h          | CLC2CON                                         |

|         | F1Ah          |                                                 |

|         | F1Bh          | CLC2POL                                         |

|         | F1Ch          | CLC2SEL0                                        |

|         | F1Dh          | CLC2SEL1                                        |

|         | F1Eh          | CLC2SEL2                                        |

|         | F1Fh          | CLC2SEL3                                        |

|         | F20h          | CLC2GLS0                                        |

|         | F21h          | CLC2GLS1                                        |

|         | F22h          | CLC2GLS2                                        |

|         | F23h          | CLC2GLS3                                        |

|         | F24h          | CLC3CON                                         |

|         | F25h          | CLC3POL                                         |

|         | F26h          | CLC3SEL0                                        |

|         | F27h          | CLC3SEL1                                        |

|         | F28h          | CLC3SEL2<br>CLC3SEL3                            |

|         | F29h<br>F2Ah  | CLC3GLS0                                        |

|         | F2An<br>F2Bh  | CLC3GLS0                                        |

|         | F2Ch          | CLC3GLS1                                        |

|         | F2Dh          | CLC3GLS3                                        |

|         | F2Eh          | CLC4CON                                         |

|         | F2Fh          | CLC4POL                                         |

|         | F30h          | CLC4SEL0                                        |

|         | F31h          | CLC4SEL1                                        |

|         | F32h          | CLC4SEL2                                        |

|         | F33h          | CLC4SEL3                                        |

|         | F34h          | CLC4GLS0                                        |

|         | F35h          | CLC4GLS1                                        |

|         | F36h          | CLC4GLS2                                        |

|         | F37h          | CLC4GLS3                                        |

|         | F38h          |                                                 |

|         |               | —                                               |

|         | F6Fh          |                                                 |

|         |               |                                                 |

| Legend: |               | Unimplemented data memory locations, ad as '0'. |

| 1       |               |                                                 |

## TABLE 3-12: PIC16(L)F1615/9 MEMORY MAP, BANK 31

|         | Bank 31                                |                 |

|---------|----------------------------------------|-----------------|

| F8Ch    |                                        |                 |

|         | Unimplemented<br>Read as '0'           |                 |

| FE3h    |                                        |                 |

| FE4h    | STATUS_SHAD                            |                 |

| FE5h    | WREG_SHAD                              |                 |

| FE6h    | BSR_SHAD                               |                 |

| FE7h    | PCLATH_SHAD                            |                 |

| FE8h    | FSR0L_SHAD                             |                 |

| FE9h    | FSR0H_SHAD                             |                 |

| FEAh    | FSR1L_SHAD                             |                 |

| FEBh    |                                        |                 |

| FECh    |                                        |                 |

| FEDh    | STKPTR                                 |                 |

| FEEh    | TOSL                                   |                 |

| FEFh    | TOSH                                   |                 |

| Logondu | - Unimplemented data ma                | monulopotiono   |

| Legend: | = Unimplemented data me<br>ead as '0'. | mory locations, |

## 7.6 Register Definitions: Interrupt Control

| R/W-0/0            |                                                               | R/W-0/0                                                     | R/W-0/0              | R/W-0/0          | R/W-0/0           | R/W-0/0           | R-0/0                |

|--------------------|---------------------------------------------------------------|-------------------------------------------------------------|----------------------|------------------|-------------------|-------------------|----------------------|

| GIE <sup>(1)</sup> | PEIE <sup>(2)</sup>                                           | TMR0IE                                                      | INTE                 | IOCIE            | TMR0IF            | INTF              | IOCIF <sup>(3)</sup> |

| bit 7              |                                                               |                                                             |                      |                  |                   |                   | bit (                |

|                    |                                                               |                                                             |                      |                  |                   |                   |                      |

| Legend:            |                                                               |                                                             |                      |                  |                   |                   |                      |

| R = Reada          | ble bit                                                       | W = Writable                                                | bit                  | U = Unimpler     | mented bit, read  | l as '0'          |                      |

| u = Bit is u       | •                                                             | x = Bit is unkı                                             |                      | -n/n = Value a   | at POR and BO     | R/Value at all o  | ther Resets          |

| '1' = Bit is s     | set                                                           | '0' = Bit is cle                                            | ared                 |                  |                   |                   |                      |

| bit 7              | GIE: Global                                                   | Interrupt Enable                                            | e bit <sup>(1)</sup> |                  |                   |                   |                      |

|                    |                                                               | all active interru<br>all interrupts                        | ıpts                 |                  |                   |                   |                      |

| bit 6              | 1 = Enables                                                   | neral Interrupt E<br>all active periph<br>all peripheral ir | eral interrupts      | 3                |                   |                   |                      |

| bit 5              | 1 = Enables                                                   | ner0 Overflow Ir<br>the Timer0 inter<br>the Timer0 inter    | rupt                 | e bit            |                   |                   |                      |

| bit 4              | 1 = Enables                                                   | xternal Interrupt<br>the INT externa<br>the INT externa     | l interrupt          |                  |                   |                   |                      |

| bit 3              | 1 = Enables                                                   | upt-on-Change<br>the interrupt-on<br>the interrupt-or       | -change              |                  |                   |                   |                      |

| bit 2              | 1 = TMR0 re                                                   | ner0 Overflow Ir<br>gister has overf<br>gister did not ov   | lowed                | it               |                   |                   |                      |

| bit 1              | 1 = The INT                                                   | kternal Interrupt<br>external interru<br>external interru   | pt occurred          | ır               |                   |                   |                      |

| bit 0              | 1 = When at                                                   | upt-on-Change<br>least one of the<br>the interrupt-on       | interrupt-on-o       | change pins ch   |                   |                   |                      |

| Note 1:            | Interrupt flag bits<br>enable bit or the<br>appropriate inter | Global Interrupt                                            | Enable bit, G        | E of the INTCO   | ON register. Use  |                   |                      |

| 2:                 | Bit PEIE of the IN                                            | NTCON register                                              | must be set t        | o enable any p   | eripheral interru | upt.              |                      |

| 3:                 | The IOCIF Flag                                                | oit is read-only a                                          | and cleared w        | hen all the inte | rrupt-on-change   | e flags in the IC | CxF register         |

## REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

## 12.2 Register Definitions: PORTA

| U-0                                     | U-0 | R/W-x/x                               | R/W-x/x                                               | R-x/x                              | R/W-x/x | R/W-x/x | R/W-x/x |

|-----------------------------------------|-----|---------------------------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|

| —                                       | _   | RA5                                   | RA4                                                   | RA3                                | RA2     | RA1     | RA0     |

| bit 7                                   |     |                                       |                                                       |                                    | •       |         | bit 0   |

|                                         |     |                                       |                                                       |                                    |         |         |         |

| Legend:                                 |     |                                       |                                                       |                                    |         |         |         |

| R = Readable b                          | oit | W = Writable                          | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |

| u = Bit is unchanged x = Bit is unknown |     |                                       | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |

|                                         |     | '1' = Bit is set '0' = Bit is cleared |                                                       |                                    |         |         |         |

| REGISTER 12-1: | PORTA: PORTA REGISTER |

|----------------|-----------------------|

|----------------|-----------------------|

| bit 7-6 | Unimplemented: Read as '0'                                                               |

|---------|------------------------------------------------------------------------------------------|

| bit 5-0 | <b>RA&lt;5:0&gt;</b> : PORTA I/O Value bits <sup>(1)</sup><br>1 = Port pin is $\geq$ VIH |

|         | 0 = Port pin is <u>&lt;</u> Vı∟                                                          |

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 12-2: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|-----|---------|---------|---------|

| —     | —   | TRISA5  | TRISA4  | (1) | TRISA2  | TRISA1  | TRISA0  |

| bit 7 |     |         |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                         |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>TRISA&lt;5:4&gt;:</b> PORTA Tri-State Control bit<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

| bit 3   | Unimplemented: Read as '1'                                                                                                                         |

| bit 2-0 | <b>TRISA&lt;2:0&gt;:</b> PORTA Tri-State Control bit<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

Note 1: Unimplemented, read as '1'.

#### 12.3.7 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the peripheral pin select logic. See **Section13.0** "**Peripheral Pin Select (PPS) Module**" for more information. Analog input functions, such as ADC inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELB register. Digital output functions continue to may continue to control the pin when it is in Analog mode.

## 13.0 PERIPHERAL PIN SELECT (PPS) MODULE

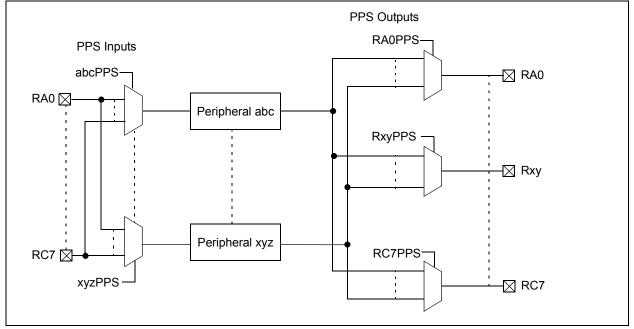

The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections. All analog inputs and outputs remain fixed to their assigned pins. Input and output selections are independent as shown in the simplified block diagram Figure 13-1.

## 13.1 PPS Inputs

Each peripheral has a PPS register with which the inputs to the peripheral are selected. Inputs include the device pins.

Multiple peripherals can operate from the same source simultaneously. Port reads always return the pin level regardless of peripheral PPS selection. If a pin also has associated analog functions, the ANSEL bit for that pin must be cleared to enable the digital input buffer.

Although every peripheral has its own PPS input selection register, the selections are identical for every peripheral as shown in Register 13-1.

| Note: | The notation "xxx" in the register name is    |

|-------|-----------------------------------------------|

|       | a place holder for the peripheral identifier. |

|       | For example, CLC1PPS.                         |

## 13.2 PPS Outputs

Each I/O pin has a PPS register with which the pin output source is selected. With few exceptions, the port TRIS control associated with that pin retains control over the pin output driver. Peripherals that control the pin output driver as part of the peripheral operation will override the TRIS control as needed. These peripherals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

- · CWG (auto-shutdown)

Although every pin has its own PPS peripheral selection register, the selections are identical for every pin as shown in Register 13-2.

**Note:** The notation "Rxy" is a place holder for the pin identifier. For example, RA0PPS.

#### FIGURE 13-1: SIMPLIFIED PPS BLOCK DIAGRAM

| R/W-0/       |                          | R/W-0/0           | R/W-0/0          | R/W-0/0                       | U-0             | U-0              | U-0          |

|--------------|--------------------------|-------------------|------------------|-------------------------------|-----------------|------------------|--------------|

|              | Т                        | RIGSEL<4:0>(1     | )                |                               |                 | —                | —            |

| bit 7        |                          |                   |                  |                               |                 |                  | bit          |

| Legend:      |                          |                   |                  |                               |                 |                  |              |

| R = Reada    | able bit                 | W = Writable      | bit              | U = Unimplem                  | ented bit. read | d as '0'         |              |

|              | unchanged                | x = Bit is unkr   |                  | -                             |                 | R/Value at all o | other Resets |

| '1' = Bit is | 0                        | '0' = Bit is cle  |                  |                               |                 |                  |              |

|              |                          |                   |                  |                               |                 |                  |              |

| bit 7-3      | TRIGSEL<4                | :0>: Auto-Conv    | ersion Trigger   | Selection bits <sup>(1)</sup> |                 |                  |              |

|              | 11111 = Re               | eserved           |                  |                               |                 |                  |              |

|              | •                        |                   |                  |                               |                 |                  |              |

|              |                          |                   |                  |                               |                 |                  |              |

|              | 10101 <b>= Re</b>        | served            |                  |                               |                 |                  |              |

|              | 10100 <b>= AT</b>        | 1_cmp3            |                  |                               |                 |                  |              |

|              | 10011 <b>= AT</b>        |                   |                  |                               |                 |                  |              |

|              | 10010 <b>= AT</b>        |                   |                  |                               |                 |                  |              |

|              | 10001 = CL<br>10000 = CL |                   |                  |                               |                 |                  |              |

|              | 01111 = CL               |                   |                  |                               |                 |                  |              |

|              | 01110 = CL               |                   |                  |                               |                 |                  |              |

|              |                          | IR5_overflow      |                  |                               |                 |                  |              |

|              |                          | IR3_overflow      |                  |                               |                 |                  |              |

|              | 01011 = SN               |                   |                  |                               |                 |                  |              |

|              | 01010 =SM                | 1R6_postscaled    |                  |                               |                 |                  |              |

|              |                          | 1R4_postscaled    |                  |                               |                 |                  |              |

|              | 00111 <b>= C2</b>        |                   |                  |                               |                 |                  |              |

|              |                          | _OUT_sync         |                  |                               |                 |                  |              |

|              |                          | 1R2_postscaled    |                  |                               |                 |                  |              |

|              | 00100 = T1<br>00011 = T0 |                   |                  |                               |                 |                  |              |

|              | 00011 = 10<br>00010 = CC |                   |                  |                               |                 |                  |              |

|              | 00001 = CC               |                   |                  |                               |                 |                  |              |

|              |                          | auto-conversio    | n trigger seled  | ted                           |                 |                  |              |

| bit 2-0      | Unimpleme                | nted: Read as '   | 0'               |                               |                 |                  |              |

| Note 1:      | This is a rising ed      | dge sensitive inp | out for all sour | ces.                          |                 |                  |              |

| 2:           | Signal also sets i       | to corresponding  | n interrunt floo |                               |                 |                  |              |

## REGISTER 17-3: ADCON2: ADC CONTROL REGISTER 2

#### **19.3 Comparator Hysteresis**

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See **Section35.0 "Electrical Specifications"** for more information.

## 19.4 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section22.5 "Timer1 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 19.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from a comparator can be synchronized with Timer1 by setting the CxSYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 19-2) and the Timer1 Block Diagram (Figure 22-1) for more information.

#### **19.5** Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (CxINTP and/or CxINTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- CxON, CxPOL and CxSP bits of the CMxCON0 register

- CxIE bit of the PIE2 register

- CxINTP bit of the CMxCON1 register (for a rising edge detection)

- CxINTN bit of the CMxCON1 register (for a falling edge detection)

- PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

**Note:** Although a comparator is disabled, an interrupt can be generated by changing the output polarity with the CxPOL bit of the CMxCON0 register, or by switching the comparator on or off with the CxON bit of the CMxCON0 register.

## 19.6 Comparator Positive Input Selection

Configuring the CxPCH<1:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- CxIN+ analog pin

- DAC output

- FVR (Fixed Voltage Reference)

- Vss (Ground)

See Section15.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section18.0 "8-bit Digital-to-Analog Converter (DAC1) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

## 19.7 Comparator Negative Input Selection

The CxNCH<2:0> bits of the CMxCON1 register direct an analog input pin or analog ground to the inverting input of the comparator:

- CxIN0- pin

- CxIN1- pin

- CxIN2- pin

- CxIN3- pin

- Analog Ground

- FVR\_buffer2

Some inverting input selections share a pin with the operational amplifier output function. Enabling both functions at the same time will direct the operational amplifier output to the comparator inverting input.

Note: To use CxINy+ and CxINy- pins as analog input, the appropriate bits must be set in the ANSEL register and the corresponding TRIS bits must also be set to disable the output drivers.

## 24.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

## 24.1 MSSP Module Overview

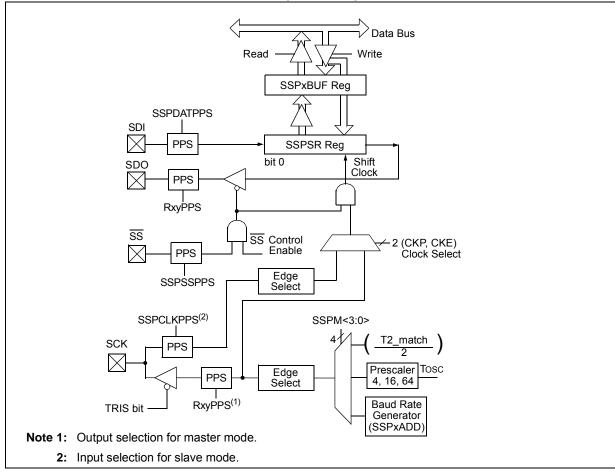

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 24-1 is a block diagram of the SPI interface module.

#### FIGURE 24-1: MSSP BLOCK DIAGRAM (SPI MODE)

## 24.3 I<sup>2</sup>C MODE OVERVIEW

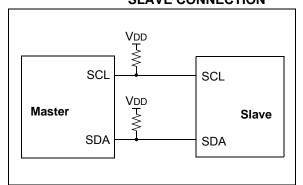

The Inter-Integrated Circuit  $(I^2C)$  bus is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- Serial Clock (SCL)

- Serial Data (SDA)

Figure 24-11 shows the block diagram of the MSSP module when operating in  $I^2C$  mode.

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 24-11 shows a typical connection between two processors configured as master and slave devices.

The  $I^2C$  bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode (master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

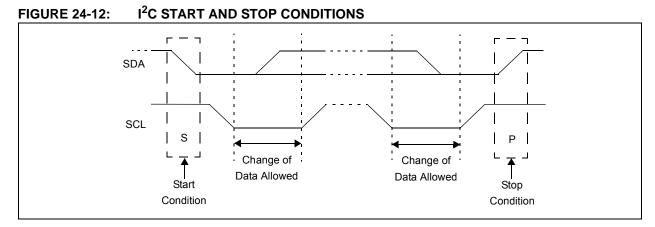

A Start bit is indicated by a high-to-low transition of the SDA line while the SCL line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

### FIGURE 24-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDA line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCL line is held low. Transitions that occur while the SCL line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an ACK bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

#### 24.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 24-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDA line low before asserting it low. This does not conform to the  $I^2C$  Specification that states no bus collision can occur on a Start.

#### 24.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

Note: At least one SCL low time must appear before a Stop is valid, therefore, if the SDA line goes low then high again while the SCL line stays high, only the Start condition is detected.

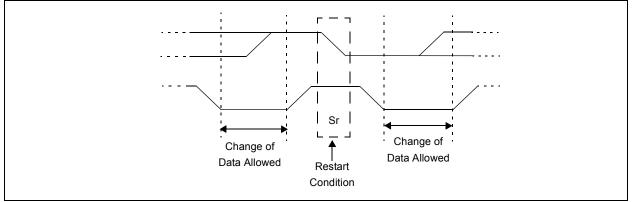

## 24.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 24-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the R/W bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained until a Stop condition, a high address with  $R/\overline{W}$  clear, or high address match fails.

#### 24.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPxCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

|        |                   | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                |                   |                             |                |                    |                             |                |            |                             |

|--------|-------------------|------------------------------------------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|--------------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 20.000 MHz |                                                      | Fosc = 18.432 MHz           |                | Fosc = 16.000 MHz |                             |                | Fosc = 11.0592 MHz |                             |                |            |                             |

| RATE   | Actual<br>Rate    | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0             | 0.00                                                 | 16665                       | 300.0          | 0.00              | 15359                       | 300.0          | 0.00               | 13332                       | 300.0          | 0.00       | 9215                        |

| 1200   | 1200              | -0.01                                                | 4166                        | 1200           | 0.00              | 3839                        | 1200.1         | 0.01               | 3332                        | 1200           | 0.00       | 2303                        |

| 2400   | 2400              | 0.02                                                 | 2082                        | 2400           | 0.00              | 1919                        | 2399.5         | -0.02              | 1666                        | 2400           | 0.00       | 1151                        |

| 9600   | 9597              | -0.03                                                | 520                         | 9600           | 0.00              | 479                         | 9592           | -0.08              | 416                         | 9600           | 0.00       | 287                         |

| 10417  | 10417             | 0.00                                                 | 479                         | 10425          | 0.08              | 441                         | 10417          | 0.00               | 383                         | 10433          | 0.16       | 264                         |

| 19.2k  | 19.23k            | 0.16                                                 | 259                         | 19.20k         | 0.00              | 239                         | 19.23k         | 0.16               | 207                         | 19.20k         | 0.00       | 143                         |

| 57.6k  | 57.47k            | -0.22                                                | 86                          | 57.60k         | 0.00              | 79                          | 57.97k         | 0.64               | 68                          | 57.60k         | 0.00       | 47                          |

| 115.2k | 116.3k            | 0.94                                                 | 42                          | 115.2k         | 0.00              | 39                          | 114.29k        | -0.79              | 34                          | 115.2k         | 0.00       | 23                          |

## TABLE 25-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|----------------|------------------------------------------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000                                            | ) MHz                       | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0          | 0.00                                                 | 6666                        | 300.0            | 0.01       | 3332                        | 300.0             | 0.00       | 3071                        | 300.1            | 0.04       | 832                         |

| 1200   | 1200           | -0.02                                                | 1666                        | 1200             | 0.04       | 832                         | 1200              | 0.00       | 767                         | 1202             | 0.16       | 207                         |

| 2400   | 2401           | 0.04                                                 | 832                         | 2398             | 0.08       | 416                         | 2400              | 0.00       | 383                         | 2404             | 0.16       | 103                         |

| 9600   | 9615           | 0.16                                                 | 207                         | 9615             | 0.16       | 103                         | 9600              | 0.00       | 95                          | 9615             | 0.16       | 25                          |

| 10417  | 10417          | 0                                                    | 191                         | 10417            | 0.00       | 95                          | 10473             | 0.53       | 87                          | 10417            | 0.00       | 23                          |

| 19.2k  | 19.23k         | 0.16                                                 | 103                         | 19.23k           | 0.16       | 51                          | 19.20k            | 0.00       | 47                          | 19.23k           | 0.16       | 12                          |

| 57.6k  | 57.14k         | -0.79                                                | 34                          | 58.82k           | 2.12       | 16                          | 57.60k            | 0.00       | 15                          | —                | _          | _                           |

| 115.2k | 117.6k         | 2.12                                                 | 16                          | 111.1k           | -3.55      | 8                           | 115.2k            | 0.00       | 7                           | —                | _          | —                           |

## 28.5 Dead-Band Control

The dead-band control provides non-overlapping PWM signals to prevent shoot-through current in PWM switches. Dead-band operation is employed for Half-Bridge and Full-Bridge modes. The CWG contains two 6-bit dead-band counters. One is used for the rising edge of the input source control in Half-Bridge mode or for reverse dead-band Full-Bridge mode. The other is used for the falling edge of the input source control in Half-Bridge mode or for forward dead band in Full-Bridge mode.

Dead band is timed by counting CWG clock periods from zero up to the value in the rising or falling deadband counter registers. See CWGxDBR and CWGxDBF registers, respectively.

#### 28.5.1 DEAD-BAND FUNCTIONALITY IN HALF-BRIDGE MODE

In Half-Bridge mode, the dead-band counters dictate the delay between the falling edge of the normal output and the rising edge of the inverted output. This can be seen in Figure 28-9.

#### 28.5.2 DEAD-BAND FUNCTIONALITY IN FULL-BRIDGE MODE

In Full-Bridge mode, the dead-band counters are used when undergoing a direction change. The MODE<0> bit of the CWGxCON0 register can be set or cleared while the CWG is running, allowing for changes from Forward to Reverse mode. The CWGxA and CWGxC signals will change immediately upon the first rising input edge following a direction change, but the modulated signals (CWGxB or CWGxD, depending on the direction of the change) will experience a delay dictated by the dead-band counters. This is demonstrated in Figure 28-3.

## 28.6 Rising Edge and Reverse Dead Band

CWGxDBR controls the rising edge dead-band time at the leading edge of CWGxA (Half-Bridge mode) or the leading edge of CWGxB (Full-Bridge mode). The CWGxDBR value is double-buffered. When EN = 0, the CWGxDBR register is loaded immediately when CWGxDBR is written. When EN = 1, then software must set the LD bit of the CWGxCON0 register, and the buffer will be loaded at the next falling edge of the CWG input signal. If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output.

## 28.7 Falling Edge and Forward Dead Band

CWGxDBF controls the dead-band time at the leading edge of CWGxB (Half-Bridge mode) or the leading edge of CWGxD (Full-Bridge mode). The CWGxDBF value is double-buffered. When EN = 0, the CWGxDBF register is loaded immediately when CWGxDBF is written. When EN = 1 then software must set the LD bit of the CWGxCON0 register, and the buffer will be loaded at the next falling edge of the CWG input signal. If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output. Refer to Figure 28.6 and Figure 28.7 for examples.

| R/W-x/u          | R/W-x/u         | R/W-x/u                            | R/W-x/u       | R/W-x/u           | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|-----------------|------------------------------------|---------------|-------------------|------------------|------------------|-------------|

| LCxG2D4T         | LCxG2D4N        | LCxG2D3T                           | LCxG2D3N      | LCxG2D2T          | LCxG2D2N         | LCxG2D1T         | LCxG2D1N    |

| bit 7            |                 |                                    |               |                   |                  |                  | bit 0       |

|                  |                 |                                    |               |                   |                  |                  |             |

| Legend:          |                 |                                    |               |                   |                  |                  |             |

| R = Readable     | bit             | W = Writable                       |               | U = Unimpler      | nented bit, read | as '0'           |             |

| u = Bit is unch  | anged           | x = Bit is unkr                    | nown          | -n/n = Value a    | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |                 | '0' = Bit is cle                   | ared          |                   |                  |                  |             |

|                  |                 |                                    |               |                   |                  |                  |             |

| bit 7            |                 | Gate 2 Data 4 1                    | •             | rted) bit         |                  |                  |             |

|                  |                 | gated into lcxg<br>not gated into  |               |                   |                  |                  |             |

| bit 6            |                 | Gate 2 Data 4                      | •             | rted) bit         |                  |                  |             |

|                  |                 | gated into lcx                     |               |                   |                  |                  |             |

|                  |                 | not gated into                     |               |                   |                  |                  |             |

| bit 5            |                 | Gate 2 Data 3 1                    | ,             | rted) bit         |                  |                  |             |

|                  |                 | gated into lcxg                    |               |                   |                  |                  |             |

| bit 4            |                 | not gated into<br>Gate 2 Data 3    | •             | tod) bit          |                  |                  |             |

| DIL 4            |                 | gated into lcx                     | •             | (eu) bit          |                  |                  |             |

|                  |                 | not gated into                     | •             |                   |                  |                  |             |

| bit 3            | LCxG2D2T: (     | Gate 2 Data 2 1                    | rue (non-inve | rted) bit         |                  |                  |             |

|                  |                 | gated into lcxg                    |               |                   |                  |                  |             |

|                  |                 | not gated into                     | •             |                   |                  |                  |             |

| bit 2            |                 | Gate 2 Data 2                      | •             | rted) bit         |                  |                  |             |

|                  |                 | s gated into lcx<br>not gated into |               |                   |                  |                  |             |

| bit 1            |                 | Gate 2 Data 1 1                    | -             | rted) bit         |                  |                  |             |

|                  |                 | gated into lcxg                    |               | ···· <b>,</b> · · |                  |                  |             |

|                  | 0 = lcxd1T is   | not gated into                     | lcxg2         |                   |                  |                  |             |

| bit 0            |                 | Gate 2 Data 1                      | •             | rted) bit         |                  |                  |             |

|                  |                 | gated into lcx                     |               |                   |                  |                  |             |

|                  | 0 = 1000  IN IS | not gated into                     | icxgz         |                   |                  |                  |             |

|                  |                 |                                    |               |                   |                  |                  |             |

|                  |                 |                                    |               |                   |                  |                  |             |

## REGISTER 29-8: CLCxGLS1: GATE 2 LOGIC SELECT REGISTER

#### 30.6.8 CAPTURE MODE

This mode captures the Timer value based on a rising or falling edge on the SMTWINx input and triggers an interrupt. This mimics the capture feature of a CCP module. The timer begins incrementing upon the SMTxGO bit being set, and updates the value of the SMTxCPR register on each rising edge of SMTWINx, and updates the value of the CPW register on each falling edge of the SMTWINx. The timer is not reset by any hardware conditions in this mode and must be reset by software, if desired. See Figure 30-16 and Figure 30-17.

| U-0              | R/W-0/0        | U-0                                                                                               | R/W-0/0      | U-0              | R/W-0/0           | R-0/0            | R-0/0        |  |  |  |

|------------------|----------------|---------------------------------------------------------------------------------------------------|--------------|------------------|-------------------|------------------|--------------|--|--|--|

| —                | PHP            | —                                                                                                 | PRP          |                  | MPP               | ACCS             | VALID        |  |  |  |

| bit 7            |                |                                                                                                   |              |                  |                   |                  | bit 0        |  |  |  |

|                  |                |                                                                                                   |              |                  |                   |                  |              |  |  |  |

| Legend:          |                |                                                                                                   |              |                  |                   |                  |              |  |  |  |

| R = Readable     | bit            | W = Writable                                                                                      | bit          | U = Unimpler     | mented bit, read  | as '0'           |              |  |  |  |

| u = Bit is unch  | anged          | x = Bit is unkr                                                                                   | nown         | -n/n = Value     | at POR and BO     | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is set |                | '0' = Bit is clea                                                                                 | ared         | q = Value de     | pends on conditi  | on               |              |  |  |  |

|                  |                |                                                                                                   |              |                  |                   |                  |              |  |  |  |

| bit 7            | Unimplemen     | ted: Read as '                                                                                    | כ'           |                  |                   |                  |              |  |  |  |

| bit 6            | PHP: Phase (   | Clock Output P                                                                                    | olarity bit  |                  |                   |                  |              |  |  |  |

|                  |                | ock output is ad                                                                                  |              |                  |                   |                  |              |  |  |  |

|                  |                | ock output is a                                                                                   | •            |                  |                   |                  |              |  |  |  |

| bit 5            | Unimplemen     | ted: Read as '                                                                                    | כ'           |                  |                   |                  |              |  |  |  |

| bit 4            |                | Clock Output P                                                                                    | •            |                  |                   |                  |              |  |  |  |

|                  |                | <ul> <li>Period clock output is active-low</li> <li>Period clock output is active-high</li> </ul> |              |                  |                   |                  |              |  |  |  |

| 1 11 0           |                |                                                                                                   | •            |                  |                   |                  |              |  |  |  |

| bit 3            | •              | ted: Read as '                                                                                    |              |                  |                   |                  |              |  |  |  |

| bit 2            | •              | Pulse Output                                                                                      | •            |                  |                   |                  |              |  |  |  |

|                  |                | oulse output is a<br>oulse output is a                                                            |              |                  |                   |                  |              |  |  |  |

| bit 1            |                | eration Sign bit                                                                                  | -            |                  |                   |                  |              |  |  |  |

| bit i            |                | e currently in A                                                                                  |              | s than the prev  | ious value        |                  |              |  |  |  |

|                  |                |                                                                                                   |              |                  | ual to the previo | ous value        |              |  |  |  |

| bit 0            |                | Measurement I                                                                                     | •            |                  | •                 |                  |              |  |  |  |

|                  | 1 = Sufficient | t input cycles h                                                                                  | ave occurred | to make ATxP     | ER and ATxPHS     | S valid.         |              |  |  |  |

|                  | 0 = The value  | es in ATxPER a                                                                                    | and ATxPHS   | are not valid; n | ot enough input   | cycles have o    | ccurred      |  |  |  |

## REGISTER 31-2: ATxCON1: ANGULAR TIMER CONTROL 1 REGISTER

| Mnemonic,<br>Operands |      | Description                                   |        | 14-Bit Opcode |      |      |      | Status   | Notes |

|-----------------------|------|-----------------------------------------------|--------|---------------|------|------|------|----------|-------|

|                       |      |                                               |        | MSb           |      |      | LSb  | Affected | Notes |

|                       |      | CONTROL OPERA                                 | TIONS  |               |      |      |      |          |       |

| BRA                   | k    | Relative Branch                               | 2      | 11            | 001k | kkkk | kkkk |          |       |

| BRW                   | _    | Relative Branch with W                        | 2      | 00            | 0000 | 0000 | 1011 |          |       |

| CALL                  | k    | Call Subroutine                               | 2      | 10            | 0kkk | kkkk | kkkk |          |       |

| CALLW                 | _    | Call Subroutine with W                        | 2      | 00            | 0000 | 0000 | 1010 |          |       |

| GOTO                  | k    | Go to address                                 | 2      | 10            | 1kkk | kkkk | kkkk |          |       |

| RETFIE                | k    | Return from interrupt                         | 2      | 00            | 0000 | 0000 | 1001 |          |       |

| RETLW                 | k    | Return with literal in W                      | 2      | 11            | 0100 | kkkk | kkkk |          |       |

| RETURN                | _    | Return from Subroutine                        | 2      | 00            | 0000 | 0000 | 1000 |          |       |

|                       |      | INHERENT OPERA                                | TIONS  |               |      |      |      | •        | •     |

| CLRWDT                | _    | Clear Watchdog Timer                          | 1      | 00            | 0000 | 0110 | 0100 | TO, PD   |       |

| NOP                   | -    | No Operation                                  | 1      | 00            | 0000 | 0000 | 0000 |          |       |

| OPTION                | _    | Load OPTION_REG register with W               | 1      | 00            | 0000 | 0110 | 0010 |          |       |

| RESET                 | -    | Software device Reset                         | 1      | 00            | 0000 | 0000 | 0001 |          |       |

| SLEEP                 | _    | Go into Standby mode                          | 1      | 00            | 0000 | 0110 | 0011 | TO, PD   |       |

| TRIS                  | f    | Load TRIS register with W                     | 1      | 00            | 0000 | 0110 | Offf |          |       |

|                       |      | C-COMPILER OPT                                | IMIZED |               |      |      |      | •        | •     |

| ADDFSR                | n, k | Add Literal k to FSRn                         | 1      | 11            | 0001 | 0nkk | kkkk |          |       |

| MOVIW                 | n mm | Move Indirect FSRn to W with pre/post inc/dec | 1      | 00            | 0000 | 0001 | 0nmm | Z        | 2, 3  |

|                       |      | modifier, mm                                  |        |               |      |      | kkkk |          |       |

|                       | k[n] | Move INDFn to W, Indexed Indirect.            | 1      | 11            | 1111 | 0nkk | 1nmm | Z        | 2     |

| MOVWI                 | n mm | Move W to Indirect FSRn with pre/post inc/dec | 1      | 00            | 0000 | 0001 | kkkk |          | 2, 3  |

|                       |      | modifier, mm                                  |        |               |      |      |      |          |       |

|                       | k[n] | Move W to INDFn, Indexed Indirect.            | 1      | 11            | 1111 | 1nkk |      |          | 2     |

#### TABLE 34-3: ENHANCED MID-RANGE INSTRUCTION SET (CONTINUED)

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

**3:** See Table in the MOVIW and MOVWI instruction descriptions.

| RETURN           | Return from Subroutine                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                                                                        |

| Operands:        | None                                                                                                                                                  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                  |

| Status Affected: | None                                                                                                                                                  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a 2-cycle instruction. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RRF f,d                                                                                                                                                                                                    |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                        |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                              |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                  |  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |  |  |  |  |  |

| <b>→</b> C <b>→</b> | Register f | <b></b> |

|---------------------|------------|---------|

|                     |            |         |

|                  |                                                                                                                                                |           | SLEEP            | Enter Sleep mode                                                                                                                                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RLF              | Rotate Left f through Car                                                                                                                      | ry        | Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                       |           | Operands:        | None                                                                                                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                |           | Operation:       | $00h \rightarrow WDT$ ,<br>$0 \rightarrow WDT$ prescaler,                                                                                                                                                                            |

| Operation:       | See description below                                                                                                                          |           |                  | $1 \rightarrow \overline{\overline{\text{TO}}},$                                                                                                                                                                                     |

| Status Affected: | С                                                                                                                                              |           |                  | $0 \rightarrow PD$                                                                                                                                                                                                                   |

| Description:     | The contents of register 'f' are                                                                                                               | e rotated | Status Affected: | TO, PD                                                                                                                                                                                                                               |

|                  | one bit to the left through the<br>flag. If 'd' is '0', the result is pl<br>the W register. If 'd' is '1', the<br>stored back in register 'f'. | aced in   | Description:     | The power-down Status bit, $\overline{PD}$ is<br>cleared. Time-out Status bit, $\overline{TO}$ is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into Sleep mode<br>with the oscillator stopped. |

| Words:           | 1                                                                                                                                              |           |                  |                                                                                                                                                                                                                                      |

| Cycles:          | 1                                                                                                                                              |           |                  |                                                                                                                                                                                                                                      |

| Example:         | RLF REG1,0                                                                                                                                     |           |                  |                                                                                                                                                                                                                                      |

|                  | Before Instruction                                                                                                                             |           |                  |                                                                                                                                                                                                                                      |

|                  | REG1 = 111<br>C = 0<br>After Instruction                                                                                                       | 0 0110    |                  |                                                                                                                                                                                                                                      |

|                  |                                                                                                                                                | 0 0110    |                  |                                                                                                                                                                                                                                      |

|                  |                                                                                                                                                | 0 1100    |                  |                                                                                                                                                                                                                                      |

|                  | C = 1                                                                                                                                          |           |                  |                                                                                                                                                                                                                                      |

## **38.0 PACKAGING INFORMATION**

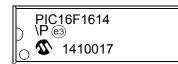

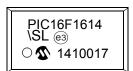

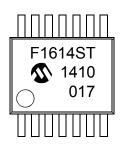

## 38.1 Package Marking Information

#### 14-Lead PDIP

14-Lead SOIC (.150")

14-Lead TSSOP

Example

Example

#### Example