Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

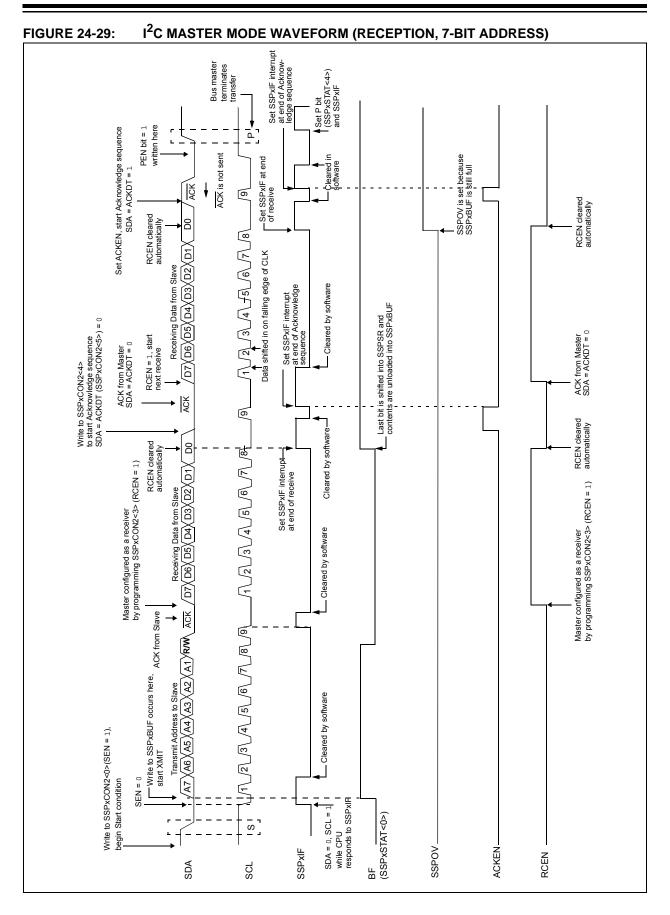

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1615-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 0/1 | 20-Pin PDIP, SOIC, SSOP                                                                                                                                                                                                                                                        | 20-Pin UQFN | A/D  | Reference | Comparator       | Timers                                      | ССР                 | CWG                   | ZCD    | CLC                   | EUSART              | SMT                    | Angular Timer       | MSSP                 | MWG | High Current I/O | Interrupt  | Bull-up | Basic       |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-----------|------------------|---------------------------------------------|---------------------|-----------------------|--------|-----------------------|---------------------|------------------------|---------------------|----------------------|-----|------------------|------------|---------|-------------|

| RA0 | 19                                                                                                                                                                                                                                                                             | 16          | AN0  | DAC10UT   | C1IN+            | _                                           |                     | _                     | _      | _                     |                     | —                      | _                   | —                    | _   | —                | IOC        | Y       | ICSPDAT     |

| RA1 | 18                                                                                                                                                                                                                                                                             | 15          | AN1  | VREF+     | C1IN0-<br>C2IN0- | _                                           |                     | —                     | —      | _                     |                     | —                      | _                   | —                    | —   | —                | IOC        | Y       | ICSPCLK     |

| RA2 | 17                                                                                                                                                                                                                                                                             | 14          | AN2  | -         |                  | T0CKI <sup>(1)</sup>                        |                     | CWG1IN <sup>(1)</sup> | ZCD1IN | _                     | -                   | _                      |                     | -                    | -   | -                | INT<br>IOC | Y       | —           |

| RA3 | 4                                                                                                                                                                                                                                                                              | 1           | _    | —         |                  | T6IN <sup>(1)</sup>                         |                     | —                     | _      | _                     | _                   | SMTWIN2 <sup>(1)</sup> | _                   | —                    | _   | _                | IOC        | Y       | MCLR<br>VPP |

| RA4 | 3                                                                                                                                                                                                                                                                              | 20          | AN3  | _         |                  | T1G <sup>(1)</sup>                          |                     | _                     | _      | _                     |                     | SMTSIG1(1)             | _                   | _                    | _   | _                | IOC        | Y       | CLKOUT      |

| RA5 | 2                                                                                                                                                                                                                                                                              | 19          | —    | _         |                  | T1CKI <sup>(1)</sup><br>T2IN <sup>(1)</sup> |                     | —                     | _      | CLCIN3 <sup>(1)</sup> | _                   | SMTWIN1 <sup>(1)</sup> | _                   | —                    | _   | —                | IOC        | Y       | CLKIN       |

| RB4 | 13                                                                                                                                                                                                                                                                             | 10          | AN10 | —         | _                | _                                           | _                   | _                     | _      | _                     | _                   | _                      | _                   | SDI(1)               | _   | _                | IOC        | Y       | —           |

| RB5 | 12                                                                                                                                                                                                                                                                             | 9           | AN11 | _         | -                | _                                           | _                   | —                     | _      | _                     | RX <sup>(1,3)</sup> | _                      |                     | _                    | _   | —                | IOC        | Y       | _           |

| RB6 | 11                                                                                                                                                                                                                                                                             | 8           | _    | _         | -                | _                                           | _                   | _                     | _      | _                     | -                   | _                      | _                   | SCK <sup>(1,3)</sup> | _   | -                | IOC        | Υ       | —           |

| RB7 | 10                                                                                                                                                                                                                                                                             | 7           |      | _         |                  | —                                           |                     | _                     | _      | —                     | CK <sup>(1)</sup>   | —                      | _                   | —                    | _   | —                | IOC        | Y       | —           |

| RC0 | 16                                                                                                                                                                                                                                                                             | 13          | AN4  | —         | C2IN+            | T5CKI <sup>(1)</sup>                        | —                   | _                     | _      | _                     | _                   | _                      | —                   | _                    | _   | _                | IOC        | Y       | —           |

| RC1 | 15                                                                                                                                                                                                                                                                             | 12          | AN5  | _         | C1IN1-<br>C2IN1- | T4IN <sup>(1)</sup>                         | _                   | —                     | -      | CLCIN2 <sup>(2)</sup> | _                   | SMTSIG2 <sup>(1)</sup> |                     | —                    | -   | -                | IOC        | Y       | -           |

| RC2 | 14                                                                                                                                                                                                                                                                             | 11          | AN6  | —         | C1IN2-<br>C2IN2- | _                                           | _                   | —                     | -      | -                     | _                   | —                      | —                   | —                    | -   | —                | IOC        | Y       | —           |

| RC3 | 7                                                                                                                                                                                                                                                                              | 4           | AN7  | —         | C1IN3-<br>C2IN3- | T5G <sup>(1)</sup>                          | CCP2 <sup>(1)</sup> | —                     | _      | CLCIN0 <sup>(1)</sup> | _                   | —                      | ATCC <sup>(1)</sup> | —                    | _   | —                | IOC        | Y       | -           |

| RC4 | 6                                                                                                                                                                                                                                                                              | 3           | _    | _         | _                | T3G <sup>(1)</sup>                          | _                   | _                     | —      | CLCIN1 <sup>(1)</sup> | _                   | _                      | _                   | _                    | —   | HIC4             | IOC        | Y       | —           |

| RC5 | 5                                                                                                                                                                                                                                                                              | 2           | _    | —         | _                | T3CKI <sup>(1)</sup>                        | CCP1 <sup>(1)</sup> | —                     | _      | —                     | _                   | —                      | ATIN <sup>(1)</sup> | —                    | _   | HIC5             | IOC        | Y       | _           |

| RC6 | 8                                                                                                                                                                                                                                                                              | 5           | AN8  | _         | _                | _                                           | _                   | _                     | _      | _                     | —                   | _                      | _                   | SS <sup>(1)</sup>    | _   | _                | IOC        | Y       | _           |

| RC7 | 9                                                                                                                                                                                                                                                                              | 6           | AN9  | _         |                  | _                                           |                     | _                     | _      | _                     |                     | _                      |                     | —                    | _   | _                | IOC        | Y       | _           |

| Vdd | 1                                                                                                                                                                                                                                                                              | 18          | _    | _         | _                | —                                           |                     | _                     | _      | _                     | _                   | _                      |                     | _                    | _   | _                | _          | _       | _           |

| Vss | 20                                                                                                                                                                                                                                                                             | 17          | _    | _         |                  | _                                           |                     | _                     | _      | _                     |                     | _                      |                     | —                    | _   | —                |            | _       | _           |

|     | <ol> <li>Default peripheral input. Input can be moved to any other pin with the PPS input selection registers.</li> <li>All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers.</li> </ol> |             |      |           |                  |                                             |                     |                       |        |                       |                     |                        |                     |                      |     |                  |            |         |             |

#### TABLE 4: 20-PIN ALLOCATION TABLE (PIC16(L)F1619)

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers.

These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections. 3:

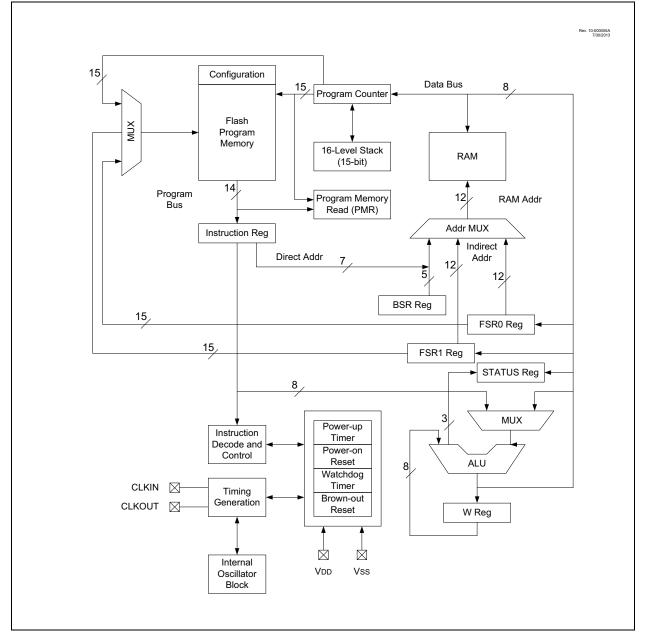

## 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative Addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- · 16-level Stack with Overflow and Underflow

- · File Select Registers

- Instruction Set

| IADLE | 3-14: SPE            |                       | IUN REGISI            | ER SUMIMA                 |           | UED)   |           |           |         |                      |                           |  |

|-------|----------------------|-----------------------|-----------------------|---------------------------|-----------|--------|-----------|-----------|---------|----------------------|---------------------------|--|

| Addr  | Name                 | Bit 7                 | Bit 6                 | Bit 5                     | Bit 4     | Bit 3  | Bit 2     | Bit 1     | Bit 0   | Value on<br>POR, BOR | Value on all other Resets |  |

| Bank  | 1                    |                       |                       |                           |           |        |           |           |         |                      |                           |  |

| 08Ch  | TRISA                |                       | _                     | TRISA5                    | TRISA4    | (2)    | TRISA2    | TRISA1    | TRISA0  | 11 1111              | 11 1111                   |  |

| 08Dh  | TRISB <sup>(4)</sup> | TRISB7                | TRISB6                | TRISB5                    | TRISB4    |        |           | _         | _       | 1111                 | 1111                      |  |

| 08Eh  | TRISC                | TRISC7 <sup>(4)</sup> | TRISC6 <sup>(4)</sup> | TRISC5                    | TRISC4    | TRISC3 | TRISC2    | TRISC1    | TRISC0  | 1111 1111            | 1111 1111                 |  |

| 08Fh  | —                    | Unimplemented         |                       |                           |           |        |           |           |         | —                    | —                         |  |

| 090h  | —                    | Unimplemented         |                       |                           |           |        |           |           |         | —                    | —                         |  |

| 090h  | PIE1                 | TMR1GIE               | ADIE                  | RCIE                      | TXIE      | SSP1IE | CCP1IE    | TMR2IE    | TMR1IE  | 0000 0000            | 0000 0000                 |  |

| 091h  | PIE2                 | OSFIE                 | C2IE                  | C1IE                      |           | BCL1IE | TMR6IE    | TMR4IE    | CCP2IE  | -00- 0000            | -00- 0000                 |  |

| 092h  | PIE3                 | —                     |                       | CWGIE                     | ZCDIE     | CLC4IE | CLC3IE    | CLC2IE    | CLC1IE  | 00 0000              | 00 0000                   |  |

| 093h  | PIE4                 | SCANIE                | CRCIE                 | SMT2PWAIE                 | SMT2PRAIE | SMT2IE | SMT1PWAIE | SMT1PRAIE | SMT1IE  | 0000 0000            | 0000 0000                 |  |

| 094h  | PIE5                 | TMR3GIE               | TMR3IE                | TMR5GIE                   | TMR5IE    |        | AT1IE     | PID1EIE   | PID1DIE | 0000 -000            | 0000 -000                 |  |

| 095h  | OPTION_REG           | WPUEN                 | INTEDG                | TMR0CS                    | TMR0SE    | PSA    |           | PS<2:0>   | _       | 1111 1111            | 1111 1111                 |  |

| 096h  | PCON                 | STKOVF                | STKUNF                | WDTWV                     | RWDT      | RMCLR  | RI        | POR       | BOR     | 00-1 11qq            | qq-q qquu                 |  |

| 097h  | —                    | Unimplemented         |                       |                           |           |        |           |           |         | —                    | —                         |  |

| 098h  | OSCTUNE              | _                     |                       |                           |           | TUN    | <5:0>     | _         |         | 00 0000              | 00 0000                   |  |

| 099h  | OSCCON               | SPLLEN                |                       | IRCF                      | <3:0>     |        | —         | SCS       | <1:0>   | 0011 1-00            | 0011 1-00                 |  |

| 09Ah  | OSCSTAT              | —                     | PLLR                  | OSTS                      | HFIOFR    | HFIOFL | MFIOFR    | LFIOFR    | HFIOFS  | -000 0000            | -वेर्वेते वेर्वेतेत       |  |

| 09Bh  | ADRESL               | ADC Result Re         | gister Low            | ster Low                  |           |        |           |           |         |                      | uuuu uuuu                 |  |

| 09Ch  | ADRESH               | ADC Result Re         | ster High             |                           |           |        |           |           |         | XXXX XXXX            | uuuu uuuu                 |  |

| 09Dh  | ADCON0               | —                     | CHS<4:0> GO/DONE ADON |                           |           |        |           |           |         | -000 0000            | -000 0000                 |  |

| 09Eh  | ADCON1               | ADFM                  |                       | ADCS<2:0> — — ADPREF<1:0> |           |        |           |           |         |                      | 000000                    |  |

| 09Fh  | ADCON2               |                       |                       | TRIGSEL<4:0> — — —        |           |        |           |           |         |                      |                           |  |

### TABLE 3-14: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** PIC16F1615/9 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1615 only.

4: PIC16(L)F1619 only.

|                    | 3-14. 3FE      |               |          |          |          |                | 1        | 1            |          |                      |                           |

|--------------------|----------------|---------------|----------|----------|----------|----------------|----------|--------------|----------|----------------------|---------------------------|

| Addr               | Name           | Bit 7         | Bit 6    | Bit 5    | Bit 4    | Bit 3          | Bit 2    | Bit 1        | Bit 0    | Value on<br>POR, BOR | Value on all other Resets |

| Banks              | 30 (Continued) |               |          |          |          |                |          |              |          |                      |                           |

| F24h               | CLC3CON        | LC3EN         | —        | LC3OUT   | LC3INTP  | <b>LC3INTN</b> |          | LC3MODE<2:0> | •        | 0-x0 0000            | 0-x0 0000                 |

| F25h               | CLC3POL        | LC3POL        | —        | _        |          | LC3G4POL       | LC3G3POL | LC3G2POL     | LC3G1POL | x xxxx               | x xxxx                    |

| F26h               | CLC3SEL0       | —             | -        |          |          | LC3D1          | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F27h               | CLC3SEL1       | —             |          |          |          | LC3D2          | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F28h               | CLC3SEL2       | —             |          |          |          | LC3D3          | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F29h               | CLC3SEL3       | —             | _        |          |          | LC3D4          | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F2Ah               | CLC3GLS0       | LC3G1D4T      | LC3G1D4N | LC3G1D3T | LC3G1D3N | LC3G1D2T       | LC3G1D2N | LC3G1D1T     | LC3G1D1N | xxxx xxxx            | XXXX XXXX                 |

| F2Bh               | CLC3GLS1       | LC3G2D4T      | LC3G2D4N | LC3G2D3T | LC3G2D3N | LC3G2D2T       | LC3G2D2N | LC3G2D1T     | LC3G2D1N | xxxx xxxx            | xxxx xxxx                 |

| F2Ch               | CLC3GLS2       | LC3G3D4T      | LC3G3D4N | LC3G3D3T | LC3G3D3N | LC3G3D2T       | LC3G3D2N | LC3G3D1T     | LC3G3D1N | xxxx xxxx            | xxxx xxxx                 |

| F2Dh               | CLC3GLS3       | LC3G4D4T      | LC3G4D4N | LC3G4D3T | LC3G4D3N | LC3G4D2T       | LC3G4D2N | LC3G4D1T     | LC3G4D1N | xxxx xxxx            | xxxx xxxx                 |

| F2Eh               | CLC4CON        | LC4EN         |          | LC4OUT   | LC4INTP  | LC4INTN        |          | LC4MODE<2:0> | •        | 0-x0 0000            | 0-x0 0000                 |

| F2Fh               | CLC4POL        | LC4POL        | _        | _        | _        | LC4G4POL       | LC4G3POL | LC4G2POL     | LC4G1POL | x xxxx               | x xxxx                    |

| F30h               | CLC4SEL0       | —             |          |          |          | LC4D1          | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F31h               | CLC4SEL1       | —             | _        |          |          | LC4D2          | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F32h               | CLC4SEL2       | —             | _        |          |          | LC4D3          | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F33h               | CLC4SEL3       | —             | _        |          |          | LC4D4          | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F34h               | CLC4GLS0       | LC4G1D4T      | LC4G1D4N | LC4G1D3T | LC4G1D3N | LC4G1D2T       | LC4G1D2N | LC4G1D1T     | LC4G1D1N | xxxx xxxx            | xxxx xxxx                 |

| F35h               | CLC4GLS1       | LC4G2D4T      | LC4G2D4N | LC4G2D3T | LC4G2D3N | LC4G2D2T       | LC4G2D2N | LC4G2D1T     | LC4G2D1N | xxxx xxxx            | xxxx xxxx                 |

| F36h               | CLC4GLS2       | LC4G3D4T      | LC4G3D4N | LC4G3D3T | LC4G3D3N | LC4G3D2T       | LC4G3D2N | LC4G3D1T     | LC4G3D1N | xxxx xxxx            | xxxx xxxx                 |

| F37h               | CLC4GLS3       | LC4G4D4T      | LC4G4D4N | LC4G4D3T | LC4G4D3N | LC4G4D2T       | LC4G4D2N | LC4G4D1T     | LC4G4D1N | xxxx xxxx            | xxxx xxxx                 |

| F38h<br>to<br>F6Fh | _              | Unimplemented |          |          |          |                |          |              |          |                      |                           |

### TABLE 3-14: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** PIC16F1615/9 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1615 only.

4: PIC16(L)F1619 only.

#### **REGISTER 4-3: CONFIG3: CONFIGURATION WORD 3**

|       |       | R/P-0  | R/P-0       | R/P-1 | R/P-1      | R/P-1      | R/P-1 |

|-------|-------|--------|-------------|-------|------------|------------|-------|

|       |       |        | WDTCCS<2:0> | >     | , v        | WDTCWS<2:0 | >     |

|       |       | bit 13 |             |       |            |            | bit 8 |

| U-1   | R/P-1 | R/P-1  | R/P-1       | R/P-1 | R/P-1      | R/P-1      | R/P-1 |

| _     |       | E<1:0> |             |       | WDTCPS<4:0 |            |       |

| bit 7 | -     |        | •           |       |            |            | bit 0 |

|       |       |        |             |       |            |            |       |

| Leaend: |  |

|---------|--|

| Leyenu. |  |

bit 6-5

| Legend:              |                      |                                           |

|----------------------|----------------------|-------------------------------------------|

| R = Readable bit     | P = Programmable bit | U = Unimplemented bit, read as '1'        |

| '0' = Bit is cleared | '1' = Bit is set     | -n = Value when blank or after Bulk Erase |

WDTCCS<2:0>: WDT Configuration Clock Select bits bit 13-11

- 111 =Software Control; WDT clock selected by CS<2:0> 110 =Reserved

- 010 =Reserved

- 001 =WDT reference clock is MFINTOSC, 31.25 kHz (default value)

- 000 =WDT reference clock is LFINTOSC, 31.00 kHz output

WDTCWS<2:0>: WDT Configuration Window Select bits. bit 10-8

| WDTCWS |       | WINDOW at P                     | OR                                | Software              | Keyed               |                    |

|--------|-------|---------------------------------|-----------------------------------|-----------------------|---------------------|--------------------|

| <2:0>  | Value | Window delay<br>Percent of time | Window opening<br>Percent of time | control of<br>WINDOW? | access<br>required? |                    |

| 111    | 111   | n/a                             | 100                               | Yes                   | No                  | Default fuse = 111 |

| 110    | 111   | n/a                             | 100                               |                       |                     |                    |

| 101    | 101   | 25                              | 75                                |                       |                     |                    |

| 100    | 100   | 37.5                            | 62.5                              |                       |                     |                    |

| 011    | 011   | 50                              | 50                                | No                    | Yes                 |                    |

| 010    | 010   | 62.5                            | 37.5                              |                       |                     |                    |

| 001    | 001   | 75                              | 25                                |                       |                     |                    |

| 000    | 000   | 87.5                            | 12.5 <sup>(1)</sup>               |                       |                     |                    |

bit 7 Unimplemented: Read as '1'

WDTE<1:0>: Watchdog Timer Enable bits

11 =WDT enabled in all modes, the SEN bit in the WDTCON0 register is ignored

10 =WDT enabled while running and disabled in Sleep

01 =WDT controlled by the SEN bit in the WDTCON0 register

00 = WDT disabled

| U-0            | U-0               | R/W-0/0           | R/W-0/0       | R/W-0/0           | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|----------------|-------------------|-------------------|---------------|-------------------|------------------|----------------|--------------|

|                | _                 |                   |               | TUN               | <5:0>            |                |              |

| bit 7          |                   |                   |               |                   |                  |                | bit 0        |

|                |                   |                   |               |                   |                  |                |              |

| Legend:        |                   |                   |               |                   |                  |                |              |

| R = Readal     | ole bit           | W = Writable      | bit           | U = Unimplen      | nented bit, read | d as '0'       |              |

| u = Bit is ur  | nchanged          | x = Bit is unkr   | nown          | -n/n = Value a    | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is s | et                | '0' = Bit is clea | ared          |                   |                  |                |              |

|                |                   |                   |               |                   |                  |                |              |

| bit 7-6        | Unimpleme         | ented: Read as '  | 0'            |                   |                  |                |              |

| bit 5-0        | TUN<5:0>:         | Frequency Tunir   | ng bits       |                   |                  |                |              |

|                | 100000 <b>= N</b> | Ainimum frequen   | су            |                   |                  |                |              |

|                | •                 |                   |               |                   |                  |                |              |

|                | •                 |                   |               |                   |                  |                |              |

|                | 111111 =          |                   |               |                   |                  |                |              |

|                |                   | Oscillator module | is running at | the factory-calib | prated frequend  | cy.            |              |

|                | 000001 =          |                   |               |                   |                  |                |              |

|                | •                 |                   |               |                   |                  |                |              |

|                | •                 |                   |               |                   |                  |                |              |

|                | •<br>011110 =     |                   |               |                   |                  |                |              |

|                |                   | Maximum frequer   |               |                   |                  |                |              |

### REGISTER 5-3: OSCTUNE: OSCILLATOR TUNING REGISTER

### TABLE 5-3: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7  | Bit 6 | Bit 5 | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|--------|-------|-------|----------|--------|--------|--------|--------|---------------------|

| OSCCON  | SPLLEN |       | IRCF  | <3:0>    |        | _      | SCS    | <1:0>  | 89                  |

| OSCSTAT | _      | PLLR  | OSTS  | HFIOFR   | HFIOFL | MFIOFR | LFIOFR | HFIOFS | 90                  |

| OSCTUNE |        | _     |       | TUN<5:0> |        |        |        |        |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

### TABLE 5-4: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1  | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|----------|---------|---------------------|

| CONFIG1 | 13:8 | _       |         | FCMEN    | IESO     | CLKOUTEN | BORE     | N<1:0>   |         | 69                  |

| CONFIGI | 7:0  | CP      | MCLRE   | PWRTE    | _        |          | F        | OSC<2:0> | •       | 09                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

# PIC16(L)F1615/9

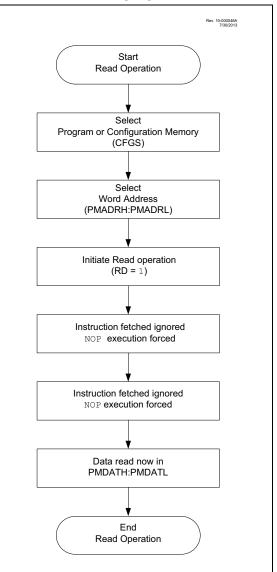

# 10.2.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the desired address to the PMADRH:PMADRL register pair.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Then, set control bit RD of the PMCON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF PMCON1, RD" instruction to be ignored. The data is available in the very next cycle, in the PMDATH:PMDATL register pair; therefore, it can be read as two bytes in the following instructions.

PMDATH:PMDATL register pair will hold this value until another read or until it is written to by the user.

| Note: | The two instructions following a program   |

|-------|--------------------------------------------|

|       | memory read are required to be NOPS.       |

|       | This prevents the user from executing a 2- |

|       | cycle instruction on the next instruction  |

|       | after the RD bit is set.                   |

### FIGURE 10-1:

### FLASH PROGRAM MEMORY READ FLOWCHART

### 10.6 Register Definitions: Flash Program Memory Control

### REGISTER 10-1: PMDATL: PROGRAM MEMORY DATA LOW BYTE REGISTER

| R/W-x/u              | R/W-x/u | R/W-x/u              | R/W-x/u | R/W-x/u           | R/W-x/u              | R/W-x/u             | R/W-x/u |

|----------------------|---------|----------------------|---------|-------------------|----------------------|---------------------|---------|

|                      |         |                      | PMDA    | T<7:0>            |                      |                     |         |

| bit 7                |         |                      |         |                   |                      |                     | bit 0   |

|                      |         |                      |         |                   |                      |                     |         |

| Legend:              |         |                      |         |                   |                      |                     |         |

| R = Readable bit     |         | W = Writable bit     |         | U = Unimpleme     | nted bit, read as '0 | ,                   |         |

| u = Bit is unchanged |         | x = Bit is unknown   |         | -n/n = Value at F | POR and BOR/Valu     | ue at all other Res | ets     |

| '1' = Bit is set     |         | '0' = Bit is cleared |         |                   |                      |                     |         |

bit 7-0

PMDAT<7:0>: Read/write value for Least Significant bits of program memory

### REGISTER 10-2: PMDATH: PROGRAM MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u  | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|----------|---------|---------|

| _     | —   |         |         | PMDA    | AT<13:8> |         |         |

| bit 7 |     |         |         |         |          |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 PMDAT<13:8>: Read/write value for Most Significant bits of program memory

### REGISTER 10-3: PMADRL: PROGRAM MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-----------|---------|---------|---------|---------|---------|---------|---------|

|           |         |         | PMAD    | R<7:0>  |         |         |         |

| bit 7 bit |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PMADR<7:0>**: Specifies the Least Significant bits for program memory address

### REGISTER 10-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-------------|---------|---------|---------|

| (1)   |         |         |         | PMADR<14:8> |         |         |         |

| bit 7 |         |         |         |             |         |         | bit 0   |

## Legend:

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 PMADR<14:8>: Specifies the Most Significant bits for program memory address

Note 1: Unimplemented, read as '1'.

### TABLE 13-3: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE (CONTINUED)

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4       | Bit 3       | Bit 2    | Bit 1 | Bit 0 | Register<br>on page |

|-----------------------|-------|-------|-------|-------------|-------------|----------|-------|-------|---------------------|

| RC1PPS                | —     | —     | _     |             | RC1PPS<4:0> |          |       |       | 180                 |

| RC2PPS                | —     | —     | _     |             | RC2PPS<4:0> |          |       |       | 180                 |

| RC3PPS                | —     | —     | _     |             | RC3PPS<4:0> |          |       |       | 180                 |

| RC4PPS                | —     | —     | _     |             |             | RC4PPS<4 | :0>   |       | 180                 |

| RC5PPS                | —     | —     | _     |             | RC5PPS<4:0> |          |       |       | 180                 |

| RC6PPS <sup>(1)</sup> | —     | —     | _     | RC6PPS<4:0> |             |          |       | 180   |                     |

| RC7PPS <sup>(1)</sup> | —     | _     | _     | RC7PPS<4:0> |             |          |       | 180   |                     |

Note 1: PIC16(L)F1619 only.

| R/W-x/u        | R/W-x/u                         | R/W-x/u | R/W-x/u | R/W-x/u      | R/W-x/u          | R/W-x/u  | R/W-x/u |

|----------------|---------------------------------|---------|---------|--------------|------------------|----------|---------|

| —              | _                               |         | _       | _            | —                | ADRE     | S<9:8>  |

| bit 7          |                                 |         | •       |              | •                |          | bit 0   |

|                |                                 |         |         |              |                  |          |         |

| Legend:        |                                 |         |         |              |                  |          |         |

| R = Readable b | = Readable bit W = Writable bit |         |         | U = Unimpler | nented bit, read | l as '0' |         |

### REGISTER 17-6: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7-2 Reserved: Do not use.

bit 1-0 **ADRES<9:8>**: ADC Result Register bits Upper two bits of 10-bit conversion result

### REGISTER 17-7: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|------------|---------|---------|---------|---------|---------|---------|

|         | ADRES<7:0> |         |         |         |         |         |         |

| bit 7 b |            |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower eight bits of 10-bit conversion result

PIC16(L)F1615/9

| R/W-0/0          | R/W-0/0                                                                                                                                                         | R/W-0/0                                   | R/W-0/0   | R/W-0/0                                               | R/W-0/0             | R/W-0/0             | R/W-0/0             |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------|-------------------------------------------------------|---------------------|---------------------|---------------------|--|--|--|--|

| OVRD             | OVRC                                                                                                                                                            | OVRB                                      | OVRA      | STRD <sup>(2)</sup>                                   | STRC <sup>(2)</sup> | STRB <sup>(2)</sup> | STRA <sup>(2)</sup> |  |  |  |  |

| bit 7            | •                                                                                                                                                               |                                           | •<br>     |                                                       |                     | •                   | bit 0               |  |  |  |  |

| Legend:          |                                                                                                                                                                 |                                           |           |                                                       |                     |                     |                     |  |  |  |  |

| R = Readable     | bit                                                                                                                                                             | W = Writable                              | bit       | U = Unimplemented bit, read as '0'                    |                     |                     |                     |  |  |  |  |

| u = Bit is unch  | anged                                                                                                                                                           | x = Bit is unki                           | nown      | -n/n = Value at POR and BOR/Value at all other Resets |                     |                     |                     |  |  |  |  |

| '1' = Bit is set | '0' = Bit is cle                                                                                                                                                | is cleared q = Value depends on condition |           |                                                       |                     |                     |                     |  |  |  |  |

|                  |                                                                                                                                                                 |                                           |           |                                                       |                     |                     |                     |  |  |  |  |

| bit 7            | OVRD: Steer                                                                                                                                                     | ing Data D bit                            |           |                                                       |                     |                     |                     |  |  |  |  |

| bit 6            | OVRC: Steering Data C bit                                                                                                                                       |                                           |           |                                                       |                     |                     |                     |  |  |  |  |

| bit 5            | OVRB: Steering Data B bit                                                                                                                                       |                                           |           |                                                       |                     |                     |                     |  |  |  |  |

| bit 4            | OVRA: Steering Data A bit                                                                                                                                       |                                           |           |                                                       |                     |                     |                     |  |  |  |  |

| bit 3            | STRD: Steering Enable D bit <sup>(2)</sup>                                                                                                                      |                                           |           |                                                       |                     |                     |                     |  |  |  |  |

|                  | <ul> <li>1 = CWGxD output has the CWGx_data waveform with polarity control from POLD bit</li> <li>0 = CWGxD output is assigned the value of OVRD bit</li> </ul> |                                           |           |                                                       |                     |                     |                     |  |  |  |  |

| bit 2            | STRC: Steering Enable C bit <sup>(2)</sup>                                                                                                                      |                                           |           |                                                       |                     |                     |                     |  |  |  |  |

|                  | <ul> <li>1 = CWGxC output has the CWGx_data waveform with polarity control from POLC bit</li> <li>0 = CWGxC output is assigned the value of OVRC bit</li> </ul> |                                           |           |                                                       |                     |                     |                     |  |  |  |  |

| bit 1            |                                                                                                                                                                 | ng Enable B bi                            |           |                                                       |                     |                     |                     |  |  |  |  |

|                  | 1 = CWGxB                                                                                                                                                       | •                                         | CWGx_data |                                                       | polarity control    | from POLB bit       |                     |  |  |  |  |

| bit 0            | STRA: Steering Enable A bit <sup>(2)</sup>                                                                                                                      |                                           |           |                                                       |                     |                     |                     |  |  |  |  |

|                  | <ul> <li>1 = CWGxA output has the CWGx_data waveform with polarity control from POLA bit</li> <li>0 = CWGxA output is assigned the value of OVRA bit</li> </ul> |                                           |           |                                                       |                     |                     |                     |  |  |  |  |

## REGISTER 28-7: CWGxOCON0: CWGx STEERING CONTROL REGISTER<sup>(1)</sup>

Note 1: The bits in this register apply only when MODE<2:0> = 00x.

2: This bit is effectively double-buffered when MODE<2:0> = 001.

### 30.6.8 CAPTURE MODE

This mode captures the Timer value based on a rising or falling edge on the SMTWINx input and triggers an interrupt. This mimics the capture feature of a CCP module. The timer begins incrementing upon the SMTxGO bit being set, and updates the value of the SMTxCPR register on each rising edge of SMTWINx, and updates the value of the CPW register on each falling edge of the SMTWINx. The timer is not reset by any hardware conditions in this mode and must be reset by software, if desired. See Figure 30-16 and Figure 30-17.

| U-0                               | U-0                      | U-0                              | R/W-0/0     | R/W-0/0                            | R/W-0/0        | R/W-0/0        | R/W-0/0      |  |  |  |

|-----------------------------------|--------------------------|----------------------------------|-------------|------------------------------------|----------------|----------------|--------------|--|--|--|

| _                                 | _                        |                                  |             |                                    | SSEL<4:0>      |                |              |  |  |  |

| bit 7                             | ·                        |                                  |             |                                    |                |                | bit          |  |  |  |

|                                   |                          |                                  |             |                                    |                |                |              |  |  |  |

| Legend:                           |                          |                                  |             |                                    |                |                |              |  |  |  |

| R = Readable bit W = Writable bit |                          |                                  | bit         | U = Unimplemented bit, read as '0' |                |                |              |  |  |  |

| u = Bit is unchanged              |                          | x = Bit is unknown               |             | -n/n = Value a                     | at POR and BC  | R/Value at all | other Resets |  |  |  |

| '1' = Bit is set                  |                          | '0' = Bit is cleared             |             | q = Value dep                      | pends on condi | tion           |              |  |  |  |

| bit 7-5                           | Unimpleme                | nted: Read as                    | <b>'</b> ∩' |                                    |                |                |              |  |  |  |

| bit 4-0                           | -                        | SMT2 Signal S                    |             |                                    |                |                |              |  |  |  |

|                                   | 111111 = Re              | -                                |             |                                    |                |                |              |  |  |  |

|                                   | •                        |                                  |             |                                    |                |                |              |  |  |  |

|                                   | •                        |                                  |             |                                    |                |                |              |  |  |  |

|                                   | •<br>10101 <b>= Re</b>   | served                           |             |                                    |                |                |              |  |  |  |

|                                   | 10100 = PV               |                                  |             |                                    |                |                |              |  |  |  |

|                                   | 10011 = PV               |                                  |             |                                    |                |                |              |  |  |  |

|                                   | 10010 = CC               |                                  |             |                                    |                |                |              |  |  |  |

|                                   | 10001 = CC               | IR0 overflow                     |             |                                    |                |                |              |  |  |  |

|                                   | 01111 <b>= Re</b>        |                                  |             |                                    |                |                |              |  |  |  |

|                                   | 01110 <b>= SN</b>        |                                  |             |                                    |                |                |              |  |  |  |

|                                   |                          | IR5_overflow                     |             |                                    |                |                |              |  |  |  |

|                                   |                          | IR3_overflow<br>IR1_overflow     |             |                                    |                |                |              |  |  |  |

|                                   | 01011 = 10<br>01010 = LC |                                  |             |                                    |                |                |              |  |  |  |

|                                   | 01001 = LC               |                                  |             |                                    |                |                |              |  |  |  |

|                                   | 01000 = LC               |                                  |             |                                    |                |                |              |  |  |  |

|                                   | 00111 = LC               |                                  |             |                                    |                |                |              |  |  |  |

|                                   |                          | IR6_postscaled<br>IR4_postscaled |             |                                    |                |                |              |  |  |  |

|                                   |                          | IR2 postscaled                   |             |                                    |                |                |              |  |  |  |

|                                   | 00011 <b>= ZC</b>        |                                  |             |                                    |                |                |              |  |  |  |

|                                   | 00010 <b>= C2</b>        |                                  |             |                                    |                |                |              |  |  |  |

|                                   | 00001 = C1               |                                  |             |                                    |                |                |              |  |  |  |

|                                   | 00000 = SN               | n xõig pin                       |             |                                    |                |                |              |  |  |  |

### REGISTER 30-8: SMT2SIG: SMT2 SIGNAL INPUT SELECT REGISTER

### 31.2.3 MISSING PULSE DETECTION

In both Single-Pulse and Multi-Pulse modes, the AT module monitors for missing pulses in the following manner. The latched value of the ATxPER register pair is continuously subtracted from the value of the period counter as it counts up. The result of this subtraction is compared to a third value and a missing pulse event is generated when the comparison is equal.

The third value is either the ATxMISS register pair or the ATxPER register pair divided by two. The APMOD bit of ATxCON0 register (Register 31-1) selects which of these two values is used.

In Single-Pulse mode, a missing pulse event generates the missing pulse output of the module as well as triggering the MISSIF interrupt.

In Multi-Pulse mode, a missing pulse event generates the output and interrupt, and is also used to determine the period signal timing.

### 31.2.4 MISSING PULSE MODES

Missing pulse detection has two modes of operation selected with the APMOD bit of the ATxCON0 register:

- Adaptive

- Fixed

### 31.2.4.1 Adaptive Missing Pulse Mode

When APMOD = 1, the missing pulse detection is in the Adaptive mode. In Adaptive mode, the difference between the period counter and the latched ATxPER value is compared to the latched ATxPER value divided by two. A missing pulse event will occur when an input signal pulse is not detected within 1.5 times the previous time between pulses. If the signal input period changes, the missing pulse comparison adapts to the change to maintain the relative time to the missing pulse event at 1.5 times the previous pulse interval.

### 31.2.4.2 Fixed Missing Pulse Mode

When APMOD = 0, the missing pulse detection is in the Fixed mode. In Fixed mode, the difference between the period counter and the latched ATxPER value is compared to the value in the ATxMISS register pair. This gives the user absolute control over when the missing pulse will be detected, with the trade-off of not being adaptive to changes in the period.

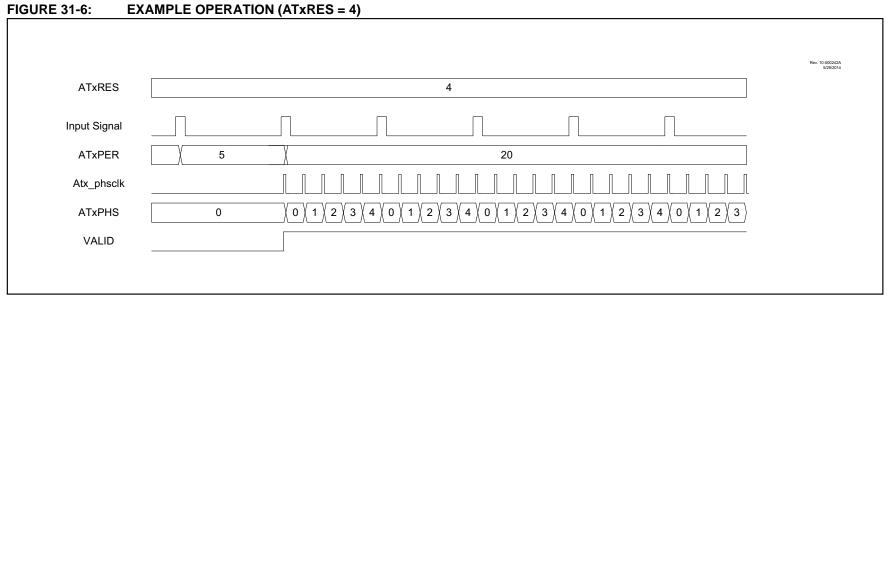

# FIGURE 31-6:

### 32.0 MATH ACCELERATOR WITH PROPORTIONAL-INTEGRAL-DERIVATIVE (PID) MODULE

The math accelerator module is a mathematics module that can perform a variety of operations, most prominently acting as a PID (Proportional-Integral-Derivative) controller. A PID controller is an algorithm that uses the present error (proportional), the sum of the present and all previous errors (integral), and the difference between the present and previous change (derivative) to correct errors and provide stability in a system. It provides feedback to a system through a series of iterations, using the present error as well as previous errors to calculate a new input to the controller. The data flow for both PID modes is illustrated in Figure 32-1.

The module accomplishes the task of calculating the PID algorithm by utilizing user-provided coefficients along with a multiplier and accumulator. As such, this multiplier and accumulator can also be configured to quickly and efficiently perform signed and unsigned multiply-and-add calculations both with and without accumulation. The data flow for these modes is illustrated in Figure 32-2.

Features of this module include:

- · Signed multiplier

- 35-bit signed accumulator

- PID controller support with user inputs for K1, K2, K3, system error and desired set point

- · Completion and Error interrupts

- Multiple user modes allowing for PID with or without accumulation as well as several multiplication operations

### 32.1 PID Module Setup Summary

The PID module can be configured either as a PID controller or as a multiply and accumulate module. Multiply and accumulate can be performed in four modes:

- Unsigned multiply and add, without accumulation

- Unsigned multiply and accumulate

- · Signed multiply and add, without accumulation

- · Signed multiply and accumulate

All of the modes are selected by the MODE<2:0> bits of the PIDxCON register.

# 32.1.1 PID MODE SETUP AND OPERATION

When the MODE<2:0> bits of the PIDxCON register are equal to '101', the module is in PID controller mode. The operation of the module in PID controller mode is generally performed as a loop. The input from an external system is fed into the controller, and the controller's output is fed back into the external system. This will produce a new response from the system that is then looped back into the PID controller. The data flow for the PID operation is illustrated in Figure 32-1.

| Mnemonic,<br>Operands                  |              | <b>B</b> 1.44                              |               | 14-Bit Opcode |      |      |      | Status   |       |

|----------------------------------------|--------------|--------------------------------------------|---------------|---------------|------|------|------|----------|-------|

|                                        |              | Description                                | Cycles        | MSb           |      |      | LSb  | Affected | Notes |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |              |                                            |               |               |      |      |      |          |       |

| ADDWF                                  | f, d         | Add W and f                                | 1             | 00            | 0111 | dfff | ffff | C, DC, Z | 2     |

| ADDWFC                                 | f, d         | Add with Carry W and f                     | 1             | 11            | 1101 | dfff | ffff | C, DC, Z | 2     |

| ANDWF                                  | f, d         | AND W with f                               | 1             | 00            | 0101 | dfff | ffff | Z        | 2     |

| ASRF                                   | f, d         | Arithmetic Right Shift                     | 1             | 11            | 0111 | dfff | ffff | C, Z     | 2     |

| LSLF                                   | f, d         | Logical Left Shift                         | 1             | 11            | 0101 | dfff | ffff | C, Z     | 2     |

| LSRF                                   | f, d         | Logical Right Shift                        | 1             | 11            | 0110 | dfff | ffff | C, Z     | 2     |

| CLRF                                   | f            | Clear f                                    | 1             | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW                                   | _            | Clear W                                    | 1             | 00            |      | 0000 |      | Z        |       |

| COMF                                   | f, d         | Complement f                               | 1             | 00            | 1001 | dfff | ffff | z        | 2     |

| DECF                                   | f, d         | Decrement f                                | 1             | 00            |      | dfff |      | z        | 2     |

| INCF                                   | f, d         | Increment f                                | 1             | 00            |      | dfff |      |          | 2     |

| IORWF                                  | f, d         | Inclusive OR W with f                      | 1             | 00            | 0100 | dfff |      |          | 2     |

| MOVF                                   | f, d         | Move f                                     | 1             | 00            |      | dfff |      |          | 2     |

| MOVWF                                  | f.           | Move W to f                                | 1             | 00            |      | 1fff |      | -        | 2     |

| RLF                                    | f, d         | Rotate Left f through Carry                | 1             | 00            |      | dfff |      | с        | 2     |

| RRF                                    | f, d         | Rotate Right f through Carry               | 1             | 00            |      | dfff |      | c        | 2     |

| SUBWF                                  | f, d         | Subtract W from f                          | 1             | 00            |      | dfff |      | -        | 2     |

| SUBWFB                                 | f, d         | Subtract with Borrow W from f              | 1             | 11            |      | dfff |      |          | 2     |

|                                        | '            |                                            | 1             |               |      |      |      | C, DC, Z | 2     |

| SWAPF<br>XORWF                         | f, d<br>f, d | Swap nibbles in f<br>Exclusive OR W with f | 1             | 00            | 1110 | dfff |      | z        | 2     |

| AURWE                                  | 1, U         | BYTE ORIENTED                              |               |               | 0110 | dfff | LLLL | 2        | Z     |

|                                        | fd           |                                            | 1             |               | 1011 | dfff | ffff |          | 1 0   |

| DECFSZ                                 | f, d         | Decrement f, Skip if 0                     | 1(2)          | 00            | 1011 |      |      |          | 1, 2  |

| INCFSZ                                 | f, d         | Increment f, Skip if 0                     | 1(2)          | 00            | 1111 | dfff | ffff |          | 1, 2  |

|                                        |              | BIT-ORIENTED FILE R                        | EGISTER OPER  | RATIO         | NS   |      |      | -        |       |

| BCF                                    | f, b         | Bit Clear f                                | 1             | 01            | 00bb | bfff | ffff |          | 2     |

| BSF                                    | f, b         | Bit Set f                                  | 1             | 01            | 01bb | bfff | ffff |          | 2     |

|                                        |              | BIT-ORIENTED S                             | SKIP OPERATIO | NS            |      |      |      | •        |       |

| BTFSC                                  | f, b         | Bit Test f, Skip if Clear                  | 1 (2)         | 01            | 10bb | bfff | ffff |          | 1, 2  |

| BTFSS                                  | f, b         | Bit Test f, Skip if Set                    | 1 (2)         | 01            | 11bb | bfff | ffff |          | 1, 2  |

|                                        |              | 1                                          | PERATIONS     | 1             |      |      |      |          | 1     |

| ADDLW                                  | k            | Add literal and W                          | 1             | 11            | 1110 | kkkk |      | C, DC, Z |       |

| ANDLW                                  | k            | AND literal with W                         | 1             | 11            |      | kkkk |      | Z        |       |

| IORLW                                  | k            | Inclusive OR literal with W                | 1             | 11            |      | kkkk |      | Z        |       |

| MOVLB                                  | k            | Move literal to BSR                        | 1             | 00            | 0000 | 001k |      |          |       |

| MOVLP                                  | k            | Move literal to PCLATH                     | 1             | 11            | 0001 | 1kkk |      |          |       |

| MOVLW                                  | k            | Move literal to W                          | 1             | 11            | 0000 | kkkk |      |          |       |

| SUBLW                                  | k            | Subtract W from literal                    | 1             | 11            | 1100 | kkkk | kkkk | C, DC, Z |       |

| XORLW                                  | k            | Exclusive OR literal with W                | 1             | 11            | 1010 | kkkk | kkkk | Z        |       |

### TABLE 34-3: ENHANCED MID-RANGE INSTRUCTION SET

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

### TABLE 35-6: THERMAL CHARACTERISTICS

| Standard Operating Conditions (unless otherwise stated) |           |                                        |      |       |                                                          |  |  |  |

|---------------------------------------------------------|-----------|----------------------------------------|------|-------|----------------------------------------------------------|--|--|--|

| Param.<br>No.                                           | Sym.      | Characteristic                         | Тур. | Units | Conditions                                               |  |  |  |

| TH01                                                    | θJA       | Thermal Resistance Junction to Ambient | 62.2 | °C/W  | 20-pin DIP package                                       |  |  |  |

|                                                         |           |                                        | 77.7 | °C/W  | 20-pin SOIC package                                      |  |  |  |

|                                                         |           |                                        | 87.3 | °C/W  | 20-pin SSOP package                                      |  |  |  |

|                                                         |           |                                        | 43   | °C/W  | 20-pin QFN 4X4mm package                                 |  |  |  |

| TH02                                                    | θJC       | Thermal Resistance Junction to Case    | 27.5 | °C/W  | 20-pin DIP package                                       |  |  |  |

|                                                         |           |                                        | 23.1 | °C/W  | 20-pin SOIC package                                      |  |  |  |

|                                                         |           |                                        | 31.1 | °C/W  | 20-pin SSOP package                                      |  |  |  |

|                                                         |           |                                        | 5.3  | °C/W  | 20-pin QFN 4X4mm package                                 |  |  |  |

| TH03                                                    | TJMAX     | Maximum Junction Temperature           | 150  | °C    |                                                          |  |  |  |

| TH04                                                    | PD        | Power Dissipation                      |      | W     | PD = PINTERNAL + PI/O                                    |  |  |  |