Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1615-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

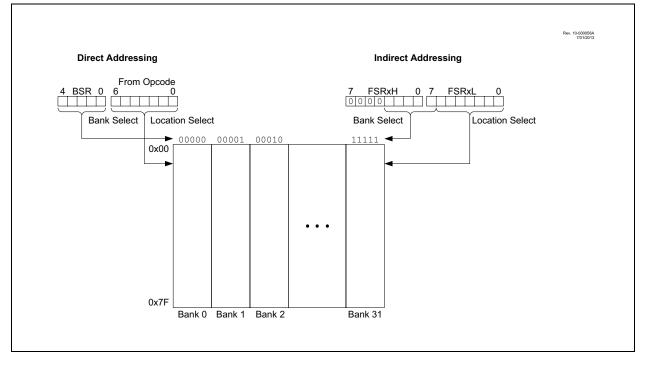

#### 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

#### FIGURE 3-9: TRADITIONAL DATA MEMORY MAP

| R/W-0/0        | R/W-0/0            | R/W-0/0                                                                                                         | R/W-0/0         | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |  |

|----------------|--------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|-----------------|------------------|------------------|-------------|--|--|--|--|

| TMR1GIE        | ADIE               | RCIE                                                                                                            | TXIE            | SSP1IE          | CCP1IE           | TMR2IE           | TMR1IE      |  |  |  |  |

| bit 7          |                    |                                                                                                                 |                 |                 |                  |                  | bit C       |  |  |  |  |

|                |                    |                                                                                                                 |                 |                 |                  |                  |             |  |  |  |  |

| Legend:        |                    |                                                                                                                 |                 |                 |                  |                  |             |  |  |  |  |

| R = Readab     |                    | W = Writable                                                                                                    |                 | •               | nented bit, read |                  |             |  |  |  |  |

| u = Bit is un  | 6                  | x = Bit is unki                                                                                                 |                 | -n/n = Value a  | at POR and BO    | R/Value at all o | ther Resets |  |  |  |  |

| '1' = Bit is s | et                 | '0' = Bit is cle                                                                                                | ared            |                 |                  |                  |             |  |  |  |  |

| bit 7          | TMR1GIE: Ti        | mer1 Gate Inte                                                                                                  | rrunt Enable I  | nit             |                  |                  |             |  |  |  |  |

|                |                    | he Timer1 gate                                                                                                  | •               |                 |                  |                  |             |  |  |  |  |

|                |                    | the Timer1 gate                                                                                                 |                 |                 |                  |                  |             |  |  |  |  |

| bit 6          | ADIE: Analog       | g-to-Digital Con                                                                                                | verter (ADC)    | Interrupt Enabl | e bit            |                  |             |  |  |  |  |

|                |                    | 1 = Enables the ADC interrupt                                                                                   |                 |                 |                  |                  |             |  |  |  |  |

|                |                    | the ADC interru                                                                                                 | •               |                 |                  |                  |             |  |  |  |  |

| bit 5          |                    | RT Receive Interrupt Enable bit                                                                                 |                 |                 |                  |                  |             |  |  |  |  |

|                |                    | <ul> <li>1 = Enables the EUSART receive interrupt</li> <li>0 = Disables the EUSART receive interrupt</li> </ul> |                 |                 |                  |                  |             |  |  |  |  |

| bit 4          |                    | RT Transmit Int                                                                                                 | •               |                 |                  |                  |             |  |  |  |  |

|                |                    | 1 = Enables the EUSART transmit interrupt                                                                       |                 |                 |                  |                  |             |  |  |  |  |

|                | 0 = Disables       | the EUSART tr                                                                                                   | ansmit interru  | pt              |                  |                  |             |  |  |  |  |

| bit 3          | •                  | SSP1IE: Synchronous Serial Port (MSSP) Interrupt Enable bit                                                     |                 |                 |                  |                  |             |  |  |  |  |

|                |                    | 1 = Enables the MSSP interrupt                                                                                  |                 |                 |                  |                  |             |  |  |  |  |

| bit 2          |                    | 0 = Disables the MSSP interrupt                                                                                 |                 |                 |                  |                  |             |  |  |  |  |

|                |                    | <b>CCP1IE:</b> CCP1 Interrupt Enable bit<br>1 = Enables the CCP1 interrupt                                      |                 |                 |                  |                  |             |  |  |  |  |

|                |                    | 0 = Disables the CCP1 interrupt                                                                                 |                 |                 |                  |                  |             |  |  |  |  |

| bit 1          | TMR2IE: TM         | R2 to PR2 Mate                                                                                                  | ch Interrupt Er | nable bit       |                  |                  |             |  |  |  |  |

|                |                    | 1 = Enables the Timer2 to PR2 match interrupt                                                                   |                 |                 |                  |                  |             |  |  |  |  |

|                |                    | 0 = Disables the Timer2 to PR2 match interrupt                                                                  |                 |                 |                  |                  |             |  |  |  |  |

| bit 0          |                    | imer1 Overflow Interrupt Enable bit<br>s the Timer1 overflow interrupt                                          |                 |                 |                  |                  |             |  |  |  |  |

|                |                    | the Timer1 over<br>the Timer1 over                                                                              |                 |                 |                  |                  |             |  |  |  |  |

|                |                    |                                                                                                                 |                 | •               |                  |                  |             |  |  |  |  |

| Note: E        | Bit PEIE of the IN |                                                                                                                 | must bo         |                 |                  |                  |             |  |  |  |  |

|                | set to enable any  |                                                                                                                 |                 |                 |                  |                  |             |  |  |  |  |

# REGISTER 7-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

# PIC16(L)F1615/9

| -                                 |                                     |                   |         |                                                       |         |         |         |  |

|-----------------------------------|-------------------------------------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| R/W-0/0                           | R/W-0/0                             | R/W-0/0           | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|                                   |                                     |                   | HADR<   | 15:8> <b>(1, 2)</b>                                   |         |         |         |  |

| bit 7                             |                                     |                   |         |                                                       |         |         | bit 0   |  |

|                                   |                                     |                   |         |                                                       |         |         |         |  |

| Legend:                           |                                     |                   |         |                                                       |         |         |         |  |

| R = Readable bit W = Writable bit |                                     |                   | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unch                   | Bit is unchanged x = Bit is unknown |                   |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set                  |                                     | '0' = Bit is clea | ared    |                                                       |         |         |         |  |

#### REGISTER 11-14: SCANHADRH: SCAN HIGH ADDRESS HIGH BYTE REGISTER

bit 7-0 HADR<15:8>: Scan End Address bits<sup>(1, 2)</sup>

Most Significant bits of the address at the end of the designated scan

**Note 1:** Registers SCANHADRH/L form a 16-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

## REGISTER 11-15: SCANHADRL: SCAN HIGH ADDRESS LOW BYTE REGISTER

| R/W-0/0        | R/W-0/0 | R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0          | R/W-0/0 | R/W-0/0 |

|----------------|---------|------------------|---------|--------------------|------------------|---------|---------|

|                |         |                  | HADR<   | 7:0> <b>(1, 2)</b> |                  |         |         |

| bit 7          |         |                  |         |                    |                  |         | bit 0   |

|                |         |                  |         |                    |                  |         |         |

| Legend:        |         |                  |         |                    |                  |         |         |

| R = Readable b | oit     | W = Writable bit | t       | U = Unimpler       | nented bit, read | as '0'  |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 HADR<7:0>: Scan End Address bits<sup>(1, 2)</sup>

Least Significant bits of the address at the end of the designated scan

- **Note 1:** Registers SCANHADRH/L form a 16-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

- 2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

| Legend: |     |         |         |         |         |         |         |

|---------|-----|---------|---------|---------|---------|---------|---------|

| bit 7   |     |         |         |         |         |         | bit 0   |

|         | —   | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   |

| U-0     | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

U = Unimplemented bit, read as '0'

-n/n = Value at POR and BOR/Value at all other Resets

#### **REGISTER 12-5: WPUA: WEAK PULL-UP PORTA REGISTER**

W = Writable bit

x = Bit is unknown

| '1' = Bit is set | '0' = Bit is cleared                                 |

|------------------|------------------------------------------------------|

|                  |                                                      |

| bit 7-6          | Unimplemented: Read as '0'                           |

| bit 5-0          | WPUA<5:0>: Weak Pull-up Register bits <sup>(3)</sup> |

| bit 5-0 | WPUA<5:0>: Weak Pull-up Register bits <sup>(3)</sup> |

|---------|------------------------------------------------------|

|         | 1 = Pull-up enabled                                  |

|         | 0 = Pull-up disabled                                 |

|         | -                                                    |

R = Readable bit

u = Bit is unchanged

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is configured as an output.

- **3:** For the WPUA3 bit, when MCLRE = 1, weak pull-up is internally enabled, but not reported here.

#### REGISTER 12-6: ODCONA: PORTA OPEN-DRAIN CONTROL REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|-----|---------|---------|---------|

| —     | —   | ODA5    | ODA4    | —   | ODA2    | ODA1    | ODA0    |

| bit 7 |     |         |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>ODA&lt;5:4&gt;:</b> PORTA Open-Drain Enable bits<br>For RA<5:4> pins, respectively<br>1 = Port pin operates as open-drain drive (sink current only)<br>0 = Port pin operates as standard push-pull drive (source and sink current) |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0 | <b>ODA&lt;2:0&gt;:</b> PORTA Open-Drain Enable bits<br>For RA<2:0> pins, respectively<br>1 = Port pin operates as open-drain drive (sink current only)<br>0 = Port pin operates as standard push-pull drive (source and sink current) |

-n/n = Value at POR and BOR/Value at all other Resets

| R/W-1/1                           | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0          | U-0              | U-0    | U-0   |

|-----------------------------------|---------|---------|---------|--------------|------------------|--------|-------|

| WPUB7                             | WPUB6   | WPUB5   | WPUB4   | —            | —                | —      | —     |

| bit 7                             |         |         |         |              |                  |        | bit 0 |

|                                   |         |         |         |              |                  |        |       |

| Legend:                           |         |         |         |              |                  |        |       |

| R = Readable bit W = Writable bit |         |         |         | U = Unimpler | mented bit, read | as '0' |       |

# **REGISTER 12-13: WPUB: WEAK PULL-UP PORTB REGISTER**<sup>(1),(2)</sup>

x = Bit is unknown

'0' = Bit is cleared

| bit 7-4 | WPUB<7:4>: Weak Pull-up Register bits |

|---------|---------------------------------------|

|         | 1 = Pull-up enabled                   |

|         | 0 = Pull-up disabled                  |

|         |                                       |

bit 3-0 Unimplemented: Read as '0'

u = Bit is unchanged

'1' = Bit is set

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

## REGISTER 12-14: ODCONB: PORTB OPEN-DRAIN CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| ODB7    | ODB6    | ODB5    | ODB4    | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| ODB<7:4>: PORTB Open-Drain Enable bits                                      |

|-----------------------------------------------------------------------------|

| For RB<7:4> pins, respectively                                              |

| 1 = Port pin operates as open-drain drive (sink current only)               |

| 0 = Port pin operates as standard push-pull drive (source and sink current) |

| Unimplemented: Read as '0'                                                  |

|                                                                             |

#### 12.5.8 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the peripheral pin select logic. See **Section13.0** "**Peripheral Pin Select (PPS) Module**" for more information. Analog input functions, such as ADC inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELC register. Digital output functions continue to may continue to control the pin when it is in Analog mode.

# 22.8 Register Definitions: Timer1 Control

## REGISTER 22-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0/u          | R/W-0/u                | R/W-0/u           | R/W-0/u        | U-0             | R/W-0/u          | U-0            | R/W-0/u      |

|------------------|------------------------|-------------------|----------------|-----------------|------------------|----------------|--------------|

| TMR10            | 1CS<1:0> T1CKPS<1:0>   |                   |                |                 | T1SYNC           | —              | TMR10N       |

| pit 7            |                        |                   |                |                 |                  |                | bit 0        |

|                  |                        |                   |                |                 |                  |                |              |

| Legend:          |                        |                   |                |                 |                  |                |              |

| R = Readable     | bit                    | W = Writable I    | oit            | U = Unimpler    | nented bit, read | as '0'         |              |

| u = Bit is unch  | anged                  | x = Bit is unkn   | own            | -n/n = Value a  | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |                        | '0' = Bit is clea | ared           |                 |                  |                |              |

|                  |                        |                   |                |                 |                  |                |              |

| bit 7-6          | TMR1CS<1:0             | D>: Timer1 Cloc   | k Source Sele  | ect bits        |                  |                |              |

|                  | 11 =LFINTOS            | SC                |                |                 |                  |                |              |

|                  | 10 =T1CKI              |                   |                |                 |                  |                |              |

|                  | 01 =Fosc<br>00 =Fosc/4 |                   |                |                 |                  |                |              |

| bit 5-4          |                        | >: Timer1 Input   | Clock Presca   | ale Select hits |                  |                |              |

|                  | 11 =1:8 Pres           | •                 |                |                 |                  |                |              |

|                  | 10 =1:4 Pres           |                   |                |                 |                  |                |              |

|                  | 01 =1:2 Pres           | cale value        |                |                 |                  |                |              |

|                  | 00 =1:1 Pres           | cale value        |                |                 |                  |                |              |

| bit 3            | Unimplemen             | ted: Read as '    | )'             |                 |                  |                |              |

| bit 2            | T1SYNC: Tin            | ner1 Synchroniz   | zation Control | bit             |                  |                |              |

|                  |                        | ynchronize asyr   |                |                 |                  |                |              |

|                  | -                      | nize asynchrono   |                | t with system c | lock (Fosc)      |                |              |

| bit 1            | Unimplemen             | ted: Read as '    | )'             |                 |                  |                |              |

| bit 0            | TMR1ON: Tir            |                   |                |                 |                  |                |              |

|                  | 1 = Enables            |                   |                | a: a            |                  |                |              |

|                  | 0 = Stops Tir          | mer1 and clears   | s Timer1 gate  | tlip-tlop       |                  |                |              |

| R/W-0/u          | R/W-0/u                        | R/W-0/u                                | R/W-0/u          | R/W/HC-0/u                         | R-x/x                          | R/W-0/u    | R/W-0/u      |  |  |

|------------------|--------------------------------|----------------------------------------|------------------|------------------------------------|--------------------------------|------------|--------------|--|--|

| TMR1GE           | T1GPOL                         | T1GTM                                  | T1GSPM           | T1GGO/<br>DONE                     | T1GVAL                         | T1GSS      | S<1:0>       |  |  |

| bit 7            |                                |                                        |                  |                                    |                                |            | bit 0        |  |  |

|                  |                                |                                        |                  |                                    |                                |            |              |  |  |

| Legend:          |                                |                                        |                  |                                    |                                |            |              |  |  |

| R = Readable     |                                | W = Writable                           |                  | U = Unimplemented bit, read as '0' |                                |            |              |  |  |

| u = Bit is uncl  | 0                              | x = Bit is unkr                        |                  |                                    | at POR and BO                  |            | other Resets |  |  |

| '1' = Bit is set |                                | '0' = Bit is cle                       | ared             | HC = Bit is cle                    | eared by hardw                 | are        |              |  |  |

| bit 7            | TMR1GE: Tir                    | mer1 Gate Ena                          | ble bit          |                                    |                                |            |              |  |  |

|                  | <u>If TMR1ON =</u>             |                                        |                  |                                    |                                |            |              |  |  |

|                  | This bit is ign<br>If TMR1ON = |                                        |                  |                                    |                                |            |              |  |  |

|                  |                                | ounting is cont                        | rolled by the Ti | imer1 gate fund                    | ction                          |            |              |  |  |

|                  | 0 = Timer1 c                   | ounts regardle                         | ss of Timer1 ga  | ate function                       |                                |            |              |  |  |

| bit 6            |                                | T1GPOL: Timer1 Gate Polarity bit       |                  |                                    |                                |            |              |  |  |

|                  |                                | ate is active-hi                       |                  |                                    |                                |            |              |  |  |

| bit 5            |                                | er1 Gate Toggle                        | •                | 5                                  | ,                              |            |              |  |  |

|                  |                                | Bate Toggle mo                         |                  |                                    |                                |            |              |  |  |

|                  |                                | Bate Toggle mo<br>Ip-flop toggles      |                  |                                    | flop is cleared                |            |              |  |  |

| bit 4            | •                              | ner1 Gate Sing                         |                  |                                    |                                |            |              |  |  |

|                  |                                | -                                      |                  |                                    | ntrolling Timer1               | aate       |              |  |  |

|                  |                                | ate Single-Puls                        |                  |                                    | <b>J</b>                       | 0          |              |  |  |

| bit 3            |                                | IE: Timer1 Gate                        | •                | •                                  |                                |            |              |  |  |

|                  |                                | ate single-puls<br>ate single-puls     |                  |                                    | for an edge<br>or has not been | started    |              |  |  |

| bit 2            | T1GVAL: Tin                    | ner1 Gate Value                        | e Status bit     |                                    |                                |            |              |  |  |

|                  |                                | current state o<br>y Timer1 Gate I     |                  |                                    | e provided to T                | MR1H:TMR1L |              |  |  |

| bit 0            | T1GSS<1:0>                     | : Timer1 Gate                          | Source Select    | bits                               |                                |            |              |  |  |

|                  |                                | ator 2 optionally<br>ator 1 optionally |                  |                                    |                                |            |              |  |  |

|                  | 01 =Timer0 c                   | verflow output                         |                  |                                    |                                |            |              |  |  |

|                  | 00 =Timer1 g                   | ata aia (T10)                          |                  |                                    |                                |            |              |  |  |

# REGISTER 22-2: T1GCON: TIMER1 GATE CONTROL REGISTER

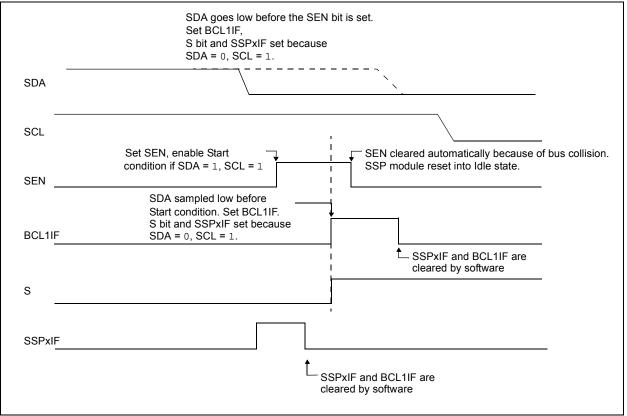

#### 24.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 24-33).

- b) SCL is sampled low before SDA is asserted low (Figure 24-34).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- · the Start condition is aborted,

- the BCL1IF flag is set and

- the MSSP module is reset to its Idle state (Figure 24-33).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 24-35). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

## 25.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 25.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXxSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART.

#### 25.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 25.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDxCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

25.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXxREG register. If the TSR still contains all or part of a previous character, the new character data is held in the TXxREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXxREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

Note: The TSR register is not mapped in data memory, so it is not available to the user.

- 25.5.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXxREG register.

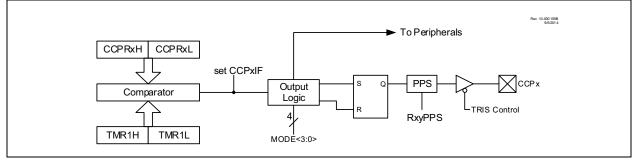

## 26.2 Compare Mode

The Compare mode function described in this section is available and identical for all CCP modules.

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- · Toggle the CCPx output

- · Set the CCPx output

- Clear the CCPx output

- · Pulse the CCPx output

- · Generate a Software Interrupt

- Optionally Reset TMR1

The action on the pin is based on the value of the MODE<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set.

All Compare modes can generate an interrupt.

Figure 26-2 shows a simplified diagram of the compare operation.

#### 26.2.1 CCPx PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

# FIGURE 26-2: COMPARE MODE OPERATION BLOCK DIAGRAM

| R/W-x/u          | R/W-x/u       | R/W-x/u                                              | R/W-x/u        | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|---------------|------------------------------------------------------|----------------|----------------|------------------|------------------|-------------|

| LCxG4D4T         | LCxG4D4N      | LCxG4D3T                                             | LCxG4D3N       | LCxG4D2T       | LCxG4D2N         | LCxG4D1T         | LCxG4D1N    |

| bit 7            |               |                                                      |                |                |                  |                  | bit C       |

|                  |               |                                                      |                |                |                  |                  |             |

| Legend:          |               |                                                      |                |                |                  |                  |             |

| R = Readable     |               | W = Writable                                         | bit            | •              | nented bit, read |                  |             |

| u = Bit is unch  | anged         | x = Bit is unkr                                      |                | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |               | '0' = Bit is clea                                    | ared           |                |                  |                  |             |

| bit 7            | 1 = Icxd4T is | Gate 4 Data 4 1<br>gated into lcxg<br>not gated into | <u>,</u>       | rted) bit      |                  |                  |             |

| bit 6            |               | Gate 4 Data 4                                        | •              | rted) bit      |                  |                  |             |

|                  |               | gated into lcxg<br>not gated into                    |                |                |                  |                  |             |

| bit 5            | LCxG4D3T: G   | Gate 4 Data 3 1                                      | True (non-inve | rted) bit      |                  |                  |             |

|                  |               | gated into lcxg<br>not gated into                    |                |                |                  |                  |             |

| bit 4            |               | Gate 4 Data 3 I                                      | •              | rted) bit      |                  |                  |             |

|                  |               | gated into Icxo<br>not gated into                    |                |                |                  |                  |             |

| bit 3            | LCxG4D2T:     | Gate 4 Data 2 1                                      | True (non-inve | rted) bit      |                  |                  |             |

|                  |               | gated into lcxg<br>not gated into                    |                |                |                  |                  |             |

| bit 2            | LCxG4D2N:     | Gate 4 Data 2 I                                      | Negated (inver | rted) bit      |                  |                  |             |

|                  |               | gated into lcxo<br>not gated into                    |                |                |                  |                  |             |

| bit 1            | LCxG4D1T: G   | Gate 4 Data 1 1                                      | True (non-inve | rted) bit      |                  |                  |             |

|                  |               | gated into lcxg                                      |                |                |                  |                  |             |

|                  |               | not gated into                                       | •              |                |                  |                  |             |

| bit 0            |               | Gate 4 Data 1 I gated into Icxo                      | •              | rted) bit      |                  |                  |             |

## REGISTER 29-10: CLCxGLS3: GATE 4 LOGIC SELECT REGISTER

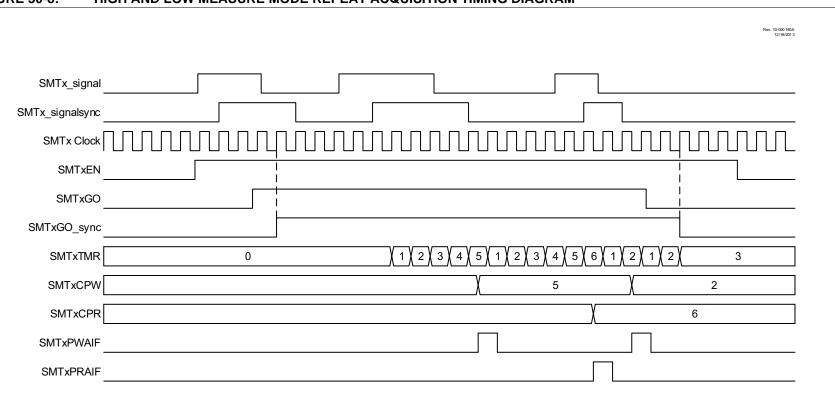

# FIGURE 30-8:

## -8: HIGH AND LOW MEASURE MODE REPEAT ACQUISITION TIMING DIAGRAM

PIC16(L)F1615/9

| U-0            | U-0                      | U-0                                   | R/W-0/0          | R/W-0/0                                                                                  | R/W-0/0         | R/W-0/0 | R/W-0/0 |  |  |  |

|----------------|--------------------------|---------------------------------------|------------------|------------------------------------------------------------------------------------------|-----------------|---------|---------|--|--|--|

| _              | —                        | —                                     |                  |                                                                                          | WSEL<4:0>       |         |         |  |  |  |

| bit 7          |                          |                                       |                  |                                                                                          |                 |         | bit (   |  |  |  |

|                |                          |                                       |                  |                                                                                          |                 |         |         |  |  |  |

| Legend:        |                          |                                       |                  |                                                                                          |                 |         |         |  |  |  |

| R = Readal     |                          | W = Writable                          |                  | U = Unimplemented bit, read as '0'<br>p(a = )(clus at ROR and ROR)(clus at all other Rec |                 |         |         |  |  |  |

| u = Bit is ur  | •                        | x = Bit is unl                        |                  | -n/n = Value at POR and BOR/Value at all other Res                                       |                 |         |         |  |  |  |

| '1' = Bit is s | et                       | '0' = Bit is cl                       | eared            | q = Value de                                                                             | pends on condit | ion     |         |  |  |  |

| bit 7-5        | Unimpleme                | nted: Read as                         | '∩'              |                                                                                          |                 |         |         |  |  |  |

|                | -                        |                                       |                  | _                                                                                        |                 |         |         |  |  |  |

| bit 4-0        | 11111 = Re               |                                       | w Selection bits | 5                                                                                        |                 |         |         |  |  |  |

|                | •                        | 301700                                |                  |                                                                                          |                 |         |         |  |  |  |

|                | •                        |                                       |                  |                                                                                          |                 |         |         |  |  |  |

|                | •                        | •                                     |                  |                                                                                          |                 |         |         |  |  |  |

|                |                          | 1000 = Reserved<br>0111 = MFINTOSC/16 |                  |                                                                                          |                 |         |         |  |  |  |

|                | 10111 = MF<br>10110 = AT |                                       |                  |                                                                                          |                 |         |         |  |  |  |

|                | 10101 = LF               |                                       |                  |                                                                                          |                 |         |         |  |  |  |

|                | 10100 <b>= PV</b>        |                                       |                  |                                                                                          |                 |         |         |  |  |  |

|                | 10011 <b>= PV</b>        |                                       |                  |                                                                                          |                 |         |         |  |  |  |

|                | 10010 = Re<br>10001 = SN |                                       |                  |                                                                                          |                 |         |         |  |  |  |

|                |                          | IR0_overflow                          |                  |                                                                                          |                 |         |         |  |  |  |

|                |                          | IR5 overflow                          |                  |                                                                                          |                 |         |         |  |  |  |

|                |                          | IR3_overflow                          |                  |                                                                                          |                 |         |         |  |  |  |

|                |                          | IR1_overflow                          |                  |                                                                                          |                 |         |         |  |  |  |

|                | 01100 = LC<br>01011 = LC |                                       |                  |                                                                                          |                 |         |         |  |  |  |

|                | 01011 = LC<br>01010 = LC |                                       |                  |                                                                                          |                 |         |         |  |  |  |

|                | 01001 = LC               | -                                     |                  |                                                                                          |                 |         |         |  |  |  |

|                |                          | IR6_postscaled                        | t                |                                                                                          |                 |         |         |  |  |  |

|                |                          | IR4_postscaled                        |                  |                                                                                          |                 |         |         |  |  |  |

|                |                          | IR2_postscaled                        | d d              |                                                                                          |                 |         |         |  |  |  |

|                | 00101 = ZC<br>00100 = CC |                                       |                  |                                                                                          |                 |         |         |  |  |  |

|                | 00011 = CC               |                                       |                  |                                                                                          |                 |         |         |  |  |  |

|                | 00010 = C2               |                                       |                  |                                                                                          |                 |         |         |  |  |  |

|                | 00001 = C1               |                                       |                  |                                                                                          |                 |         |         |  |  |  |

|                | 00000 = SN               | 1TWINx pin                            |                  |                                                                                          |                 |         |         |  |  |  |

# REGISTER 30-6: SMT2WIN: SMT2 WINDOW INPUT SELECT REGISTER

## REGISTER 30-15: SMTxCPWL: SMT CAPTURED PULSE WIDTH REGISTER – LOW BYTE

| R-x/x            | R-x/x | R-x/x             | R-x/x | R-x/x                                               | R-x/x            | R-x/x    | R-x/x |  |

|------------------|-------|-------------------|-------|-----------------------------------------------------|------------------|----------|-------|--|

|                  |       |                   | SMTxC | PW<7:0>                                             |                  |          |       |  |

| bit 7            |       |                   |       |                                                     |                  |          | bit 0 |  |

|                  |       |                   |       |                                                     |                  |          |       |  |

| Legend:          |       |                   |       |                                                     |                  |          |       |  |

| R = Readable     | bit   | W = Writable b    | it    | U = Unimpler                                        | mented bit, read | d as '0' |       |  |

| u = Bit is unch  | anged | x = Bit is unkno  | own   | -n/n = Value at POR and BOR/Value at all other Rese |                  |          |       |  |

| '1' = Bit is set |       | '0' = Bit is clea | red   |                                                     |                  |          |       |  |

bit 7-0 SMTxCPW<7:0>: Significant bits of the SMT PW Latch – Low Byte

## REGISTER 30-16: SMTxCPWH: SMT CAPTURED PULSE WIDTH REGISTER - HIGH BYTE

| R-x/x | R-x/x | R-x/x | R-x/x  | R-x/x   | R-x/x | R-x/x | R-x/x |

|-------|-------|-------|--------|---------|-------|-------|-------|

|       |       |       | SMTxCP | W<15:8> |       |       |       |

| bit 7 |       |       |        |         |       |       | bit 0 |

|       |       |       |        |         |       |       |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxCPW<15:8>: Significant bits of the SMT PW Latch – High Byte

#### REGISTER 30-17: SMTxCPWU: SMT CAPTURED PULSE WIDTH REGISTER - UPPER BYTE

| R-x/x          | R-x/x | R-x/x | R-x/x   | R-x/x          | R-x/x          | R-x/x          |  |  |  |  |  |

|----------------|-------|-------|---------|----------------|----------------|----------------|--|--|--|--|--|

| SMTxCPW<23:16> |       |       |         |                |                |                |  |  |  |  |  |

|                |       |       |         |                |                | bit 0          |  |  |  |  |  |

|                |       |       |         |                |                |                |  |  |  |  |  |

|                |       |       | SMTxCPV | SMTxCPW<23:16> | SMTxCPW<23:16> | SMTxCPW<23:16> |  |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxCPW<23:16>: Significant bits of the SMT PW Latch – Upper Byte

## 32.5 PID Control Registers

Long bit name prefixes for the 16-bit PID peripherals are shown in Table 32-1. Refer to **Section 1.1** "**Register and Bit Naming Conventions**" for more information

TABLE 32-1:

| Peripheral | Bit Name Prefix |  |  |

|------------|-----------------|--|--|

| PID1       | PID1            |  |  |

### REGISTER 32-1: PIDxCON: PID CONFIGURATION REGISTER

| R/W-0/0 | R/HS/HC-0/0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|---------|-------------|-----|-----|-----|---------|-----------|---------|

| EN      | BUSY        |     | _   | _   |         | MODE<2:0> |         |

| bit 7   |             |     |     |     |         |           | bit 0   |

| Legend:                     |                      |                                                       |  |  |  |

|-----------------------------|----------------------|-------------------------------------------------------|--|--|--|

| HC = Bit is cleared by hard | dware                | HS = Bit is set by hardware                           |  |  |  |

| R = Readable bit            | W = Writable bit     | U = Unimplemented bit, read as '0'                    |  |  |  |

| u = Bit is unchanged        | x = Bit is unknown   | -m/n = Value at POR and BOR/Value at all other Resets |  |  |  |

| '1' = Bit is set            | '0' = Bit is cleared | q = Value depends on condition                        |  |  |  |

- 1 = PID module is enabled

- 0 = PID module is disabled

bit 6 **BUSY:** PID module is currently calculating

- bit 5-3 Unimplemented: Read as '0'

- bit 2-0 MODE<2:0>: PID Mode Control bits

- 11x = Reserved. Do not use.

- 101 = PID output is the calculated output (current error plus accumulated previous errors) in 2's complement notation

- 100 = Reserved. Do not use.

- 011 = (IN<15:0>+SET<15:0>)\*K1<15:0> 2's complement signed inputs, with accumulation

- 010 = (IN<15:0>+SET<15:0>)\*K1<15:0> 2's complement signed inputs, without accumulation

- 001 = (IN<15:0>+SET<15:0>)\*K1<15:0> unsigned inputs, with accumulation

- 000 = (IN<15:0>+SET<15:0>)\*K1<15:0> unsigned inputs, without accumulation

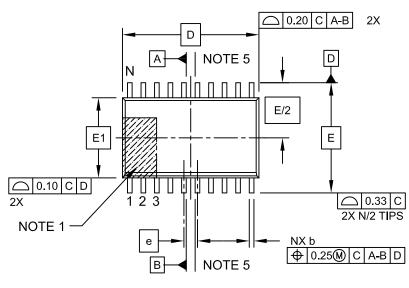

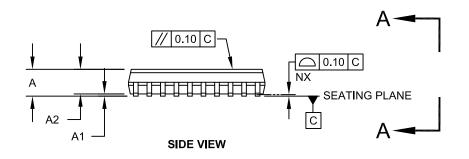

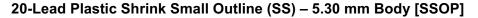

# 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW A-A

Microchip Technology Drawing C04-094C Sheet 1 of 2

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |          | MILLIMETERS | 6    |  |

|--------------------------|----------|----------|-------------|------|--|

| Dimension                | n Limits | MIN      | NOM         | MAX  |  |

| Number of Pins           |          | 20       |             |      |  |

| Pitch                    | е        | 0.65 BSC |             |      |  |

| Overall Height           | Α        | -        | -           | 2.00 |  |

| Molded Package Thickness | A2       | 1.65     | 1.75        | 1.85 |  |

| Standoff                 | A1       | 0.05     | -           | -    |  |

| Overall Width            | Е        | 7.40     | 7.80        | 8.20 |  |

| Molded Package Width     | E1       | 5.00     | 5.30        | 5.60 |  |

| Overall Length           | D        | 6.90     | 7.20        | 7.50 |  |

| Foot Length              | L        | 0.55     | 0.75        | 0.95 |  |

| Footprint                | L1       | 1.25 REF |             |      |  |

| Lead Thickness           | С        | 0.09     | _           | 0.25 |  |

| Foot Angle               | φ        | 0°       | 4°          | 8°   |  |

| Lead Width               | b        | 0.22     | -           | 0.38 |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B

# THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Micro-chip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support