Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 14-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1615-i-sl |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.1 Register and Bit Naming Conventions

#### 1.1.1 REGISTER NAMES

When there are multiple instances of the same peripheral in a device, the peripheral control registers will be depicted as the concatenation of a peripheral identifier, peripheral instance, and control identifier. The control registers section will show just one instance of all the register names with an 'x' in the place of the peripheral instance number. This naming convention may also be applied to peripherals when there is only one instance of that peripheral in the device to maintain compatibility with other devices in the family that contain more than one.

#### 1.1.2 BIT NAMES

There are two variants for bit names:

- Short name: Bit function abbreviation

- Long name: Peripheral abbreviation + short name

#### 1.1.2.1 Short Bit Names

Short bit names are an abbreviation for the bit function. For example, some peripherals are enabled with the EN bit. The bit names shown in the registers are the short name variant.

Short bit names are useful when accessing bits in C programs. The general format for accessing bits by the short name is *RegisterName*bits.*ShortName*. For example, the enable bit, EN, in the COG1CON0 register can be set in C programs with the instruction COG1CON0bits.EN = 1.

Short names are generally not useful in assembly programs because the same name may be used by different peripherals in different bit positions. When this occurs, during the include file generation, all instances of that short bit name are appended with an underscore plus the name of the register in which the bit resides to avoid naming contentions.

#### 1.1.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral, thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN.

Long bit names are useful in both C and assembly programs. For example, in C the COG1CON0 enable bit can be set with the G1EN = 1 instruction. In assembly, this bit can be set with the BSF COG1CON0, G1EN instruction.

#### 1.1.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

COG1CON0bits.MD = 0x5;

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name MD2 and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to Push-Pull mode:

Example 1:

MOVLW ~(1<<G1MD1) ANDWF COG1CON0,F MOVLW 1<<G1MD2 | 1<<G1MD0 IORWF COG1CON0,F

#### Example 2:

| BSF | COG1CON0,G1MD2 |

|-----|----------------|

| BCF | COG1CON0,G1MD1 |

| BSF | COG1CON0,G1MD0 |

#### 1.1.3 REGISTER AND BIT NAMING EXCEPTIONS

#### 1.1.3.1 Status, Interrupt, and Mirror Bits

Status, interrupt enables, interrupt flags, and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

#### 1.1.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

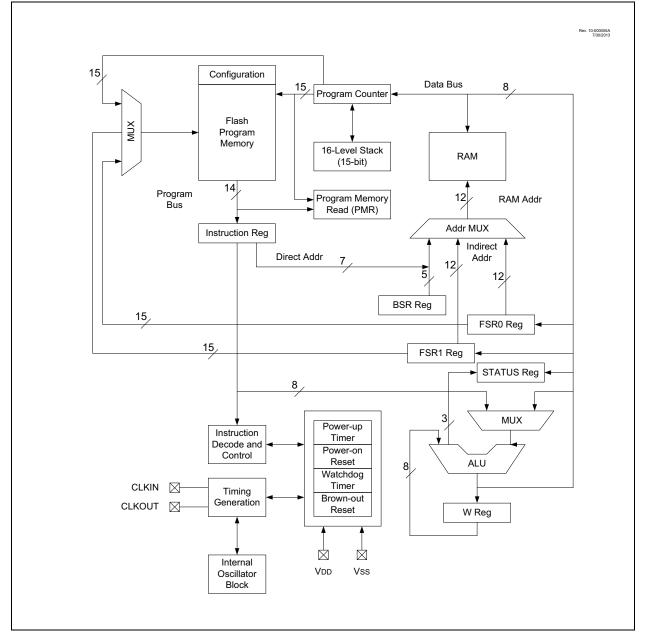

# 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative Addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- · 16-level Stack with Overflow and Underflow

- · File Select Registers

- Instruction Set

## 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 7.5 "Automatic Context Saving"**, for more information.

# 2.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See section **Section 3.5** "**Stack**" for more details.

# 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.6 "Indirect Addressing"** for more details.

## 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 34.0** "Instruction Set Summary" for more details.

# 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

## 3.1 **Program Memory Organization**

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (See Figure 3-1).

## 3.2 High-Endurance Flash

This device has a 128-byte section of high-endurance Program Flash Memory (PFM) in lieu of data EEPROM. This area is especially well suited for nonvolatile data storage that is expected to be updated frequently over the life of the end product. See Section 10.2 "Flash Program Memory Overview" for more information on writing data to PFM. See Section 3.2.1.2 "Indirect Read with FSR" for more information about using the FSR registers to read byte data stored in PFM.

| Device          | Program Memory Space<br>(Words) | Last Program Memory<br>Address | High-Endurance Flash<br>Memory Address<br>Range <sup>(1)</sup> |

|-----------------|---------------------------------|--------------------------------|----------------------------------------------------------------|

| PIC16(L)F1615/9 | 8,192                           | 1FFFh                          | 1F80h-1FFFh                                                    |

Note 1: High-endurance Flash applies to low byte of each address in the range.

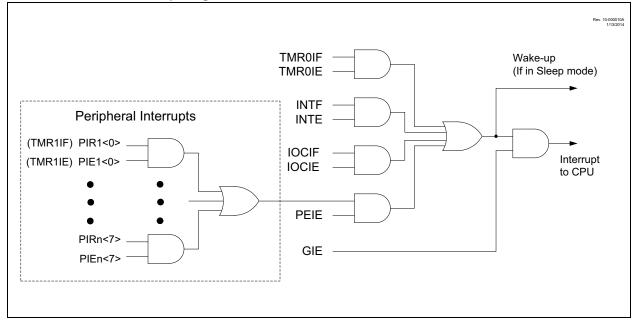

# 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 7-1.

FIGURE 7-1: Interrupt Logic

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| LATB7   | LATB6   | LATB5   | LATB4   | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

|         |         |         |         |     |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | LATB<7:4>: RB<7:4> Output Latch Value bits <sup>(1)</sup> |

|---------|-----------------------------------------------------------|

|---------|-----------------------------------------------------------|

bit 3-0 Unimplemented: Read as '0'

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

#### REGISTER 12-12: ANSELB: PORTB ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|---------|---------|-----|-----|-----|-------|

| —     | _   | ANSB5   | ANSB4   |     | _   | _   | —     |

| bit 7 |     |         |         |     |     |     | bit 0 |

|       |     |         |         |     |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-4 **ANSB<5:4>**: Analog Select between Analog or Digital Function on Pins RB<5:4>, respectively 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

analog input: Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disact

0 = Digital I/O. Pin is assigned to port or digital special function.

bit 3-0 Unimplemented: Read as '0'

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### 17.2.6 ADC CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- · Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

**Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section17.4 "ADC Acquisition Requirements".

#### EXAMPLE 17-1: ADC CONVERSION

| ;This code block configures the ADC<br>;for polling, Vdd and Vss references, FRC |                |                      |  |  |  |

|----------------------------------------------------------------------------------|----------------|----------------------|--|--|--|

| ;oscillat                                                                        | or and ANO in  | iput.                |  |  |  |

| ;                                                                                |                |                      |  |  |  |

| ;Conversi                                                                        | ion start & po | lling for completion |  |  |  |

| ; are inc                                                                        | cluded.        |                      |  |  |  |

| ;                                                                                |                |                      |  |  |  |

| BANKSEL                                                                          | ADCON1         | ;                    |  |  |  |

| MOVLW                                                                            | B'11110000'    | ;Right justify, FRC  |  |  |  |

|                                                                                  |                | ;oscillator          |  |  |  |

| MOVWF                                                                            | ADCON1         | ;Vdd and Vss Vref+   |  |  |  |

| BANKSEL                                                                          | TRISA          | ;                    |  |  |  |

| BSF                                                                              | TRISA,0        | ;Set RAO to input    |  |  |  |

| BANKSEL                                                                          | ANSEL          | ;                    |  |  |  |

| BSF                                                                              | ANSEL,0        | ;Set RAO to analog   |  |  |  |

| BANKSEL                                                                          | ADCON0         | i                    |  |  |  |

| MOVLW                                                                            | B'0000001'     | ;Select channel ANO  |  |  |  |

| MOVWF                                                                            | ADCON0         | ;Turn ADC On         |  |  |  |

| CALL                                                                             | SampleTime     | ;Acquisiton delay    |  |  |  |

| BSF                                                                              | ADCON0, ADGO   | ;Start conversion    |  |  |  |

| BTFSC                                                                            | ADCON0, ADGO   | ;Is conversion done? |  |  |  |

| GOTO                                                                             | \$-1           | ;No, test again      |  |  |  |

| BANKSEL                                                                          | ADRESH         | ;                    |  |  |  |

| MOVF                                                                             | ADRESH,W       | ;Read upper 2 bits   |  |  |  |

| MOVWF                                                                            | RESULTHI       | ;store in GPR space  |  |  |  |

| BANKSEL                                                                          | ADRESL         | ;                    |  |  |  |

| MOVF                                                                             | ADRESL,W       |                      |  |  |  |

| MOVWF                                                                            | RESULTLO       | ;Store in GPR space  |  |  |  |

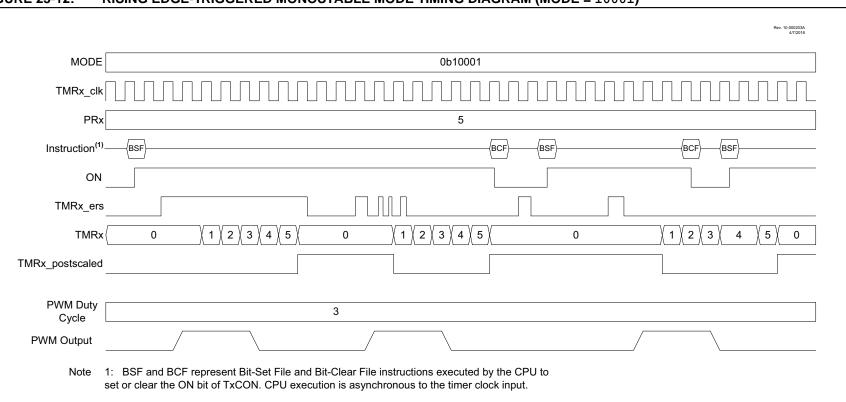

# FIGURE 23-12: RISING EDGE-TRIGGERED MONOSTABLE MODE TIMING DIAGRAM (MODE = 10001)

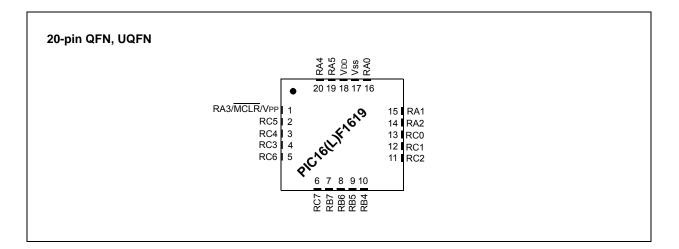

PIC16(L)F1615/9

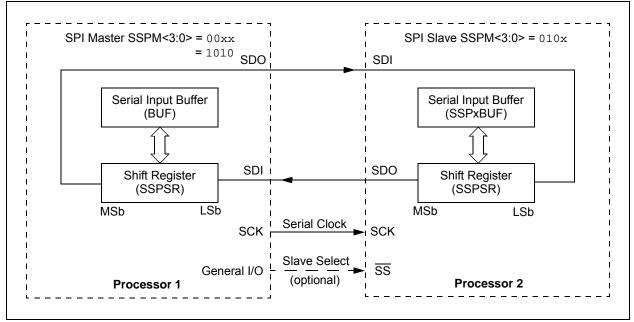

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPxBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full Detect bit, BF of the SSPxSTAT register, and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/reception of data will be ignored and the write collision detect bit WCOL of the SSPxCON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPxBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various Status conditions.

FIGURE 24-5: SPI MASTER/SLAVE CONNECTION

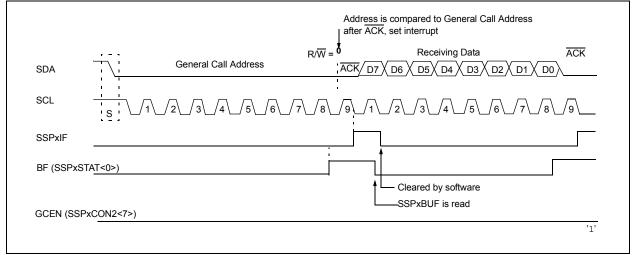

#### 24.5.7 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^{2}C$  protocol, defined as address 0x00. When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with the

R/W bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 24-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

## FIGURE 24-24: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE

## 24.5.8 SSP MASK REGISTER

An SSP Mask (SSPxMSK) register (Register 24-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

## 24.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception (Figure 24-29) is enabled by programming the Receive Enable bit, RCEN bit of the SSPxCON2 register.

| Note: | The MSSP module must be in an Idle      |

|-------|-----------------------------------------|

|       | state before the RCEN bit is set or the |

|       | RCEN bit will be disregarded.           |

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/ low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPxCON2 register.

## 24.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPSR. It is cleared when the SSPxBUF register is read.

## 24.6.7.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when eight bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

## 24.6.7.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### 24.6.7.4 Typical Receive Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. User writes SSPxBUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 7. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 8. User sets the RCEN bit of the SSPxCON2 register and the master clocks in a byte from the slave.

- 9. After the eighth falling edge of SCL, SSPxIF and BF are set.

- 10. Master clears SSPxIF and reads the received byte from SSPxBUF, clears BF.

- 11. Master sets ACK value sent to slave in ACKDT bit of the SSPxCON2 register and initiates the ACK by setting the ACKEN bit.

- 12. Master's ACK is clocked out to the slave and SSPxIF is set.

- 13. User clears SSPxIF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

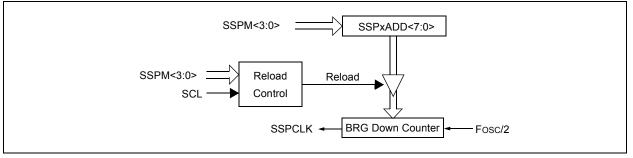

## 24.7 BAUD RATE GENERATOR

The MSSP module has a Baud Rate Generator available for clock generation in both I<sup>2</sup>C and SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSPxADD register (Register 24-6). When a write occurs to SSPxBUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" in Figure 24-40 triggers the value from SSPxADD to be loaded into the BRG counter. This occurs twice for each oscillation of the

module clock line. The logic dictating when the reload signal is asserted depends on the mode the MSSP is being operated in.

Table 24-4 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPxADD.

#### **EQUATION 24-1:**

$$FCLOCK = \frac{FOSC}{(SSPxADD + 1)(4)}$$

#### FIGURE 24-40: BAUD RATE GENERATOR BLOCK DIAGRAM

**Note:** Values of 0x00, 0x01 and 0x02 are not valid for SSPxADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

#### TABLE 24-4: MSSP CLOCK RATE W/BRG

| Fosc   | Fcy   | BRG Value | FCLOCK<br>(2 Rollovers of BRG) |

|--------|-------|-----------|--------------------------------|

| 32 MHz | 8 MHz | 13h       | 400 kHz                        |

| 32 MHz | 8 MHz | 19h       | 308 kHz                        |

| 32 MHz | 8 MHz | 4Fh       | 100 kHz                        |

| 16 MHz | 4 MHz | 09h       | 400 kHz                        |

| 16 MHz | 4 MHz | 0Ch       | 308 kHz                        |

| 16 MHz | 4 MHz | 27h       | 100 kHz                        |

| 4 MHz  | 1 MHz | 09h       | 100 kHz                        |

**Note:** Refer to the I/O port electrical specifications in Table 35-4 to ensure the system is designed to support IOL requirements.

|        |                   |            |                             |                | SYNC       | <b>C =</b> 0, <b>BRG</b>    | l = 0, BRC     | <b>316 =</b> 0 |                             |                |            |                             |

|--------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|----------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 20.000 MHz |            | Fosc = 18.432 MHz           |                |            | Fosc = 16.000 MHz           |                |                | Fosc = 11.0592 MHz          |                |            |                             |

| RATE   | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                 | _          | _                           | _              | _          | _                           | _              | _              | _                           | _              |            |                             |

| 1200   | 1221              | 1.73       | 255                         | 1200           | 0.00       | 239                         | 1202           | 0.16           | 207                         | 1200           | 0.00       | 143                         |

| 2400   | 2404              | 0.16       | 129                         | 2400           | 0.00       | 119                         | 2404           | 0.16           | 103                         | 2400           | 0.00       | 71                          |

| 9600   | 9470              | -1.36      | 32                          | 9600           | 0.00       | 29                          | 9615           | 0.16           | 25                          | 9600           | 0.00       | 17                          |

| 10417  | 10417             | 0.00       | 29                          | 10286          | -1.26      | 27                          | 10417          | 0.00           | 23                          | 10165          | -2.42      | 16                          |

| 19.2k  | 19.53k            | 1.73       | 15                          | 19.20k         | 0.00       | 14                          | 19.23k         | 0.16           | 12                          | 19.20k         | 0.00       | 8                           |

| 57.6k  | —                 | _          | _                           | 57.60k         | 0.00       | 7                           | —              | —              | _                           | 57.60k         | 0.00       | 2                           |

| 115.2k | —                 | _          | _                           | _              | _          | —                           | —              | _              | _                           | —              | _          | —                           |

#### TABLE 25-5:BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  |            |                             |                | SYNC       | <b>C</b> = 0, BRGH          | <b>1</b> = 0, BRO | <b>616 =</b> 0 |                             |                |            |                             |

|--------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|-------------------|----------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |            | Fosc = 4.000 MHz            |                |            | Fosc = 3.6864 MHz           |                   |                | Fosc = 1.000 MHz            |                |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                |            | _                           | 300            | 0.16       | 207                         | 300               | 0.00           | 191                         | 300            | 0.16       | 51                          |

| 1200   | 1202             | 0.16       | 103                         | 1202           | 0.16       | 51                          | 1200              | 0.00           | 47                          | 1202           | 0.16       | 12                          |

| 2400   | 2404             | 0.16       | 51                          | 2404           | 0.16       | 25                          | 2400              | 0.00           | 23                          | —              | —          | —                           |

| 9600   | 9615             | 0.16       | 12                          | —              | —          | —                           | 9600              | 0.00           | 5                           | —              | —          | —                           |

| 10417  | 10417            | 0.00       | 11                          | 10417          | 0.00       | 5                           | —                 | _              | _                           | —              | _          | _                           |

| 19.2k  | —                | _          | _                           | —              | _          | _                           | 19.20k            | 0.00           | 2                           | —              | _          | _                           |

| 57.6k  | —                | _          | —                           | —              | —          | —                           | 57.60k            | 0.00           | 0                           | —              | _          | —                           |

| 115.2k | —                | _          | —                           | —              | _          | _                           | —                 | _              | —                           | —              | _          | —                           |

|        | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                |                            |                   |                |            |                             |                |            |                             |

|--------|-------------------------------|------------|-----------------------------|----------------|----------------------------|-------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 20.000 MHz             |            | Fosc = 18.432 MHz           |                |                            | Fosc = 16.000 MHz |                |            | Fosc = 11.0592 MHz          |                |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | % SPBRG<br>Error (decimal) |                   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                             | _          | _                           | _              | _                          | _                 |                | _          |                             |                | _          |                             |

| 1200   | _                             | _          | —                           | —              | _                          | —                 | _              | _          | —                           | _              | _          | _                           |

| 2400   |                               | _          | _                           | —              | _                          | _                 | _              | _          | _                           | _              | _          | _                           |

| 9600   | 9615                          | 0.16       | 129                         | 9600           | 0.00                       | 119               | 9615           | 0.16       | 103                         | 9600           | 0.00       | 71                          |

| 10417  | 10417                         | 0.00       | 119                         | 10378          | -0.37                      | 110               | 10417          | 0.00       | 95                          | 10473          | 0.53       | 65                          |

| 19.2k  | 19.23k                        | 0.16       | 64                          | 19.20k         | 0.00                       | 59                | 19.23k         | 0.16       | 51                          | 19.20k         | 0.00       | 35                          |

| 57.6k  | 56.82k                        | -1.36      | 21                          | 57.60k         | 0.00                       | 19                | 58.82k         | 2.12       | 16                          | 57.60k         | 0.00       | 11                          |

| 115.2k | 113.64k                       | -1.36      | 10                          | 115.2k         | 0.00                       | 9                 | 111.1k         | -3.55      | 8                           | 115.2k         | 0.00       | 5                           |

| R/W-0/0          | R/W-0/0          | R/W-0/0           | R/W-0/0     | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0     |

|------------------|------------------|-------------------|-------------|----------------|------------------|----------------|-------------|

|                  |                  |                   | CCPR        | <15:8>         |                  |                |             |

| bit 7            |                  |                   |             |                |                  |                | bit C       |

|                  |                  |                   |             |                |                  |                |             |

| Legend:          |                  |                   |             |                |                  |                |             |

| R = Readable     | bit              | W = Writable b    | oit         | U = Unimpler   | nented bit, read | d as '0'       |             |

| u = Bit is unch  | anged            | x = Bit is unkno  | own         | -n/n = Value a | at POR and BC    | R/Value at all | other Reset |

| '1' = Bit is set |                  | '0' = Bit is clea | red         |                |                  |                |             |

|                  |                  |                   |             |                |                  |                |             |

| bit 7-0          | <u>MODE = Ca</u> | <u>pture Mode</u> |             |                |                  |                |             |

|                  | CCPRxH<7         | :0>: MSB of capt  | ured TMR1 v | alue           |                  |                |             |

#### REGISTER 26-4: CCPRxH: CCPx HIGH BYTE REGISTER

7-0 <u>MODE = Capture Mode</u> CCPRxH<7:0>: MSB of captured TMR1 value <u>MODE = Compare Mode</u> CCPRxH<7:0>: MSB compared to TMR1 value <u>MODE = PWM Mode && FMT = 0</u> CCPRxH<7:2>: Not used CCPRxH<1:0>: CCPW<9:8> — Pulse width Most Significant two bits <u>MODE = PWM Mode && FMT = 1</u> CCPRxH<7:0>: CCPW<9:2> — Pulse width Most Significant eight bits

#### REGISTER 26-5: CCPxCAP: CCPx CAPTURE INPUT SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

|       | —   | —   | —   | —   |         | CTS<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

| Legend:              |                      |                                                      |

|----------------------|----------------------|------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                   |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Reset |

| '1' = Bit is set     | '0' = Bit is cleared |                                                      |

| bit 7-3 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 2-0 CTS<2:0>: Capture Trigger Input Selection bits

- 111 = LC4\_out

- 110 = LC3\_out

- 101 = LC2\_out

- 100 = LC1\_out

- 011 = IOC\_interrupt

- 010 = C2\_OUT\_sync

- 001 = C1\_OUT\_sync

- 000 = CCPx pin

|                        | Tir                                                               |                                                                        |                                                                                     |                                                        |                                                                                                                                                                                                             |                                                                        | on Page                                                |  |  |  |

|------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|

|                        | Timer2 module Period Register                                     |                                                                        |                                                                                     |                                                        |                                                                                                                                                                                                             |                                                                        |                                                        |  |  |  |

| _                      | OUT                                                               | POL                                                                    | _                                                                                   | _                                                      |                                                                                                                                                                                                             | _                                                                      | 369                                                    |  |  |  |

| DC<9:2>                |                                                                   |                                                                        |                                                                                     |                                                        |                                                                                                                                                                                                             |                                                                        |                                                        |  |  |  |

| DC<1:0>                |                                                                   |                                                                        |                                                                                     |                                                        |                                                                                                                                                                                                             | 369                                                                    |                                                        |  |  |  |

| _                      | OUT                                                               | POL                                                                    | _                                                                                   | _                                                      | _                                                                                                                                                                                                           | _                                                                      | 369                                                    |  |  |  |

|                        |                                                                   | DC<                                                                    | ):2>                                                                                |                                                        |                                                                                                                                                                                                             |                                                                        | 369                                                    |  |  |  |

| DC<1:0>                | —                                                                 | —                                                                      | _                                                                                   | —                                                      | —                                                                                                                                                                                                           | —                                                                      | 369                                                    |  |  |  |

|                        | CKPS<2:0>                                                         |                                                                        |                                                                                     | OUTPS                                                  | S<3:0>                                                                                                                                                                                                      |                                                                        | 262                                                    |  |  |  |

| Timer2 module Register |                                                                   |                                                                        |                                                                                     |                                                        |                                                                                                                                                                                                             | 243*                                                                   |                                                        |  |  |  |

| —                      | TRISA5                                                            | TRISA4                                                                 | —(1)                                                                                | TRISA2                                                 | TRISA1                                                                                                                                                                                                      | TRISA0                                                                 | 159                                                    |  |  |  |

| (2) TRISC6(2)          | TRISC5                                                            | TRISC4                                                                 | TRISC3                                                                              | TRISC2                                                 | TRISC1                                                                                                                                                                                                      | TRISC0                                                                 | 173                                                    |  |  |  |

| 1                      | DC<1:0><br>DC<1:0><br>DC<1:0><br>DC<1:0><br>TRISC6 <sup>(2)</sup> | DC<1:0> — OUT<br>DC<1:0> — OUT<br>DC<1:0> — I<br>CKPS<2:0><br>— TRISA5 | DC<1:0>     —     —       DC<1:0>     —     OUT     POL       DC<1:0>     —     DC< | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | DC<1:0> — — —   — OUT POL — —   DC<1:0> — POL — —   DC<1:0> — — DC<9:2>   DC<1:0> — — DC<9:2>   DC<1:0> — — —   I CKPS<2:0> OUTPS   Timer2 module Register OUTPS   — TRISA5 TRISA4   — TRISC5 TRISC4 TRISC3 | $\begin{array}{c c c c c c c } & DC <9:2> & DC <1:0> & & & & & & & & $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |  |  |  |

#### TABLE 27-3: SUMMARY OF REGISTERS ASSOCIATED WITH PWM

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the PWM. \* Page provides register information.

**Note 1:** Unimplemented, read as '1'.

2: PIC16(L)F1619 only.

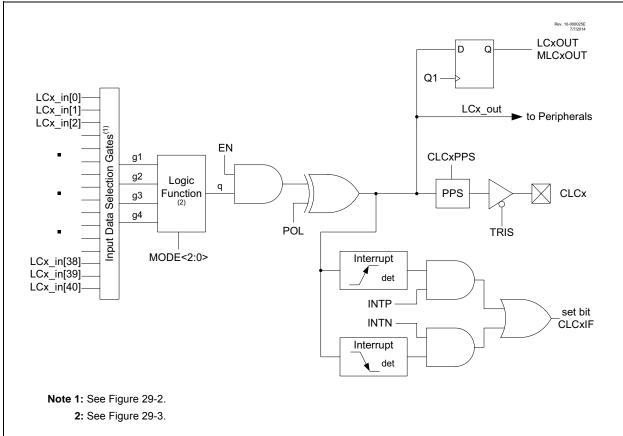

# 29.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLCx) provides programmable logic that operates outside the speed limitations of software execution. The logic cell takes up to 16 input signals, and through the use of configurable gates, reduces the 16 inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- · I/O pins

- Internal clocks

- · Peripherals

- · Register bits

The output can be directed internally to peripherals and to an output pin.

Refer to Figure 29-1 for a simplified diagram showing signal flow through the CLCx.

Possible configurations include:

- Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

- Clocked J-K with Reset

#### FIGURE 29-1: CONFIGURABLE LOGIC CELL BLOCK DIAGRAM

#### TABLE 35-4: I/O PORTS

| Standard      | d Operat | ing Conditions (unless otherw        | ise stated)       |      |          |       |                                                                                  |

|---------------|----------|--------------------------------------|-------------------|------|----------|-------|----------------------------------------------------------------------------------|

| Param.<br>No. | Sym.     | Characteristic                       | Min.              | Тур† | Max.     | Units | Conditions                                                                       |

|               | VIL      | Input Low Voltage                    |                   |      |          |       |                                                                                  |

|               |          | I/O PORT:                            |                   |      |          |       |                                                                                  |

| D030          |          | with TTL buffer                      | —                 | —    | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                                 |

| D030A         |          |                                      | —                 | —    | 0.15 Vdd | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                                 |

| D031          |          | with Schmitt Trigger buffer          | —                 | _    | 0.2 VDD  | V     | $2.0V \leq V\text{DD} \leq 5.5V$                                                 |

| D032          |          | MCLR                                 | —                 | —    | 0.2 VDD  | V     |                                                                                  |

|               | Vih      | Input High Voltage                   |                   |      |          |       |                                                                                  |

| D040          |          | with TTL buffer                      | 2.0               | —    | —        | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                                 |

| D040A         |          |                                      | 0.25 VDD +<br>0.8 | _    | _        | V     | $1.8V \le V\text{DD} \le 4.5V$                                                   |

| D041          |          | with Schmitt Trigger buffer          | 0.8 VDD           | —    | —        | V     | $2.0V \leq V\text{DD} \leq 5.5V$                                                 |

| D042          |          | MCLR                                 | 0.8 Vdd           | _    | _        | V     |                                                                                  |

|               | lı∟      | Input Leakage Current <sup>(1)</sup> |                   |      |          |       |                                                                                  |

| D060          |          | I/O Ports                            | —                 | ± 5  | ± 125    | nA    | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance, 85°C                          |

|               |          |                                      | —                 | ± 5  | ± 1000   | nA    | Vss $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance, 125°C                      |

| D061          |          | MCLR <sup>(3)</sup>                  | —                 | ± 50 | ± 200    | nA    | Vss $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance, 85°C                       |

|               | IPUR     | Weak Pull-up Current                 |                   |      | •        |       |                                                                                  |

| D070*         |          |                                      | 25                | 100  | 200      | μA    | VDD = 3.3V, VPIN = VSS                                                           |

|               |          |                                      | 25                | 140  | 300      | μA    | VDD = 5.0V, VPIN = VSS                                                           |

|               | Vol      | Output Low Voltage <sup>(3)</sup>    |                   |      |          |       |                                                                                  |

| D080          |          | I/O Ports                            | —                 | _    | 0.6      | V     | IOL = 8.0 mA, VDD = 5.0V<br>IOL = 6.0 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |

| D080A         |          | High Drive I/O <sup>(1)</sup>        | —                 | 1.4V | —        | V     | IOL = 100 mA, VDD = 5.0V                                                         |

|               | Voн      | Output High Voltage <sup>(3)</sup>   |                   |      | •        |       |                                                                                  |

| D090          |          | I/O Ports                            | Vdd - 0.7         | _    | _        | V     | IOH = 3.5 mA, VDD = 5.0V<br>IOH = 3.0 mA, VDD = 3.3V<br>IOH = 1.0 mA, VDD = 1.8V |

| D090A         |          | High Drive I/O <sup>(1)</sup>        | _                 | 3.5V | <u> </u> | V     | IOL = 100 mA, VDD = 5.0V                                                         |

| D101A*        | CIO      | All I/O pins                         |                   |      | 50       | pF    | <u> </u>                                                                         |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Negative current is defined as current sourced by the pin.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Excluding OSC2 in CLKOUT mode.