Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿXFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1615t-i-sl |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             | SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |  |

|-------------|-----------------------------------------------|--|

| IADLE 3-14. | SPECIAL FUNCTION REGISTER SUMMART (CONTINUED) |  |

| TADLE  | : 3-14: SPE            |                      | ION REGIST           | ER SUIVIIVIA     |                   |                  |        |        |          |                      |                           |

|--------|------------------------|----------------------|----------------------|------------------|-------------------|------------------|--------|--------|----------|----------------------|---------------------------|

| Addr   | Name                   | Bit 7                | Bit 6                | Bit 5            | Bit 4             | Bit 3            | Bit 2  | Bit 1  | Bit 0    | Value on<br>POR, BOR | Value on all other Resets |

| Bank 3 |                        |                      |                      |                  |                   |                  |        |        |          |                      |                           |

| 18Ch   | ANSELA                 | —                    | —                    | —                | ANSA4             | —                | ANSA2  | ANSA1  | ANSA0    | 1 -111               | 1 -111                    |

| 18Dh   | ANSELB <sup>(4)</sup>  | —                    | —                    | ANSB5            | ANSB4             | —                | —      | —      | —        | 11                   | 11                        |

| 18Eh   | ANSELC                 | ANSC7 <sup>(4)</sup> | ANSC6 <sup>(4)</sup> | —                | —                 | ANSC3            | ANSC2  | ANSC1  | ANSC0    | 11 1111              | 11 1111                   |

| 18Fh   | —                      | Unimplemented        | 1                    |                  |                   |                  |        |        |          | _                    | —                         |

| 190h   | —                      | Unimplemented        | 1                    |                  |                   |                  |        |        |          | _                    | —                         |

| 191h   | PMADRL                 | Flash Program        | Memory Address       | Register Low B   | Byte              |                  |        |        |          | 0000 0000            | 0000 0000                 |

| 192h   | PMADRH                 | (2)                  | Flash Program        | Memory Address   | s Register High I | 3yte             |        |        |          | 1000 0000            | 1000 0000                 |

| 193h   | PMDATL                 | Flash Program        | Memory Read D        | ata Register Lov | v Byte            |                  |        |        |          | xxxx xxxx            | uuuu uuuu                 |

| 194h   | PMDATH                 | —                    | —                    | Flash Program    | Memory Read D     | ata Register Hig | h Byte |        |          | xx xxxx              | uu uuuu                   |

| 195h   | PMCON1                 | (2)                  | CFGS                 | LWLO             | FREE              | WRERR            | WREN   | WR     | RD       | 1000 x000            | 1000 q000                 |

| 196h   | PMCON2                 | Flash Program        | Memory Control       | Register 2       |                   |                  |        |        |          | 0000 0000            | 0000 0000                 |

| 197h   | VREGCON <sup>(1)</sup> | —                    | —                    | —                | —                 | —                | —      | VREGPM | Reserved | 01                   | 01                        |

| 198h   | —                      | Unimplemented        | 1                    |                  |                   |                  |        |        |          | —                    | —                         |

| 199h   | RC1REG                 | EUSART Recei         | ve Data Register     |                  |                   |                  |        |        |          | 0000 0000            | 0000 0000                 |

| 19Ah   | TX1REG                 | EUSART Trans         | mit Data Registe     | r                |                   |                  |        |        |          | 0000 0000            | 0000 0000                 |

| 19Bh   | SP1BRGL                | Baud Rate Gen        | erator Data Regi     | ster Low         |                   |                  |        |        |          | 0000 0000            | 0000 0000                 |

| 19Ch   | SP1BRGH                | Baud Rate Gen        | erator Data Regi     | ster High        |                   |                  |        |        |          | 0000 0000            | 0000 0000                 |

| 19Dh   | RC1STA                 | SPEN                 | RX9                  | SREN             | CREN              | ADDEN            | FERR   | OERR   | RX9D     | 0000 000x            | 0000 000x                 |

| 19Eh   | TX1STA                 | CSRC                 | TX9                  | TXEN             | SYNC              | SENDB            | BRGH   | TRMT   | TX9D     | 0000 0010            | 0000 0010                 |

| 19Fh   | BAUD1CON               | ABDOVF               | RCIDL                | —                | SCKP              | BRG16            | —      | WUE    | ABDEN    | 01-0 0-00            | 01-0 0-00                 |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** PIC16F1615/9 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1615 only.

4: PIC16(L)F1619 only.

| TABLE 3-14: | SPECIAL FUNCTION REGISTER SUMMARY | (CONTINUED) |

|-------------|-----------------------------------|-------------|

|             |                                   |             |

|            |                  |               |                     |       |        | ,     | 5%.0  | Dir d     | <b>D</b> 14 A | Value on  | Value on all |

|------------|------------------|---------------|---------------------|-------|--------|-------|-------|-----------|---------------|-----------|--------------|

| Addr       | Name             | Bit 7         | Bit 6               | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1     | Bit 0         | POR, BOR  | other Resets |

| Bank       | 17               |               |                     |       |        |       |       |           |               |           |              |

| 88Ch       | AT1CLK           | —             | —                   | —     | —      |       | —     | —         | CS0           | 0         | 0            |

| 88Dh       | AT1SIG           | —             | — — — — — SSEL<2:0> |       |        |       |       |           |               | 000       | 000          |

| 88Eh       | AT1CSEL1         | —             | CP1S<2:0>           |       |        |       |       |           |               |           | 000          |

| 88Fh       | AT1CC1L CC1<7:0> |               |                     |       |        |       |       |           |               | 0000 0000 | 0000 0000    |

| 890h       | AT1CC1H          | CC1<9:8>      |                     |       |        |       | 000   | 000       |               |           |              |

| 891h       | AT1CCON1         | CC1EN         | —                   | —     | CC1POL | CAP1P | —     | —         | CC1MODE       | 00 00     | 00 00        |

| 892h       | AT1CSEL2         | —             | CP2S<2:0>           |       |        |       |       |           |               | 000       | 000          |

| 893h       | AT1CC2L          |               |                     |       | CC2    | <7:0> |       |           |               | 0000 0000 | 0000 0000    |

| 894h       | AT1CC2H          | —             | —                   | —     | —      |       | —     | CC2·      | <9:8>         | 000       | 000          |

| 895h       | AT1CCON2         | CC2EN         | —                   | —     | CC2POL | CAP2P | —     | —         | CC2MODE       | 00 00     | 00 00        |

| 896h       | AT1CSEL3         | —             | —                   | —     | —      |       |       | CP3S<2:0> |               | 000       | 000          |

| 897h       | AT1CC1L          |               |                     |       | CC3    | <7:0> |       |           |               | 0000 0000 | 0000 0000    |

| 898h       | AT1CC1H          | —             | —                   | —     | —      | _     | —     | CC3       | <9:8>         | 000       | 000          |

| 899h       | AT1CCON1         | CC3EN         | —                   | —     | CC3POL | CAP3P | —     | —         | CC3MODE       | 00 00     | 00 00        |

| 89Ah       |                  |               |                     |       |        |       |       |           |               |           |              |

| to<br>89Fh | —                | Unimplemented | 1                   |       |        |       |       |           |               | —         | —            |

| Bank       | 18-26            |               |                     |       |        |       |       |           |               |           |              |

| Bank  | 18-26 |               |

|-------|-------|---------------|

| x0Ch/ | _     | Unimplemented |

| x8Ch  |       |               |

| —     |       |               |

| x1Fh/ |       |               |

| x9Fh  |       |               |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** PIC16F1615/9 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1615 only.

4: PIC16(L)F1619 only.

\_\_\_\_

| Addr | Name           | Bit 7  | Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0 |     |        |          |      |           |         | Value on<br>POR, BOR | Value on all other Resets |

|------|----------------|--------|---------------------------------------------------------------------------------------------------------|-----|--------|----------|------|-----------|---------|----------------------|---------------------------|

| Bank | 27 (Continued) |        |                                                                                                         |     |        |          |      |           |         |                      |                           |

| DA5h | SMT2CPWH       |        |                                                                                                         |     | SMT2CP | W<15:8>  |      |           |         | XXXX XXXX            | XXXX XXXX                 |

| DA6h | SMT2CPWU       |        |                                                                                                         |     | SMT2CP | N<23:16> |      |           |         | XXXX XXXX            | XXXX XXXX                 |

| DA7h | SMT2PRL        |        |                                                                                                         |     | SMT2P  | PR<7:0>  |      |           |         | xxxx xxxx            | XXXX XXXX                 |

| DA8h | SMT2PRH        |        |                                                                                                         |     | SMT2PI | R<15:8>  |      |           |         | XXXX XXXX            | XXXX XXXX                 |

| DA9h | SMT2PRU        |        |                                                                                                         |     | SMT2PF | R<23:16> |      |           |         | XXXX XXXX            | XXXX XXXX                 |

| DAAh | SMT2CON0       | EN     | —                                                                                                       | STP | WPOL   | SPOL     | CPOL | SMT2F     | 'S<1:0> | 0-00 0000            | 0-00 0000                 |

| DABh | SMT2CON1       | SMT2GO | REPEAT                                                                                                  | —   | —      |          | MODE | =<3:0>    |         | 00 0000              | 00 0000                   |

| DACh | SMT2STAT       | CPRUP  | CPWUP                                                                                                   | RST | —      | —        | TS   | WS        | AS      | 000000               | 000000                    |

| DADh | SMT2CLK        | _      | —                                                                                                       | _   | _      | —        |      | CSEL<2:0> |         | 000                  | 000                       |

SSEL<4:0>

WSEL<4:0>

## TABLE 3-14: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

\_\_\_\_

\_\_\_\_

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

\_

\_\_\_\_

Note 1: PIC16F1615/9 only.

SMT2SIG

SMT2WIN

DAEh

DAFh

2: Unimplemented, read as '1'.

\_\_\_\_

\_

PIC16(L)F1615 only. 3:

4: PIC16(L)F1619 only.

---0 0000

---0 0000

---0 0000

---0 0000

## REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External clock, High-Power mode: on CLKIN pin

- 110 =ECM: External clock, Medium-Power mode: on CLKIN pin

- 101 =ECL: External clock, Low-Power mode: on CLKIN pin

- 100 =INTOSC oscillator: I/O function on CLKIN pin

- 011 =Reserved

- 010 =HS: HS oscillator, high-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 =Reserved

- 000 =Reserved

- Note 1: Enabling Brown-out Reset does not automatically enable Power-up Timer.

- 2: Once enabled, code-protect can only be disabled by bulk erasing the device.

#### **REGISTER 4-3: CONFIG3: CONFIGURATION WORD 3**

|       |       | R/P-0  | R/P-0       | R/P-1 | R/P-1      | R/P-1      | R/P-1 |

|-------|-------|--------|-------------|-------|------------|------------|-------|

|       |       |        | WDTCCS<2:0> | >     | , v        | WDTCWS<2:0 | >     |

|       |       | bit 13 |             |       |            |            | bit 8 |

| U-1   | R/P-1 | R/P-1  | R/P-1       | R/P-1 | R/P-1      | R/P-1      | R/P-1 |

| _     |       | E<1:0> |             |       | WDTCPS<4:0 |            |       |

| bit 7 | -     |        | •           |       |            |            | bit 0 |

|       |       |        |             |       |            |            |       |

| Leaend: |  |

|---------|--|

| Leyenu. |  |

bit 6-5

| Legend:              |                      |                                           |

|----------------------|----------------------|-------------------------------------------|

| R = Readable bit     | P = Programmable bit | U = Unimplemented bit, read as '1'        |

| '0' = Bit is cleared | '1' = Bit is set     | -n = Value when blank or after Bulk Erase |

WDTCCS<2:0>: WDT Configuration Clock Select bits bit 13-11

- 111 =Software Control; WDT clock selected by CS<2:0> 110 =Reserved

- 010 =Reserved

- 001 =WDT reference clock is MFINTOSC, 31.25 kHz (default value)

- 000 =WDT reference clock is LFINTOSC, 31.00 kHz output

WDTCWS<2:0>: WDT Configuration Window Select bits. bit 10-8

| WDTCWS |       | WINDOW at P                     | OR                                | Software              | Keyed               |                    |

|--------|-------|---------------------------------|-----------------------------------|-----------------------|---------------------|--------------------|

| <2:0>  | Value | Window delay<br>Percent of time | Window opening<br>Percent of time | control of<br>WINDOW? | access<br>required? |                    |

| 111    | 111   | n/a                             | 100                               | Yes                   | No                  | Default fuse = 111 |

| 110    | 111   | n/a                             | 100                               |                       |                     |                    |

| 101    | 101   | 25                              | 75                                |                       |                     |                    |

| 100    | 100   | 37.5                            | 62.5                              |                       |                     |                    |

| 011    | 011   | 50                              | 50                                | No                    | Yes                 |                    |

| 010    | 010   | 62.5                            | 37.5                              |                       |                     |                    |

| 001    | 001   | 75                              | 25                                |                       |                     |                    |

| 000    | 000   | 87.5                            | 12.5 <sup>(1)</sup>               |                       |                     |                    |

bit 7 Unimplemented: Read as '1'

WDTE<1:0>: Watchdog Timer Enable bits

11 =WDT enabled in all modes, the SEN bit in the WDTCON0 register is ignored

10 =WDT enabled while running and disabled in Sleep

01 =WDT controlled by the SEN bit in the WDTCON0 register

00 = WDT disabled

| U-0          | U-0               | R/W-0/0                                                                                                         | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |  |  |

|--------------|-------------------|-----------------------------------------------------------------------------------------------------------------|----------------|----------------|------------------|------------------|--------------|--|--|--|--|--|

| —            | —                 | CWGIF                                                                                                           | ZCDIF          | CLC4IF         | CLC3IF           | CLC2IF           | CLC1IF       |  |  |  |  |  |

| bit 7        |                   |                                                                                                                 |                |                |                  |                  | bit (        |  |  |  |  |  |

| Legend:      |                   |                                                                                                                 |                |                |                  |                  |              |  |  |  |  |  |

| R = Read     | able bit          | W = Writable                                                                                                    | bit            | U = Unimpler   | nented bit, read | 1 as '0'         |              |  |  |  |  |  |

| u = Bit is   | unchanged         | x = Bit is unk                                                                                                  | nown           | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |  |  |  |

| '1' = Bit is | s set             | '0' = Bit is cle                                                                                                | ared           |                |                  |                  |              |  |  |  |  |  |

|              |                   |                                                                                                                 |                |                |                  |                  |              |  |  |  |  |  |

| bit 7-6      | Unimplem          | ented: Read as '                                                                                                | 0'             |                |                  |                  |              |  |  |  |  |  |

| bit 5        | CWGIF: CV         | VG Interrupt Flag                                                                                               | g bit          |                |                  |                  |              |  |  |  |  |  |

|              |                   | ot is pending ot is not pending                                                                                 |                |                |                  |                  |              |  |  |  |  |  |

| bit 4        | ZCDIF: ZC         | <b>ZCDIF</b> : ZCD Interrupt Flag bit                                                                           |                |                |                  |                  |              |  |  |  |  |  |

|              |                   | 1 = Interrupt is pending                                                                                        |                |                |                  |                  |              |  |  |  |  |  |

|              | 0 = Interrup      | 0 = Interrupt is not pending                                                                                    |                |                |                  |                  |              |  |  |  |  |  |

| bit 3        |                   | CLC4IF: Configurable Logic Block 4 Interrupt Flag bit                                                           |                |                |                  |                  |              |  |  |  |  |  |

|              |                   | 1 = Interrupt is pending                                                                                        |                |                |                  |                  |              |  |  |  |  |  |

| h:4 0        |                   | <ul> <li>0 = Interrupt is not pending</li> <li>CLC3IF: Configurable Logic Block 3 Interrupt Flag bit</li> </ul> |                |                |                  |                  |              |  |  |  |  |  |

| bit 2        |                   | • •                                                                                                             | BIOCK 3 Intern | upt Flag bit   |                  |                  |              |  |  |  |  |  |

|              |                   | 1 = Interrupt is pending<br>0 = Interrupt is not pending                                                        |                |                |                  |                  |              |  |  |  |  |  |

| bit 1        |                   | onfigurable Logic                                                                                               | Block 2 Interr | rupt Flag bit  |                  |                  |              |  |  |  |  |  |

|              |                   | ot is pending                                                                                                   |                | 1 3            |                  |                  |              |  |  |  |  |  |

|              | 0 = Interrup      | 0 = Interrupt is not pending                                                                                    |                |                |                  |                  |              |  |  |  |  |  |

| bit 0        | CLC1IF: Co        | CLC1IF: Configurable Logic Block 1 Interrupt Flag bit                                                           |                |                |                  |                  |              |  |  |  |  |  |

|              |                   | 1 = Interrupt is pending                                                                                        |                |                |                  |                  |              |  |  |  |  |  |

|              | 0 = Interrup      | ot is not pending                                                                                               |                |                |                  |                  |              |  |  |  |  |  |

| Note:        |                   | are set when ar                                                                                                 |                |                |                  |                  |              |  |  |  |  |  |

|              |                   | , regardless of th                                                                                              |                |                |                  |                  |              |  |  |  |  |  |

|              |                   | g enable bit or th<br>of the INTCON                                                                             |                |                |                  |                  |              |  |  |  |  |  |

|              | User software     |                                                                                                                 | •              |                |                  |                  |              |  |  |  |  |  |

|              |                   | rupt flag bits are o                                                                                            | clear prior    |                |                  |                  |              |  |  |  |  |  |

|              | to onobling on in | to mark the t                                                                                                   |                |                |                  |                  |              |  |  |  |  |  |

## REGISTER 7-9: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

to enabling an interrupt.

| R/W-1/1                                 | R/W-1/1              | R/W-1/1 | R/W-1/1 | R/W-1/1                                               | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |

|-----------------------------------------|----------------------|---------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| WPUC7 <sup>(1)</sup>                    | WPUC6 <sup>(1)</sup> | WPUC5   | WPUC4   | WPUC3                                                 | WPUC2   | WPUC1   | WPUC0   |  |  |

| bit 7                                   |                      |         | •       |                                                       |         | •       | bit 0   |  |  |

|                                         |                      |         |         |                                                       |         |         |         |  |  |

| Legend:                                 |                      |         |         |                                                       |         |         |         |  |  |

| R = Readable bit W = Writable bit       |                      |         |         | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown |                      |         | nown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

## **REGISTER 12-21: WPUC: WEAK PULL-UP PORTC REGISTER**<sup>(2),(3)</sup>

'0' = Bit is cleared

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits<sup>(1)</sup>

- 1 = Pull-up enabled

- 0 = Pull-up disabled

Note 1: WPUC<7:6> on PIC16(L)F1619 only.

'1' = Bit is set

- 2: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 3: The weak pull-up device is automatically disabled if the pin is configured as an output.

## REGISTER 12-22: ODCONC: PORTC OPEN-DRAIN CONTROL REGISTER

| R/W-0/0             | R/W-0/0             | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------------------|---------------------|---------|---------|---------|---------|---------|---------|

| ODC7 <sup>(1)</sup> | ODC6 <sup>(1)</sup> | ODC5    | ODC4    | ODC3    | ODC2    | ODC1    | ODC0    |

| bit 7               |                     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ODC<7:0>:** PORTC Open-Drain Enable bits<sup>(1)</sup>

For RC<7:0> pins, respectively

- 1 = Port pin operates as open-drain drive (sink current only)

- 0 = Port pin operates as standard push-pull drive (source and sink current)

**Note 1:** ODC<7:6> on PIC16(L)F1619 only.

The pull-up and pull-down resistor values are significantly affected by small variations of VCPINV. Measuring VCPINV can be difficult, especially when the waveform is relative to VDD. However, by combining Equations 20-2 and 20-3, the resistor value can be determined from the time difference between the ZCDx\_output high and low periods. Note that the time difference,  $\Delta T$ , is 4\*TOFFSET. The equation for determining the pull-up and pull-down resistor values from the high and low ZCDx\_output periods is shown in Equation 20-4. The ZCDx\_output signal can be directly observed on the ZCDxOUT pin by setting the ZCDxOE bit.

## EQUATION 20-4:

$$R = RSERIES\left(\frac{V_{BIAS}}{V_{PEAK}\left(\sin\left(\pi Freq\frac{(\Delta T)}{2}\right)\right)} - 1\right)$$

R is pull-up or pull-down resistor.

$\mathsf{VBIAS}\xspace$  is  $\mathsf{VPULLUP}\xspace$  when R is pull-up or  $\mathsf{VDD}\xspace$  when R is pull-down.

$\Delta T$  is the ZCDxOUT high and low period difference.

## 20.6 Handling VPEAK variations

If the peak amplitude of the external voltage is expected to vary, the series resistor must be selected to keep the ZCD current source and sink below the design maximum range of  $\pm 600 \ \mu$ A and above a reasonable minimum range. A general rule of thumb is that the maximum peak voltage can be no more than six times the minimum peak voltage. To ensure that the maximum current does not exceed  $\pm 600 \ \mu$ A and the minimum is at least  $\pm 100 \ \mu$ A, compute the series resistance as shown in Equation 20-5. The compensating pull-up for this series resistance can be determined with Equation 20-3 because the pull-up value is independent from the peak voltage.

## EQUATION 20-5: SERIES R FOR V RANGE

$$RSERIES = \frac{VMAXPEAK + VMINPEAK}{7 \times 10^{-4}}$$

## 20.7 Operation During Sleep

The ZCD current sources and interrupts are unaffected by Sleep.

## 20.8 Effects of a Reset

The ZCD circuit can be configured to default to the active or inactive state on Power-On-Reset (POR). When the ZCD Configuration bit is cleared, the ZCD circuit will be active at POR. When the ZCD Configuration bit is set, the ZCDxEN bit of the ZCDxCON register must be set to enable the ZCD module.

| IGURE 22-5:            | TIMERT GATE SINGLE-PULSE MODE                                           |

|------------------------|-------------------------------------------------------------------------|

| TMR1GE                 |                                                                         |

| T1GPOL                 |                                                                         |

| T1GSPM                 |                                                                         |

| T1GG <u>O/</u><br>DONE | Cleared by hardware on<br>falling edge of T1GVAL<br>Counting enabled on |

| T1G_in                 | rising edge of T1G                                                      |

| T1CKI                  |                                                                         |

| T1GVAL                 |                                                                         |

| Timer1                 | N N + 1 N + 2                                                           |

| TMR1GIF                | Cleared by software Cleared software on falling edge of T1GVAL          |

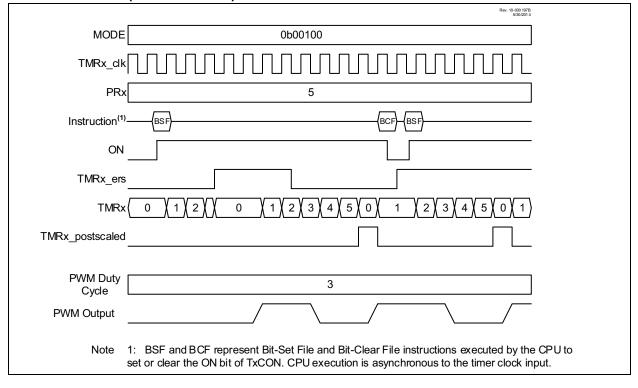

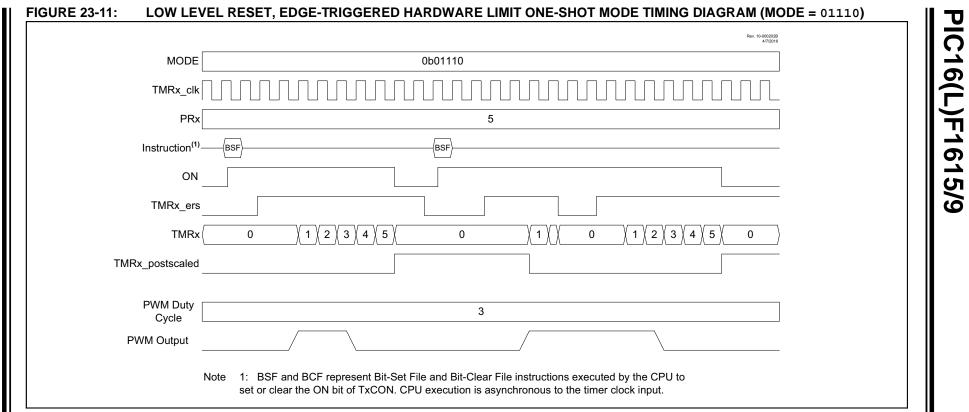

#### 23.5.3 EDGE-TRIGGERED HARDWARE LIMIT MODE

In Hardware Limit mode the timer can be reset by the TMRx\_ers external signal before the timer reaches the period count. Three types of Resets are possible:

- Reset on rising or falling edge

- (MODE<4:0>= 00011)

- Reset on rising edge (MODE<4:0> = 00100)

- Reset on falling edge (MODE<4:0> = 00101)

When the timer is used in conjunction with the CCP in PWM mode then an early Reset shortens the period and restarts the PWM pulse after a two-clock delay. Refer to Figure 23-6.

#### FIGURE 23-6: EDGE-TRIGGERED HARDWARE LIMIT MODE TIMING DIAGRAM (MODE = 00100)

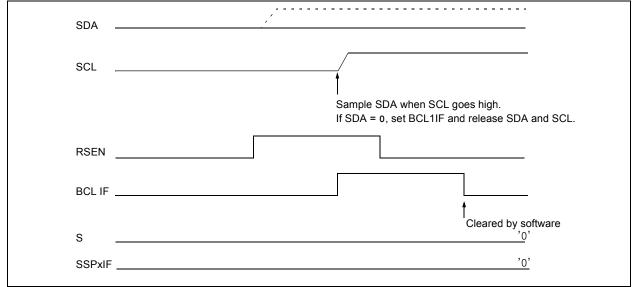

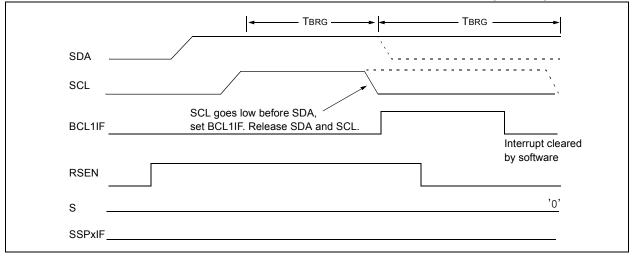

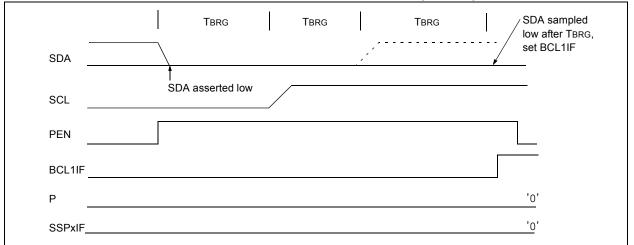

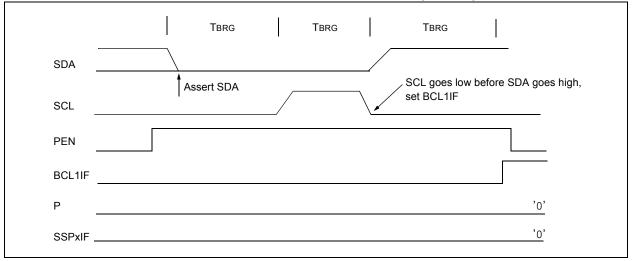

# 24.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 24-36). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 24-37.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 24-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### 24.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to zero. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 24-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 24-39).

### FIGURE 24-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 24-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

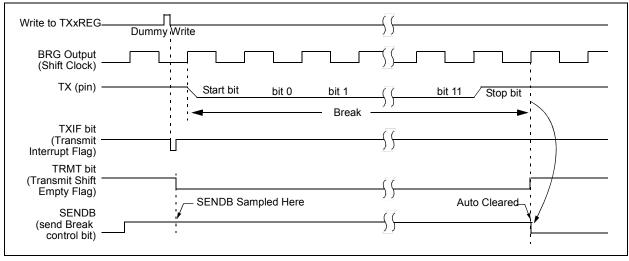

#### 25.4.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXxSTA register. The Break character transmission is then initiated by a write to the TXxREG. The value of data written to TXxREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXxSTA register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 25-9 for the timing of the Break character sequence.

#### 25.4.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXxREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXxREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXxREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXxREG.

## 25.4.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCxSTA register and the received data as indicated by RCxREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- RCIF bit is set

- FERR bit is set

- RCxREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 25.4.3 "Auto-Wake-up on Break"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDxCON register before placing the EUSART in Sleep mode.

## FIGURE 25-9: SEND BREAK CHARACTER SEQUENCE

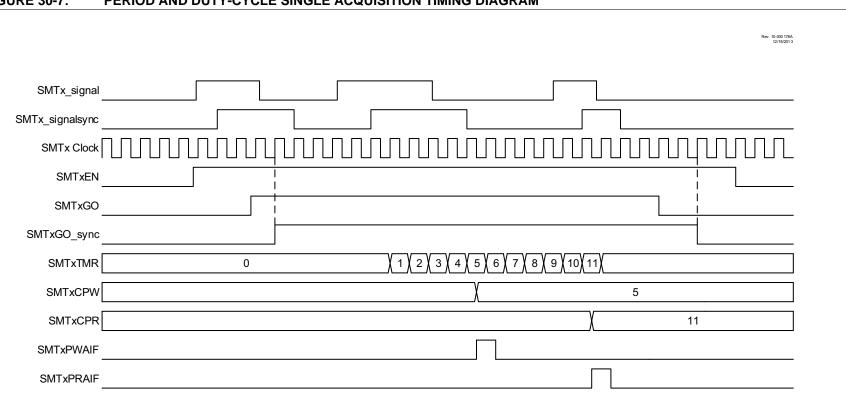

## FIGURE 30-7: PERIOD AND DUTY-CYCLE SINGLE ACQUISITION TIMING DIAGRAM

| U-0                               | U-0                                       | U-0                | R/W-0/0           | R/W-0/0      | R/W-0/0          | R/W-0/0 | R/W-0/0      |  |  |

|-----------------------------------|-------------------------------------------|--------------------|-------------------|--------------|------------------|---------|--------------|--|--|

| _                                 | _                                         | _                  |                   |              | WSEL<4:0>        |         |              |  |  |

| bit 7                             |                                           |                    |                   |              |                  |         | bit (        |  |  |

|                                   |                                           |                    |                   |              |                  |         |              |  |  |

| Legend:                           |                                           |                    |                   |              |                  |         |              |  |  |

| R = Readable bit W = Writable bit |                                           |                    |                   | •            | mented bit, read |         |              |  |  |

| u = Bit is u                      | •                                         | x = Bit is ur      |                   |              | at POR and BO    |         | other Resets |  |  |

| '1' = Bit is s                    | set                                       | '0' = Bit is c     | leared            | q = Value de | pends on condi   | tion    |              |  |  |

| bit 7-5                           | Unimplom                                  | ented: Read as     | <b>•</b> 'o'      |              |                  |         |              |  |  |

|                                   |                                           |                    |                   | _            |                  |         |              |  |  |

| bit 4-0                           | 11111 = Re                                |                    | ow Selection bits | 5            |                  |         |              |  |  |

|                                   | •                                         |                    |                   |              |                  |         |              |  |  |

|                                   | •                                         |                    |                   |              |                  |         |              |  |  |

|                                   | •                                         |                    |                   |              |                  |         |              |  |  |

|                                   | 11000 = Reserved                          |                    |                   |              |                  |         |              |  |  |

|                                   | 10111 = MFINTOSC/16<br>10110 = AT1 perclk |                    |                   |              |                  |         |              |  |  |

|                                   | 10110 = <b>L</b> F                        |                    |                   |              |                  |         |              |  |  |

|                                   |                                           | 10100 = PWM4_out   |                   |              |                  |         |              |  |  |

|                                   |                                           | 10011 = PWM3_out   |                   |              |                  |         |              |  |  |

|                                   |                                           | 10010 = SMT2_match |                   |              |                  |         |              |  |  |

|                                   | 10001 = Reserved<br>10000 = TMR0 overflow |                    |                   |              |                  |         |              |  |  |

|                                   | 01111 = TMR5_overflow                     |                    |                   |              |                  |         |              |  |  |

|                                   |                                           | /R3_overflow       |                   |              |                  |         |              |  |  |

|                                   |                                           | /IR1_overflow      |                   |              |                  |         |              |  |  |

|                                   | 01100 = LC                                |                    |                   |              |                  |         |              |  |  |

|                                   | $01011 = LC3_out$<br>01010 = LC2 out      |                    |                   |              |                  |         |              |  |  |

|                                   | 01010 - LC<br>01001 = LC                  |                    |                   |              |                  |         |              |  |  |

|                                   |                                           | /R6_postscale      | ed                |              |                  |         |              |  |  |

|                                   | 00111 = TMR4_postscaled                   |                    |                   |              |                  |         |              |  |  |

|                                   |                                           | /IR2_postscale     | ed                |              |                  |         |              |  |  |

|                                   | 00101 <b>= ZC</b>                         |                    |                   |              |                  |         |              |  |  |

|                                   | 00100 = CO<br>00011 = CO                  |                    |                   |              |                  |         |              |  |  |

|                                   | 00011 = CC<br>00010 = C2                  |                    |                   |              |                  |         |              |  |  |

|                                   | 00001 = C                                 |                    |                   |              |                  |         |              |  |  |

|                                   | 00000 = SN                                |                    |                   |              |                  |         |              |  |  |

## REGISTER 30-5: SMT1WIN: SMT1 WINDOW INPUT SELECT REGISTER

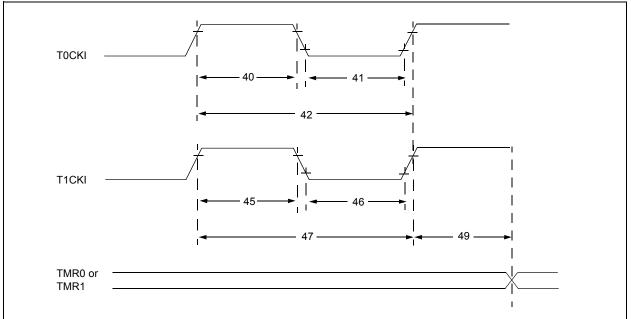

| TABLE 35-12: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|--------------|-----------------------------------------------|

|--------------|-----------------------------------------------|

| Param.<br>No. | Sym.      | Characteristic                                        |                             |                | Min.                                      | Тур†   | Max. | Units                  | Conditions         |

|---------------|-----------|-------------------------------------------------------|-----------------------------|----------------|-------------------------------------------|--------|------|------------------------|--------------------|

| 40*           | T⊤0H      | T0CKI High Pulse Width No Prescaler<br>With Prescaler |                             | No Prescaler   | 0.5 TCY + 20                              |        |      | ns                     |                    |

|               |           |                                                       |                             | With Prescaler | 10                                        |        |      | ns                     |                    |

| 41*           | T⊤0L      | T0CKI Low Pulse Width No Prescaler                    |                             | 0.5 TCY + 20   | _                                         |        | ns   |                        |                    |

|               |           |                                                       |                             | With Prescaler | 10                                        | _      |      | ns                     |                    |

| 42*           | TT0P      | T0CKI Period                                          | I Period                    |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _      | _    | ns                     | N = prescale value |

| 45*           | T⊤1H      | T1CKI High<br>Time                                    | Synchronous, No Prescaler   |                | 0.5 TCY + 20                              |        |      | ns                     |                    |

|               |           |                                                       | Synchronous, with Prescaler |                | 15                                        |        |      | ns                     |                    |

|               |           |                                                       | Asynchronous                | ;              | 30                                        |        |      | ns                     |                    |

| 46*           | TT1L      | T1CKI Low<br>Time                                     | Synchronous,                | No Prescaler   | 0.5 TCY + 20                              | _      | _    | ns                     |                    |

|               |           |                                                       | Synchronous, with Prescaler |                | 15                                        | _      | _    | ns                     |                    |

|               |           |                                                       | Asynchronous                | ;              | 30                                        |        |      | ns                     |                    |

| 47*           | TT1P      | T⊤1P T1CKI Input<br>Period                            | Synchronous                 |                | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —      | _    | ns                     | N = prescale value |

|               |           |                                                       | Asynchronous                | ;              | 60                                        | _      | —    | ns                     |                    |

| 49*           | TCKEZTMR1 | Delay from External Clock Edge to Timer<br>Increment  |                             | 2 Tosc         | _                                         | 7 Tosc | —    | Timers in Sync<br>mode |                    |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

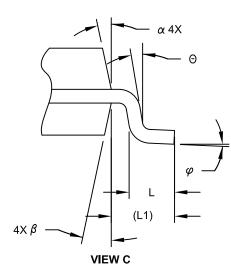

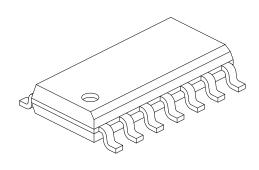

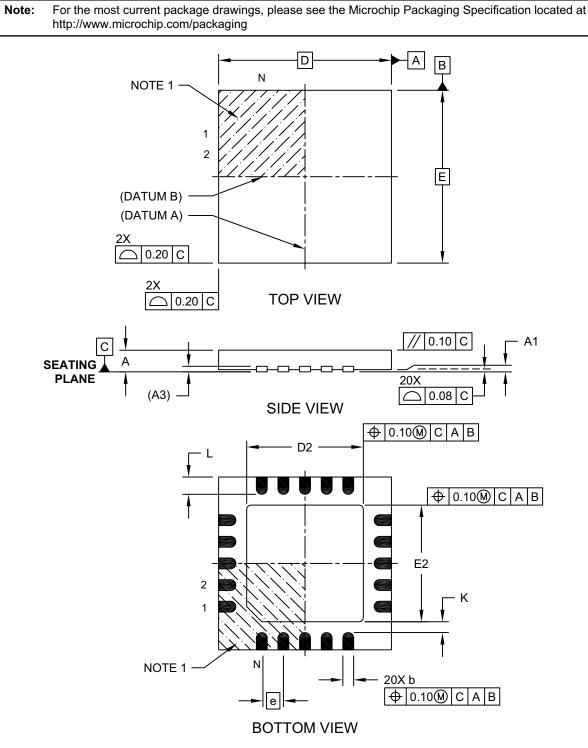

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     | MILLIMETERS |          |      |  |  |

|--------------------------|-----------|-------------|----------|------|--|--|

| Dimension Lin            | nits      | MIN         | NOM      | MAX  |  |  |

| Number of Pins           | N         | 14          |          |      |  |  |

| Pitch                    | е         |             |          |      |  |  |

| Overall Height           | A         | -           | -        | 1.75 |  |  |

| Molded Package Thickness | A2        | 1.25        | -        | -    |  |  |

| Standoff §               | A1        | 0.10        | -        | 0.25 |  |  |

| Overall Width            | E         |             | 6.00 BSC |      |  |  |

| Molded Package Width     | E1        | 3.90 BSC    |          |      |  |  |

| Overall Length           | D         | 8.65 BSC    |          |      |  |  |

| Chamfer (Optional)       | h         | 0.25        | -        | 0.50 |  |  |

| Foot Length              | L         | 0.40        | -        | 1.27 |  |  |

| Footprint                | L1        | 1.04 REF    |          |      |  |  |

| Lead Angle               | Θ         | 0°          | -        | -    |  |  |

| Foot Angle               | $\varphi$ | 0°          | -        | 8°   |  |  |

| Lead Thickness           | с         | 0.10        | -        | 0.25 |  |  |

| Lead Width               | b         | 0.31        | -        | 0.51 |  |  |

| Mold Draft Angle Top     | α         | 5°          | -        | 15°  |  |  |

| Mold Draft Angle Bottom  | β         | 5°          | -        | 15°  |  |  |

|                          |           |             |          |      |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- Reference Dimension, usually without tolerance, for information pu

Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2

## 20-Lead Ultra Thin Plastic Quad Flat, No Lead Package (GZ) - 4x4x0.5 mm Body [UQFN]

Microchip Technology Drawing C04-255A Sheet 1 of 2