Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                             |

| Supplier Device Package    | 14-TSSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1615t-i-st |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 0/1 | 20-Pin PDIP, SOIC, SSOP | 20-Pin UQFN | A/D  | Reference | Comparator       | Timers                                      | ССР                 | CWG                                | ZCD    | CLC                   | EUSART              | SMT                    | Angular Timer       | MSSP                 | MWG | High Current I/O | Interrupt  | Bull-up | Basic       |

|-----|-------------------------|-------------|------|-----------|------------------|---------------------------------------------|---------------------|------------------------------------|--------|-----------------------|---------------------|------------------------|---------------------|----------------------|-----|------------------|------------|---------|-------------|

| RA0 | 19                      | 16          | AN0  | DAC10UT   | C1IN+            | _                                           |                     | _                                  | _      | _                     |                     | —                      | _                   | —                    | _   | —                | IOC        | Y       | ICSPDAT     |

| RA1 | 18                      | 15          | AN1  | VREF+     | C1IN0-<br>C2IN0- | _                                           |                     | —                                  | —      | _                     |                     | —                      | _                   | —                    | —   | —                | IOC        | Y       | ICSPCLK     |

| RA2 | 17                      | 14          | AN2  | -         |                  | T0CKI <sup>(1)</sup>                        |                     | CWG1IN <sup>(1)</sup>              | ZCD1IN | _                     | -                   | _                      |                     | -                    | -   | -                | INT<br>IOC | Y       | —           |

| RA3 | 4                       | 1           | _    | —         |                  | T6IN <sup>(1)</sup>                         |                     | —                                  | _      | _                     | _                   | SMTWIN2 <sup>(1)</sup> | _                   | —                    | _   | _                | IOC        | Y       | MCLR<br>VPP |

| RA4 | 3                       | 20          | AN3  | _         |                  | T1G <sup>(1)</sup>                          |                     | _                                  | _      | _                     |                     | SMTSIG1(1)             | _                   | _                    | _   | _                | IOC        | Y       | CLKOUT      |

| RA5 | 2                       | 19          | —    | _         |                  | T1CKI <sup>(1)</sup><br>T2IN <sup>(1)</sup> |                     | —                                  | _      | CLCIN3 <sup>(1)</sup> | _                   | SMTWIN1 <sup>(1)</sup> | _                   | —                    | _   | —                | IOC        | Y       | CLKIN       |

| RB4 | 13                      | 10          | AN10 | —         | _                | _                                           | _                   | _                                  | _      | _                     | _                   | _                      | _                   | SDI(1)               | _   | _                | IOC        | Y       | —           |

| RB5 | 12                      | 9           | AN11 | _         | -                | _                                           | _                   | —                                  | _      | _                     | RX <sup>(1,3)</sup> | _                      |                     | _                    | _   | —                | IOC        | Y       | _           |

| RB6 | 11                      | 8           | _    | _         | -                | _                                           | _                   | _                                  | _      | _                     | -                   | _                      | _                   | SCK <sup>(1,3)</sup> | _   | -                | IOC        | Υ       | —           |

| RB7 | 10                      | 7           |      | _         |                  | —                                           |                     | —                                  | _      | —                     | CK <sup>(1)</sup>   | —                      | _                   | —                    | _   | —                | IOC        | Y       | —           |

| RC0 | 16                      | 13          | AN4  | —         | C2IN+            | T5CKI <sup>(1)</sup>                        | —                   | _                                  | _      | _                     | _                   | _                      | —                   | _                    | _   | _                | IOC        | Y       | —           |

| RC1 | 15                      | 12          | AN5  | —         | C1IN1-<br>C2IN1- | T4IN <sup>(1)</sup>                         | _                   | —                                  | -      | CLCIN2 <sup>(2)</sup> | _                   | SMTSIG2 <sup>(1)</sup> |                     | —                    | -   | -                | IOC        | Y       | -           |

| RC2 | 14                      | 11          | AN6  | —         | C1IN2-<br>C2IN2- | _                                           | _                   | —                                  | -      | -                     | _                   | —                      | —                   | —                    | -   | —                | IOC        | Y       | —           |

| RC3 | 7                       | 4           | AN7  | —         | C1IN3-<br>C2IN3- | T5G <sup>(1)</sup>                          | CCP2 <sup>(1)</sup> | —                                  | _      | CLCIN0 <sup>(1)</sup> | _                   | —                      | ATCC <sup>(1)</sup> | —                    | _   | —                | IOC        | Y       | -           |

| RC4 | 6                       | 3           | _    | _         | _                | T3G <sup>(1)</sup>                          | _                   | _                                  | —      | CLCIN1 <sup>(1)</sup> | _                   | _                      | _                   | _                    | —   | HIC4             | IOC        | Y       | —           |

| RC5 | 5                       | 2           | _    | —         | _                | T3CKI <sup>(1)</sup>                        | CCP1 <sup>(1)</sup> | —                                  | _      | —                     | _                   | —                      | ATIN <sup>(1)</sup> | —                    | _   | HIC5             | IOC        | Y       | _           |

| RC6 | 8                       | 5           | AN8  | _         | _                | _                                           | _                   | _                                  | _      | _                     | —                   | _                      | _                   | SS <sup>(1)</sup>    | _   | _                | IOC        | Y       | _           |

| RC7 | 9                       | 6           | AN9  | _         |                  | —                                           |                     | _                                  | _      | _                     |                     | _                      |                     | —                    | _   | _                | IOC        | Y       | _           |

| Vdd | 1                       | 18          | _    | _         | _                | —                                           |                     | _                                  | _      | _                     | _                   | _                      |                     | _                    | _   | _                | _          | _       | _           |

| Vss | 20                      | 17          | _    | _         |                  | _                                           |                     | _                                  | _      | _                     |                     | _                      |                     | —                    | _   | _                |            | _       | _           |

|     |                         |             |      |           |                  |                                             |                     | vith the PPS in<br>cted as a digit |        |                       | e PPS out           | tput selection re      | gisters.            |                      |     |                  |            |         |             |

#### TABLE 4: 20-PIN ALLOCATION TABLE (PIC16(L)F1619)

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers.

These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections. 3:

| Name                                                  | Function | Input<br>Type | Output<br>Type | Description                             |

|-------------------------------------------------------|----------|---------------|----------------|-----------------------------------------|

| RA0/AN0/C1IN+/DAC1OUT1/                               | RA0      | TTL/ST        | CMOS/OD        | General purpose I/O.                    |

| ICSPDAT                                               | AN0      | AN            | —              | ADC Channel input.                      |

|                                                       | C1IN+    | AN            | _              | Comparator positive input.              |

|                                                       | DAC1OUT1 | _             | AN             | Digital-to-Analog Converter output.     |

|                                                       | ICSPDAT  | ST            | CMOS           | ICSP™ Data I/O.                         |

| RA1/AN1/VREF+/C1IN0-/C2IN0-/                          | RA1      | TTL/ST        | CMOS/OD        | General purpose I/O.                    |

| ICSPCLK                                               | AN1      | AN            | —              | ADC Channel input.                      |

|                                                       | VREF+    | AN            | —              | Voltage Reference input.                |

|                                                       | C1IN0-   | AN            | —              | Comparator negative input.              |

|                                                       | C2IN0-   | AN            | CMOS/OD        | Comparator negative input.              |

|                                                       | ICSPCLK  | ST            | —              | ICSP Programming Clock.                 |

| RA2/AN2/T0CKI <sup>(1)</sup> /CWG1IN <sup>(1)</sup>   | RA2      | TTL/ST        | CMOS/OD        | General purpose I/O.                    |

| ZCD1IN/INT                                            | AN2      | AN            | _              | ADC Channel input.                      |

|                                                       | TOCKI    | TTL/ST        | —              | Timer0 clock input.                     |

|                                                       | CWG1IN   | TTL/ST        | _              | CWG complementary input.                |

|                                                       | ZCD1IN   | AN            | _              | Zero-Cross Detect input.                |

|                                                       | INT      | TTL/ST        | —              | External interrupt.                     |

| RA3/VPP/T6IN <sup>(1)</sup> /SMTWIN2 <sup>(1)</sup> / | RA3      | TTL/ST        | —              | General purpose input with IOC and WPU. |

| MCLR                                                  | Vpp      | HV            | _              | Programming voltage.                    |

|                                                       | T6IN     | TTL/ST        | —              | Timer6 input.                           |

|                                                       | SMTWIN2  | TTL/ST        | —              | SMT2 window input.                      |

|                                                       | MCLR     | TTL/ST        | —              | Master Clear with internal pull-up.     |

| RA4/AN3/T1G <sup>(1)</sup> /SMTSIG1 <sup>(1)</sup> /  | RA4      | TTL/ST        | CMOS/OD        | General purpose I/O.                    |

| CLKOUT                                                | AN3      | AN            | _              | ADC Channel input.                      |

|                                                       | T1G      | TTL/ST        | —              | Timer1 Gate input.                      |

|                                                       | SMTSIG1  | TTL/ST        | —              | SMT1 signal input.                      |

|                                                       | CLKOUT   | _             | CMOS           | Fosc/4 output.                          |

| RA5/CLKIN/T1CKI <sup>(1)</sup> /T2IN <sup>(1)</sup> / | RA5      | TTL/ST        | CMOS/OD        | General purpose I/O.                    |

| SMTWIN1 <sup>(1)</sup>                                | CLKIN    | CMOS          | —              | External clock input (EC mode).         |

|                                                       | T1CKI    | TTL/ST        | —              | Timer1 clock input.                     |

|                                                       | T2IN     | TTL/ST        | —              | Timer2 input.                           |

|                                                       | SMTWIN1  | TTL/ST        | —              | SMT1 window input.                      |

| RC0/AN4/C2IN+/T5CKI <sup>(1)</sup> /                  | RC0      | TTL/ST        | CMOS/OD        | General purpose I/O.                    |

| SCK <sup>(1)</sup>                                    | AN4      | AN            | —              | ADC Channel input.                      |

|                                                       | C2IN+    | AN            | —              | Comparator positive input.              |

|                                                       | T5CKI    | TTL/ST        |                | Timer5 clock input.                     |

|                                                       | SCK      | ST            | CMOS           | SPI clock.                              |

TABLE 1-2: PIC16(L)F1615 PINOUT DESCRIPTION

Legend:AN= Analog input or outputCMOS= CMOS compatible input or outputOD=Open-DrainTTL= TTL compatible inputST=Schmitt Trigger input with CMOS levels $I^2C^{TM}$ =Schmitt Trigger input with  $I^2C^{TM}$ HV= High VoltageXTAL=Crystallevels

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-1.

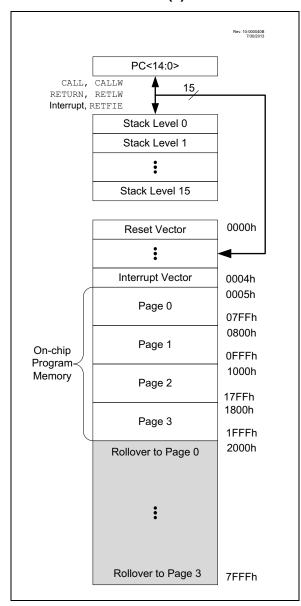

#### FIGURE 3-1: PROGRAM MEMORY MAP AND STACK FOR PIC16(L)F1615/9

# 3.2.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

#### 3.2.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

| EXAMPLE 3-1:  | RETLW INSTRUCTION              |

|---------------|--------------------------------|

| constants     |                                |

| BRW           | ;Add Index in W to             |

|               | <pre>;program counter to</pre> |

|               | ;select data                   |

| RETLW DATA0   | ;Index0 data                   |

| RETLW DATA1   | ;Index1 data                   |

| RETLW DATA2   |                                |

| RETLW DATA3   |                                |

|               |                                |

|               |                                |

| my_function   |                                |

| ; LOTS OF CO  | DDE                            |

| MOVLW D.      | ATA_INDEX                      |

| call constant | ts                             |

| ; THE CONSTR  | ANT IS IN W                    |

|               |                                |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available, so the older table read method must be used.

#### 3.2.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH operator will set bit<7> if a label points to a location in program memory.

| EXAMPLE 3-2: | ACCESSING PROGRAM |

|--------------|-------------------|

|              | MEMORY VIA FSR    |

| constants                          |

|------------------------------------|

| DW DATAO ;First constant           |

| DW DATA1 ;Second constant          |

| DW DATA2                           |

| DW DATA3                           |

| my_function                        |

| ; LOTS OF CODE                     |

| MOVLW DATA_INDEX                   |

| ADDLW LOW constants                |

| MOVWF FSR1L                        |

| MOVLW HIGH constants;MSb sets      |

| automatically                      |

| MOVWF FSR1H                        |

| BTFSC STATUS, C ;carry from ADDLW? |

| INCF FSR1h, f ;yes                 |

| MOVIW 0[FSR1]                      |

| ;THE PROGRAM MEMORY IS IN W        |

# TABLE 3-14: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr               | Name     | Bit 7         | Bit 6    | Bit 5    | Bit 4       | Bit 3    | Bit 2    | Bit 1        | Bit 0    | Value on<br>POR, BOR | Value on all other Resets |

|--------------------|----------|---------------|----------|----------|-------------|----------|----------|--------------|----------|----------------------|---------------------------|

| Banks 30           |          |               |          |          |             |          |          |              |          |                      |                           |

| F0Ch<br>to<br>F0Eh | _        | Unimplemented | l        |          |             |          |          |              |          | _                    | —                         |

| F0Fh               | CLCDATA  | _             | —        | _        | —           | MLC4OUT  | MLC3OUT  | MLC2OUT      | MLC1OUT  | 0000                 | 0000                      |

| F10h               | CLC1CON  | LC1EN         | —        | LC1OUT   | LC1INTP     | LC1INTN  |          | LC1MODE<2:0> | •        | 0-x0 0000            | 0-x0 0000                 |

| F11h               | CLC1POL  | LC1POL        | —        |          | —           | LC1G4POL | LC1G3POL | LC1G2POL     | LC1G1POL | x xxxx               | x xxxx                    |

| F12h               | CLC1SEL0 | _             | _        |          |             | LC1D1    | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F13h               | CLC1SEL1 | _             | _        |          |             | LC1D2    | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F14h               | CLC1SEL2 | —             | _        |          |             | LC1D3    | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F15h               | CLC1SEL3 | _             | _        |          |             | LC1D4    | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F16h               | CLC1GLS0 | LC1G1D4T      | LC1G1D4N | LC1G1D3T | LC1G1D3N    | LC1G1D2T | LC1G1D2N | LC1G1D1T     | LC1G1D1N | xxxx xxxx            | xxxx xxxx                 |

| F17h               | CLC1GLS1 | LC1G2D4T      | LC1G2D4N | LC1G2D3T | LC1G2D3N    | LC1G2D2T | LC1G2D2N | LC1G2D1T     | LC1G2D1N | xxxx xxxx            | xxxx xxxx                 |

| F18h               | CLC1GLS2 | LC1G3D4T      | LC1G3D4N | LC1G3D3T | LC1G3D3N    | LC1G3D2T | LC1G3D2N | LC1G3D1T     | LC1G3D1N | xxxx xxxx            | xxxx xxxx                 |

| F19h               | CLC1GLS3 | LC1G4D4T      | LC1G4D4N | LC1G4D3T | LC1G4D3N    | LC1G4D2T | LC1G4D2N | LC1G4D1T     | LC1G4D1N | xxxx xxxx            | xxxx xxxx                 |

| F1Ah               | CLC2CON  | LC2EN         | _        | LC2OUT   | LC2INTP     | LC2INTN  |          | LC2MODE<2:0> | •        | 0-x0 0000            | 0-x0 0000                 |

| F1Bh               | CLC2POL  | LC2POL        | —        | _        | —           | LC2G4POL | LC2G3POL | LC2G2POL     | LC2G1POL | x xxxx               | x xxxx                    |

| F1Ch               | CLC2SEL0 | _             | _        |          |             | LC2D1    | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F1Dh               | CLC2SEL1 | —             | —        |          |             | LC2D2    | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F1Eh               | CLC2SEL2 | _             | _        |          |             | LC2D3    | S<5:0>   |              |          | xx xxxx              | xx xxxx                   |

| F1Fh               | CLC2SEL3 | _             | —        |          | LC2D4S<5:0> |          |          |              |          |                      |                           |

| F20h               | CLC2GLS0 | LC2G1D4T      | LC2G1D4N | LC2G1D3T | LC2G1D3N    | LC2G1D2T | LC2G1D2N | LC2G1D1T     | LC2G1D1N | xxxx xxxx            | xxxx xxxx                 |

| F21h               | CLC2GLS1 | LC2G2D4T      | LC2G2D4N | LC2G2D3T | LC2G2D3N    | LC2G2D2T | LC2G2D2N | LC2G2D1T     | LC2G2D1N | xxxx xxxx            | xxxx xxxx                 |

| F22h               | CLC2GLS2 | LC2G3D4T      | LC2G3D4N | LC2G3D3T | LC2G3D3N    | LC2G3D2T | LC2G3D2N | LC2G3D1T     | LC2G3D1N | xxxx xxxx            | xxxx xxxx                 |

| F23h               | CLC2GLS3 | LC2G4D4T      | LC2G4D4N | LC2G4D3T | LC2G4D3N    | LC2G4D2T | LC2G4D2N | LC2G4D1T     | LC2G4D1N | xxxx xxxx            | xxxx xxxx                 |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** PIC16F1615/9 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1615 only.

4: PIC16(L)F1619 only.

#### 5.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<1:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run-time. See Section5.3 "Clock Switching"for more information.

In **INTOSC** mode, CLKIN is available for general purpose I/O. CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators and a dedicated Phase Lock Loop, HFPLL that can produce one of three internal system clock sources.

- The HFINTOSC (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase Lock Loop, HFPLL. The frequency of the HFINTOSC can be useradjusted via software using the OSCTUNE register (Register 5-3).

- 2. The **MFINTOSC** (Medium-Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 3. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

#### 5.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 16 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of multiple frequencies derived from the HFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section5.2.2.8 "Internal Oscillator Clock Switch Timing**" for more information.

The HFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<1:0> = 00, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'.

A fast start-up oscillator allows internal circuits to power up and stabilize before switching to HFINTOSC.

The High-Frequency Internal Oscillator Ready bit (HFIOFR) of the OSCSTAT register indicates when the HFINTOSC is running.

The High-Frequency Internal Oscillator Status Locked bit (HFIOFL) of the OSCSTAT register indicates when the HFINTOSC is running within 2% of its final value.

The High-Frequency Internal Oscillator Stable bit (HFIOFS) of the OSCSTAT register indicates when the HFINTOSC is running within 0.5% of its final value.

#### 5.2.2.2 MFINTOSC

The Medium-Frequency Internal Oscillator (MFINTOSC) is a factory calibrated 500 kHz internal clock source. The frequency of the MFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the MFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of nine frequencies derived from the MFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section5.2.2.8 "Internal Oscillator Clock Switch Timing**" for more information.

The MFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<1:0> = 00, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

The Medium-Frequency Internal Oscillator Ready bit (MFIOFR) of the OSCSTAT register indicates when the MFINTOSC is running.

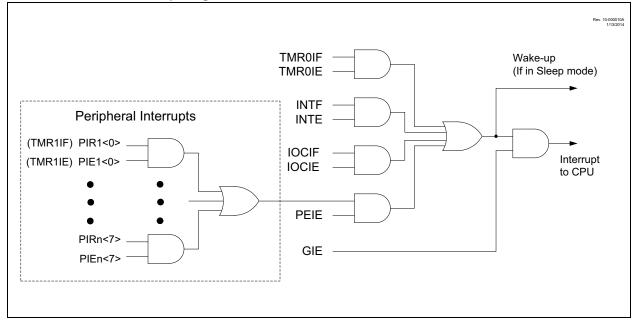

# 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 7-1.

FIGURE 7-1: Interrupt Logic

| R/W-0/       | 0 R/W-0/0                              | R/W-0/0                                                         | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0           | R/W-0/0    |  |  |  |  |  |  |

|--------------|----------------------------------------|-----------------------------------------------------------------|-----------------|----------------|------------------|-------------------|------------|--|--|--|--|--|--|

| SCANI        | F CRCIF                                | SMT2PWAIF                                                       | SMT2PRAIF       | SMT2IF         | SMT1PWAIF        | SMT1PRAIF         | SMT1IF     |  |  |  |  |  |  |

| bit 7        |                                        |                                                                 |                 |                |                  |                   | bit        |  |  |  |  |  |  |

|              |                                        |                                                                 |                 |                |                  |                   |            |  |  |  |  |  |  |

| Legend:      |                                        |                                                                 |                 |                |                  |                   |            |  |  |  |  |  |  |

| R = Reada    |                                        | W = Writable I                                                  | oit             |                | mented bit, read |                   |            |  |  |  |  |  |  |

| u = Bit is u | 0                                      | x = Bit is unkn                                                 |                 | -n/n = Value   | at POR and BO    | R/Value at all ot | her Resets |  |  |  |  |  |  |

| '1' = Bit is | set                                    | '0' = Bit is clea                                               | ared            |                |                  |                   |            |  |  |  |  |  |  |

| bit 7        | SCANIF: So                             | canner Interrupt                                                | Flag bit        |                |                  |                   |            |  |  |  |  |  |  |

|              |                                        | Interrupt is pending                                            |                 |                |                  |                   |            |  |  |  |  |  |  |

| bit 6        | CRCIF: CR                              | C Interrupt Flag                                                | bit             |                |                  |                   |            |  |  |  |  |  |  |

|              | 1 = Interrup                           | t is pending<br>t is not pending                                |                 |                |                  |                   |            |  |  |  |  |  |  |

| bit 5        | •                                      |                                                                 | Width Acquisiti | on Interrunt F | lag hit          |                   |            |  |  |  |  |  |  |

| bito         | 1 = Interrup                           | : SMT2 Pulse Width Acquisition Interrupt Flag bit<br>is pending |                 |                |                  |                   |            |  |  |  |  |  |  |

|              |                                        | t is not pending                                                |                 |                |                  |                   |            |  |  |  |  |  |  |

| bit 4        | SMT2PRAI                               | SMT2PRAIF: SMT2 Period Acquisition Interrupt Flag bit           |                 |                |                  |                   |            |  |  |  |  |  |  |

|              |                                        | 1 = Interrupt is pending                                        |                 |                |                  |                   |            |  |  |  |  |  |  |

|              | -                                      | 0 = Interrupt is not pending                                    |                 |                |                  |                   |            |  |  |  |  |  |  |

| bit 3        |                                        | SMT2 Match Interrupt Flag bit                                   |                 |                |                  |                   |            |  |  |  |  |  |  |

|              |                                        | 1 = Interrupt is pending<br>0 = Interrupt is not pending        |                 |                |                  |                   |            |  |  |  |  |  |  |

| bit 2        | -                                      | SMT1PWAIF: SMT1 Pulse Width Acquisition Interrupt Flag bit      |                 |                |                  |                   |            |  |  |  |  |  |  |

|              |                                        | 1 = Interrupt is pending                                        |                 |                |                  |                   |            |  |  |  |  |  |  |

|              | 0 = Interrup                           | t is not pending                                                |                 |                |                  |                   |            |  |  |  |  |  |  |

| bit 1        |                                        | F: SMT1 Period                                                  | Acquisition Int | errupt Flag bi | t                |                   |            |  |  |  |  |  |  |

|              | 1 = Interrup                           |                                                                 |                 |                |                  |                   |            |  |  |  |  |  |  |

| hit O        |                                        | t is not pending                                                | unt Flog bit    |                |                  |                   |            |  |  |  |  |  |  |

| bit 0        | 1 = Interrup                           | AT1 Match Inter                                                 | upt Flag bit    |                |                  |                   |            |  |  |  |  |  |  |

|              |                                        | t is not pending                                                |                 |                |                  |                   |            |  |  |  |  |  |  |

|              | ·                                      | 1 0                                                             |                 |                |                  |                   |            |  |  |  |  |  |  |

| Note:        | Interrupt flag bits                    |                                                                 |                 |                |                  |                   |            |  |  |  |  |  |  |

|              | condition occurs,<br>its corresponding |                                                                 |                 |                |                  |                   |            |  |  |  |  |  |  |

|              | Enable bit, GIE                        |                                                                 |                 |                |                  |                   |            |  |  |  |  |  |  |

|              | User software                          | should ens                                                      | ure the         |                |                  |                   |            |  |  |  |  |  |  |

|              | appropriate interr                     |                                                                 | clear prior     |                |                  |                   |            |  |  |  |  |  |  |

|              | to enabling an int                     | terrupt.                                                        |                 |                |                  |                   |            |  |  |  |  |  |  |

# REGISTER 7-10: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4

| D DDO - 4-0 | Outrast Olamal          | 1     | PIC16(L)F161 | 9     | PIC16(L)F1615 |       |  |

|-------------|-------------------------|-------|--------------|-------|---------------|-------|--|

| RxyPPS<4:0> | Output Signal           | PORTA | PORTB        | PORTC | PORTA         | PORTO |  |

| llxxx       | Reserved                | •     | •            | ٠     | •             | •     |  |

| 10111       | Reserved                | •     | •            | •     | •             | •     |  |

| 10110       | Reserved                | •     | •            | •     | •             | •     |  |

| 10101       | Reserved                | •     | •            | •     | •             | •     |  |

| 10100       | Reserved                | •     | •            | •     | •             | •     |  |

| 10011       | DT                      | •     | •            | •     | •             | •     |  |

| 10010       | TX/CK                   | •     | •            | •     | •             | •     |  |

| 10001       | SDO/SDA <sup>(1)</sup>  | •     | •            | •     | •             | •     |  |

| 10000       | SCK/SCL <sup>(1)</sup>  | •     | •            | •     | •             | •     |  |

| 01111       | PWM4_out                | •     | •            | •     | •             | •     |  |

| 01110       | PWM3_out                | •     | •            | •     | •             | •     |  |

| 01101       | CCP2_out                | •     | •            | •     | •             | •     |  |

| 01100       | CCP1_out                | •     | •            | •     | •             | •     |  |

| 01011       | CWG1OUTD <sup>(1)</sup> | •     | •            | •     | •             | •     |  |

| 01010       | CWG1OUTC <sup>(1)</sup> | •     | •            | •     | •             | •     |  |

| 01001       | CWG1OUTB <sup>(1)</sup> | •     | •            | ٠     | •             | •     |  |

| 01000       | CWG1OUTA <sup>(1)</sup> | •     | •            | •     | •             | •     |  |

| 00111       | LC4_out                 | •     | •            | •     | •             | •     |  |

| 00110       | LC3_out                 | •     | •            | •     | •             | •     |  |

| 00101       | LC2_out                 | •     | •            | •     | •             | •     |  |

| 00100       | LC1_out                 | •     | •            | •     | •             | •     |  |

| 00011       | ZCD1_out                | •     | •            | •     | •             | •     |  |

| 00010       | sync_C2OUT              | •     | •            | •     | •             | •     |  |

| 00001       | sync_C1OUT              | •     | •            | •     | •             | •     |  |

| 00000       | LATxy                   | •     | •            | •     | •             | •     |  |

| TABLE 13-2: AV | AILABLE PORTS FOR OUTPUT BY PERIPHERAL <sup>(2)</sup> |

|----------------|-------------------------------------------------------|

|----------------|-------------------------------------------------------|

**Note 1:** TRIS control is overridden by the peripheral as required.

2: Unsupported peripherals will output a '0'.

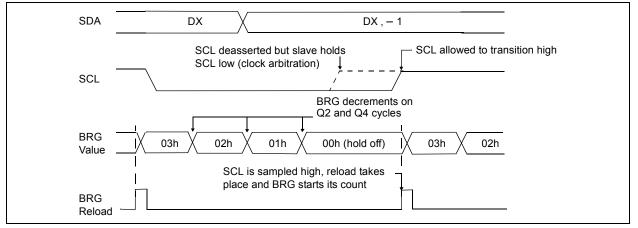

#### 24.6.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 24-25).

#### FIGURE 24-25: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

#### 24.6.3 WCOL STATUS FLAG

If the user writes the SSPxBUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSPxBUF was attempted while the module was not idle.

| Note: | Because queuing of events is not allowed,<br>writing to the lower five bits of SSPxCON2 |  |  |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | is disabled until the Start condition is complete.                                      |  |  |  |  |  |  |  |  |  |  |

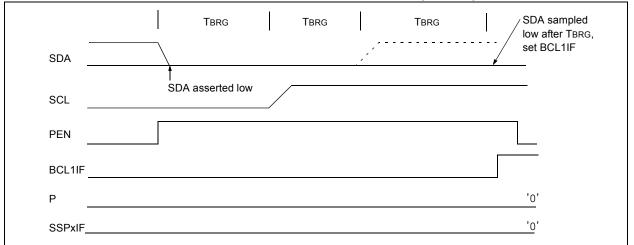

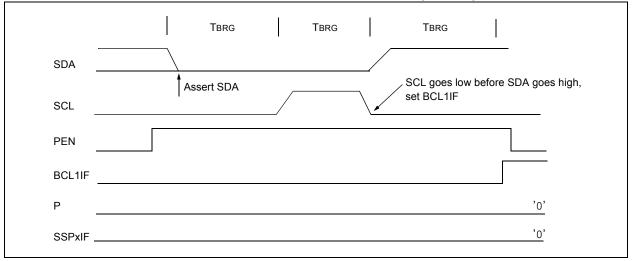

#### 24.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to zero. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 24-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 24-39).

#### FIGURE 24-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 24-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

| R-0/0                 | R/W-0/0                                                                                                                                                  | R/W-0/0                             | R/W-0/0                       | R/W-0/0                      | R/W-0/0           | R/W-0/0             | R/W-0/0        |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------|------------------------------|-------------------|---------------------|----------------|--|--|--|--|

| ACKTIM <sup>(3)</sup> | PCIE                                                                                                                                                     | SCIE                                | BOEN                          | SDAHT                        | SBCDE             | AHEN                | DHEN           |  |  |  |  |

| bit 7                 |                                                                                                                                                          |                                     |                               |                              |                   |                     | bit            |  |  |  |  |

|                       |                                                                                                                                                          |                                     |                               |                              |                   |                     |                |  |  |  |  |

| Legend:               |                                                                                                                                                          |                                     |                               |                              |                   |                     |                |  |  |  |  |

| R = Readable          |                                                                                                                                                          | W = Writable                        |                               | -                            | mented bit, read  |                     |                |  |  |  |  |

| u = Bit is unch       | 0                                                                                                                                                        | x = Bit is unk                      |                               | -n/n = Value                 | at POR and BO     | R/Value at all c    | other Resets   |  |  |  |  |

| '1' = Bit is set      |                                                                                                                                                          | '0' = Bit is cle                    | ared                          |                              |                   |                     |                |  |  |  |  |

| bit 7                 | ACKTIM: Act                                                                                                                                              | knowledge Tim                       | e Status bit (l <sup>2</sup>  | <sup>2</sup> C mode only)    | (3)               |                     |                |  |  |  |  |

|                       |                                                                                                                                                          |                                     |                               |                              | e, set on eighth  | falling edge of     | SCL clock      |  |  |  |  |

|                       | 0 = Not an Ad                                                                                                                                            | cknowledge se                       | quence, cleare                | ed on 9 <sup>th</sup> rising | edge of SCL c     | lock                |                |  |  |  |  |

| bit 6                 |                                                                                                                                                          | ondition Interru                    | •                             | •                            | y)                |                     |                |  |  |  |  |

|                       |                                                                                                                                                          | terrupt on dete                     |                               |                              |                   |                     |                |  |  |  |  |

| L:1 C                 | •                                                                                                                                                        | ection interrupts                   |                               |                              |                   |                     |                |  |  |  |  |

| bit 5                 |                                                                                                                                                          |                                     |                               | •                            |                   |                     |                |  |  |  |  |

|                       | <ol> <li>Enable interrupt on detection of Start or Restart conditions</li> <li>Start detection interrupts are disabled<sup>(2)</sup></li> </ol>          |                                     |                               |                              |                   |                     |                |  |  |  |  |

| bit 4                 |                                                                                                                                                          | r Overwrite En                      |                               |                              |                   |                     |                |  |  |  |  |

|                       | In SPI Slave                                                                                                                                             | <u>mode:</u> (1)                    |                               |                              |                   |                     |                |  |  |  |  |

|                       | 1 = SSP1BUF updates every time that a new data byte is shifted in ignoring the BF bit                                                                    |                                     |                               |                              |                   |                     |                |  |  |  |  |

|                       | 0 = If new byte is received with BF bit of the SSP1STAT register already set, SSPOV bit of th<br>SSP1CON1 register is set, and the buffer is not updated |                                     |                               |                              |                   |                     |                |  |  |  |  |

|                       |                                                                                                                                                          | mode and SP                         |                               |                              | upualeu           |                     |                |  |  |  |  |

|                       | This bit is                                                                                                                                              | s ignored.                          |                               | _                            |                   |                     |                |  |  |  |  |

|                       | In $\frac{I = C Slave mode:}{1 = SSP1BUF}$ is updated and $\overline{ACK}$ is generated for a received address/data byte, ignoring the                   |                                     |                               |                              |                   |                     |                |  |  |  |  |

|                       |                                                                                                                                                          | of the SSPOV                        |                               |                              | or a received ad  | dress/data byte     | e, ignoring ti |  |  |  |  |

|                       |                                                                                                                                                          | 1BUF is only u                      |                               |                              | ır                |                     |                |  |  |  |  |

| bit 3                 | SDAHT: SDA                                                                                                                                               | Hold Time Se                        | lection bit (I <sup>2</sup> C | mode only)                   |                   |                     |                |  |  |  |  |

|                       |                                                                                                                                                          | of 300 ns hold                      |                               |                              |                   |                     |                |  |  |  |  |

|                       |                                                                                                                                                          | of 100 ns hold                      |                               |                              |                   |                     |                |  |  |  |  |

| bit 2                 |                                                                                                                                                          |                                     |                               | •                            | C Slave mode o    | •                   |                |  |  |  |  |

|                       |                                                                                                                                                          | ng edge of SC<br>the PIR2 regis     |                               |                              | en the module is  | s outputting a l    | nigh state, th |  |  |  |  |

|                       | 1 = Enable sl                                                                                                                                            | ave bus collisi                     | on interrupts                 |                              |                   |                     |                |  |  |  |  |

|                       |                                                                                                                                                          | s collision inter                   | -                             |                              |                   |                     |                |  |  |  |  |

| bit 1                 |                                                                                                                                                          | ess Hold Enabl                      | •                             | • /                          |                   |                     |                |  |  |  |  |

|                       |                                                                                                                                                          |                                     |                               |                              | ching received    | address byte; (     | CKP bit of the |  |  |  |  |

|                       |                                                                                                                                                          | DN1 register wi<br>holding is disal |                               | nd the SCL WI                | li de neid low.   |                     |                |  |  |  |  |

| bit 0                 |                                                                                                                                                          | Hold Enable bi                      |                               | ode only)                    |                   |                     |                |  |  |  |  |

|                       |                                                                                                                                                          |                                     | •                             | • ·                          | ed data byte; sla | ave hardware c      | lears the CK   |  |  |  |  |

|                       |                                                                                                                                                          | SSP1CON1 r                          |                               |                              |                   |                     |                |  |  |  |  |

|                       | 0 = Data hold                                                                                                                                            | ling is disabled                    |                               |                              |                   |                     |                |  |  |  |  |

| Note 1: For           | r daisy-chained                                                                                                                                          | SPI operation:                      | allows the use                | er to ignore all             | but the last rece | eived byte. SSP     | OV is still se |  |  |  |  |

| wh                    | en a new byte is                                                                                                                                         |                                     |                               |                              | ues to write the  |                     |                |  |  |  |  |

|                       | P1BUF.                                                                                                                                                   |                                     |                               |                              |                   |                     |                |  |  |  |  |

| 2: Th                 | is bit has no effe                                                                                                                                       | ect in Slave mo                     | odes that Start               | and Stop cond                | dition detection  | is explicitly liste | ed as enable   |  |  |  |  |

#### REGISTER 24-4: SSP1CON3: SSP CONTROL REGISTER 3

3: The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is set.

#### 27.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 27-4.

## EQUATION 27-4: PWM RESOLUTION

Resolution =  $\frac{\log[4(PR2 + 1)]}{\log(2)}$  bits

**Note:** If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

#### TABLE 27-1:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 0.31 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

### TABLE 27-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 0.31 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 27.1.6 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 27.1.7 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to **Section 5.0 "Oscillator Module"** for additional details.

#### 27.1.8 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the PWM registers to their Reset states.

#### 30.6.2 GATED TIMER MODE

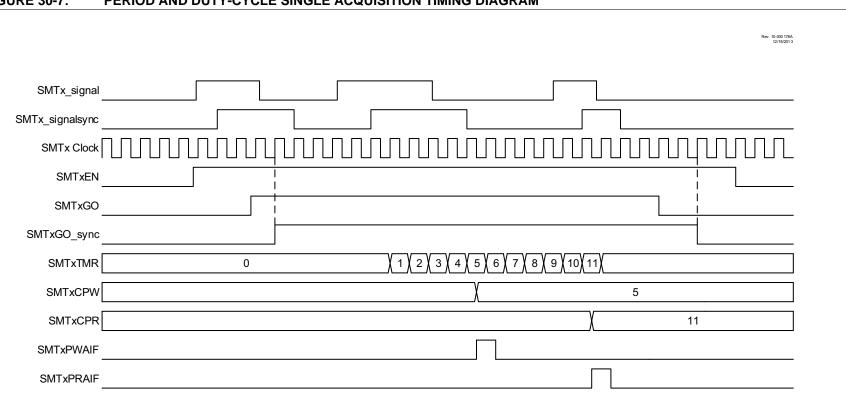

Gated Timer mode uses the SMTSIGx input to control whether or not the SMTxTMR will increment. Upon a falling edge of the external signal, the SMTxCPW register will update to the current value of the SMTxTMR. Example waveforms for both repeated and single acquisitions are provided in Figure 30-4 and Figure 30-5.

### FIGURE 30-7: PERIOD AND DUTY-CYCLE SINGLE ACQUISITION TIMING DIAGRAM

# REGISTER 30-4: SMTxCLK: SMT CLOCK SELECTION REGISTER

| U-0                                     | U-0                                 | U-0                        | U-0                                                   | U-0                            | R/W-0/0 | R/W-0/0   | R/W-0/0 |  |

|-----------------------------------------|-------------------------------------|----------------------------|-------------------------------------------------------|--------------------------------|---------|-----------|---------|--|

| _                                       |                                     | —                          |                                                       | _                              |         | CSEL<2:0> |         |  |

| bit 7                                   |                                     |                            |                                                       | ·                              |         |           | bit 0   |  |

|                                         |                                     |                            |                                                       |                                |         |           |         |  |

| Legend:                                 |                                     |                            |                                                       |                                |         |           |         |  |

| R = Readable bit W = Writable bit       |                                     | bit                        | U = Unimplemented bit, read as '0'                    |                                |         |           |         |  |

| u = Bit is unchanged x = Bit is unknown |                                     | nown                       | -n/n = Value at POR and BOR/Value at all other Resets |                                |         |           |         |  |

| '1' = Bit is set '0' = Bit is cleared   |                                     |                            | ared                                                  | q = Value depends on condition |         |           |         |  |

|                                         |                                     |                            |                                                       |                                |         |           |         |  |

| bit 7-3                                 | Unimplemen                          | Unimplemented: Read as '0' |                                                       |                                |         |           |         |  |

| bit 2-0                                 | CSEL<2:0>: SMT Clock Selection bits |                            |                                                       |                                |         |           |         |  |

|                                         | 111 = Reser                         | ved                        |                                                       |                                |         |           |         |  |

| 110 = AT1_perclk                        |                                     |                            |                                                       |                                |         |           |         |  |

|                                         | 101 = MFINT                         | TOSC                       |                                                       |                                |         |           |         |  |

|                                         | 100 = MFINT                         | OSC/16                     |                                                       |                                |         |           |         |  |

|                                         | 011 = LFINT                         | OSC                        |                                                       |                                |         |           |         |  |

|                                         |                                     |                            |                                                       |                                |         |           |         |  |

010 = HFINTOSC 16 MHz

001 = Fosc/4

000 = Fosc

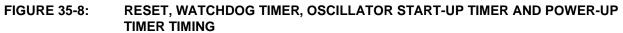

# 35.2 Standard Operating Conditions

The standard operating conditions for any device are defined as:  $V \text{DDMIN} \leq V \text{DD} \leq V \text{DDMAX}$ Operating Voltage: Operating Temperature: TA MIN  $\leq$  TA  $\leq$  TA MAX VDD — Operating Supply Voltage<sup>(1)</sup> PIC16LF1615/9 PIC16F1615/9 TA — Operating Ambient Temperature Range Industrial Temperature TA MIN.....--40°C **Extended Temperature** Ta MIN.....--40°C

Note 1: See Parameter D001, DS Characteristics: Supply Voltage.

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

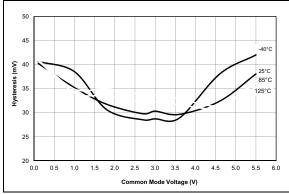

**FIGURE 36-91:** Comparator Hysteresis, NP Mode (CxSP = 1), VDD = 5.5V, Typical Measured Values, PIC16F1615/9 Only.

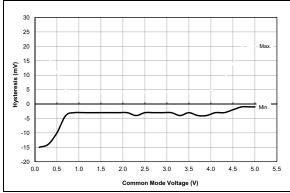

**FIGURE 36-92:** Comparator Offset, NP Mode (CxSP = 1), VDD = 5.0V, Typical Measured Values at 25°C, PIC16F1615/9 Only.

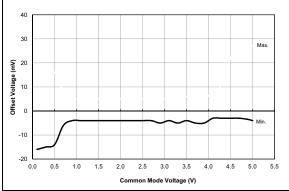

**FIGURE 36-93:** Comparator Offset, NP Mode (CxSP = 1), VDD = 5.5V, Typical Measured Values From -40°C to 125°C, PIC16F1615/9 Only.

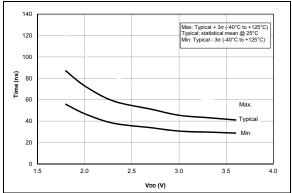

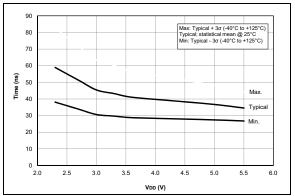

**FIGURE 36-94:** Comparator Response Time Over Voltage, NP Mode (CxSP = 1), Typical Measured Values, PIC16LF1615/9 Only.

**FIGURE 36-95:** Comparator Response Time Over Voltage, NP Mode (CxSP = 1), Typical Measured Values, PIC16F1615/9 Only.

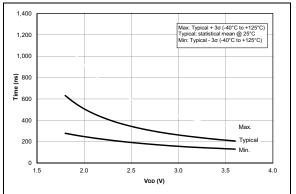

**FIGURE 36-96:** Comparator Output Filter Delay Time Over Temp., NP Mode (CxSP = 1), Typical Measured Values, PIC16LF1615/9 Only.

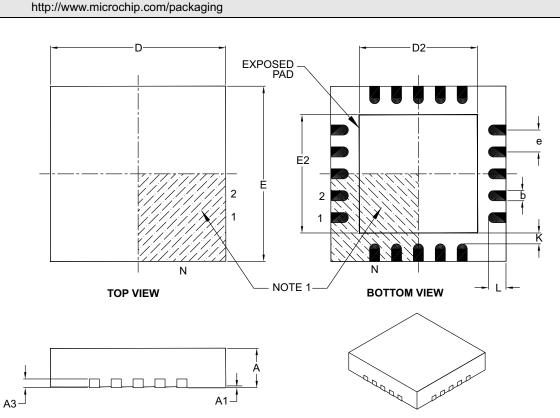

For the most current package drawings, please see the Microchip Packaging Specification located at

#### 20-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

Units MILLIMETERS Dimension Limits MIN NOM MAX Number of Pins Ν 20 Pitch 0.50 BSC е **Overall Height** А 0.80 0.90 1.00 Standoff A1 0.00 0.02 0.05 Contact Thickness A3 0.20 REF Overall Width 4.00 BSC Е Exposed Pad Width E2 2.60 2.70 2.80 **Overall Length** D 4.00 BSC Exposed Pad Length D2 2.60 2.70 2.80 Contact Width 0.18 0.25 0.30 b Contact Length L 0.30 0.40 0.50 Contact-to-Exposed Pad Κ 0.20 \_ \_

#### Notes:

Note:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-126B