Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                |                                                                            |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1619-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-11:PIC16(L)F1615/9 MEMORYMAP, BANK 30

|         | •             |                                                 |

|---------|---------------|-------------------------------------------------|

|         |               | Bank 30                                         |

|         | F0Ch          |                                                 |

|         | F0Dh          |                                                 |

|         | F0Eh          |                                                 |

|         | F0Fh          | CLCDATA                                         |

|         | F10h          | CLC1CON                                         |

|         | F11h          | CLC1POL                                         |

|         | F12h          | CLC1SEL0                                        |

|         | F13h          | CLC1SEL1                                        |

|         | F14h          | CLC1SEL2                                        |

|         | F15h          | CLC1SEL3                                        |

|         | F16h          | CLC1GLS0                                        |

|         | F17h          | CLC1GLS1                                        |

|         | F1711<br>F18h | CLC1GLS2                                        |

|         |               | CLC1GLS3                                        |

|         | F19h          | CLC2CON                                         |

|         | F1Ah          |                                                 |

|         | F1Bh          | CLC2POL                                         |

|         | F1Ch          | CLC2SEL0                                        |

|         | F1Dh          | CLC2SEL1                                        |

|         | F1Eh          | CLC2SEL2                                        |

|         | F1Fh          | CLC2SEL3                                        |

|         | F20h          | CLC2GLS0                                        |

|         | F21h          | CLC2GLS1                                        |

|         | F22h          | CLC2GLS2                                        |

|         | F23h          | CLC2GLS3                                        |

|         | F24h          | CLC3CON                                         |

|         | F25h          | CLC3POL                                         |

|         | F26h          | CLC3SEL0                                        |

|         | F27h          | CLC3SEL1                                        |

|         | F28h          | CLC3SEL2<br>CLC3SEL3                            |

|         | F29h<br>F2Ah  | CLC3GLS0                                        |

|         | F2An<br>F2Bh  | CLC3GLS0                                        |

|         | F2Ch          | CLC3GLS1                                        |

|         | F2Dh          | CLC3GLS3                                        |

|         | F2Eh          | CLC4CON                                         |

|         | F2Fh          | CLC4POL                                         |

|         | F30h          | CLC4SEL0                                        |

|         | F31h          | CLC4SEL1                                        |

|         | F32h          | CLC4SEL2                                        |

|         | F33h          | CLC4SEL3                                        |

|         | F34h          | CLC4GLS0                                        |

|         | F35h          | CLC4GLS1                                        |

|         | F36h          | CLC4GLS2                                        |

|         | F37h          | CLC4GLS3                                        |

|         | F38h          |                                                 |

|         |               | —                                               |

|         | F6Fh          |                                                 |

|         |               |                                                 |

| Legend: |               | Unimplemented data memory locations, ad as '0'. |

| 1       |               |                                                 |

# TABLE 3-12: PIC16(L)F1615/9 MEMORY MAP, BANK 31

|         | Bank 31                                |                 |  |  |  |  |

|---------|----------------------------------------|-----------------|--|--|--|--|

| F8Ch    |                                        |                 |  |  |  |  |

|         | Unimplemented<br>Read as '0'           |                 |  |  |  |  |

| FE3h    |                                        |                 |  |  |  |  |

| FE4h    | STATUS_SHAD                            |                 |  |  |  |  |

| FE5h    | WREG_SHAD                              |                 |  |  |  |  |

| FE6h    | BSR_SHAD                               |                 |  |  |  |  |

| FE7h    | PCLATH_SHAD                            |                 |  |  |  |  |

| FE8h    | FSR0L_SHAD                             |                 |  |  |  |  |

| FE9h    | FSR0H_SHAD                             |                 |  |  |  |  |

| FEAh    | FSR1L_SHAD                             |                 |  |  |  |  |

| FEBh    |                                        |                 |  |  |  |  |

| FECh    |                                        |                 |  |  |  |  |

| FEDh    | STKPTR                                 |                 |  |  |  |  |

| FEEh    | TOSL                                   |                 |  |  |  |  |

| FEFh    | TOSH                                   |                 |  |  |  |  |

| Logondu | - Unimplemented data ma                | monulopotiono   |  |  |  |  |

| Legend: | = Unimplemented data me<br>ead as '0'. | mory locations, |  |  |  |  |

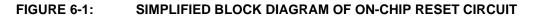

# 6.0 RESETS

There are multiple ways to reset this device:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- Low-Power Brown-Out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- · Stack Underflow

- Programming mode exit

To allow VDD to stabilize, an optional power-up timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-chip Reset Circuit is shown in Figure 6-1.

# 6.13 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 6-2.

# 6.14 Register Definitions: Power Control

#### REGISTER 6-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|------------|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | WDTWV      | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      | •          | •          |            |            |            |            | bit 0      |

| Legend:                     |                      |                                                       |

|-----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by hard | dware                | HS = Bit is set by hardware                           |

| R = Readable bit            | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged        | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set            | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7 | <b>STKOVF</b> : Stack Overflow Flag bit<br>1 = A Stack Overflow occurred<br>0 = A Stack Overflow has not occurred or cleared by firmware                                                                                                                                                                      |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>STKUNF:</b> Stack Underflow Flag bit<br>1 = A Stack Underflow occurred<br>0 = A Stack Underflow has not occurred or cleared by firmware                                                                                                                                                                    |

| bit 5 | <ul> <li>WDTWV: WDT Window Violation Flag bit</li> <li>1 = A WDT Window Violation Reset has not occurred or set by firmware</li> <li>0 = A WDT Window Violation Reset has occurred (a CLRWDT instruction was executed either without arming the window or outside the window (cleared by hardware)</li> </ul> |

| bit 4 | <b>RWDT</b> : Watchdog Timer Reset Flag bit<br>1 = A Watchdog Timer Reset has not occurred or set by firmware<br>0 = A Watchdog Timer Reset has occurred (cleared by hardware)                                                                                                                                |

| bit 3 | <b>RMCLR</b> : MCLR Reset Flag bit<br>1 = A MCLR Reset has not occurred or set by firmware<br>0 = A MCLR Reset has occurred (cleared by hardware)                                                                                                                                                             |

| bit 2 | <b>RI:</b> RESET Instruction Flag bit<br>1 = A RESET instruction has not been executed or set by firmware<br>0 = A RESET instruction has been executed (cleared by hardware)                                                                                                                                  |

| bit 1 | <b>POR:</b> Power-On Reset Status bit<br>1 = No Power-on Reset occurred<br>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                                                                                                                              |

| bit 0 | <b>BOR:</b> Brown-Out Reset Status bit<br>1 = No Brown-out Reset occurred<br>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurs)                                                                                                                        |

#### 9.1 Independent Clock Source

The WDT can derive its time base from either the 31 kHz LFINTOSC or 31.25 kHz MFINTOSC internal oscillators, depending on the value of either the WDTCCS<2:0> configuration bits or the WDTCS<2:0> bits of WDTCON1. Time intervals in this chapter are based on a minimum nominal interval of 1 ms. See **Section35.0 "Electrical Specifications**" for LFINTOSC and MFINTOSC tolerances.

# 9.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 9-1.

#### 9.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 9.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 9.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SEN bit of the WDTCON0 register.

WDT protection is unchanged by Sleep. See Table 9-1 for more details.

| WDTE<1:0> | SEN | Device<br>Mode | WDT<br>Mode |

|-----------|-----|----------------|-------------|

| 11        | Х   | Х              | Active      |

| 10        |     | Awake          | Active      |

| 10        | Х   | Sleep          | Disabled    |

| 0.1       | 1   | х              | Active      |

| 01        | 0   | х              | Disabled    |

| 00        | Х   | х              | Disabled    |

| TABLE 9-1: | WDT OPERATING MODES |

|------------|---------------------|

|            |                     |

# 9.3 Time-Out Period

The WDTPS bits of the WDTCON0 register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

#### 9.4 Watchdog Window

The Watchdog Timer has an optional Windowed mode that is controlled by the WDTCWS<2:0> Configuration bits and WINDOW<2:0> bits of the WDTCON1 register. In the Windowed mode, the CLRWDT instruction must occur within the allowed window of the WDT period. Any CLRWDT instruction that occurs outside of this window will trigger a window violation and will cause a WDT Reset, similar to a WDT time out. See Figure 9-2 for an example.

The window size is controlled by the WDTCWS<2:0> Configuration bits, or the WINDOW<2:0> bits of WDTCON1, if WDTCWS<2:0> = 111.

In the event of a <u>window</u> violation, a Reset will be generated and the WDTWV bit of the PCON register will be cleared. This bit is set by a POR or can be set in firmware.

### 9.5 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- Valid CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- · WDT is disabled

- · Oscillator Start-up Timer (OST) is running

- Any write to the WDTCON0 or WDTCON1 registers

#### 9.5.1 CLRWDT CONSIDERATIONS (WINDOWED MODE)

When in Windowed mode, the WDT must be armed before a CLRWDT instruction will clear the timer. This is performed by reading the WDTCON0 register. Executing a CLRWDT instruction without performing such an arming action will trigger a window violation.

See Table 9-2 for more information.

# 9.6 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting. When the device exits Sleep, the WDT is cleared again.

The WDT remains clear until the OST, if enabled, completes. See **Section5.0** "**Oscillator Module**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the event. The  $\overline{RWDT}$  bit in the PCON register can also be used. See **Section3.0** "Memory **Organization**" for more information.

#### REGISTER 9-3: WDTPSL: WDT PRESCALE SELECT LOW BYTE REGISTER (READ ONLY)

| R-0/0               | R-0/0 | R-0/0              | R-0/0 | R-0/0                 | R-0/0              | R-0/0               | R-0/0  |

|---------------------|-------|--------------------|-------|-----------------------|--------------------|---------------------|--------|

|                     |       |                    | PSCN  | Γ<7:0> <sup>(1)</sup> |                    |                     |        |

| bit 7               |       |                    |       |                       |                    |                     | bit 0  |

|                     |       |                    |       |                       |                    |                     |        |

| Legend:             |       |                    |       |                       |                    |                     |        |

| R = Readable bit    |       | W = Writable bit   |       | U = Unimpleme         | ented bit, read as | ʻ0'                 |        |

| u = Bit is unchange | d     | x = Bit is unknown |       | -n/n = Value at       | POR and BOR/V      | alue at all other F | Resets |

bit 7-0 **PSCNT<7:0>:** Prescale Select Low Byte bits<sup>(1)</sup>

'0' = Bit is cleared

'1' = Bit is set

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### REGISTER 9-4: WDTPSH: WDT PRESCALE SELECT HIGH BYTE REGISTER (READ ONLY)

| R-0/0               | R-0/0 | R-0/0                | R-0/0 | R-0/0                 | R-0/0              | R-0/0                | R-0/0 |

|---------------------|-------|----------------------|-------|-----------------------|--------------------|----------------------|-------|

|                     |       |                      | PSCNT | <15:8> <sup>(1)</sup> |                    |                      |       |

| bit 7               |       |                      |       |                       |                    |                      | bit 0 |

|                     |       |                      |       |                       |                    |                      |       |

| Legend:             |       |                      |       |                       |                    |                      |       |

| R = Readable bit    |       | W = Writable bit     |       | U = Unimpleme         | ented bit, read as | ʻ0'                  |       |

| u = Bit is unchange | ed    | x = Bit is unknown   |       | -n/n = Value at       | POR and BOR/V      | alue at all other Re | sets  |

| '1' = Bit is set    |       | '0' = Bit is cleared |       |                       |                    |                      |       |

bit 7-0 PSCNT<15:8>: Prescale Select High Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### REGISTER 9-5: WDTTMR: WDT TIMER REGISTER (READ ONLY)

| R-0/0       | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0  | R-0/0             |

|-------------|-------|-------|-------|-------|-------|--------|-------------------|

| WDTTMR<3:0> |       |       |       |       | STATE | PSCNT< | 17:16> <b>(1)</b> |

| bit 7       |       |       |       |       |       |        | bit 0             |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-3 WDTTMR<4:0>: Watchdog Timer Value

- bit 2 STATE: WDT Armed Status bit 1 = WDT is armed 0 = WDT is not armed

- bit 1-0 **PSCNT<17:16>**: Prescale Select Upper Byte bits<sup>(1)</sup>

- **Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

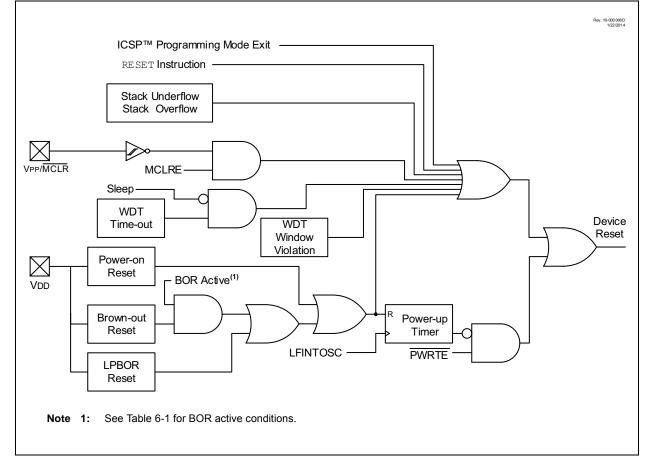

#### EXAMPLE 10-1: FLASH PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI: PROG_ADDR_LO

data will be returned in the variables;

PROG_DATA_HI, PROG_DATA_LO

BANKSEL PMADRL

; Select Bank for PMCON registers

PROG_ADDR_LO

MOVLW

;

MOVWF

PMADRL

; Store LSB of address

PROG_ADDR_HI

MOVLW

;

MOVWF

PMADRH

; Store MSB of address

BCF

PMCON1,CFGS

; Do not select Configuration Space

BSF

PMCON1,RD

; Initiate read

NOP

; Ignored (Figure 10-2)

NOP

; Ignored (Figure 10-2)

MOVF

PMDATL,W

; Get LSB of word

MOVWF

PROG_DATA_LO

; Store in user location

; Get MSB of word

PMDATH,W

MOVF

MOVWF

PROG_DATA_HI

; Store in user location

```

# 15.3 Register Definitions: FVR Control

| R/W-0/0              | R-q/q                                        | R/W-0/0                                                                                | R/W-0/0                                                  | R/W-0/0                            | R/W-0/0                                                                      | R/W-0/0          | R/W-0/0              |

|----------------------|----------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------|------------------|----------------------|

| FVREN <sup>(1)</sup> | FVRRDY <sup>(2)</sup>                        | TSEN <sup>(3)</sup>                                                                    | TSRNG <sup>(3)</sup>                                     | CDAFV                              | ′R<1:0> <sup>(1)</sup>                                                       | ADFVR            | <1:0> <sup>(1)</sup> |

| bit 7                |                                              |                                                                                        | 1                                                        |                                    |                                                                              |                  | bit                  |

|                      |                                              |                                                                                        |                                                          |                                    |                                                                              |                  |                      |

| Legend:              |                                              |                                                                                        |                                                          |                                    |                                                                              |                  |                      |

| R = Readable         |                                              | W = Writable                                                                           | bit                                                      | •                                  | mented bit, read                                                             |                  |                      |

| u = Bit is unch      | nanged                                       | x = Bit is unk                                                                         | nown                                                     | -n/n = Value                       | at POR and BO                                                                | R/Value at all o | ther Resets          |

| '1' = Bit is set     |                                              | '0' = Bit is cle                                                                       | ared                                                     | q = Value de                       | pends on condit                                                              | ion              |                      |

| bit 7                | 1 = Fixed Vo                                 | d Voltage Refe<br>Itage Referenc<br>Itage Referenc                                     | e is enabled                                             | bit <sup>(1)</sup>                 |                                                                              |                  |                      |

| bit 6                | 1 = Fixed Vo                                 | ed Voltage Re<br>Itage Referenc<br>Itage Referenc                                      | e output is rea                                          | dy for use                         | enabled                                                                      |                  |                      |

| bit 5                | 1 = Tempera                                  | erature Indicate<br>ture Indicator i<br>ture Indicator i                               | s enabled                                                | )                                  |                                                                              |                  |                      |

| bit 4                | 1 = VOUT = V                                 | perature Indica<br>/DD - 4VT (Higł<br>/DD - 2VT (Low                                   | n Range)                                                 | lection bit <sup>(3)</sup>         |                                                                              |                  |                      |

| bit 3-2              | 11 = Compara<br>10 = Compara<br>01 = Compara | ator FVR Buffe                                                                         | er Gain is 4x, v<br>er Gain is 2x, v<br>er Gain is 1x, v | vith output Vcc<br>vith output Vcc | bits <sup>(1)</sup><br>DAFVR = 4x VFVR<br>DAFVR = 2x VFVR<br>DAFVR = 1x VFVR | <sub>(</sub> (4) |                      |

| bit 1-0              | 11 = ADC FV<br>10 = ADC FV<br>01 = ADC FV    | : ADC FVR Bu<br>'R Buffer Gain<br>'R Buffer Gain<br>'R Buffer Gain<br>'R Buffer is off | is 4x, with out<br>is 2x, with out                       | out VADFVR = 2<br>out VADFVR = 2   | 2x V <sub>FVR</sub> (4)                                                      |                  |                      |

|                      | minimize curren<br>the Buffer Gain           |                                                                                        |                                                          | R is disabled, t                   | he FVR buffers                                                               | should be turne  | ed off by clea       |

|                      |                                              |                                                                                        |                                                          | louiooo                            |                                                                              |                  |                      |

# **REGISTER 15-1:** FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

- 2: FVRRDY is always '1' for the PIC16LF1615/9 devices.

- 3: See Section16.0 "Temperature Indicator Module" for additional information.

- 4: Fixed Voltage Reference output cannot exceed VDD.

#### TABLE 15-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|---------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | ′R<1:0> | ADFVF | R<1:0> | 194                 |

**Legend:** Shaded cells are unused by the Fixed Voltage Reference module.

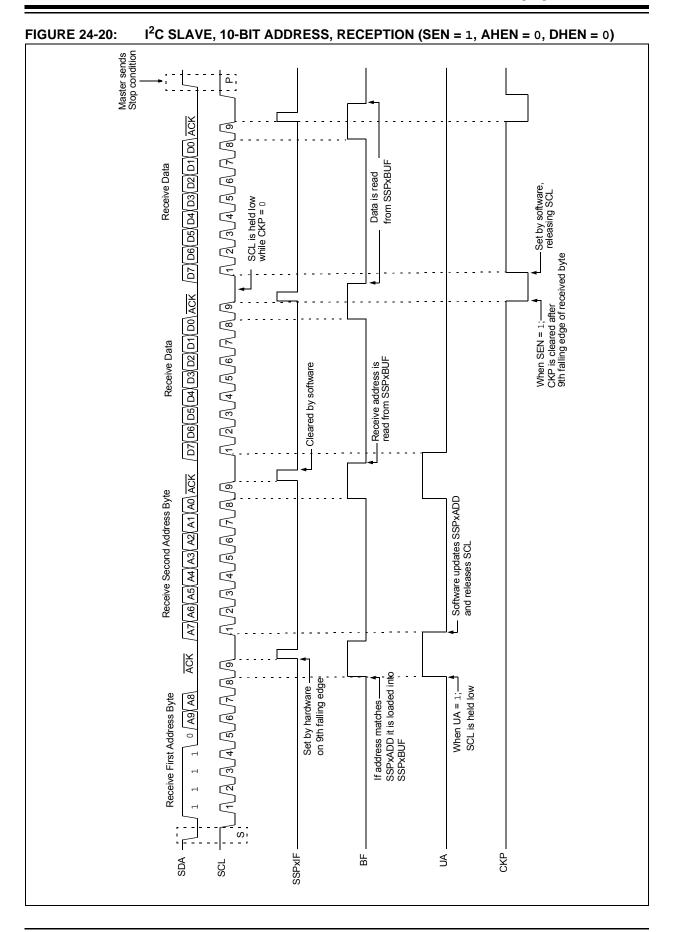

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCL line, is called clock stretching. Clock stretching gives slave devices a mechanism to control the flow of data. When this detection is used on the SDA line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

# 24.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCL clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCL line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCL connection is opendrain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

#### 24.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

#### 24.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high. When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCL low and SDA unchanged (Figure 24-28).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCL low and allowing SDA to float.

### 24.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all eight bits are shifted out.

### 24.6.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

# 24.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

24.6.6.4 Typical Transmit Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- 6. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- 7. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 8. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDA pin until all eight bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPxCON2 register. Interrupt is generated once the Stop/Restart condition is complete.

| Name                  | Bit 7                 | Bit 6                 | Bit 5         | Bit 4         | Bit 3   | Bit 2      | Bit 1  | Bit 0  | Reset<br>Values on<br>Page: |  |

|-----------------------|-----------------------|-----------------------|---------------|---------------|---------|------------|--------|--------|-----------------------------|--|

| ANSELA                | _                     | _                     | _             | ANSA4         | _       | ANSA2      | ANSA1  | ANSA0  | 160                         |  |

| ANSELB <sup>(1)</sup> | _                     | _                     | ANSB5         | ANSB4         | _       | _          | _      | —      | 167                         |  |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | _             |               | ANSC3   | ANSC2      | ANSC1  | ANSC0  | 174                         |  |

| INTCON                | GIE                   | PEIE                  | TMR0IE        | INTE          | IOCIE   | TMR0IF     | INTF   | IOCIF  | 105                         |  |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE          | TXIE          | SSP1IE  | CCP1IE     | TMR2IE | TMR1IE | 106                         |  |

| PIE2                  | OSFIE                 | C2IE                  | C1IE          |               | BCL1IE  | TMR6IE     | TMR4IE | CCP2IE | 107                         |  |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF          | TXIF          | SSP1IF  | CCP1IF     | TMR2IF | TMR1IF | 111                         |  |

| PIR2                  | OSFIF                 | C2IF                  | C1IF          | _             | BCL1IF  | TMR6IF     | TMR4IF | CCP2IF | 112                         |  |

| RxyPPS                | _                     | _                     |               | RxyPPS<4:0>   |         |            |        |        |                             |  |

| SSPCLKPPS             | —                     | _                     | _             |               | SS      | PCLKPPS<4  | :0>    |        | 182, 180                    |  |

| SSPDATPPS             | —                     | _                     | —             |               | SS      | PDATPPS<4  | :0>    |        | 182, 180                    |  |

| SSPSSPPS              | _                     | _                     |               |               | S       | SPSSPPS<4: | )>     |        | 182, 180                    |  |

| SSP1ADD               |                       |                       |               | ADD           | <7:0>   |            |        |        | 318                         |  |

| SSP1BUF               | Synchronous           | s Serial Port F       | Receive Buffe | r/Transmit Re | egister |            |        |        | 270*                        |  |

| SSP1CON1              | WCOL                  | SSPOV                 | SSPEN         | CKP           |         | SSPN       | <3:0>  |        | 315                         |  |

| SSP1CON2              | GCEN                  | ACKSTAT               | ACKDT         | ACKEN         | RCEN    | PEN        | RSEN   | SEN    | 316                         |  |

| SSP1CON3              | ACKTIM                | PCIE                  | SCIE          | BOEN          | SDAHT   | SBCDE      | AHEN   | DHEN   | 317                         |  |

| SSP1MSK               | MSK<7:0>              |                       |               |               |         |            |        | 318    |                             |  |

| SSP1STAT              | SMP                   | CKE                   | D/A           | Р             | S       | R/W        | UA     | BF     | 314                         |  |

| TRISA                 | —                     | —                     | TRISA5        | TRISA4        | (2)     | TRISA2     | TRISA1 | TRISA0 | 159                         |  |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5        | TRISB4        | —       | —          | —      | —      | 166                         |  |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5        | TRISC4        | TRISC3  | TRISC2     | TRISC1 | TRISC0 | 173                         |  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C$  mode.

\* Page provides register information.

**Note 1:** PIC16(L)F1619 only.

2: Unimplemented, read as '1'.

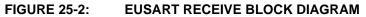

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXxSTA)

- · Receive Status and Control (RCxSTA)

- Baud Rate Control (BAUDxCON)

These registers are detailed in Register 25-1, Register 25-2 and Register 25-3, respectively.

The RX and CK input pins are selected with the RXPPS and CKPPS registers, respectively. TX, CK, and DT output pins are selected with each pin's RxyPPS register. Since the RX input is coupled with the DT output in Synchronous mode, it is the user's responsibility to select the same pin for both of these functions when operating in Synchronous mode. The EUSART control logic will control the data direction drivers automatically.

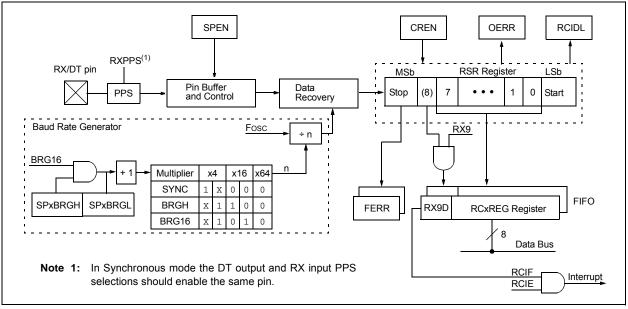

#### 25.1.2.8 Asynchronous Reception Set-up

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCxSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCxREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 25.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- 8. The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RCxSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCxREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

# 25.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 5.2.2.3 "Internal Oscillator Frequency Adjustment"** for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see **Section 25.4.1 "Auto-Baud Detect"**). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

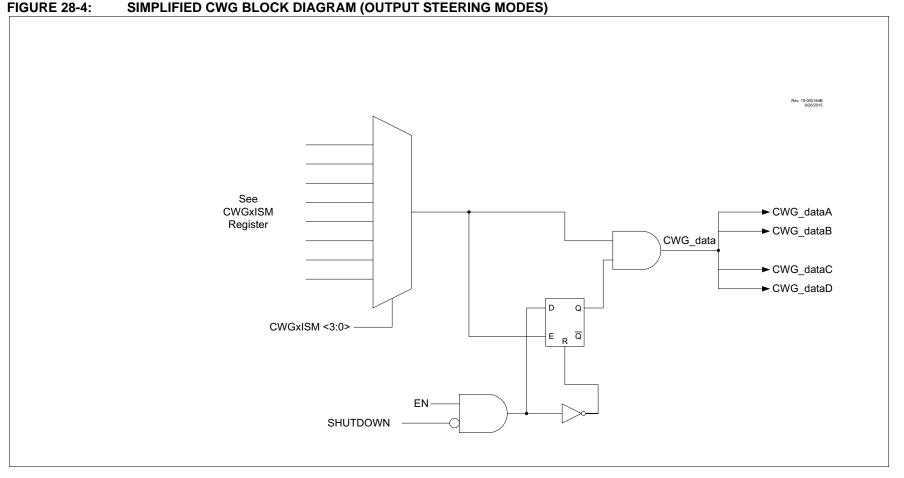

#### **FIGURE 28-4:** SIMPLIFIED CWG BLOCK DIAGRAM (OUTPUT STEERING MODES)

# 28.2 Clock Source

The CWG module allows the following clock sources to be selected:

- Fosc (system clock)

- HFINTOSC (16 MHz only)

The clock sources are selected using the CS bit of the CWGxCLKCON register.

### 28.3 Selectable Input Sources

The CWG generates the output waveforms from the input sources in Table 28-1.

TABLE 28-1: SELECTABLE INPUT SOURCES

| Source Peripheral | Signal Name   |

|-------------------|---------------|

| CWG pin           | PPS selection |

| Comparator C1     | C1_OUT_sync   |

| Comparator C2     | C2_OUT_sync   |

| CCP1              | CCP1_out      |

| CCP2              | CCP2_out      |

| CLC1              | LC1_out       |

| CLC2              | LC2_out       |

| CLC3              | LC3_out       |

| CLC4              | LC4_out       |

| PWM3              | PWM3_out      |

| PWM4              | PWM4_out      |

The input sources are selected using the CWGxISM register.

# 28.4 Output Control

### 28.4.1 OUTPUT ENABLES

Each CWG output pin has individual output enable control. Output enables are selected with the Gx1OEx <3:0> bits. When an output enable control is cleared, the module asserts no control over the pin. When an output enable is set, the override value or active PWM waveform is applied to the pin per the port priority selection. The output pin enables are dependent on the module enable bit, EN of the CWGxCON0 register. When EN is cleared, CWG output enables and CWG drive levels have no effect.

### 28.4.2 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the POLx bits of the CWGxCON1. Auto-shutdown and steering options are unaffected by polarity.

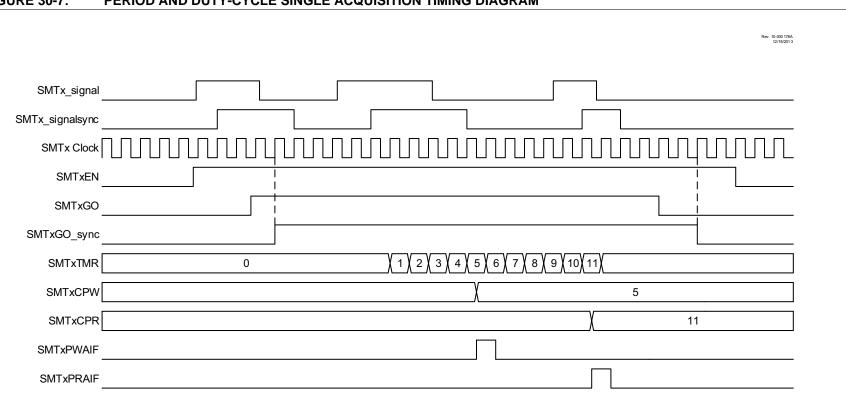

# FIGURE 30-7: PERIOD AND DUTY-CYCLE SINGLE ACQUISITION TIMING DIAGRAM

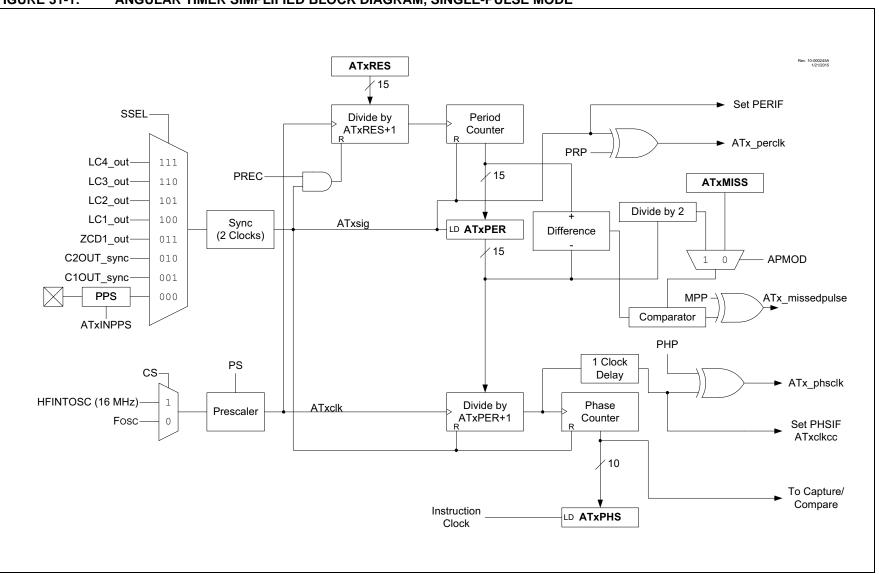

# FIGURE 31-1: ANGULAR TIMER SIMPLIFIED BLOCK DIAGRAM, SINGLE-PULSE MODE

PIC16(L)F1615/9

| U-0                                   | U-0           | U-0                                       | U-0             | U-0                            | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |

|---------------------------------------|---------------|-------------------------------------------|-----------------|--------------------------------|------------------|------------------|--------------|--|--|--|

|                                       | —             | —                                         | —               | —                              | PHSIE            | MISSIE           | PERIE        |  |  |  |

| bit 7                                 |               |                                           |                 |                                |                  |                  | bit 0        |  |  |  |

|                                       |               |                                           |                 |                                |                  |                  |              |  |  |  |

| Legend:                               |               |                                           |                 |                                |                  |                  |              |  |  |  |

| R = Readab                            | ole bit       | W = Writable                              | bit             | U = Unimpler                   | mented bit, read | as '0'           |              |  |  |  |

| u = Bit is un                         | ichanged      | x = Bit is unkr                           | nown            | -n/n = Value a                 | at POR and BOF   | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set '0' = Bit is cleared |               |                                           |                 | q = Value depends on condition |                  |                  |              |  |  |  |

|                                       |               |                                           |                 |                                |                  |                  |              |  |  |  |

| bit 7-3                               | Unimplemen    | ted: Read as '                            | 0'              |                                |                  |                  |              |  |  |  |

| bit 2                                 | PHSIE: Phas   | e Interrupt Ena                           | ble bit         |                                |                  |                  |              |  |  |  |

|                                       | 1 = The phas  | = The phase interrupt is enabled          |                 |                                |                  |                  |              |  |  |  |

|                                       | 0 = The phase | se interrupt is d                         | isabled         |                                |                  |                  |              |  |  |  |

| bit 1                                 | MISSIE: Miss  | ed Pulse Interr                           | upt Enable bit  | t                              |                  |                  |              |  |  |  |

|                                       | 1 = The miss  | 1 = The missed pulse interrupt is enabled |                 |                                |                  |                  |              |  |  |  |

|                                       | 0 = The miss  | ed pulse interr                           | upt is disabled | ł                              |                  |                  |              |  |  |  |

| bit 0                                 | PERIE: Perio  | d Interrupt Ena                           | ble bit         |                                |                  |                  |              |  |  |  |

|                                       |               | od interrupt is e                         |                 |                                |                  |                  |              |  |  |  |

|                                       | 0 = The perio | od interrupt is d                         | isabled         |                                |                  |                  |              |  |  |  |

|                                       |               |                                           |                 |                                |                  |                  |              |  |  |  |

# REGISTER 31-13: ATxIE0: ANGULAR TIMER ENABLE 0 REGISTER

# REGISTER 31-14: ATxIR0: ANGULAR TIMER INTERRUPT FLAG 0 REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | —   | PHSIF   | MISSIF  | PERIF   |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-3 | Unimplemented: Read as '0'                                           |

|---------|----------------------------------------------------------------------|

| bit 2   | PHSIF: Phase Interrupt Flag bit                                      |

|         | 1 = The phase interrupt has occurred                                 |

|         | 0 = The phase interrupt has not occurred, or has been cleared        |

| bit 1   | MISSIF: Missed Pulse Interrupt Flag bit                              |

|         | 1 = The missed pulse interrupt has occurred                          |

|         | 0 = The missed pulse interrupt has not occurred, or has been cleared |

| bit 0   | PERIF: Period Interrupt Flag bit                                     |

|         | 1 = The period interrupt has occurred                                |

|         | 0 = The period interrupt has not occurred, or has been cleared       |

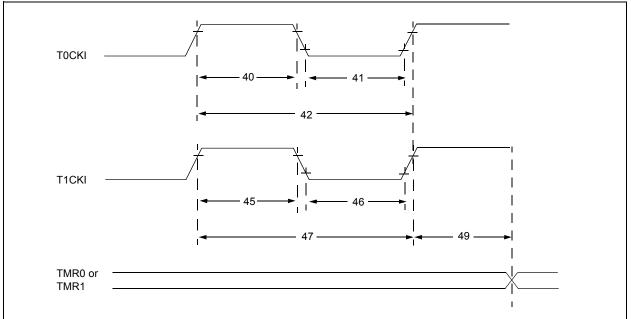

| TABLE 35-12: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|--------------|-----------------------------------------------|

|--------------|-----------------------------------------------|

| Param.<br>No. | Sym.      |                                     | Characterist                         | ic           | Min.                                      | Тур† | Max.   | Units | Conditions             |

|---------------|-----------|-------------------------------------|--------------------------------------|--------------|-------------------------------------------|------|--------|-------|------------------------|

| 40* TT0H      |           | TOCKI High Pulse Width No Prescaler |                                      |              | 0.5 TCY + 20                              |      |        | ns    |                        |

|               |           | With Prescaler                      |                                      | 10           |                                           |      | ns     |       |                        |

| 41*           | T⊤0L      | OL TOCKI Low Puls                   |                                      | No Prescaler | 0.5 TCY + 20                              | _    |        | ns    |                        |

|               |           | With Prescaler                      |                                      | 10           | _                                         |      | ns     |       |                        |

| 42*           | TT0P      | T0CKI Period                        | 1                                    |              | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _    | _      | ns    | N = prescale value     |

| 45* T⊤1H      | T⊤1H      | T1CKI High<br>Time                  | Synchronous, No Prescaler            |              | 0.5 TCY + 20                              |      |        | ns    |                        |

|               |           |                                     | Synchronous, with Prescaler          |              | 15                                        |      |        | ns    |                        |

|               |           |                                     | Asynchronous                         |              | 30                                        |      |        | ns    |                        |

| 46*           | T⊤1L      | T1CKI Low<br>Time                   | Synchronous, No Prescaler            |              | 0.5 TCY + 20                              | _    | _      | ns    |                        |

|               |           |                                     | Synchronous, with Prescaler          |              | 15                                        | _    | _      | ns    |                        |

|               |           |                                     | Asynchronous                         |              | 30                                        |      |        | ns    |                        |

| 47*           | TT1P      | T1CKI Input<br>Period               | Synchronous                          |              | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —    | _      | ns    | N = prescale value     |

|               |           |                                     | Asynchronous                         |              | 60                                        | _    | —      | ns    |                        |

| 49*           | TCKEZTMR1 | Delay from E<br>Increment           | ay from External Clock Edge to Timer |              |                                           | _    | 7 Tosc | —     | Timers in Sync<br>mode |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.