Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

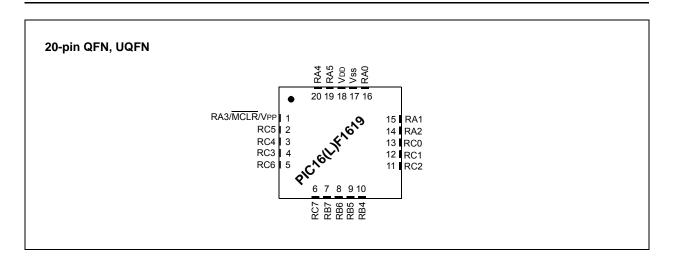

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1619-e-so |

| 민                |  |

|------------------|--|

| $ \vec{\Omega} $ |  |

| <u></u> [        |  |

|                  |  |

| F1               |  |

| 62               |  |

| 5/3              |  |

TABLE 3-14: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr   | Name               | Bit 7         | Bit 6     | Bit 5     | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0 | Value on POR, BOR | Value on all other Resets |

|--------|--------------------|---------------|-----------|-----------|-------|-----------|-------|--------|-------|-------------------|---------------------------|

| Bank ' | 16                 |               |           |           |       |           |       |        |       |                   |                           |

| 80Ch   | AT1RESL            |               | xxxx xxxx | xxxx xxxx |       |           |       |        |       |                   |                           |

| 80Dh   | AT1RESH            | _             | _         | _         | _     | _         | _     | RES    | <9:8> | xx                | xx                        |

| 80Eh   | AT1MISSL           |               |           |           | MISS  | <7:0>     |       |        |       | xxxx xxxx         | xxxx xxxx                 |

| 80Fh   | AT1MISSH           |               |           |           | MISS  | <15:8>    |       |        |       | xxxx xxxx         | xxxx xxxx                 |

| 810h   | AT1PERL            |               |           |           | PER•  | <7:0>     |       |        |       | xxxx xxxx         | xxxx xxxx                 |

| 811h   | AT1PERH            | POV           |           |           |       | PER<14:8> |       |        |       | xxxx xxxx         | xxxx xxxx                 |

| 812h   | AT1PHSL            |               |           |           | PHS•  | <7:0>     |       |        |       | xxxx xxxx         | xxxx xxxx                 |

| 813h   | AT1PHSH            | _             | _         | _         | _     | _         | _     | PHS    | <9:8> | xx                | xx                        |

| 814h   | AT1CON0            | EN            | PREC      | PS<       | 1:0>  | POL       | _     | APMOD  | MODE  | 0x0000            | 0x00 -00                  |

| 815h   | AT1CON1            | _             | PHP       | _         | PRP   | _         | MPP   | ACCS   | VALID | 0000 0000         | 0000 0000                 |

| 816h   | AT1IR0             | _             | _         | _         | _     | _         | PHSIF | MISSIF | PERIF | 000               | 000                       |

| 817h   | AT1IE0             | _             | _         | _         | _     | _         | PHSIE | MISSIE | PERIE | 000               | 000                       |

| 818h   | AT1IR1             | _             | _         | _         | _     | _         | CC3IF | CC2IF  | CC1IF | 000               | 000                       |

| 819h   | AT1IE1             | _             |           | _         | _     |           | CC3IE | CC2IE  | CC1IE | 000               | 000                       |

| 81Ah   | AT1STPTL           |               |           |           | STPT  | <7:0>     |       |        |       | xxxx xxxx         | xxxx xxxx                 |

| 81Bh   | AT1STPTH           | — STPT<14:8>  |           |           |       |           |       |        |       |                   | -xxx xxxx                 |

| 81Ch   | AT1ERRL            | ERR<7:0>      |           |           |       |           |       |        |       |                   | xxxx xxxx                 |

| 81Dh   | AT1ERRH            | ERR<15:8>     |           |           |       |           |       |        |       |                   | xxxx xxxx                 |

| 81Eh   | _                  | Unimplemented |           |           |       |           |       |        |       |                   | _                         |

| 81Fh   | Fh — Unimplemented |               |           |           |       |           |       |        |       | _                 | _                         |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition, - = unimplemented, r = value depends on condition depends on condi

**Note 1:** PIC16F1615/9 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1615 only.

4: PIC16(L)F1619 only.

TABLE 3-14: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr       | Name     | Bit 7         | Bit 6                          | Bit 5 | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0   | Value on POR, BOR | Value on all other Resets |  |

|------------|----------|---------------|--------------------------------|-------|-----------|-----------|-----------|-----------|---------|-------------------|---------------------------|--|

| Banks      | s 27     |               |                                |       |           |           |           |           |         |                   |                           |  |

| D80h       |          |               |                                |       |           |           |           |           |         |                   |                           |  |

| to<br>D8Bh | _        | Unimplemented | nimplemented                   |       |           |           |           |           |         |                   |                           |  |

| D8Ch       | SMT1TMRL |               | SMT1TMR<7:0>                   |       |           |           |           |           |         |                   |                           |  |

| D8Dh       | SMT1TMRH |               | SMT1TMR<15:8>                  |       |           |           |           |           |         |                   |                           |  |

| D8Eh       | SMT1TMRU |               |                                |       | SMT1TM    | R<23:16>  |           |           |         | 0000 0000         | 0000 0000                 |  |

| D8Fh       | SMT1CPRL |               |                                |       | SMT1CF    | PR<7:0>   |           |           |         | xxxx xxxx         | xxxx xxxx                 |  |

| D90h       | SMT1CPRH |               |                                |       | SMT1CF    | PR<15:8>  |           |           |         | xxxx xxxx         | xxxx xxxx                 |  |

| D91h       | SMT1CPRU |               |                                |       | SMT1CP    | R<23:16>  |           |           |         | xxxx xxxx         | xxxx xxxx                 |  |

| D92h       | SMT1CPWL |               |                                |       | SMT1CF    | PW<7:0>   |           |           |         | xxxx xxxx         | xxxx xxxx                 |  |

| D93h       | SMT1CPWH |               |                                |       | SMT1CP    | W<15:8>   |           |           |         | xxxx xxxx         | xxxx xxxx                 |  |

| D94h       | SMT1CPWU |               | SMT1CPW<23:16>                 |       |           |           |           |           |         |                   |                           |  |

| D95h       | SMT1PRL  |               |                                |       | SMT1P     | R<7:0>    |           |           |         | xxxx xxxx         | xxxx xxxx                 |  |

| D96h       | SMT1PRH  |               |                                |       | SMT1PI    | R<15:8>   |           |           |         | xxxx xxxx         | xxxx xxxx                 |  |

| D97h       | SMT1PRU  |               |                                |       | SMT1PF    | R<23:16>  |           |           |         | xxxx xxxx         | xxxx xxxx                 |  |

| D98h       | SMT1CON0 | EN            | _                              | STP   | WPOL      | SPOL      | CPOL      | SMT1F     | 'S<1:0> | 0-00 0000         | 0-00 0000                 |  |

| D99h       | SMT1CON1 | SMT1GO        | REPEAT                         |       | _         |           | MODE      | <3:0>     |         | 00 0000           | 00 0000                   |  |

| D9Ah       | SMT1STAT | CPRUP         | CPWUP                          | RST   | _         | _         | TS        | WS        | AS      | 000000            | 000000                    |  |

| D9Bh       | SMT1CLK  | _             | 1                              | 1     | _         | _         |           | CSEL<2:0> |         | 000               | 000                       |  |

| D9Ch       | SMT1SIG  | _             | -                              |       |           |           | SSEL<4:0> |           |         | 0 0000            | 0 0000                    |  |

| D9Dh       | SMT1WIN  | _             |                                |       |           |           | WSEL<4:0> |           |         | 0 0000            | 0 0000                    |  |

| D9Eh       | SMT2TMRL |               |                                |       | SMT2TN    | MR<7:0>   |           |           |         | 0000 0000         | 0000 0000                 |  |

| D9Fh       | SMT2TMRH |               | SMT2TMR<15:8>                  |       |           |           |           |           |         |                   |                           |  |

| DA0h       | SMT2TMRU |               |                                |       | SMT2TM    | R<23:16>  |           |           |         | 0000 0000         | 0000 0000                 |  |

| DA1h       | SMT2CPRL |               | SMT2CPR<7:0>                   |       |           |           |           |           |         |                   |                           |  |

| DA2h       | SMT2CPRH |               | SMT2CPR<15:8>                  |       |           |           |           |           |         |                   |                           |  |

| DA3h       | SMT2CPRU |               |                                |       | xxxx xxxx | xxxx xxxx |           |           |         |                   |                           |  |

| DA4h       | SMT2CPWL |               | SMT2CPR<23:16><br>SMT2CPW<7:0> |       |           |           |           |           |         |                   |                           |  |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, -= unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

- **Note 1:** PIC16F1615/9 only.

- 2: Unimplemented, read as '1'.

- 3: PIC16(L)F1615 only.

- 4: PIC16(L)F1619 only.

## 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

# 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h, Configuration Word 2 at 8008h, and Configuration 3 at 8009h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name       | Bit 7   | Bit 6  | Bit 5     | Bit 4     | Bit 3  | Bit 2     | Bit 1     | Bit 0   | Register on Page |

|------------|---------|--------|-----------|-----------|--------|-----------|-----------|---------|------------------|

| INTCON     | GIE     | PEIE   | TMR0IE    | INTE      | IOCIE  | TMR0IF    | INTF      | IOCIF   | 105              |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS    | TMR0SE    | PSA    |           | PS<2:0>   |         | 230              |

| PIE1       | TMR1GIE | ADIE   | RCIE      | TXIE      | SSP1IE | CCP1IE    | TMR2IE    | TMR1IE  | 106              |

| PIE2       | OSFIE   | C2IE   | C1IE      | _         | BCL1IE | TMR6IE    | TMR4IE    | CCP2IE  | 107              |

| PIE3       | _       | _      | CWGIE     | ZCDIE     | CLC4IE | CLC3IE    | CLC2IE    | CLC1IE  | 108              |

| PIE4       | SCANIE  | CRCIE  | SMT2PWAIE | SMT2PRAIE | SMT2IE | SMT1PWAIE | SMT1PRAIE | SMT1IF  | 109              |

| PIE5       | TMR3GIE | TMR3IE | TMR5GIE   | TMR5IE    | _      | AT1IE     | PID1EIE   | PID1DIE | 110              |

| PIR1       | TMR1GIF | ADIF   | RCIF      | TXIF      | SSP1IF | CCP1IF    | TMR2IF    | TMR1IF  | 111              |

| PIR2       | OSFIF   | C2IF   | C1IF      | _         | BCL1IF | TMR6IF    | TMR4IF    | CCP2IF  | 112              |

| PIR3       | _       | _      | CWGIF     | ZCDIF     | CLC4IF | CLC3IF    | CLC2IF    | CLC1IF  | 113              |

| PIR4       | SCANIF  | CRCIF  | SMT2PWAIF | SMT2PRAIF | SMT2IF | SMT1PWAIF | SMT1PRAIF | SMT1IF  | 114              |

| PIR5       | TMR3GIF | TMR3IF | TMR5GIF   | TMR5IF    | _      | AT1IF     | PID1EIF   | PID1DIF | 115              |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

#### REGISTER 10-5: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W/HC-0/0 | R/W/HC-x/q <sup>(2)</sup> | R/W-0/0 | R/S/HC-0/0 | R/S/HC-0/0 |

|-------|---------|---------|------------|---------------------------|---------|------------|------------|

| (1)   | CFGS    | LWLO    | FREE       | WRERR                     | WREN    | WR         | RD         |

| bit 7 |         |         |            |                           |         |            | bit 0      |

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

S = Bit can only be set

x = Bit is unknown

-n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set

'0' = Bit is cleared

HC = Bit is cleared by hardware

bit 7 **Unimplemented:** Read as '1'

bit 6

bit 3

**CFGS:** Configuration Select bit 1 = Access Configuration, User ID and Device ID Registers

0 = Access Flash program memory

bit 5 **LWLO:** Load Write Latches Only bit<sup>(3)</sup>

1 = Only the addressed program memory write latch is loaded/updated on the next WR command

0 = The addressed program memory write latch is loaded/updated and a write of all program memory write latches will be initiated on the next WR command

bit 4 FREE: Program Flash Erase Enable bit

1 = Performs an erase operation on the next WR command (hardware cleared upon completion)

0 = Performs a write operation on the next WR command

WRERR: Program/Erase Error Flag bit

1 = Condition indicates an improper program or erase sequence attempt or termination (bit is set automatically on any set attempt (write '1') of the WR bit)

0 = The program or erase operation completed normally

bit 2 WREN: Program/Erase Enable bit

1 = Allows program/erase cycles

0 = Inhibits programming/erasing of program Flash

bit 1 WR: Write Control bit

1 = Initiates a program Flash program/erase operation.

The operation is self-timed and the bit is cleared by hardware once operation is complete.

The WR bit can only be set (not cleared) in software.

0 = Program/erase operation to the Flash is complete and inactive

bit 0 RD: Read Control bit

1 = Initiates a program Flash read. Read takes one cycle. RD is cleared in hardware. The RD bit can only be set (not cleared) in software.

0 = Does not initiate a program Flash read

Note 1: Unimplemented bit, read as '1'.

2: The WRERR bit is automatically set by hardware when a program memory write or erase operation is started (WR = 1).

3: The LWLO bit is ignored during a program memory erase operation (FREE = 1).

TABLE 12-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name       | Bit 7 | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register on Page |

|------------|-------|--------|---------|---------|---------|---------|---------|---------|------------------|

| ANSELA     | _     | _      | _       | ANSA4   | _       | ANSA2   | ANSA1   | ANSA0   | 160              |

| INLVLA     | _     | -      | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 162              |

| LATA       | -     | -      | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   | 160              |

| ODCONA     | _     | -      | ODA5    | ODA4    |         | ODA2    | ODA1    | ODA0    | 161              |

| OPTION_REG | WPUEN | INTEDG | TMR0CS  | TMR0SE  | PSA     |         | PS<2:0> |         | 230              |

| PORTA      | _     | _      | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 159              |

| SLRCONA    | _     | _      | SLRA5   | SLRA4   | _       | SLRA2   | SLRA1   | SLRA0   | 162              |

| TRISA      | _     | _      | TRISA5  | TRISA4  | (1)     | TRISA2  | TRISA1  | TRISA0  | 159              |

| WPUA       | _     |        | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 161              |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: Unimplemented, read as '1'.

TABLE 12-3: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1   | Bit 8/0 | Register on Page |

|---------|------|---------|---------|----------|----------|----------|----------|-----------|---------|------------------|

| CONFICA | 13:8 | _       | _       | FCMEN    | IESO     | CLKOUTEN | BORE     | N<1:0>    | _       | 00               |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | _        | _        |          | FOSC<2:0> |         | 69               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

#### 17.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INTCON register are enabled, execution will switch to the Interrupt Service Routine.

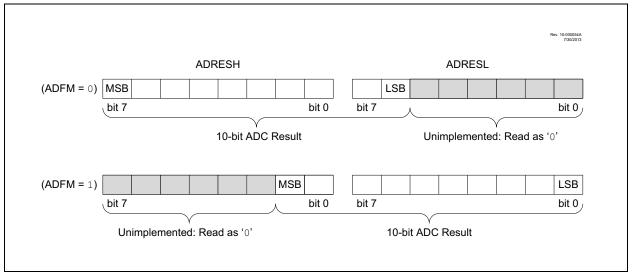

#### 17.1.6 RESULT FORMATTING

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 17-3 shows the two output formats.

FIGURE 17-3: 10-BIT ADC CONVERSION RESULT FORMAT

#### REGISTER 17-2: ADCON1: ADC CONTROL REGISTER 1

| R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-----------|---------|-----|-----|---------|---------|

| ADFM    |         | ADCS<2:0> |         | _   | _   | ADPRE   | F<1:0>  |

| bit 7   |         |           |         |     |     |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 ADFM: ADC Result Format Select bit

- 1 = Right justified. Six Most Significant bits of ADRESH are set to '0' when the conversion result is loaded.

- 0 = Left justified. Six Least Significant bits of ADRESL are set to '0' when the conversion result is loaded.

- bit 6-4 ADCS<2:0>: ADC Conversion Clock Select bits

- 111 = FRC (clock supplied from an internal RC oscillator)

- 110 = Fosc/64

- 101 = Fosc/16

- 100 = Fosc/4

- 011 = FRC (clock supplied from an internal RC oscillator)

- 010 = Fosc/32

- 001 = Fosc/8

- 000 = Fosc/2

- bit 3-2 **Unimplemented**: Read as '0'

- bit 1-0 ADPREF<1:0>: ADC Positive Voltage Reference Configuration bits

- 11 = VRPOS is connected to internal Fixed Voltage Reference (FVR)

- 10 = VRPOS is connected to external VREF+ pin(1)

- 01 = Reserved

- 00 = VRPOS is connected to VDD

- Note 1: When selecting the VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See SectionTABLE 35-13: "Analog-to-Digital Converter (ADC) Characteristics(1,2,3)" for details.

# 23.5.7 EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODE

In Edge-Triggered Hardware Limit One-Shot modes the timer starts on the first external signal edge after the ON bit is set and resets on all subsequent edges. Only the first edge after the ON bit is set is needed to start the timer. The counter will resume counting automatically two clocks after all subsequent external Reset edges. Edge triggers are as follows:

- Rising edge start and Reset (MODE<4:0> = 01100)

- Falling edge start and Reset (MODE<4:0> = 01101)

The timer resets and clears the ON bit when the timer value matches the PRx period value. External signal edges will have no effect until after software sets the ON bit. Figure 23-10 illustrates the rising edge hardware limit one-shot operation.

When this mode is used in conjunction with the CCP then the first starting edge trigger, and all subsequent Reset edges, will activate the PWM drive. The PWM drive will deactivate when the timer matches the CCPRx pulse-width value and stay deactivated until the timer halts at the PRx period match unless an external signal edge resets the timer before the match occurs.

#### REGISTER 24-4: SSP1CON3: SSP CONTROL REGISTER 3

| R-0/0                 | R/W-0/0 |

|-----------------------|---------|---------|---------|---------|---------|---------|---------|

| ACKTIM <sup>(3)</sup> | PCIE    | SCIE    | BOEN    | SDAHT   | SBCDE   | AHEN    | DHEN    |

| bit 7                 |         |         |         |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 **ACKTIM:** Acknowledge Time Status bit (I<sup>2</sup>C mode only)<sup>(3)</sup>

1 = Indicates the I<sup>2</sup>C bus is in an Acknowledge sequence, set on eighth falling edge of SCL clock

0 = Not an Acknowledge sequence, cleared on 9<sup>th</sup> rising edge of SCL clock

bit 6 **PCIE**: Stop Condition Interrupt Enable bit (I<sup>2</sup>C mode only)

1 = Enable interrupt on detection of Stop condition

0 = Stop detection interrupts are disabled(2)

bit 5 **SCIE**: Start Condition Interrupt Enable bit (I<sup>2</sup>C mode only)

1 = Enable interrupt on detection of Start or Restart conditions

0 = Start detection interrupts are disabled<sup>(2)</sup>

bit 4 **BOEN:** Buffer Overwrite Enable bit

In SPI Slave mode:(1)

1 = SSP1BUF updates every time that a new data byte is shifted in ignoring the BF bit

0 = If new byte is received with BF bit of the SSP1STAT register already set, SSPOV bit of the SSP1CON1 register is set, and the buffer is not updated

In I<sup>2</sup>C Master mode and SPI Master mode:

This bit is ignored.

In <u>I<sup>2</sup>C Slave mode:</u>

1 = SSP1BUF is updated and ACK is generated for a received address/data byte, ignoring the state of the SSPOV bit only if the BF bit = 0.

0 = SSP1BUF is only updated when SSPOV is clear

bit 3 **SDAHT:** SDA Hold Time Selection bit (I<sup>2</sup>C mode only)

1 = Minimum of 300 ns hold time on SDA after the falling edge of SCL

0 = Minimum of 100 ns hold time on SDA after the falling edge of SCL

bit 2 SBCDE: Slave Mode Bus Collision Detect Enable bit (I<sup>2</sup>C Slave mode only)

If, on the rising edge of SCL, SDA is sampled low when the module is outputting a high state, the BCL1IF bit of the PIR2 register is set, and bus goes idle

1 = Enable slave bus collision interrupts

0 = Slave bus collision interrupts are disabled

bit 1 AHEN: Address Hold Enable bit (I<sup>2</sup>C Slave mode only)

1 = Following the eighth falling edge of SCL for a matching received address byte; CKP bit of the SSP1CON1 register will be cleared and the SCL will be held low.

0 = Address holding is disabled

bit 0 **DHEN:** Data Hold Enable bit (I<sup>2</sup>C Slave mode only)

1 = Following the eighth falling edge of SCL for a received data byte; slave hardware clears the CKP bit of the SSP1CON1 register and SCL is held low.

0 = Data holding is disabled

Note 1: For daisy-chained SPI operation; allows the user to ignore all but the last received byte. SSPOV is still set when a new byte is received and BF = 1, but hardware continues to write the most recent byte to SSP1BUF.

2: This bit has no effect in Slave modes that Start and Stop condition detection is explicitly listed as enabled.

3: The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is set.

# 27.0 PULSE-WIDTH MODULATION (PWM) MODULE

The PWM module generates a Pulse-Width Modulated signal determined by the duty cycle, period, and resolution that are configured by the following registers:

- PR2

- T2CON

- PWMxDCH

- PWMxDCL

- PWMxCON

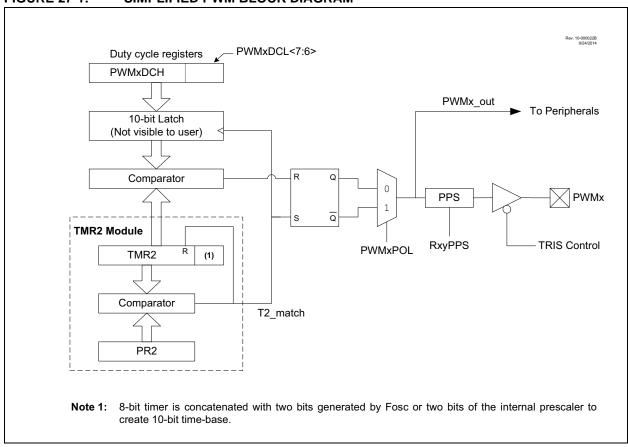

Figure 27-1 shows a simplified block diagram of PWM operation.

For a step-by-step procedure on how to set up this module for PWM operation, refer to Section 27.1.9 "Setup for PWM Operation using PWMx Pins".

#### FIGURE 27-1: SIMPLIFIED PWM BLOCK DIAGRAM

## 27.2 Register Definitions: PWM Control

#### REGISTER 27-1: PWMxCON: PWM CONTROL REGISTER

| R/W-0/0 | U-0 | R-0/0   | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|---------|---------|-----|-----|-----|-------|

| PWMxEN  | _   | PWMxOUT | PWMxPOL | _   | _   | _   | _     |

| bit 7   |     |         |         |     |     |     | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 **PWMxEN:** PWM Module Enable bit

1 = PWM module is enabled0 = PWM module is disabledUnimplemented: Read as '0'

bit 5 **PWMxOUT:** PWM Module Output Value bit

bit 4 **PWMxPOL:** PWMx Output Polarity Select bit

1 = PWM output is active-low 0 = PWM output is active-high **Unimplemented:** Read as '0'

#### REGISTER 27-2: PWMxDCH: PWM DUTY CYCLE HIGH BITS

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | PWMxD   | CH<7:0> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

bit 6

bit 3-0

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 PWMxDCH<7:0>: PWM Duty Cycle Most Significant bits

These bits are the MSbs of the PWM duty cycle. The two LSbs are found in the PWMxDCL register.

#### REGISTER 27-3: PWMxDCL: PWM DUTY CYCLE LOW BITS

| R/W-x/u      | R/W-x/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

|--------------|---------|-----|-----|-----|-----|-----|-----|

| PWMxDCL<7:6> |         | _   | _   | _   | _   | _   | _   |

| bit 7 bit 0  |         |     |     |     |     |     |     |

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

u = Bit is unchanged

x = Bit is unknown

-n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set

'0' = Bit is cleared

bit 7-6 PWMxDCL<7:6>: PWM Duty Cycle Least Significant bits

These bits are the LSbs of the PWM duty cycle. The MSbs are found in the PWMxDCH register.

bit 5-0 **Unimplemented:** Read as '0'

DS40001770C-page 443

### 31.7 Interrupts

The angular timer and its capture/compare features can generate multiple interrupt conditions. To accommodate all of these interrupt sources, the module is provided with its own interrupt logic structure, similar to that of the micro controller. Angular timer interrupts are enabled by the ATxIE0 register (Register 31-13) and their respective flags are located in the ATxIR0 register (Register 31-14). The capture/compare interrupts are enabled by the ATxIE1 register (Register 31-15) with flags in the ATxIR1 register (Register 31-16). All sources are funneled into a single Angular Timer Interrupt Flag bit, ATxIF of the PIR5 register (Register 7-11). This means that upon a triggered interrupt, the ATxIR0 and ATxIR1 register bits will indicate the source of the triggered interrupt. It also means that in order for specific interrupts to generate a microcontroller interrupt. both the ATxIE bit of the PIE register and the desired enable bit in either ATxIE0 or ATxIE1 must be set.

**Note:** Due to the nature of the angular timer interrupts, the ATxIF flag bit of the PIR5 register is read-only.

# 31.7.1 ANGULAR TIMER PERIOD INTERRUPT

This interrupt is triggered when the AT module detects a period event. In Single-Pulse mode, a period event occurs on every input signal edge. In Multi-Pulse mode, a period event occurs on the input signal edge following a missed pulse. The period interrupt generation matches with the pulses on the period clock output of the timer. It is enabled by the ATPERIE bit of the ATXIEO register and the status is indicated by the PERIF bit of the ATXIRO register.

# 31.7.2 ANGULAR TIMER PHASE CLOCK INTERRUPT

This interrupt is triggered on each pulse of the phase clock output of the timer. It is enabled by the ATPHIE bit of the ATxIE0 register and the status is indicated by the PHSIF bit of the ATxIR0 register.

# 31.7.3 ANGULAR TIMER MISSING PULSE INTERRUPT

This interrupt is triggered upon the output of a missing pulse detection signal. Refer to **Section 31.2.3 "Missing Pulse Detection"** for more information. This interrupt is enabled by the ATMISSIE bit of the ATXIEO register and its status is indicated by the ATMISSIF bit of the ATXIRO register.

# 31.7.4 ANGULAR TIMER CAPTURE/COMPARE INTERRUPTS

Capture and compare interrupts are triggered by the capture/compare functions of the module. If configured for Capture mode, the interrupt will trigger after the capture signal has successfully latched the value of the phase counter into the capture registers. If configured for Compare mode, the interrupt will trigger when a match is detected between the value placed in the compare register and the value of the phase counter. These interrupts are controlled by the CC1IE, CC2IE, and CC3IE bits of the ATxIE1 register, respectively, and are similarly indicated by the CC1IF, CC2IF, and CC3IF bits of the ATxIR1 register.

## REGISTER 32-10: PIDxK3H: PID K3 HIGH REGISTER

| R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|----------|---------|---------|---------|---------|---------|---------|---------|

| K3<15:8> |         |         |         |         |         |         |         |

| bit 7    |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7-0 K3<15:8>: K3 upper eight bits. K3 is the 16-bit user-controlled coefficient calculated from Kd

#### REGISTER 32-11: PIDxK3L: PID K3 LOW REGISTER

| R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| K3<7:0>     |         |         |         |         |         |         |         |

| bit 7 bit 0 |         |         |         |         |         |         |         |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is clearedq = Value depends on condition

bit 7-0 K3<7:0>: K3 lower eight bits. K3 is the 16-bit user-controlled coefficient calculated from Kd

## 35.4 AC Characteristics

Timing Parameter Symbology has been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

dt

io

mc

| •     |                                       |     |          |

|-------|---------------------------------------|-----|----------|

| F     | Frequency                             | Т   | Time     |

| Lower | case letters (pp) and their meanings: |     |          |

| pp    |                                       |     |          |

| cc    | CCP1                                  | osc | CLKIN    |

| ck    | CLKOUT                                | rd  | RD       |

| cs    | CS                                    | rw  | RD or WR |

| di    | SDIx                                  | sc  | SCKx     |

| do    | SDO                                   | ss  | SS       |

t0

t1

wr

T0CKI

T1CKI

WR

Uppercase letters and their meanings:

Data in

**MCLR**

I/O PORT

| S   |                          |   |                |  |

|-----|--------------------------|---|----------------|--|

| F   | Fall                     | Р | Period         |  |

| Н   | High                     | R | Rise           |  |

| - 1 | Invalid (High-impedance) | V | Valid          |  |

| L   | Low                      | Z | High-impedance |  |

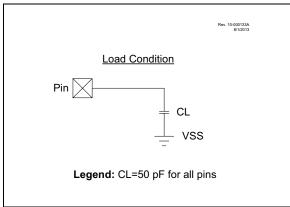

## FIGURE 35-4: LOAD CONDITIONS