# E. Coshiba Semiconductor and Storage - <u>TMP86PM47AUG(C,JZ) Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                                 |

| Core Processor             | -                                                                                        |

| Core Size                  | 8-Bit                                                                                    |

| Speed                      | 16MHz                                                                                    |

| Connectivity               | SIO, UART/USART                                                                          |

| Peripherals                | PWM, WDT                                                                                 |

| Number of I/O              | 35                                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                                           |

| Program Memory Type        | ОТР                                                                                      |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 1K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                              |

| Data Converters            | A/D 8x10b                                                                                |

| Oscillator Type            | External                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 44-LQFP                                                                                  |

| Supplier Device Package    | 44-LQFP (10x10)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/toshiba-semiconductor-and-storage/tmp86pm47aug-c-jz |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

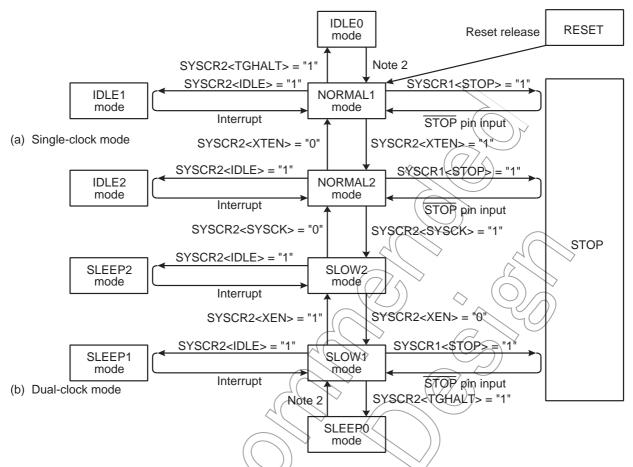

- Note 1: NORMAL1 and NORMAL2 modes are generically called NORMAL; SLOW1 and SLOW2 are called SLOW; IDLE0, IDLE1 and IDLE2 are called IDLE; SLEEP0, SLEEP1 and SLEEP2 are called SLEEP.

- Note 2: The mode is released by falling edge of TBTCR<TBTCK> setting

| Table 2-1 | Operating | Mode ar | nd Conditions | $\geq$ |

|-----------|-----------|---------|---------------|--------|

|-----------|-----------|---------|---------------|--------|

| Opera                             | iting Mode | Osc<br>High<br>Frequency        | illator<br>Low<br>Frequency | CPU Core                       | TBT     | Other<br>Peripherals | Machine Cycle<br>Time |

|-----------------------------------|------------|---------------------------------|-----------------------------|--------------------------------|---------|----------------------|-----------------------|

| ~ ((                              | RESET      | $\langle$                       |                             | Reset                          | Reset   | Reset                |                       |

| $\langle \langle \langle \rangle$ | NORMAL1    | Oscillation                     | Stop                        | Operate                        |         | Onorata              | 4/fc [s]              |

| Single clock                      | IDLE1      | Oscillation                     |                             |                                | Operate | Operate              | 4/10 [5]              |

|                                   |            |                                 | $\mathcal{I}$               | Halt                           |         | Halt                 |                       |

|                                   | STOP       | Stop                            |                             |                                | Halt    | i lait               | _                     |

| $\checkmark$                      | NORMAL2    | <ul> <li>Oscillation</li> </ul> |                             | Operate with<br>high frequency |         | Operate              | 4/fc [s]              |

|                                   | IDLE2      |                                 |                             | Halt                           |         |                      |                       |

|                                   | SLOW2      |                                 |                             | Operate with<br>low frequency  |         |                      |                       |

| Dual clock                        | SLEEP2     |                                 | Oscillation                 | Halt                           | Operate |                      |                       |

|                                   | SLOW1      |                                 |                             | Operate with<br>low frequency  |         |                      | 4/fs [s]              |

|                                   | SLEEP1     | Stop                            |                             |                                |         |                      |                       |

|                                   | SLEEP0     |                                 |                             | Halt                           |         | Halt                 |                       |

|                                   | STOP       |                                 | Stop                        |                                | Halt    | i lait               | _                     |

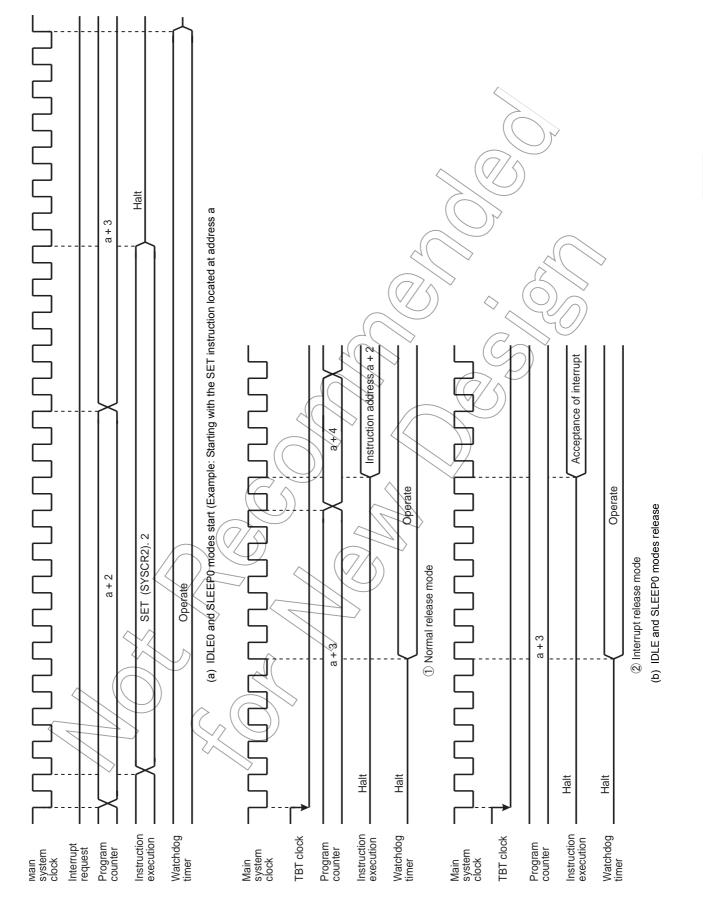

Figure 2-13 IDLE0 and SLEEP0 Modes Start/Release

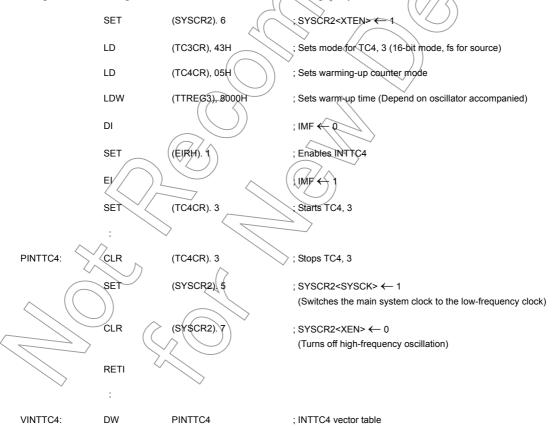

#### 2.2.4.4 SLOW mode

SLOW mode is controlled by the system control register 2 (SYSCR2).

The following is the methods to switch the mode with the warm-up counter.

#### (1) Switching from NORMAL2 mode to SLOW1 mode

First, set SYSCR2<SYSCK> to switch the main system clock to the low-frequency clock for SLOW2 mode. Next, clear SYSCR2<XEN> to turn off high-frequency oscillation.

Note: The high-frequency clock can be continued oscillation in order to return to NORMAL2 mode from SLOW mode quickly. Always turn off oscillation of high-frequency clock when switching from SLOW mode to stop mode.

Example 1 :Switching from NORMAL2 mode to SLOW1 mode. <

| SET | (SYSCR2). 5 | ; SYSCR2 <sysck> + 1.<br/>(Switches the main system clock to the low frequency</sysck> |

|-----|-------------|----------------------------------------------------------------------------------------|

|     |             | clock for SLOW2                                                                        |

| CLR | (SYSCR2). 7 | ; SYSCR2 <xen> ← 0<br/>(Turns off high-frequency oscillation)</xen>                    |

Example 2 :Switching to the SLOW1 mode after low-frequency clock has stabilized.

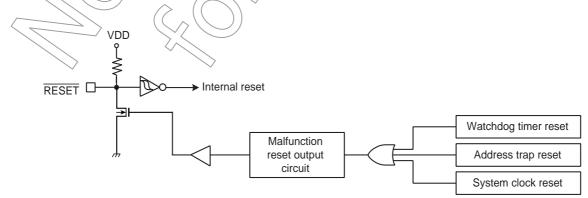

## 2.3 Reset Circuit

The TMP86PM47AUG has four types of reset generation procedures: An external reset input, an address trap reset, a watchdog timer reset and a system clock reset. Of these reset, the address trap reset, the watchdog timer and the system clock reset are a malfunction reset. When the malfunction reset request is detected, reset occurs during the maximum 24/fc[s] (The RESET pin outputs "L" level).

The malfunction reset circuit such as watchdog timer reset, address trap reset and system clock reset is not initialized when power is turned on. Therefore, reset may occur during maximum 24/fc[s] (1.5µs at 16.0 MHz) when power is turned on. RESET pin outputs "L" level during maximum 24/fc[s] (1.5µs at 16.0 MHz).

Table 2-3 shows on-chip hardware initialization by reset action.

| On-chip Hardware                                            |       | Initial Value   | On-chip Hardware                          | Initial Value               |

|-------------------------------------------------------------|-------|-----------------|-------------------------------------------|-----------------------------|

| Program counter                                             | (PC)  | (FFFEH)         | $\mathcal{A}(\mathcal{N})$                |                             |

| Stack pointer                                               | (SP)  | Not initialized | Prescaler and divider of timing generator |                             |

| General-purpose registers<br>(W, A, B, C, D, E, H, L, IX, I | Y)    | Not initialized | $\langle \rangle$                         |                             |

| Jump status flag                                            | (JF)  | Not initialized | Watchdog timer                            | Enable                      |

| Zero flag                                                   | (ZF)  | Not initialized |                                           |                             |

| Carry flag                                                  | (CF)  | Not initialized |                                           | $\mathcal{O}$               |

| Half carry flag                                             | (HF)  | Not initialized |                                           | Defer to 1/0 part eizewith  |

| Sign flag                                                   | (SF)  | Not initialized | Output latches of I/O ports               | Refer to I/O port circuitry |

| Overflow flag                                               | (VF)  | Not initialized |                                           |                             |

| Interrupt master enable flag                                | (IMF) | 0               |                                           |                             |

| Interrupt individual enable flags                           | (EF)  |                 |                                           | Refer to each of control    |

| Interrupt latches                                           | (IL)  |                 | Control registers                         | register                    |

|                                                             |       | ,               | RAM                                       | Not initialized             |

Table 2-3

Initializing Internal Status by Reset Action

### 2.3.1 External Reset Input

The RESET pin contains a Schmitt trigger (Hysteresis) with an internal pull-up resistor.

When the  $\overline{\text{RESET}}$  pin is held at "L" level for at least 3 machine cycles (12/fc [s]) with the power supply voltage within the operating voltage range and oscillation stable, a reset is applied and the internal state is initialized.

When the RESET pin input goes high, the reset operation is released and the program execution starts at the vector address stored at addresses FFFEH to FFFFH.

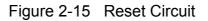

Saving/Restoring general-purpose registers using PUSH/POP data transfer instruction

### Figure 3-4 Saving/Restoring General-purpose Registers under Interrupt Processing

### 3.4.3 Interrupt return

Interrupt return instructions [RETI]/[RETN] perform as follows.

[RETI]/[RETN] Interrupt Return 1. Program counter (PC) and program status word (PSW, includes IMF) are restored from the stack. 2. Stack pointer (SP) is incremented by 3.

As for address trap interrupt (INTATRAP), it is required to alter stacked data for program counter (PC) to restarting address, during interrupt service program.

Note: If [RETN] is executed with the above data unaltered, the program returns to the address trap area and INTATRAP occurs again. When interrupt acceptance processing has completed, stacked data for PCL and PCH are located on address (SP + 1) and (SP + 2) respectively.

Example 1 :Returning from address trap interrupt (INTATRAP) service program

Example 2: Restarting without returning interrupt

(In this case, PSW (Includes IMF) before interrupt acceptance is discarded.)

| $\sim$  |                  | $\checkmark$    |                                     |

|---------|------------------|-----------------|-------------------------------------|

| PINTxx: | INC              | SP              | ; Recover SP by 3                   |

|         | INC              | SP              | ;                                   |

|         | INC              | SP              | ;                                   |

|         | (interrupt proce | essing)         |                                     |

|         | LD               | EIRL, data      | ; Set IMF to "1" or clear it to "0" |

|         | JP               | Restart Address | ; Jump into restarting address      |

|         |                  |                 |                                     |

Interrupt requests are sampled during the final cycle of the instruction being executed. Thus, the next interrupt can be accepted immediately after the interrupt return instruction is executed.

## 5. I/O Ports

|         | Primary Function | Secondary Functions                                                                              |

|---------|------------------|--------------------------------------------------------------------------------------------------|

| Port P0 | 8-bit I/O port   | External interrupt input, serial and timer/counter input/output                                  |

| Port P1 | 8-bit I/O port   | External interrupt input, timer/counter input/output, and divider output                         |

| Port P2 | 3-bit I/O port   | Low-frequncy resonator connections, external interrupt input, and STOP mode release signal input |

| Port P3 | 8-bit I/O port   | Analog input, and STOP mode release signal input                                                 |

| Port P4 | 8-bit I/O port   |                                                                                                  |

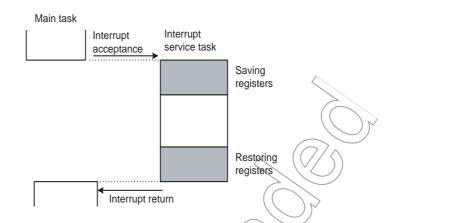

Each output port contains a latch, which holds the output data. All input ports do not have latches, so the external input data should be externally held until the input data is read from outside or reading should be performed several times before processing. Figure 5-1 shows input/output timing examples.

External data is read from an I/O port in the S1 state of the read cycle during execution of the read instruction. This timing cannot be recognized from outside, so that transient input such as chattering must be processed by the program.

Output data changes in the S2 state of the write cycle during execution of the instruction which writes to an I/O port.

Write

only

## TOSHIBA

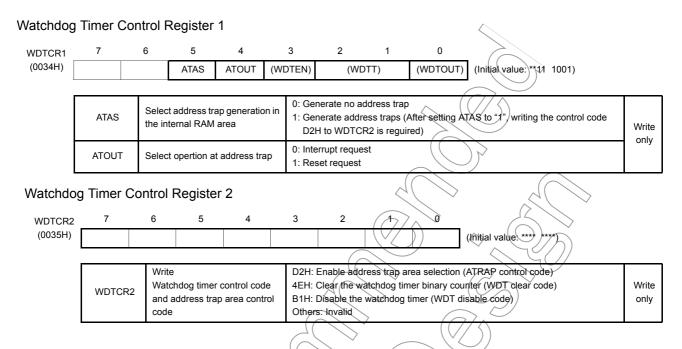

#### Watchdog Timer Control Register 1

| WDTCR1  | 7      | 6        | 5              | 4         | 3                    |    | 2                   | 1                   | 0                   |                      |               |

|---------|--------|----------|----------------|-----------|----------------------|----|---------------------|---------------------|---------------------|----------------------|---------------|

| (0034H) |        |          | (ATAS)         | (ATOUT)   | WDT                  | EN | WDT                 | Г                   | WDTOUT              | (Initial value: **11 | 1001)         |

| ,       |        |          |                |           |                      |    |                     |                     |                     | _                    |               |

|         | WDTEN  | Watchdog | g timer enable | e/disable | 0: Disab<br>1: Enab  | •  | /riting the disab   | le code to          | WDTCR2 is           | required.)           | Write<br>only |

|         |        |          |                |           |                      |    | NORMA               | L1/2 mod            | e                   | SLOW1/2              |               |

|         |        |          |                |           |                      |    | DV7CK = 0           | DV                  | 7CK = 1 ((          | mode                 |               |

|         | MOTT   | Watchdog | g timer detect | tion time | 00                   |    | 2 <sup>25</sup> /fc | 2                   | 2 <sup>17</sup> /fs | 2 <sup>17</sup> /fs  | Write         |

|         | WDTT   | [s]      |                |           | 01                   |    | 2 <sup>23</sup> /fc | $\langle \rangle^2$ | 2 <sup>15</sup> /fs | 2 <sup>15</sup> fs   | only          |

|         |        |          |                |           | 10                   |    | 2 <sup>21</sup> fc  |                     | 2 <sup>13</sup> /fs | 2 <sup>13</sup> fs   |               |

|         |        |          |                |           | 11                   |    | 2 <sup>19</sup> /fc |                     | 2 <sup>11</sup> /fs | 2 <sup>11</sup> /fs  |               |

|         | WDTOUT | Watchdog | g timer outpu  | t select  | 0: Interr<br>1: Rese | •  | · /                 | $\sim$              |                     |                      | Write<br>only |

| -       |        |          |                |           |                      |    |                     |                     | $\checkmark$        |                      | >             |

Note 1: After clearing WDTOUT to "0", the program cannot set it to "1".

- Note 2: fc: High-frequency clock [Hz], fs: Low-frequency clock [Hz], f: Don't care Note 3: WDTCR1 is a write-only register and must not be used with any of read-modify-write instructions. If WDTCR1 is read, a don't care is read.

- Note 4: To activate the STOP mode, disable the watchdog timer or clear the counter immediately before entering the STOP mode. After clearing the counter, clear the counter again immediately after the STOP mode is inactivated.

- Note 5: To clear WDTEN, set the register in accordance with the procedures shown in "1.2.3 Watchdog Timer Disable".

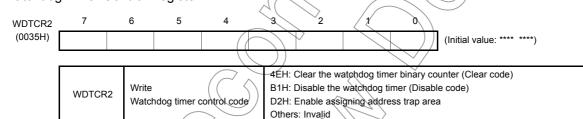

### Watchdog Timer Control Register 2

Note 1: The disable code is valid only when WDTCR1-WDTEN> = 0.

Note 2: \*: Don't care

Note 3: The binary counter of the watchdog timer must not be cleared by the interrupt task.

Note 4: Write the clear code 4EH using a cycle shorter than 3/4 of the time set in WDTCR1<WDTT>.

## 7.2.2 Watchdog Timer Enable

Setting WDTCR1<WDTEN to "1" enables the watchdog timer. Since WDTCR1<WDTEN> is initialized to "1" during reset, the watchdog timer is enabled automatically after the reset release.

## 7.3 Address Trap

The Watchdog Timer Control Register 1 and 2 share the addresses with the control registers to generate address traps.

### 7.3.1 Selection of Address Trap in Internal RAM (ATAS)

WDTCR1<ATAS> specifies whether or not to generate address traps in the internal RAM area. To execute an instruction in the internal RAM area, clear WDTCR1<ATAS> to "0". To enable the WDTCR1<ATAS> setting, set WDTCR1<ATAS> and then write D2H to WDTCR2.

Executing an instruction in the SER area generates an address trap unconditionally regardless of the setting in WDTCR1<ATAS>.

## 7.3.2 Selection of Operation at Address Trap (ATOUT)

When an address trap is generated, either the interrupt request or the reset request can be selected by WDTCR1<ATOUT>.

## 7.3.3 Address Trap Interrupt (INTATRAP)

While WDTCR1<ATOUT is "0", if the CPU should start looping for some cause such as noise and an attempt be made to fetch an instruction from the on-chip RAM (while WDTCR1<ATAS> is "1") or the SFR area, address trap interrupt (INTATRAP) will be generated.

An address trap interrupt is a non-maskable interrupt which can be accepted regardless of the interrupt master flag (IMF).

When an address trap interrupt is generated while the other interrupt including a watchdog timer interrupt is already accepted, the new address trap is processed immediately and the previous interrupt is held pending. Therefore, if address trap interrupts are generated continuously without execution of the RETN instruction, too many levels of nesting may cause a malfunction of the microcontroller.

To generate address trap interrupts, set the stack pointer beforehand.

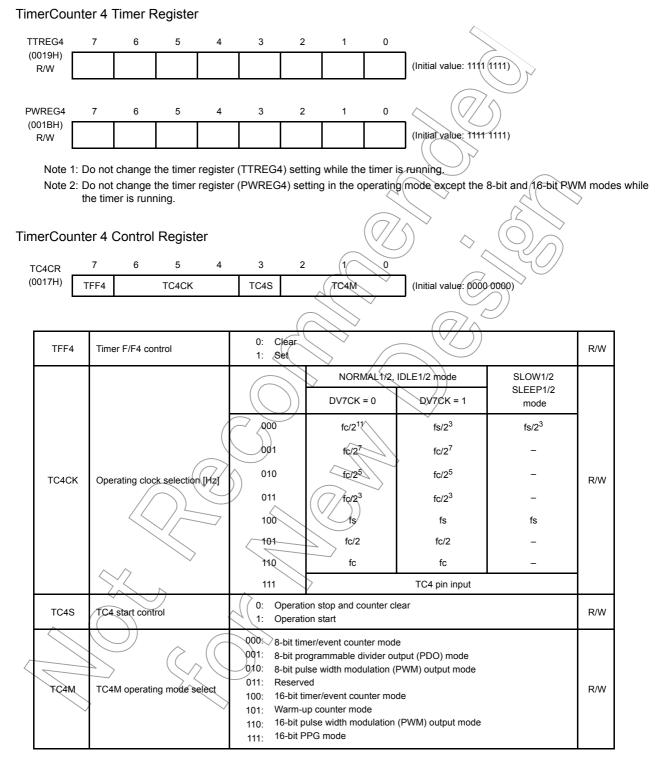

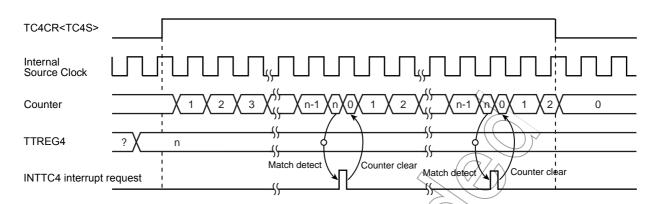

The TimerCounter 4 is controlled by the TimerCounter 4 control register (TC4CR) and two 8-bit timer registers (TTREG4 and PWREG4).

Note 1: fc: High-frequency clock [Hz] fs: Low-frequency clock [Hz]

- Note 2: Do not change the TC4M, TC4CK and TFF4 settings while the timer is running.

- Note 3: To stop the timer operation (TC4S=  $1 \rightarrow 0$ ), do not change the TC4M, TC4CK and TFF4 settings.

- To start the timer operation (TC4S= 0  $\rightarrow$  1), TC4M, TC4CK and TFF4 can be programmed.

- Note 4: When TC4M= 1\*\* (upper byte in the 16-bit mode), the source clock becomes the TC4 overflow signal regardless of the TC3CK setting.

- Note 5: To use the TimerCounter in the 16-bit mode, select the operating mode by programming TC4M, where TC3CR<TC3 M> must be set to 011.

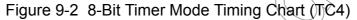

#### 9.3.2 8-Bit Event Counter Mode (TC3, 4)

In the 8-bit event counter mode, the up-counter counts up at the falling edge of the input pulse to the TCj pin. When a match between the up-counter and the TTREG value is detected, an INTTCj interrupt is generated and the up-counter is cleared. After being cleared, the up-counter restarts counting at the falling edge of the input pulse to the TCj pin. Two machine cycles are required for the low- or high-level pulse input to the TCj pin. Therefore, a maximum frequency to be supplied is  $fc/2^4$  Hz in the NORMAL1/2 or IDLE1/2 mode, and  $fs/2^4$  Hz in the SLOW1/2 or SLEEP1/2 mode.

- Note 1: In the event counter mode, fix TCjCR<TFFj> to 0. If not fixed, the PDOj, PWMj and PPGj pins may output pulses.

- Note 2: In the event counter mode, do not change the TTREGj setting while the timer is running. Since TTREGj is not in the shift register configuration in the event counter mode, the new value programmed in TTREGj is in effect immediately after the programming. Therefore, if TTREGi is changed while the timer is running, an expected operation may not be obtained.

### 9.3.3 8-Bit Programmable Divider Output (PDO) Mode (TC3, 4)

This mode is used to generate a pulse with a 50% duty cycle from the  $\overline{\text{PDOj}}$  pin.

In the PDO mode, the up-counter counts up using the internal clock. When a match between the up-counter and the TTREGj value is detected, the logic level output from the  $\overline{PDOj}$  pin is switched to the opposite state and the up-counter is cleared. The INTTCj interrupt request is generated at the time. The logic state opposite to the timer F/Fj logic level is output from the  $\overline{PDOj}$  pin. An arbitrary value can be set to the timer F/Fj by TCjCR<TFFj>. Upon reset, the timer F/Fj value is initialized to 0.

To use the programmable divider output, set the output latch of the I/O port to 1.

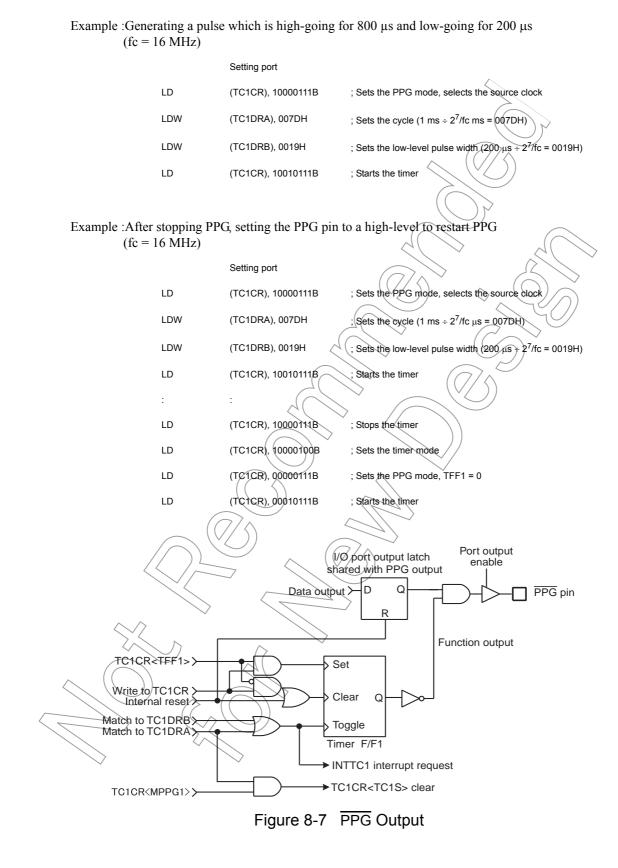

### 9.3.8 16-Bit Programmable Pulse Generate (PPG) Output Mode (TC3 and 4)

This mode is used to generate pulses with up to 16-bits of resolution. The timer counter 3 and 4 are cascadable to enter the 16-bit PPG mode.

The counter counts up using the internal clock or external clock. When a match between the up-counter and the timer register (PWREG3, PWREG4) value is detected, the logic level output from the timer F/F4 is switched to the opposite state. The counter continues counting. The logic level output from the timer F/F4 is switched to the opposite state again when a match between the up-counter and the timer register (TTREG3, TTREG4) value is detected, and the counter is cleared. The INTTC4 interrupt is generated at this time.

Two machine cycles are required for the high- or low-level pulse input to the TC3 pin. Therefore, a maximum frequency to be supplied is  $fc/2^4$  Hz in the NORMAL1 or IDLE1 mode, and  $fc/2^4$  to in the SLOW1/2 or SLEEP1/2 mode.

Since the initial value can be set to the timer F/F4 by TC4CR<TFF4>, positive and negative pulses can be generated. Upon reset, the timer F/F4 is cleared to 0.

(The logic level output from the  $\overline{PPG4}$  pin is the opposite to the timer F/F4.)

Set the lower byte and upper byte in this order to program the timer register. (TTREG3  $\rightarrow$  TTREG4, PWREG3  $\rightarrow$  PWREG4) (Programming only the upper or lower byte should not be attempted.)

For PPG output, set the output latch of the I/O port to 1.

Example :Generating a pulse with 1-ms high-level width and a period of 16.385 ms (fc = 16.0 MHz)

|     | Setting ports   | $\sim$                                                                             |

|-----|-----------------|------------------------------------------------------------------------------------|

| LDW | (PWREG3), 07D0H | : Sets the pulse width.                                                            |

| LDW | (TTREG3), 8002H | : Sets the cycle period.                                                           |

| LD  | (TC3GR), 33H    | : Sets the operating clock to fc/2 <sup>3</sup> , and16-bit PPG mode (lower byte). |

| LD  | (TC4CR), 057H   | : Sets TFF4 to the initial value 0, and 16-bit<br>PPG mode (upper byte).           |

|     | (TC4CR), 05FH   | Starts the timer.                                                                  |

|     | 9 6             | $\gamma \sim$                                                                      |

- Note 1: In the PPG mode, do not change the PWREGi and TREGi settings while the timer is running. Since PWREGi and TTREGi are not in the shift register configuration in the PPG mode, the new values programmed in PWREGi and TTREGi are in effect immediately after programming PWREGi and TTREGi. Therefore, if PWREGi and TTREGi are changed while the timer is running, an expected operation may not be obtained.

- Note 2: When the timer is stopped during PPG output, the PPG4 pin holds the output status when the timer is stopped. To change the output status, program TC4CR<TFF4> after the timer is stopped. Do not change TC4CR<TFF4> upon stopping of the timer.

Example: Fixing the PPG4 pin to the high level when the TimerCounter is stopped

- CLR (TC4CR).3: Stops the timer

- CLR (TC4CR).7: Sets the PPG4 pin to the high level

Note 3: i = 3, 4

#### (2) LSB receive mode

LSB receive mode is selected by setting SIOCR1<SIODIR> to "1", in which case the data is received sequentially beginning with the least significant bit (Bit0).

#### 10.3.2.3 Transmit/receive mode

#### (1) MSB transmit/receive mode

MSB transmit/receive mode are selected by setting SIOCR SIODIR> to "0" in which case the data is transferred sequentially beginning with the most significant bit (Bit7) and the data is received sequentially beginning with the most significant (Bit7).

(2) LSB transmit/receive mode

LSB transmit/receive mode are selected by setting SIOCR1<SIODIR to "1", in which case the data is transferred sequentially beginning with the least significant bit (Bit0) and the data is received sequentially beginning with the least significant (Bit0).

#### 10.3.3 Transfer modes

Transmit, receive and transmit/receive mode are selected by using \$10CR) \$SIOM>.

#### 10.3.3.1 Transmit mode

Transmit mode is selected by writing "00B" to SIOCR1<SIOM>.

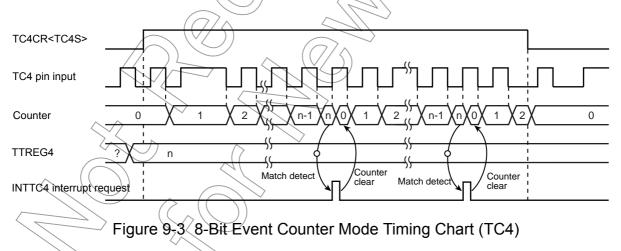

(1) Starting the transmit operation

Transmit mode is selected by setting "00B" to SIOCR1<SIOM>. Serial clock is selected by using SIOCR1<SCK>. Transfer direction is selected by using SIOCR1<SIODIR>.

When a transmit data is written to the transmit buffer register (SIOTDB), SIOSR<TXF> is cleared to "0".

After SIOCR1<SIOS> is set to "1", SIOSR<SIOF> is set synchronously to "1" the falling edge of SCK pin.

The data is transferred sequentially starting from SO pin with the direction of the bit specified by SIOCR1<SIODIR>, synchronizing with the SCK pin's falling edge.

SIOSR SEF is kept in high level, between the first clock falling edge of  $\overline{SCK}$  pin and eighth clock falling edge.

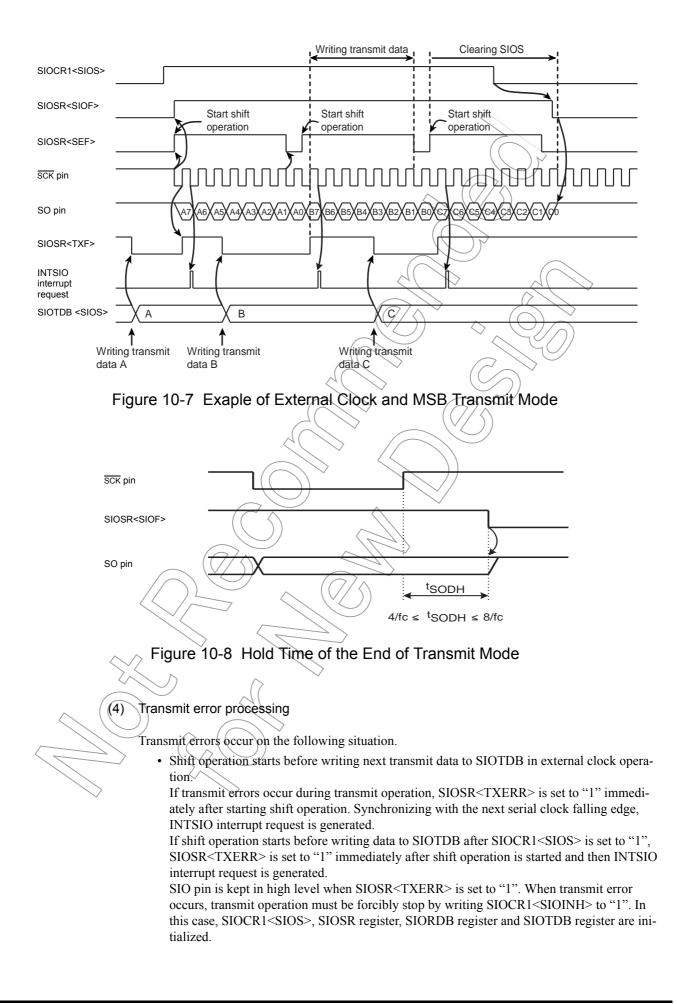

SIOSR $\langle TXF \rangle$  is set to "1" at the rising edge of pin after the data written to the SIOTDB is transferred to shift register, then the INTSIO interrupt request is generated, synchronizing with the next falling edge on  $\overline{SCK}$  pin.

- Note 1: In internal clock operation, when SIOCR1<SIOS> is set to "1", transfer mode does not start without writing a transmit data to the transmit buffer register (SIOTDB).

- Note 2: In internal clock operation, when the SIOCR1<SIOS> is set to "1", SIOTDB is transferred to shift register after maximum 1-cycle of serial clock frequency, then a serial clock is output from SCK pin.

- Note 3: In external clock operation, when the falling edge is input from SCK pin after SIOCR1<SIOS> is set to "1", SIOTDB is transferred to shift register immediately.

TOSHIBA

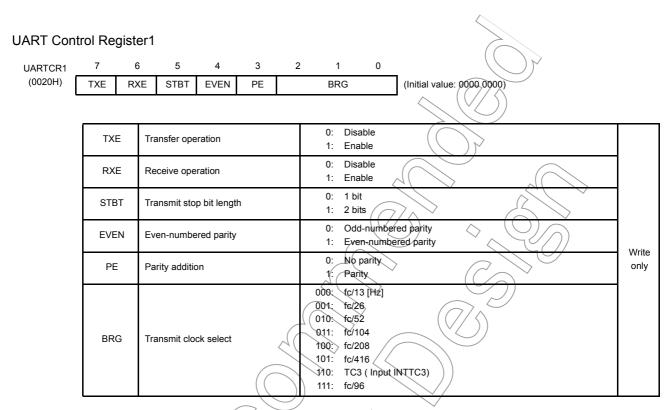

## 11.2 Control

UART is controlled by the UART Control Registers (UARTCR1, UARTCR2). The operating status can be monitored using the UART status register (UARTSR).

Note 1: When operations are disabled by setting TXE and RXE bit to "0", the setting becomes valid when data transmit or receive complete. When the transmit data is stored in the transmit data buffer, the data are not transmitted. Even if data transmit is enabled, until new data are written to the transmit data buffer, the current data are not transmitted.

$((7) \land$

Note 2: The transmit clock and the parity are common to transmit and receive.

))

Note 3: UARTCR1<RXE> and UARTCR1<TXE> should be set to "0" before UARTCR1<BRG> is changed.

| UART Control Register2                           |                                                                                                                                                                                                                                                    |               |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| UARTCR2 7 6 5 4 3<br>(0021H)                     | 2 1 0<br>RXDNC STOPBR (Initial value: **** *000)                                                                                                                                                                                                   |               |

|                                                  | $\searrow$                                                                                                                                                                                                                                         |               |

| RXDNC Selection of RXD input noise rejectio time | <ul> <li>00: No noise rejection (Hysteresis input)</li> <li>01: Rejects pulses shorter than 31/fc [s] as noise</li> <li>10: Rejects pulses shorter than 63/fc [s] as noise</li> <li>11: Rejects pulses shorter than 127/fc [s] as noise</li> </ul> | Write<br>only |

| STOPBR Receive stop bit length                   | 0: 1 bit<br>1: 2 bits                                                                                                                                                                                                                              |               |

Note: When UARTCR2<RXDNC> = "01", pulses longer than 96/fc [s] are always regarded as signals; when UARTCR2<RXDNC> = "10", longer than 192/fc [s]; and when UARTCR2<RXDNC> = "11", longer than 384/fc [s].

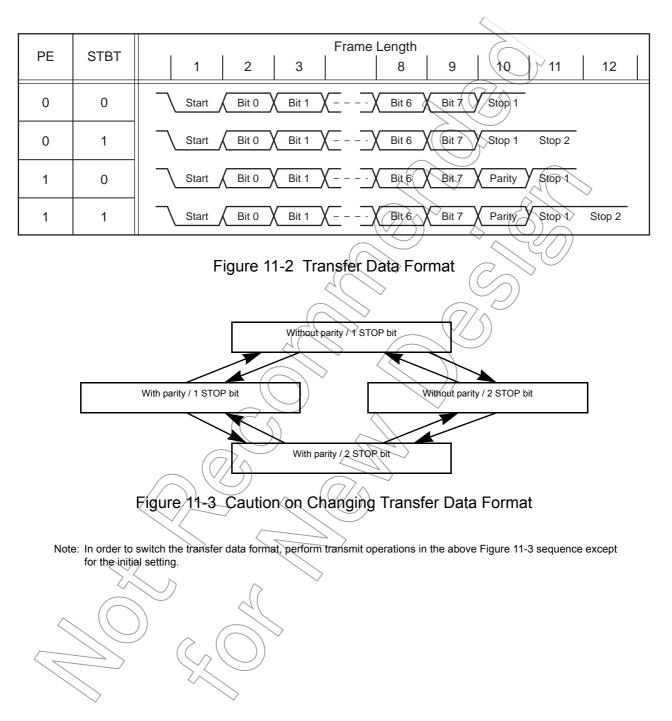

## 11.3 Transfer Data Format

In UART, an one-bit start bit (Low level), stop bit (Bit length selectable at high level, by UARTCR1<STBT>), and parity (Select parity in UARTCR1<PE>; even- or odd-numbered parity by UARTCR1<EVEN>) are added to the transfer data. The transfer data formats are shown as follows.

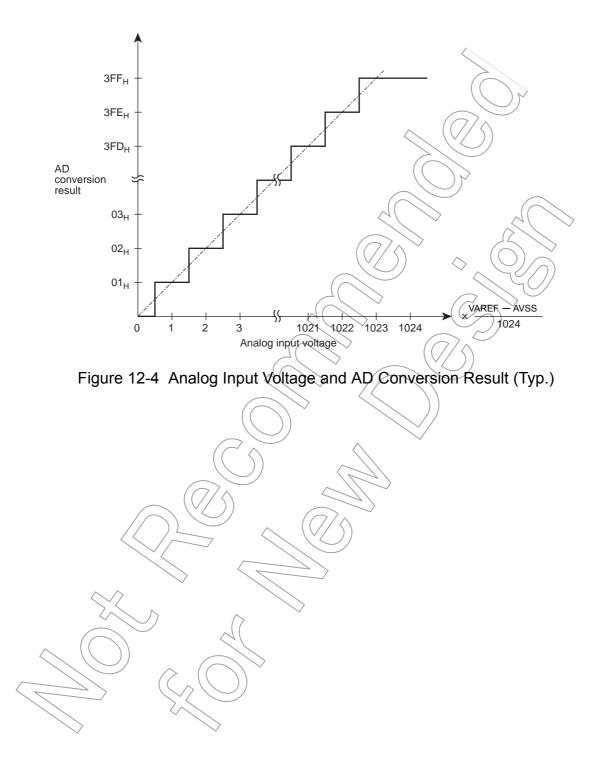

## 12.5 Analog Input Voltage and AD Conversion Result

The analog input voltage is corresponded to the 10-bit digital value converted by the AD as shown in Figure 12-4.

#### 14.1.2.2 Program Writing using a General-purpose PROM Programmer

1. Recommended OTP adaptor

BM11687 for TMP86PM47AUG

2. Setting of OTP adaptor

Set the switch (SW1) to "N" side.

- 3. Setting of PROM programmer

- a. Set PROM type to TC571000D/AD.

Vpp: 12.75 V (high-speed program writing mode)

b. Data transmission ( or Copy) (Note 1)

The PROM of TMP86PM47AUG is located on different address; it depends on operating mode: MCU mode and PROM mode. When you write the data of ROM for mask ROM products, the data shuold be transferred (or copied ) from the address for MCU mode to that for PROM mode before writing operation is executed. For the applicable program areas of MCU mode and PROM mode are different, refer to TMP86PM47AUG" Figure 14-1 Program Memory Area ".

Example: In the block transfer (copy) mode, executed as below.

32KB ROM capacity: 08000~0FFFFH → 00000~07EFFH

16KB ROM capacity: 0C000~0FFFFH → 04000~07FFFH

8KB ROM capacity )  $0E000 \sim 0FFFFH \rightarrow 06000 \sim 07FFFH$

4KB ROM capacity : 0F000~0FFFEH → 07000~07FFFH

c. Setting of the program address (Note 1).

Start address: 0000H (When 16 KB ROM capacity, start address is 4000H. When 8 KB ROM capacity, start address is 6000H. When 4KB ROM capacity, start address is 7000H.)

End address: 7FFFH

#### 4. Writting

Write and verify according to the above procedure "Setting of PROM programmer".

Note 1. For the setting/method, refer to each description of PROM programmer.

Make sure to set the data of address area that is not in use to FFH.

Note 2: When setting MCU to the adaptor or when setting the adaptor to the PROM programmer, set the first pin of the adaptor and that of PROM programmer socket matched. If the first pin is conversely set, MCU or adaptor or programmer would be damaged.

Note 3: The TMP86PM47AUG does not support the electric signature mode.

If PROM programmer uses the signature, the device would be damaged because of applying voltage of  $12\pm0.5V$  to pin 9(A9) of the address. Don't use the signature.

## TOSHIBA

## 16. Electrical Characteristics

## 16.1 Absolute Maximum Ratings

The absolute maximum ratings are rated values, which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

$\bigcap$

|                                 |                   |                          | (                             | √ <sub>SS</sub> = 0 V) |  |

|---------------------------------|-------------------|--------------------------|-------------------------------|------------------------|--|

| Parameter                       | Symbol            | Pins                     | Ratings                       | Unit                   |  |

| Supply voltage                  | V <sub>DD</sub>   |                          | -0.3 to 6.5                   |                        |  |

| Program voltage                 | V <sub>PP</sub>   | TEST/V <sub>PP</sub>     | -0.3 to 13.0                  | v                      |  |

| Input voltage                   | V <sub>IN</sub>   |                          | –0.3 to V <sub>DD</sub> + 0.3 | V                      |  |

| Output voltage                  | V <sub>OUT</sub>  | P21, P22, Tri-state port | -0.3 to V <sub>DB</sub> + 0.3 |                        |  |

| Output current (Per 1 pin)      | I <sub>OUT1</sub> | P1, P3, P4 port          | -1.8                          |                        |  |

|                                 | I <sub>OUT2</sub> | P1, P3 port              | 3.2                           |                        |  |

|                                 | I <sub>OUT3</sub> | P0, P2, P4 port          | 30                            | mA                     |  |

| Output current (Total)          | $\Sigma I_{OUT2}$ | P1, P3 port              | 60                            |                        |  |

|                                 | $\Sigma I_{OUT3}$ | P0, P2, P4 port          | 80                            |                        |  |

| Power dissipation [Topr = 85°C] | PD                |                          | 250                           | mW                     |  |

| Soldering temperature (Time)    | Tsld              |                          | 260 (10 s)                    |                        |  |

| Storage temperature             | Tstg              |                          | -55 to 125                    | °C                     |  |

| Operating temperature           | Topr              |                          | -40 to 85                     |                        |  |

## 16.6 DC Characteristics, AC Characteristics (PROM mode)

### 16.6.1 Read operation in PROM mode

|                                           |                  |                             |      | (V <sub>SS</sub> = | 0 V, Topr = -4  | ₩0 to 85°C) |

|-------------------------------------------|------------------|-----------------------------|------|--------------------|-----------------|-------------|

| Parameter                                 | Symbol           | Condition                   | Min  | Typ.               | Max             | Unit        |

| High level input voltage (TTL)            | V <sub>IH4</sub> |                             | 2.2  |                    | V <sub>CC</sub> | -           |

| Low level input voltage (TTL)             | V <sub>IL4</sub> |                             | 0    | <u> </u>           | 0.8             |             |

| Power supply                              | V <sub>CC</sub>  |                             |      |                    |                 | V           |

| Program supply of program                 | V <sub>PP</sub>  |                             | 4.75 | 5.0                | 5.25            |             |

| Address access time                       | t <sub>ACC</sub> | $V_{CC}$ = 5.0 $\pm$ 0.25 V |      | 1.5tcyc + 300      | _               | ns          |

| Note: tcyc = 500 ns at 8 MH:<br>A16 to A0 | z<br>            | ((                          | 7    |                    |                 |             |

|                                           |                  |                             |      |                    | ( ) )           |             |

| CE                                        |                  |                             | >    | C                  |                 |             |

| ŌE                                        |                  |                             |      |                    |                 |             |

| PGM                                       |                  | tacc                        |      |                    |                 |             |

| D7 to D0                                  | High-Z           | Data outpu                  |      |                    |                 |             |

|                                           |                  |                             |      |                    |                 |             |