Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                   |

|----------------------------|-------------------------------------------------------------------|

| Product Status             | Obsolete                                                          |

| Core Processor             | MAXQ20S                                                           |

| Core Size                  | 16-Bit                                                            |

| Speed                      | 12MHz                                                             |

| Connectivity               | SPI, UART/USART                                                   |

| Peripherals                | Brown-out Detect/Reset, Infrared, Power-Fail, POR, WDT            |

| Number of I/O              | 24                                                                |

| Program Memory Size        | 48KB (48K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 1.5K x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                       |

| Data Converters            | -                                                                 |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 44-TQFP                                                           |

| Supplier Device Package    | 44-TQFP (10x10)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/maxq613k-0000 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 16-Bit Microcontroller with Infrared Module

| LIST OF FIGURES                                                                  |

|----------------------------------------------------------------------------------|

| Figure 1. IR Transmit Frequency Shifting Example (IRCFME = 0)                    |

| Figure 2. IR Transmit Carrier Generation and Carrier Modulator Control           |

| Figure 3. IR Transmission Waveform (IRCFME = 0)                                  |

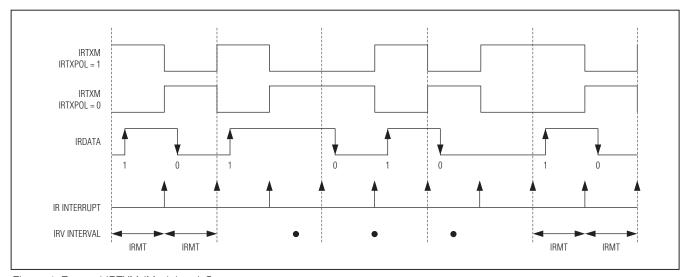

| Figure 4. External IRTXM (Modulator) Output                                      |

| Figure 5. IR Capture                                                             |

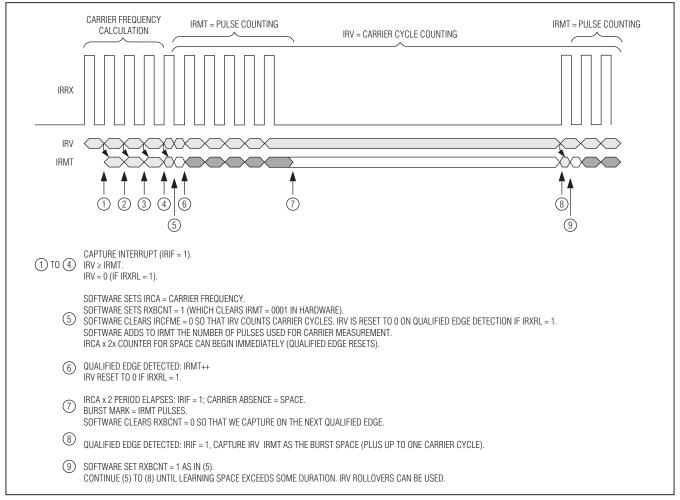

| Figure 6. Receive Burst-Count Example                                            |

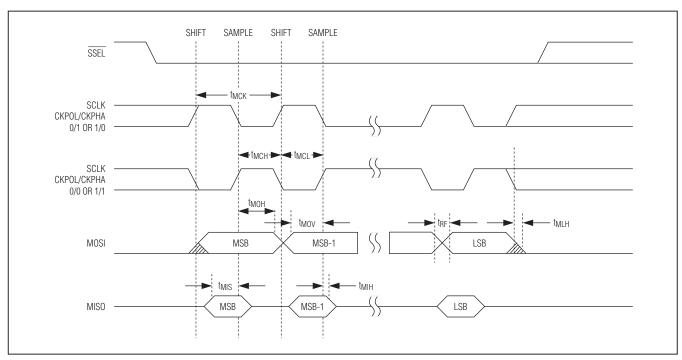

| Figure 7. SPI Master Communication Timing                                        |

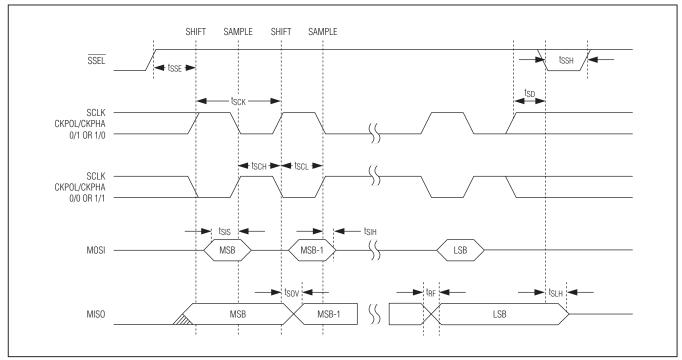

| Figure 8. SPI Slave Communication Timing                                         |

| Figure 9. On-Chip Oscillator                                                     |

| Figure 10. In-Circuit Debugger                                                   |

| Figure 11. Power-Fail Detection During Normal Operation                          |

| Figure 12. Stop Mode Power-Fail Detection States with Power-Fail Monitor Enabled |

| Figure 13. Stop Mode Power-Fail Detection with Power-Fail Monitor Disabled       |

| LIST OF TABLES                                                                   |

| Table 1. Memory Areas and Associated Maximum Privilege Levels                    |

| Table 2. Watchdog Interrupt Timeout (Sysclk = 12MHz, CD[1:0] = 00)               |

| Table 3. USART Mode Details                                                      |

| Table 4. Power-Fail Detection States During Normal Operation                     |

| Table 5. Stop Mode Power-Fail Detection States with Power-Fail Monitor Enabled   |

| Table 6. Stop Mode Power-Fail Detection States with Power-Fail Monitor Disabled  |

## 16-Bit Microcontroller with Infrared Module

#### **ABSOLUTE MAXIMUM RATINGS**

| 44 TQFN (single-layer board)                 |                 |

|----------------------------------------------|-----------------|

| (derate 27mW/°C above +70°C)                 | 2162.2mW        |

| 44 TQFN (multilayer board)                   |                 |

| (derate 37mW/°C above +70°C)                 | 2963mW          |

| Operating Temperature Range                  | 0°C to +70°C    |

| Storage Temperature Range                    | -65°C to +150°C |

| Lead Temperature (excluding dice; soldering, | 10s)+300°C      |

| Soldering Temperature (reflow)               | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

$(V_{DD} = V_{RST} \text{ to } 3.6V, T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}, \text{ unless otherwise noted.}) (Note 1)$

| PARAMETER                                                   | SYMBOL            | CO                         | NDITIONS                                    | MIN                   | TYP                                                                      | MAX                   | UNITS |

|-------------------------------------------------------------|-------------------|----------------------------|---------------------------------------------|-----------------------|--------------------------------------------------------------------------|-----------------------|-------|

| Supply Voltage                                              | $V_{DD}$          |                            |                                             | V <sub>RST</sub>      |                                                                          | 3.6                   | V     |

| 1.8V Internal Regulator                                     | VREG18            |                            |                                             | 1.62                  | 1.8                                                                      | 1.98                  | V     |

| Power-Fail Warning Voltage for Supply                       | VPFW              | Monitors V <sub>DD</sub> ( | Note 2)                                     | 1.75                  | 1.8                                                                      | 1.85                  | V     |

| Power-Fail Reset Voltage                                    | VRST              | Monitors V <sub>DD</sub> ( | Note 3)                                     | 1.64                  | 1.67                                                                     | 1.70                  | V     |

| POR Voltage                                                 | Vpor              | Monitors V <sub>DD</sub>   |                                             | 1                     |                                                                          | 1.42                  | V     |

| RAM Data-Retention Voltage                                  | VDRV              | (Note 4)                   |                                             | 1.0                   |                                                                          |                       | V     |

| Active Current                                              | I <sub>DD_1</sub> | Sysclk = 12MH              |                                             |                       | 3.25                                                                     | 4                     | mA    |

|                                                             | I <sub>S1</sub>   | Power-Fail Off             | T <sub>A</sub> = +25°C                      |                       | 0.2                                                                      | 2.0                   |       |

| Stop-Mode Current                                           | 181               | Fower-Fair Oil             | $T_A = 0$ °C to +70°C                       |                       | 0.2                                                                      | 8                     |       |

| Stop-Mode Current                                           | I <sub>S2</sub>   | Power-Fail On              | T <sub>A</sub> = +25°C                      |                       | 22                                                                       | 29.5                  | μΑ    |

|                                                             | 152               | 1 Ower-r all Off           | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$ |                       | 27.6                                                                     | 42                    |       |

| Current Consumption During<br>Power-Fail                    | IPFR              | (Note 6)                   |                                             | , ,                   | [(3 x l <sub>S2</sub> ) +<br>PCI - 3) x (l <sub>S</sub> :<br>INANO))]/PC |                       | μΑ    |

| Power Consumption During POR                                | IPOR              | (Note 7)                   |                                             |                       | 100                                                                      |                       | nA    |

| Stop-Mode Resume Time                                       | ton               |                            |                                             | ;                     | 375 + (8192<br>tHFXIN)                                                   | X                     | μs    |

| Power-Fail Monitor Startup<br>Time                          | tPFM_ON           | (Note 4)                   |                                             |                       |                                                                          | 150                   | μs    |

| Power-Fail Warning Detection<br>Time                        | tPFW              | (Note 8)                   |                                             | 10                    |                                                                          |                       | μs    |

| Input Low Voltage for IRTX, IRRX, RESET, and All Port Pins  | VIL               |                            |                                             | VGND                  |                                                                          | 0.3 x V <sub>DD</sub> | V     |

| Input High Voltage for IRTX, IRRX, RESET, and All Port Pins | VIH               |                            |                                             | 0.7 x V <sub>DD</sub> |                                                                          | V <sub>DD</sub>       | V     |

# 16-Bit Microcontroller with Infrared Module

#### RECOMMENDED OPERATING CONDITIONS (continued)

$(VDD = VRST \text{ to } 3.6V, TA = 0^{\circ}C \text{ to } +70^{\circ}C, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                                   | SYMBOL    | CONDITIONS | MIN                 | TYP MAX                      | UNITS  |

|---------------------------------------------|-----------|------------|---------------------|------------------------------|--------|

| WAKE-UP TIMER                               | •         |            |                     |                              |        |

| Wake-Up Timer Interval                      | twakeup   |            | 1/f <sub>NANO</sub> | 65,535/<br>f <sub>NANO</sub> | S      |

| FLASH MEMORY                                |           |            |                     |                              |        |

| System Clock During Flash Programming/Erase | fFPSYSCLK |            | 6                   |                              | MHz    |

| Flash Erase Time                            | tME       | Mass erase | 20                  | 40                           | mo     |

| Flash Erase Time                            | terase    | Page erase | 20                  | 40                           | ms     |

| Flash Programming Time per<br>Word          | tprog     | (Note 10)  | 20                  | 100                          | μs     |

| Write/Erase Cycles                          |           |            | 20,000              |                              | Cycles |

| Data Retention                              |           | TA = +25°C | 100                 |                              | Years  |

| IR                                          | •         |            |                     |                              |        |

| Carrier Frequency                           | fIR       | (Note 4)   |                     | fck/2                        | Hz     |

#### SPI ELECTRICAL CHARACTERISTICS

$(V_{DD} = V_{RST} \text{ to } 3.6V, T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}, \text{ unless otherwise noted.}) \text{ (Note 11)}$

| PARAMETER                                               | SYMBOL     | CONDITIONS                            | MIN                                          | TYP    | MAX                | UNITS |

|---------------------------------------------------------|------------|---------------------------------------|----------------------------------------------|--------|--------------------|-------|

| SPI Master Operating Frequency                          | 1/tMCK     |                                       |                                              |        | fck/2              | MHz   |

| SPI Slave Operating Frequency                           | 1/tsck     |                                       |                                              |        | f <sub>CK</sub> /4 | MHz   |

| SPI I/O Rise/Fall Time                                  | tspi_rf    | $C_L = 15 pF$ , pullup = $560 \Omega$ | 8.3                                          |        | 23.6               | ns    |

| SCLK Output Pulse-Width High/Low                        | tMCH, tMCL |                                       | tMCK/2 -<br>tspi_rf                          |        |                    | ns    |

| MOSI Output Hold Time After SCLK Sample Edge            | tMOH       |                                       | t <sub>MCK</sub> /2 -<br>t <sub>SPI_RF</sub> |        |                    | ns    |

| MOSI Output Valid to Sample Edge                        | tMOV       |                                       | t <sub>MCK</sub> /2 -<br>t <sub>SPI_RF</sub> |        |                    | ns    |

| MISO Input Valid to SCLK<br>Sample Edge Rise/Fall Setup | tMIS       |                                       | 25                                           |        |                    | ns    |

| MISO Input to SCLK Sample<br>Edge Rise/Fall Hold        | tMIH       |                                       | 0                                            |        |                    | ns    |

| SCLK Inactive to MOSI Inactive                          | tMLH       |                                       | t <sub>MCK</sub> /2 -<br>t <sub>SPI_RF</sub> |        |                    | ns    |

| SCLK Input Pulse-Width High/<br>Low                     | tsch, tscl |                                       |                                              | tsck/2 |                    | ns    |

| SSEL Active to First Shift Edge                         | tsse       |                                       | tspi_rf                                      |        |                    | ns    |

| MOSI Input to SCLK Sample<br>Edge Rise/Fall Setup       | tsis       |                                       | tspi_rf                                      |        |                    | ns    |

## 16-Bit Microcontroller with Infrared Module

#### SPI ELECTRICAL CHARACTERISTICS (continued)

$(VDD = VRST \text{ to } 3.6V, TA = 0^{\circ}C \text{ to } +70^{\circ}C, \text{ unless otherwise noted.})$  (Note 11)

| PARAMETER                                             | SYMBOL           | CONDITIONS | MIN              | TYP | MAX                                        | UNITS |

|-------------------------------------------------------|------------------|------------|------------------|-----|--------------------------------------------|-------|

| MOSI Input from SCLK<br>Sample Edge Transition Hold   | <sup>t</sup> SIH |            | tspi_rf          |     |                                            | ns    |

| MISO Output Valid After SCLK<br>Shift Edge Transition | tsov             |            |                  |     | 2tspi_rf                                   | ns    |

| SSEL Inactive                                         | tssh             |            | tCK +<br>tSPI_RF |     |                                            | ns    |

| SCLK Inactive to SSEL Rising                          | tsd              |            | tspi_rf          |     |                                            | ns    |

| MISO Output Disabled After SSEL Edge Rise             | tslh             |            |                  |     | 2t <sub>CK</sub> +<br>2t <sub>SPI_RF</sub> | ns    |

- **Note 1:** Specifications to 0°C are guaranteed by design and are not production tested. Typical = +25°C, V<sub>DD</sub> = +3.3V, unless otherwise noted.

- **Note 2:** VPFW can be programmed to the following nominal voltage trip points: 1.8V, 1.9V, 2.55V, and 2.75V ±3%. The values listed in the *Recommended Operating Conditions* table are for the default configuration of 1.8V nominal.

- **Note 3:** The power-fail reset and POR detectors are designed to operate in tandem to ensure that one or both of these signals is active at all times when V<sub>DD</sub> < V<sub>RST</sub>, ensuring the device maintains the reset state until minimum operating voltage is achieved.

- Note 4: Guaranteed by design and not production tested.

- **Note 5:** Measured on the VDD pin and the device not in reset. All inputs are connected to GND or VDD. Outputs do not source/ sink any current. The device is executing code from flash memory.

- Note 6: The power-check interval (PCI) can be set to always on, or to 1024, 2048, or 4096 nanopower ring clock cycles.

- Note 7: Current consumption during POR when powering up while VDD is less than the POR release voltage.

- **Note 8:** The minimum amount of time that V<sub>DD</sub> must be below V<sub>PFW</sub> before a power-fail event is detected; refer to the *MAXQ610 User's Guide* for details.

- **Note 9:** The maximum total current, I<sub>OH(MAX)</sub> and I<sub>OL(MAX)</sub>, for all listed outputs combined should not exceed 32mA to satisfy the maximum specified voltage drop. This does not include the IRTX output.

- Note 10: Programming time does not include overhead associated with utility ROM interface.

- Note 11: AC electrical specifications are guaranteed by design and are not production tested.

# 16-Bit Microcontroller with Infrared Module

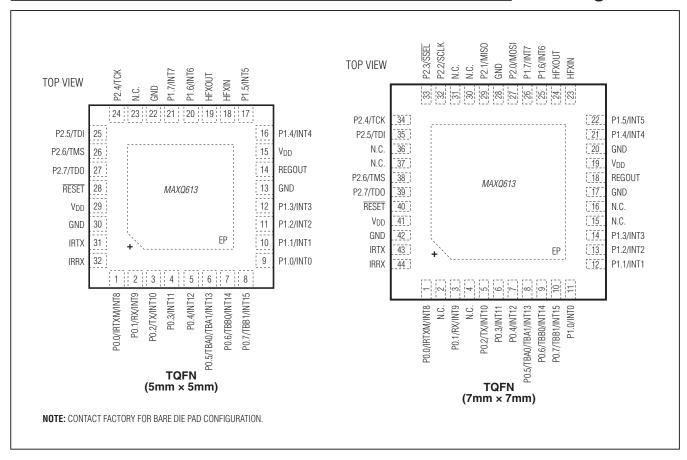

#### **Pin Configurations**

#### Pin Description

|                   | PIN            |                   |        |                                                                                                                                                                                                                                          |  |

|-------------------|----------------|-------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BARE DIE          | 32 TQFN-<br>EP | 44 TQFN-<br>EP    | NAME   | FUNCTION                                                                                                                                                                                                                                 |  |

|                   |                |                   |        | POWER PINS                                                                                                                                                                                                                               |  |

| 15, 36            | 15, 29         | 19, 41            | VDD    | Supply Voltage                                                                                                                                                                                                                           |  |

| 13, 16, 25,<br>37 | 13, 22, 30     | 17, 20, 28,<br>42 | GND    | Ground. Connect directly to the ground plane.                                                                                                                                                                                            |  |

| 14                | 14             | 18                | REGOUT | 1.8V Regulator Output. This pin must be connected to ground through 1.0µF external ceramic-chip capacitor. The capacitor must be placed close to this pin as possible. No devices other than the capacitor sho be connected to this pin. |  |

# 16-Bit Microcontroller with Infrared Module

### Pin Description (continued)

|                  | PIN            |                |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                     | scription (continued)                                                                                                                                                                                                      |  |

|------------------|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BARE DIE         | 32 TQFN-<br>EP | 44 TQFN-<br>EP | NAME                                                                                                                                      | FUNCTION                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                            |  |

|                  | l              |                | l                                                                                                                                         | RESET PIN                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                            |  |

| 35               | 28             | 40             | RESET                                                                                                                                     | Digital, Active-Low, Reset Input/Outp as long as this pin is low and begins address 8000h when this pin returns pullup current source; if this pin is dr be driven by an open-drain source c This pin can be left unconnected if the a reset state using an external signal when an internal reset condition occur. | executing from the utility ROM at to a high state. The pin includes iven by an external device, it should apable of sinking in excess of 4mA. Here is no need to place the device in . This pin is driven low as an output |  |

|                  |                |                |                                                                                                                                           | CLOCK PINS                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                            |  |

| 20               | 18             | 23             | HFXIN                                                                                                                                     | High-Frequency Crystal Input. Conn between HFXIN and HFXOUT for us                                                                                                                                                                                                                                                  | e as the high-frequency system                                                                                                                                                                                             |  |

| 21               | 19             | 24             | HFXOUT                                                                                                                                    | clock. Alternatively, HFXIN is the inp                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                            |  |

| IR FUNCTION PINS |                |                |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                            |  |

| 38               | 31             | 43             | IRTX                                                                                                                                      | IR Transmit Output. IR transmission pin capable of sinking 25mA. This pin defaults to a high-impedance input with the weak pullup disabled during all forms of reset. Software must configure this pin after release from reset to remove the high-impedance input condition.                                       |                                                                                                                                                                                                                            |  |

| 39               | 32             | 44             | IRRX                                                                                                                                      | IR Receive Input. This pin defaults to weak pullup disabled during all form this pin after release from reset to recondition.                                                                                                                                                                                       | ns of reset. Software must configure                                                                                                                                                                                       |  |

|                  |                | GENE           | RAL-PURPOS                                                                                                                                | E I/O AND SPECIAL FUNCTION PIN                                                                                                                                                                                                                                                                                      | IS                                                                                                                                                                                                                         |  |

|                  |                |                | nput and output states controlled by port pins default to high-impedance onfigure these pins after release dance condition. All alternate |                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                            |  |

|                  |                |                |                                                                                                                                           | GPIO PORT PIN                                                                                                                                                                                                                                                                                                       | SPECIAL FUNCTION                                                                                                                                                                                                           |  |

| 1                | 1              | 1              | P0.0/IRTXM/<br>INT8                                                                                                                       | P0.0                                                                                                                                                                                                                                                                                                                | IR Modulator Output/INT8                                                                                                                                                                                                   |  |

| 2                | 2              | 3              | P0.1/RX/<br>INT9                                                                                                                          | P0.1                                                                                                                                                                                                                                                                                                                | USART Receive/INT9                                                                                                                                                                                                         |  |

| 3                | 3              | 5              | P0.2/TX/<br>INT10                                                                                                                         | P0.2                                                                                                                                                                                                                                                                                                                | USART Transmit/INT10                                                                                                                                                                                                       |  |

| 4                | 4              | 6              | P0.3/INT11                                                                                                                                | P0.3                                                                                                                                                                                                                                                                                                                | INT11                                                                                                                                                                                                                      |  |

| 5                | 5              | 7              | P0.4/INT12                                                                                                                                | P0.4                                                                                                                                                                                                                                                                                                                | INT12                                                                                                                                                                                                                      |  |

| 6                | 6              | 8              | P0.5/TBA0/<br>TBA1/INT13                                                                                                                  | P0.5                                                                                                                                                                                                                                                                                                                | Type B Timer 0 Pin A or Type B<br>Timer 1 Pin A/INT13                                                                                                                                                                      |  |

# 16-Bit Microcontroller with Infrared Module

## Pin Description (continued)

|          | PIN            |                                    |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |  |  |

|----------|----------------|------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|

| BARE DIE | 32 TQFN-<br>EP | 44 TQFN-<br>EP                     | NAME                | FUNC                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CTION                        |  |  |

| 7        | 7              | 9                                  | P0.6/TBB0/<br>INT14 | P0.6                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Type B Timer 0 Pin B/INT14   |  |  |

| 8        | 8              | 10                                 | P0.7/TBB1/<br>INT15 | P0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Type B Timer 1 Pin B/INT15   |  |  |

|          |                |                                    |                     | Port 1 General-Purpose, Digital I/O Pins with Interrupt Capability. Thes port pins function as general-purpose I/O pins with their input and output states controlled by the PD1, PO1, and PI1 registers. All port pidefault to high-impedance mode after a reset. Software must configure these pins after release from reset to remove the high-impedance condition. All external interrupts must be enabled from software before they can be used. |                              |  |  |

|          |                |                                    |                     | GPIO PORT PIN                                                                                                                                                                                                                                                                                                                                                                                                                                         | EXTERNAL INTERRUPT           |  |  |

| 9        | 9              | 11                                 | P1.0/INT0           | P1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                  | INT0                         |  |  |

| 10       | 10             | 12                                 | P1.1/INT1           | P1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                  | INT1                         |  |  |

| 11       | 11             | 13                                 | P1.2/INT2           | P1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                  | INT2                         |  |  |

| 12       | 12             | 14                                 | P1.3/INT3           | P1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                  | INT3                         |  |  |

| 17       | 16             | 21                                 | P1.4/INT4           | P1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                  | INT4                         |  |  |

| 18       | 17             | 22                                 | P1.5/INT5           | P1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                  | INT5                         |  |  |

| 22       | 20             | 25                                 | P1.6/INT6           | P1.6                                                                                                                                                                                                                                                                                                                                                                                                                                                  | INT6                         |  |  |

| 23       | 21             | 26                                 | P1.7/INT7           | P1.7                                                                                                                                                                                                                                                                                                                                                                                                                                                  | INT7                         |  |  |

|          |                |                                    |                     | Port 2 General-Purpose, Digital I/O Pins. These port pins function as general-purpose I/O pins with their input and output states controlled by the PD2, PO2, and PI2 registers. All port pins default to high-impedance mode after a reset. Software must configure these pins after release from reset to remove the high-impedance condition. All special functions must be enabled from software before they can be used.                         |                              |  |  |

|          |                |                                    |                     | GPIO PORT PIN                                                                                                                                                                                                                                                                                                                                                                                                                                         | SPECIAL FUNCTION             |  |  |

| 24       | _              | 27                                 | P2.0/MOSI           | P2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SPI: Master Out-Slave In     |  |  |

| 26       | _              | 29                                 | P2.1/MISO           | P2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SPI: Master In-Slave Out     |  |  |

| 28       | _              | 32                                 | P2.2/SCLK           | P2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SPI: Slave Clock             |  |  |

| 30       | _              | 33                                 | P2.3/SSEL           | P2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SPI: Active-Low Slave Select |  |  |

| 31       | 24             | 34                                 | P2.4/TCK            | P2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                  | JTAG: Test Clock             |  |  |

| 32       | 25             | 35                                 | P2.5/TDI            | P2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                  | JTAG: Test Data In           |  |  |

| 33       | 26             | 38                                 | P2.6/TMS            | P2.6                                                                                                                                                                                                                                                                                                                                                                                                                                                  | JTAG: Test Mode Select       |  |  |

| 34       | 27             | 39                                 | P2.7/TDO            | P2.7                                                                                                                                                                                                                                                                                                                                                                                                                                                  | JTAG: Test Data Out          |  |  |

|          |                |                                    |                     | CONNECTION PINS                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |  |  |

| _        | 23             | 2, 4, 15, 16,<br>30, 31, 36,<br>37 | N.C.                | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                              |                              |  |  |

| _        | _              | _                                  | EP                  | Exposed Pad. Connect EP directly t                                                                                                                                                                                                                                                                                                                                                                                                                    | o the ground plane.          |  |  |

|          | •              |                                    |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |  |  |

## 16-Bit Microcontroller with Infrared Module

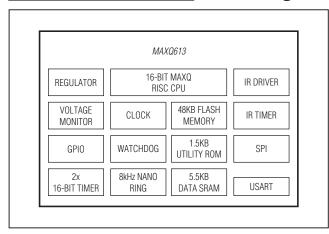

#### **Block Diagram**

#### **Detailed Description**

The MAXQ613 provides integrated, low-cost solutions that simplify the design of IR communications equipment such as universal remote controls. Standard features include the highly optimized, single-cycle, MAXQ, 16-bit RISC core; 48KB of program flash memory; 1.5KB data RAM; soft stack; 16 general-purpose registers; and three data pointers. The MAXQ core has the industry's best MIPS/mA rating, allowing developers to achieve the same performance as competing microcontrollers at substantially lower clock rates. Lower active-mode current combined with the even lower MAXQ613 stopmode current (0.2µA typ) results in increased battery life. Application-specific peripherals include flexible timers for generating IR carrier frequencies and modulation. A high-current IR drive pin capable of sinking up to 25mA current and output pins capable of sinking up to 5mA are ideal for IR applications. It also includes generalpurpose I/O pins ideal for keypad matrix input, and a power-fail-detection circuit to notify the application when the supply voltage is nearing the microcontroller's minimum operating voltage.

At the heart of the device is the MAXQ 16-bit, RISC core. Operating from DC to 12MHz, almost all instructions execute in a single clock cycle (83.3ns at 12MHz), enabling nearly 12MIPS true-code operation. When active device operation is not required, an ultra-low-power stop mode

can be invoked from software, resulting in quiescent current consumption of less than 0.2µA (typ) and 2.0µA (max). The combination of high-performance instructions and ultra-low stop-mode current increases battery life over competing microcontrollers. An integrated POR circuit with brownout support resets the device to a known condition following a power-up cycle or brownout condition. Additionally, a power-fail warning flag is set, and a power-fail interrupt can be generated when the system voltage falls below the power-fail warning voltage, VPFW. The power-fail warning feature allows the application to notify the user that the system supply is low and appropriate action should be taken.

#### **Microprocessor**

The device is based on Maxim's low-power, 16-bit MAXQ20S family of RISC cores. The core supports the Harvard memory architecture with separate 16-bit program and data address buses. A fixed 16-bit instruction word is standard, but data can be arranged in 8 or 16 bits. The MAXQ core in the device is implemented as a pipelined processor with performance approaching 1MIPS per MHz. The 16-bit data path is implemented around register modules, and each register module contributes specific functions to the core. The accumulator module consists of sixteen 16-bit registers and is tightly coupled with the arithmetic logic unit (ALU). A configurable soft stack supports program flow.

Execution of instructions is triggered by data transfer between functional register modules or between a functional register module and memory. Because data movement involves only source and destination modules, circuit switching activities are limited to active modules only. For power-conscious applications, this approach localizes power dissipation and minimizes switching noise. The modular architecture also provides a maximum of flexibility and reusability that are important for a microprocessor used in embedded applications.

The MAXQ instruction set is highly orthogonal. All arithmetical and logical operations can use any register in conjunction with the accumulator. Data movement is supported from any register to any other register. Memory is accessed through specific data-pointer registers with autoincrement/decrement support.

## 16-Bit Microcontroller with Infrared Module

#### Memory

The microcontroller incorporates several memory types:

- 48KB program flash memory

- 1.5KB SRAM data memory

- 5.5KB utility ROM

- Soft stack

#### **Memory Protection**

The optional memory-protection feature separates code memory into three areas: system, user loader, and user application. Code in the system area can be kept confidential. Code in the user areas can be prevented from reading and writing system code. The user loader can also be protected from user application code.

Memory protection is implemented using privilege levels for code. Each area has an associated privilege level. RAM/ROM are assigned privilege levels as well. Refer to the *MAXQ610 User's Guide* for a more thorough explanation of the topic. See Table 1.

#### Stack Memory

The device provides a soft stack that can be used to store program return addresses (for subroutine calls and interrupt handling) and other general-purpose data. This soft stack is located in the 1.5KB SRAM data memory, which means that the SRAM data memory must be shared between the soft stack and general-purpose application data storage. However, the location and size of the soft stack is determined by the user, providing maximum flexibility when allocating resources for a particular application. The stack is used automatically by the processor when the CALL, RET, and RETI instructions are executed and when an interrupt is serviced. An application can also store and retrieve values explicitly using the stack by means of the PUSH, POP, and POPI instructions.

The SP pointer indicates the current top of the stack, which initializes by default to the top of the SRAM data memory. As values are pushed onto the stack, the SP pointer decrements, which means that the stack grows downward towards the bottom (lowest address) of the data memory. Popping values off the stack causes the SP pointer value to increase. Refer to the *MAXQ610 User's Guide* for more details.

#### **Utility ROM**

The utility ROM is a 5.5KB block of internal ROM memory located in program space beginning at address 8000h. This ROM includes the following routines:

- In-system programming (bootstrap loader) using JTAG interface

- In-circuit debugging routines using JTAG interface

- Production test routines (internal memory tests, memory loader, etc.), which are used for internal testing only, and are generally of no use to the endapplication developer

- User-callable routines for in-application flash programming, buffer copying, and fast table lookup (more information on these routines can be found in the MAXQ610 User's Guide)

Following any reset, execution begins in the utility ROM at address 8000h. At this point, unless loader mode or test mode has been invoked (which requires special programming through the JTAG interface), the utility ROM in the device always automatically jumps to location 0000h, which is the beginning of user application code in program flash memory.

Some applications require protection against unauthorized viewing of program code memory. For these applications, access to in-system programming, in-application programming, or in-circuit debugging functions is prohibited until a password has been supplied. Three

Table 1. Memory Areas and Associated Maximum Privilege Levels

| AREA             | PAGE ADDRESS   | MAXIMUM PRIVILEGE LEVEL |

|------------------|----------------|-------------------------|

| System           | 0 to ULDR-1    | High                    |

| User Loader      | ULDR to UAPP-1 | Medium                  |

| User Application | UAPP to top    | Low                     |

| Utility ROM      | N/A            | High                    |

| Other (RAM)      | N/A            | Low                     |

## 16-Bit Microcontroller with Infrared Module

Table 2. Watchdog Interrupt Timeout (Sysclk = 12MHz, CD[1:0] = 00)

| WD[1:0] | WATCHDOG CLOCK         | WATCHDOG INTERRUPT TIMEOUT | WATCHDOG RESET AFTER<br>WATCHDOG INTERRUPT (μs) |

|---------|------------------------|----------------------------|-------------------------------------------------|

| 00      | Sysclk/2 <sup>15</sup> | 2.7ms                      | 42.7                                            |

| 01      | Sysclk/2 <sup>18</sup> | 21.9ms                     | 42.7                                            |

| 10      | Sysclk/221             | 174.7ms                    | 42.7                                            |

| 11      | Sysclk/2 <sup>24</sup> | 1.4s                       | 42.7                                            |

different password locks are provided, each of which can be used to protect a different area of memory (system memory, user loader, and user application). Each password lock is controlled by a 16-word area of flash memory; if the password is set to all FFFFh values or all 0000h values, the password is disabled. Otherwise, the password is active and must be matched by the user of the bootloader or debugger before access is granted to the corresponding area of flash program memory. Refer to the *MAXQ610 User's Guide* for more details.

#### **Watchdog Timer**

The internal watchdog timer greatly increases system reliability. The timer resets the device if software execution is disturbed. The watchdog timer is a free-running counter designed to be periodically reset by the application software. If software is operating correctly, the counter is periodically reset and never reaches its maximum count. However, if software operation is interrupted, the timer does not reset, triggering a system reset and optionally a watchdog timer interrupt. This protects the system against electrical noise or electrostatic discharge (ESD) upsets that could cause uncontrolled processor operation. The internal watchdog timer is an upgrade to older designs with external watchdog devices, reducing system cost and simultaneously increasing reliability.

The watchdog timer functions as the source of both the watchdog timer timeout and the watchdog timer reset. The timeout period can be programmed in a range of  $2^{15}$  to  $2^{24}$  system clock cycles. An interrupt is generated when the timeout period expires if the interrupt is enabled. All watchdog timer resets follow the programmed interrupt timeouts by 512 system clock cycles. If the watchdog timer is not restarted for another full interval in this time period, a system reset occurs when the reset timeout expires. See Table 2.

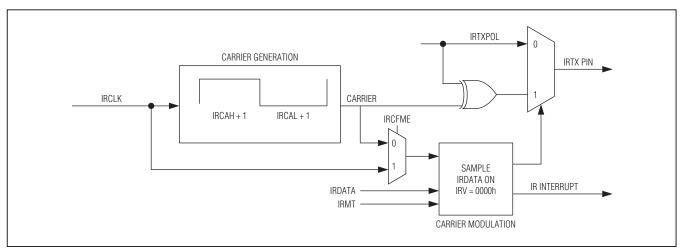

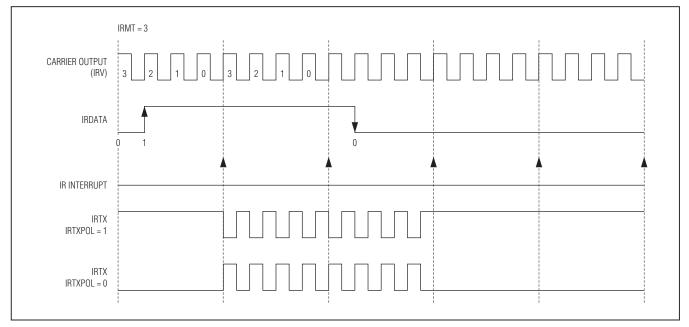

#### \_IR Carrier Generation and Modulation Timer

The dedicated IR timer/counter module simplifies low-speed infrared (IR) communication. The IR timer implements two pins (IRTX and IRRX) for supporting IR transmit and receive, respectively. The IRTX pin has no corresponding port pin designation, so the standard PD, PO, and PI port control status bits are not present. However, the IRTX pin output can be manipulated high or low using the PWCN.IRTXOUT and PWCN.IRTXOE bits when the IR timer is not enabled (i.e., IREN = 0).

The IR timer is composed of a carrier generator and a carrier modulator. The carrier generation module uses the 16-bit IR carrier register (IRCA) to define the high and low time of the carrier through the IR carrier high byte (IRCAH) and IR carrier low byte (IRCAL). The carrier modulator uses the IR data bit (IRDATA) and IR modulator time register (IRMT) to determine whether the carrier or the idle condition is present on IRTX.

The IR timer is enabled when the IR enable bit (IREN) is set to 1. The IR Value register (IRV) defines the beginning value for the carrier modulator. During transmission, the IRV register is initially loaded with the IRMT value and begins down counting towards 0000h, whereas in receive mode it counts upward from the initial IRV register value. During the receive operation, the IRV register can be configured to reload with 0000h when capture occurs on detection of selected edges or can be allowed to continue free-running throughout the receive operation. An overflow occurs when the IR timer value rolls over from 0FFFFh to 0000h. The IR overflow flag (IROV) is set to 1 and an interrupt is generated if enabled (IRIE = 1).

## 16-Bit Microcontroller with Infrared Module

IRTX pin is set to a logic-high when the IR timer module is enabled. If IRTXPOL = 0, the IRTX pin is set to a logic-low when the IR timer is enabled.

A separate register bit, IR data (IRDATA), is used to determine whether the carrier generator output is output to the IRTX pin for the next IRMT carrier cycles. When IRDATA = 1, the carrier waveform (or inversion of this waveform if IRTXPOL = 1) is output on the IRTX pin during the next IRMT cycles. When IRDATA = 0, the idle

condition, as defined by IRTXPOL, is output on the IRTX pin during the next IRMT cycles.

The IR timer acts as a down counter in transmit mode. An IR transmission starts when the IREN bit is set to 1 when IRMODE = 1; when the IRMODE bit is set to 1 when IREN = 1; or when IREN and IRMODE are both set to 1 in the same instruction. The IRMT and IRCA registers, along with the IRDATA and IRTXPOL bits, are sampled at the beginning of the transmit process and every time the IR

Figure 2. IR Transmit Carrier Generation and Carrier Modulator Control

Figure 3. IR Transmission Waveform (IRCFME = 0)

## 16-Bit Microcontroller with Infrared Module

timer value reloads its value. When the IRV reaches 0000h value, on the next carrier clock, it does the following:

- 1) Reloads IRV with IRMT.

- 2) Samples IRCA, IRDATA, and IRTXPOL.

- 3) Generates IRTX accordingly.

- 4) Sets IRIF to 1.

- 5) Generates an interrupt to the CPU if enabled (IRIE = 1).

To terminate the current transmission, the user can switch to receive mode (IRMODE = 0) or clear IREN to 0.

Carrier Modulation Time = IRMT + 1 carrier cycles

# IR Transmit—Independent External Carrier and Modulator Outputs

The normal transmit mode modulates the carrier based upon the IRDATA bit. However, the user has the option to input the modulator (envelope) on an external pin if desired. If the IRENV[1:0] bits are configured to 01b or 10b, the modulator/envelope is output to the IRTXM pin. The IRDATA bit is output directly to the IRTXM pin (if IRTXPOL = 0) on each IRV down-count interval boundary just as if it were being used to internally modulate the carrier frequency. If IRTXPOL = 1, the inverse of the IRDATA bit is output to the IRTXM pin on the IRV interval down-count boundaries. See Figure 4. When the envelope mode is enabled, it is possible to output either the modulated (IRENV[1:0] = 01b) or unmodulated (INENV[1:0] = 10b) carrier to the IRTX pin.

#### **IR Receive**

When configured in receive mode (IRMODE = 0), the IR hardware supports the IRRX capture function. The IRRXSEL[1:0] bits define which edge(s) of the IRRX pin should trigger the IR timer capture function.

The IR module starts operating in the receive mode when IRMODE = 0 and IREN = 1. Once started, the IR timer (IRV) starts up counting from 0000h when a qualified capture event as defined by IRRXSEL happens. The IRV register is, by default, counting carrier cycles as defined by the IRCA register. However, the IR carrier frequency detect (IRCFME) bit can be set to 1 to allow clocking of the IRV register directly with the IRCLK for finer resolution. When IRCFME = 0, the IRCA defined carrier is counted by IRV. When IRCFME = 1, the IRCLK clocks the IRV register.

On the next qualified event, the IR module does the following:

- 1) Captures the IRRX pin state and transfers its value to IRDATA. If a falling edge occurs, IRDATA = 0. If a rising edge occurs, IRDATA = 1.

- 2) Transfers its current IRV value to the IRMT.

- 3) Resets IRV content to 0000h (if IRXRL = 1).

- 4) Continues counting again until the next qualified event.

If the IR timer value rolls over from OFFFFh to 0000h before a qualified event happens, the IR timer overflow (IROV) flag is set to 1 and an interrupt is generated, if

Figure 4. External IRTXM (Modulator) Output

## 16-Bit Microcontroller with Infrared Module

Figure 6. Receive Burst-Count Example

#### Table 3. USART Mode Details

| MODE   | TYPE         | START BITS | DATA BITS | STOP BITS |

|--------|--------------|------------|-----------|-----------|

| Mode 0 | Synchronous  | N/A        | 8         | N/A       |

| Mode 1 | Asynchronous | 1          | 8         | 1         |

| Mode 2 | Asynchronous | 1          | 8 + 1     | 1         |

| Mode 3 | Asynchronous | 1          | 8 + 1     | 1         |

### \_Serial Peripheral Interface (SPI)

The integrated SPI provides an independent serial communication channel that communicates synchronously with peripheral devices in a multiple master or multiple slave system. The interface allows access to a 4-wire, full-duplex serial bus, and can be operated in either master mode or slave mode. Collision detection

is provided when two or more masters attempt a data transfer at the same time.

The maximum SPI master transfer rate is Sysclk/2. When operating as an SPI slave, the device can support up to Sysclk/4 SPI transfer rate. Data is transferred as an 8-bit or 16-bit value, MSB first. In addition, the SPI module supports configuration of an active SSEL state (active low or active high) through the slave active select.

# 16-Bit Microcontroller with Infrared Module

Figure 7. SPI Master Communication Timing

Figure 8. SPI Slave Communication Timing

## 16-Bit Microcontroller with Infrared Module

#### **Power-Fail Detection**

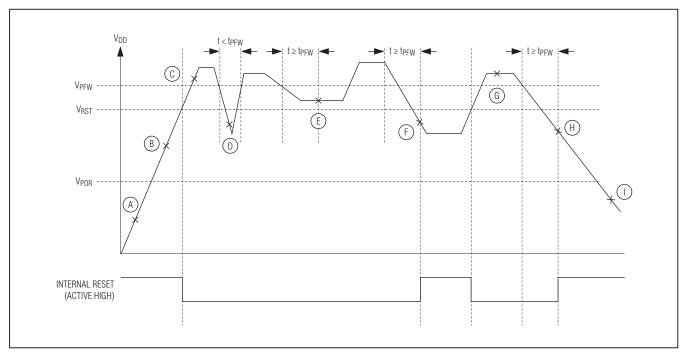

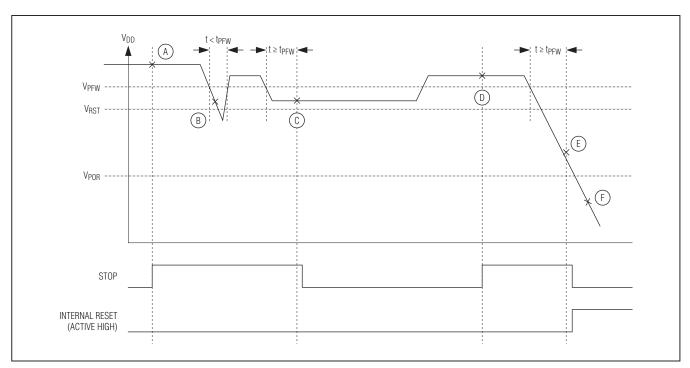

Figures 11, 12, and 13 show the power-fail detection and response during normal and stop-mode operation. If a reset is caused by a power-fail, the power-fail monitor can be set to one of the following intervals:

- Always on—continuous monitoring

- 2<sup>11</sup> nanopower ring oscillator clocks (~256ms)

- 2<sup>12</sup> nanopower ring oscillator clocks (~512ms)

- 2<sup>13</sup> nanopower ring oscillator clocks (~1.024s)

In the case where the power-fail circuitry is periodically turned on, the power-fail detection is turned on for two

nanopower ring-oscillator cycles. If  $V_{DD} > V_{RST}$  during detection,  $V_{DD}$  is monitored for an additional nanopower ring-oscillator period. If  $V_{DD}$  remains above  $V_{RST}$  for the third nanopower ring period, the CPU exits the reset state and resumes normal operation from utility ROM at 8000h after satisfying the crystal warmup period.

If a reset is generated by any other event, such as the  $\overline{\text{RESET}}$  pin being driven low externally or the watchdog timer, the power-fail, internal regulator, and crystal remain on during the CPU reset. In these cases, the CPU exits the reset state in less than 20 crystal cycles after the reset source is removed.

Figure 11. Power-Fail Detection During Normal Operation

# 16-Bit Microcontroller with Infrared Module

**Table 4. Power-Fail Detection States During Normal Operation**

| STATE | POWER-FAIL           | INTERNAL<br>REGULATOR | CRYSTAL<br>OSCILLATOR | SRAM<br>RETENTION | COMMENTS                                                                                                                                                                                         |

|-------|----------------------|-----------------------|-----------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А     | On                   | Off                   | Off                   | _                 | V <sub>DD</sub> < V <sub>POR</sub> .                                                                                                                                                             |

| В     | On                   | On                    | On                    | _                 | VPOR < VDD < VRST. Crystal warmup time, txTAL_RDY. CPU held in reset.                                                                                                                            |

| С     | On                   | On                    | On                    | _                 | VDD > VRST. CPU normal operation.                                                                                                                                                                |

| D     | On                   | On                    | On                    | _                 | Power drop too short. Power-fail not detected.                                                                                                                                                   |

| E     | On                   | On                    | On                    | _                 | VRST < VDD < VPFW. PFI is set when VRST < VDD < VPFW and maintains this state for at least tPFW, at which time a power-fail interrupt is generated (if enabled). CPU continues normal operation. |

| F     | On<br>(Periodically) | Off                   | Off                   | Yes               | VPOR < VDD < VRST. Power-fail detected. CPU goes into reset. Power-fail monitor turns on periodically.                                                                                           |

| G     | On                   | On                    | On                    | _                 | V <sub>DD</sub> > V <sub>RST</sub> . Crystal warmup time, t <sub>XTAL_RDY</sub> . CPU resumes normal operation from 8000h.                                                                       |

| Н     | On<br>(Periodically) | Off                   | Off                   | Yes               | VPOR < VDD < VRST. Power-fail detected. CPU goes into reset. Power-fail monitor turns on periodically.                                                                                           |

| I     | Off                  | Off                   | Off                   | _                 | VDD < VPOR. Device held in reset. No operation allowed.                                                                                                                                          |

# 16-Bit Microcontroller with Infrared Module

Figure 12. Stop Mode Power-Fail Detection States with Power-Fail Monitor Enabled

### Table 5. Stop Mode Power-Fail Detection States with Power-Fail Monitor Enabled

| STATE | POWER-FAIL           | INTERNAL<br>REGULATOR | CRYSTAL<br>OSCILLATOR | SRAM<br>RETENTION | COMMENTS                                                                                                                       |

|-------|----------------------|-----------------------|-----------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------|

| А     | On                   | Off                   | Off                   | Yes               | Application enters stop mode.  VDD > VRST.  CPU in stop mode.                                                                  |

| В     | On                   | Off                   | Off                   | Yes               | Power drop too short. Power-fail not detected.                                                                                 |

| С     | On                   | On                    | On                    | Yes               | VRST < VDD < VPFW. Power-fail warning detected. Turn on regulator and crystal. Crystal warmup time, txTAL_RDY. Exit stop mode. |

| D     | On                   | Off                   | Off                   | Yes               | Application enters stop mode.  VDD > VRST.  CPU in stop mode.                                                                  |

| E     | On<br>(Periodically) | Off                   | Off                   | Yes               | VPOR < VDD < VRST. Power-fail detected. CPU goes into reset. Power-fail monitor turns on periodically.                         |

| F     | Off                  | Off                   | Off                   | _                 | V <sub>DD</sub> < V <sub>POR</sub> .  Device held in reset. No operation allowed.                                              |

## 16-Bit Microcontroller with Infrared Module

Table 6. Stop Mode Power-Fail Detection States with Power-Fail Monitor Disabled (continued)

| STATE | POWER-FAIL           | INTERNAL<br>REGULATOR | CRYSTAL<br>OSCILLATOR | SRAM<br>RETENTION | COMMENTS                                                                                                                                                                                                  |

|-------|----------------------|-----------------------|-----------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|