### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI, UART/USART                   |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                  |

| Number of I/O              | 121                                                                      |

| Program Memory Size        | 768KB (768K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | ·                                                                        |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 53x10/12b                                                            |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560b54l5c6e0x |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

# 1.1 Document overview

This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the device.

# 1.2 Description

This family of 32-bit system-on-chip (SoC) microcontrollers is the latest achievement in integrated automotive application controllers. It belongs to an expanding family of automotive-focused products designed to address the next wave of body electronics applications within the vehicle.

The advanced and cost-efficient e200z0h host processor core of this automotive controller family complies with the Power Architecture technology and only implements the VLE (variable-length encoding) APU (Auxiliary Processor Unit), providing improved code density. It operates at speeds of up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

| Feature                                            | SPC5             | 60B54            | S                | PC560B           | 60               |                  | SPO              | C560B64          |                  |  |

|----------------------------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|--|

| CPU                                                |                  |                  |                  |                  | e200z0           | )h               |                  |                  |                  |  |

| Execution speed <sup>(2)</sup>                     |                  |                  |                  |                  | Up to 64         | MHz              |                  |                  |                  |  |

| Code flash memory                                  | 768              | KB               |                  | 1 MB             |                  |                  | 1                | .5 MB            |                  |  |

| Data flash memory                                  | 64 (4 × 16) KB   |                  |                  |                  |                  |                  |                  |                  |                  |  |

| SRAM                                               | 64               | KB               |                  | 80 KB            |                  |                  | ç                | 96 KB            |                  |  |

| MPU 8-entry                                        |                  |                  |                  |                  |                  |                  |                  |                  |                  |  |

| eDMA                                               |                  |                  |                  |                  | 16 ch            |                  |                  |                  |                  |  |

| 10-bit ADC                                         |                  |                  |                  |                  | Yes              |                  |                  |                  |                  |  |

| dedicated <sup>(3)</sup>                           | 7 ch             | 15 ch            | 7 ch             | 15 ch            | 29 ch            | 7 ch             | 15 ch            | 29 ch            | 29 ch            |  |

| shared with 12-bit ADC                             |                  |                  |                  |                  | 19 ch            |                  |                  |                  |                  |  |

| 12-bit ADC                                         |                  |                  |                  |                  | Yes              |                  |                  |                  |                  |  |

| dedicated <sup>(4)</sup>                           |                  |                  |                  |                  | 5 ch             |                  |                  |                  |                  |  |

| shared with 10-bit ADC                             |                  |                  |                  |                  | 19 ch            |                  |                  |                  |                  |  |

| Total timer I/O <sup>(5)</sup> eMIOS               | 37 ch,<br>16-bit | 64 ch,<br>16-bit | 37 ch,<br>16-bit | 64 ch,<br>16-bit | 64 ch,<br>16-bit | 37 ch,<br>16-bit | 64 ch,1<br>6-bit | 64 ch,<br>16-bit | 64 ch,<br>16-bit |  |

| Counter / OPWM / ICOC <sup>(6)</sup>               |                  |                  |                  |                  | 10 ch            |                  |                  |                  |                  |  |

| O(I)PWM / OPWFMB /<br>OPWMCB / ICOC <sup>(7)</sup> |                  |                  |                  |                  | 7 ch             | 7 ch             |                  |                  |                  |  |

| O(I)PWM / ICOC <sup>(8)</sup>                      | 7 ch             | 14 ch            | 7 ch             | 14 ch            | 14 ch            | 7 ch             | 14 ch            | 14 ch            | 14 ch            |  |

Table 2. SPC560B54/6x family comparison<sup>(1)</sup>

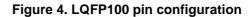

*Figure 5* shows the SPC560B54/6x in the LBGA208 package.

|             | Table 4. Voltage Supply                                                     | pin accompa |         |         |         |  |  |  |  |

|-------------|-----------------------------------------------------------------------------|-------------|---------|---------|---------|--|--|--|--|

| Dert nin    | Function                                                                    | Pin number  |         |         |         |  |  |  |  |

| Port pin    | Function                                                                    | LQFP100     | LQFP144 | LQFP176 | LBGA208 |  |  |  |  |

| VDD_BV      | Internal regulator supply voltage                                           | 20          | 24      | 32      | K3      |  |  |  |  |

| VSS_HV_ADC0 | Reference ground and analog<br>ground for the A/D converter 0 (10-<br>bit)  | 51          | 73      | 89      | R15     |  |  |  |  |

| VDD_HV_ADC0 | Reference voltage and analog<br>supply for the A/D converter 0 (10-<br>bit) | 52          | 74      | 90      | P14     |  |  |  |  |

| VSS_HV_ADC1 | Reference ground and analog<br>ground for the A/D converter 1 (12-<br>bit)  | 59          | 81      | 98      | N12     |  |  |  |  |

| VDD_HV_ADC1 | Reference voltage and analog<br>supply for the A/D converter 1 (12-<br>bit) | 60          | 82      | 99      | K13     |  |  |  |  |

Table 4. Voltage supply pin descriptions (continued)

1. A decoupling capacitor must be placed between each of the three VDD\_LV/VSS\_LV supply pairs to ensure stable voltage (see the recommended operating conditions in the device datasheet).

# 3.5 Pad types

In the device the following types of pads are available for system pins and functional port pins:

S = Slow<sup>(d)</sup>

$M = Medium^{(d)}$  (e)

F = Fast<sup>(d)</sup> (e)

I = Input only with analog feature<sup>(d)</sup>

J = Input/Output ('S' pad) with analog feature

X = Oscillator

# 3.6 System pins

The system pins are listed in Table 5.

d. See the I/O pad electrical characteristics in the chip datasheet for details.

e. All medium and fast pads are in slow configuration by default at reset and can be configured as fast or medium. The only exception is PC[1] which is in medium configuration by default (see the PCR.SRC description in the chip reference manual, Pad Configuration Registers (PCR0–PCR148)).

|          |         | 0 <sup>(1)</sup>                        |                                                                              |                                                                 | (1)                            |          | 3)                                    |             | Pin number  |             |                            |  |  | Pin number |  |  |  |  |

|----------|---------|-----------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------|----------|---------------------------------------|-------------|-------------|-------------|----------------------------|--|--|------------|--|--|--|--|

| Port pin | PCR     | Alternate function <sup>(1)</sup>       | Function                                                                     | Peripheral                                                      | I/O direction <sup>(2)</sup>   | Pad type | RESET<br>configuration <sup>(3)</sup> | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 | LBGA<br>208 <sup>(4)</sup> |  |  |            |  |  |  |  |

| PB[1]    | PCR[17] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>— | GPIO[17]<br>—<br>E0UC[31]<br>—<br>WKPU[4] <sup>(5)</sup><br>CAN0RX<br>LIN0RX | SIUL<br>—<br>eMIOS_0<br>—<br>WKPU<br>FlexCAN_0<br>LINFlex_0     | /O<br>                         | S        | Tristate                              | 24          | 32          | 40          | N1                         |  |  |            |  |  |  |  |

| PB[2]    | PCR[18] | AF0<br>AF1<br>AF2<br>AF3                | GPIO[18]<br>LINOTX<br>SDA<br>E0UC[30]                                        | SIUL<br>LINFlex_0<br>I <sup>2</sup> C_0<br>eMIOS_0              | I/O<br>O<br>I/O<br>I/O         | М        | Tristate                              | 100         | 144         | 176         | B2                         |  |  |            |  |  |  |  |

| PB[3]    | PCR[19] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—      | GPIO[19]<br>E0UC[31]<br>SCL<br>—<br>WKPU[11] <sup>(5)</sup><br>LIN0RX        | SIUL<br>eMIOS_0<br>I <sup>2</sup> C_0<br>—<br>WKPU<br>LINFlex_0 | /O<br> /O<br> /O<br> <br> <br> | S        | Tristate                              | 1           | 1           | 1           | C3                         |  |  |            |  |  |  |  |

| PB[4]    | PCR[20] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>— | <br><br><br>ADC0_P[0]<br>ADC1_P[0]<br>GPIO[20]                               |                                                                 |                                | I        | Tristate                              | 50          | 72          | 88          | T16                        |  |  |            |  |  |  |  |

SPC560B54x/6x

| 34/133           | Table 6. Functional port pin descriptions (continued) |         |                                   |                          |                |                              |          |                                       |             |             |             |                            |  |

|------------------|-------------------------------------------------------|---------|-----------------------------------|--------------------------|----------------|------------------------------|----------|---------------------------------------|-------------|-------------|-------------|----------------------------|--|

| 133              |                                                       |         | 0n <sup>(1)</sup>                 |                          |                | 5)                           |          | (2)                                   |             | Pin ni      | umber       |                            |  |

|                  | Port pin                                              | PCR     | Alternate function <sup>(1)</sup> | Function                 | Peripheral     | I/O direction <sup>(2)</sup> | Pad type | RESET<br>configuration <sup>(3)</sup> | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 | LBGA<br>208 <sup>(4)</sup> |  |

|                  |                                                       |         | AF0                               | GPIO[56]                 | SIUL           | I                            |          |                                       |             |             |             |                            |  |

|                  |                                                       |         | AF1                               | —                        | —              | —                            |          |                                       |             |             |             |                            |  |

|                  | PD[8]                                                 | PCR[56] | AF2                               | _                        | —              | —                            | Ι        | Tristate                              | 49          | 71          | 87          | T15                        |  |

|                  |                                                       |         | AF3                               |                          | ADC_0          |                              |          |                                       |             |             |             |                            |  |

|                  |                                                       |         | _                                 | ADC0_P[12]<br>ADC1_P[12] | ADC_0<br>ADC_1 |                              |          |                                       |             |             |             |                            |  |

| _                |                                                       |         | AF0                               | GPIO[57]                 | SIUL           |                              |          |                                       |             |             |             |                            |  |

| U cc             |                                                       |         | AF1                               | —                        |                | · _                          |          |                                       |             |             |             |                            |  |

| D1:              | <b>DD</b> (a)                                         | DODICZI | AF2                               | _                        | _              | _                            |          | Tristate                              | 50          |             |             |                            |  |

| 513              | PD[9]                                                 | PCR[57] | AF3                               | _                        | —              | —                            | I        | Iristate                              | 56          | 78          | 94          | N15                        |  |

| 1<br>R           |                                                       |         | —                                 | ADC0_P[13]               | ADC_0          | I                            |          |                                       |             |             |             |                            |  |

| DocID15131 Rev 9 |                                                       |         | —                                 | ADC1_P[13]               | ADC_1          | I                            |          |                                       |             |             |             |                            |  |

|                  |                                                       |         | AF0                               | GPIO[58]                 | SIUL           | I                            |          |                                       |             |             |             |                            |  |

|                  |                                                       |         | AF1                               | —                        | —              | —                            |          |                                       |             |             |             |                            |  |

|                  | PD[10]                                                | PCR[58] | AF2                               | —                        | —              | —                            | Ι        | Tristate                              | 57          | 79          | 95          | N14                        |  |

|                  |                                                       |         | AF3                               | —<br>ADC0_P[14]          | ADC_0          | —<br>                        |          |                                       |             |             |             |                            |  |

|                  |                                                       |         | _                                 | ADC0_P[14]<br>ADC1_P[14] | ADC_0<br>ADC_1 |                              |          |                                       |             |             |             |                            |  |

|                  |                                                       |         | AF0                               | GPIO[59]                 | SIUL           | 1                            |          |                                       |             |             |             |                            |  |

|                  |                                                       |         | AF1                               | <u> </u>                 |                | · _                          |          |                                       |             |             |             |                            |  |

|                  |                                                       |         | AF2                               | _                        | _              | _                            | ,        | Triototo                              | 50          | 00          | 00          | NAC                        |  |

|                  | PD[11]                                                | PCR[59] | AF3                               | —                        | —              | —                            | I        | Tristate                              | 58          | 80          | 96          | N16                        |  |

|                  |                                                       |         | —                                 | ADC0_P[15]               | ADC_0          | I                            |          |                                       |             |             |             |                            |  |

|                  |                                                       |         | —                                 | ADC1_P[15]               | ADC_1          | I                            |          |                                       |             |             |             |                            |  |

# Package pinouts and signal descriptions

SPC560B54x/6x

5

|                  |          |         |                                   | Table 6. Fund                                   | tional port pin                         | descr                        | iptions  | s (continue                           | ∋d)         |             |             |                            |

|------------------|----------|---------|-----------------------------------|-------------------------------------------------|-----------------------------------------|------------------------------|----------|---------------------------------------|-------------|-------------|-------------|----------------------------|

|                  |          |         | 00 <sup>(1)</sup>                 |                                                 |                                         | 2)                           |          | (8)                                   |             | Pin n       | umber       |                            |

|                  | Port pin | PCR     | Alternate function <sup>(1)</sup> | Function                                        | Peripheral                              | I/O direction <sup>(2)</sup> | Pad type | RESET<br>configuration <sup>(3)</sup> | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 | LBGA<br>208 <sup>(4)</sup> |

|                  | PD[12]   | PCR[60] | AF0<br>AF1<br>AF2<br>AF3<br>—     | GPIO[60]<br>CS5_0<br>E0UC[24]<br>—<br>ADC0_S[4] | SIUL<br>DSPI_0<br>eMIOS_0<br>—<br>ADC_0 | I/O<br>O<br>I/O<br>I         | J        | Tristate                              | _           | _           | 100         | M15                        |

| DocID15131 Rev 9 | PD[13]   | PCR[61] | AF0<br>AF1<br>AF2<br>AF3<br>—     | GPIO[61]<br>CS0_1<br>E0UC[25]<br><br>ADC0_S[5]  | SIUL<br>DSPI_1<br>eMIOS_0<br>—<br>ADC_0 | I/O<br>I/O<br>I/O<br>I       | J        | Tristate                              | 62          | 84          | 102         | M14                        |

| l Rev 9          | PD[14]   | PCR[62] | AF0<br>AF1<br>AF2<br>AF3<br>—     | GPIO[62]<br>CS1_1<br>E0UC[26]<br>—<br>ADC0_S[6] | SIUL<br>DSPI_1<br>eMIOS_0<br>—<br>ADC_0 | I/O<br>O<br>I/O<br>_<br>I    | J        | Tristate                              | 64          | 86          | 104         | L15                        |

|                  | PD[15]   | PCR[63] | AF0<br>AF1<br>AF2<br>AF3<br>—     | GPIO[63]<br>CS2_1<br>E0UC[27]<br>—<br>ADC0_S[7] | SIUL<br>DSPI_1<br>eMIOS_0<br>—<br>ADC_0 | I/O<br>O<br>I/O<br>_<br>I    | J        | Tristate                              | 66          | 88          | 106         | L14                        |

|                  |          |         |                                   |                                                 | Port                                    | E                            |          |                                       |             |             |             |                            |

35/133

SPC560B54x/6x

Package pinouts and signal descriptions

| 36               |          |         |                                    | Table 6. Fund                                                 | tional port pin                                | descr                        | iption   | s (continue                           | ed)         |             |             |                            |

|------------------|----------|---------|------------------------------------|---------------------------------------------------------------|------------------------------------------------|------------------------------|----------|---------------------------------------|-------------|-------------|-------------|----------------------------|

| 36/133           |          |         | on <sup>(1)</sup>                  |                                                               |                                                | 2)                           |          | (3)                                   |             | Pin ni      | umber       |                            |

|                  | Port pin | PCR     | Alternate function <sup>(1)</sup>  | Function                                                      | Peripheral                                     | I/O direction <sup>(2)</sup> | Pad type | RESET<br>configuration <sup>(3)</sup> | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 | LBGA<br>208 <sup>(4)</sup> |

|                  | PE[0]    | PCR[64] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[64]<br>E0UC[16]<br>—<br>WKPU[6] <sup>(5)</sup><br>CAN5RX | SIUL<br>eMIOS_0<br>—<br>—<br>WKPU<br>FlexCAN_5 | I/O<br>I/O<br>—<br>I<br>I    | S        | Tristate                              | 6           | 10          | 18          | F1                         |

| DocID15131 Rev 9 | PE[1]    | PCR[65] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[65]<br>E0UC[17]<br>CAN5TX<br>—                           | SIUL<br>eMIOS_0<br>FlexCAN_5<br>—              | I/O<br>I/O<br>O<br>—         | М        | Tristate                              | 8           | 12          | 20          | F4                         |

| l Rev 9          | PE[2]    | PCR[66] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[66]<br>E0UC[18]<br>—<br>EIRQ[21]<br>SIN_1                | SIUL<br>eMIOS_0<br>—<br>SIUL<br>DSPI_1         | /O<br> /O<br><br> <br> <br>  | М        | Tristate                              | 89          | 128         | 156         | D7                         |

|                  | PE[3]    | PCR[67] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[67]<br>E0UC[19]<br>SOUT_1<br>—                           | SIUL<br>eMIOS_0<br>DSPI_1<br>—                 | I/O<br>I/O<br>O<br>—         | М        | Tristate                              | 90          | 129         | 157         | C7                         |

| 5                | PE[4]    | PCR[68] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[68]<br>E0UC[20]<br>SCK_1<br>—<br>EIRQ[9]                 | SIUL<br>eMIOS_0<br>DSPI_1<br>—<br>SIUL         | /O<br> /O<br> /O<br>         | Μ        | Tristate                              | 93          | 132         | 160         | D6                         |

Package pinouts and signal descriptions

SPC560B54x/6x

|          |           | on <sup>(1)</sup>                 |            |            | 2)                           |          | (3)                                   |             | Pin nu      | umber       |                         |

|----------|-----------|-----------------------------------|------------|------------|------------------------------|----------|---------------------------------------|-------------|-------------|-------------|-------------------------|

| Port pin | PCR       | Alternate function <sup>(1)</sup> | Function   | Peripheral | I/O direction <sup>(2)</sup> | Pad type | RESET<br>configuration <sup>(3)</sup> | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 | LBG<br>208 <sup>(</sup> |

|          |           | AF0                               | GPIO[146]  | SIUL       | I/O                          |          |                                       |             |             |             |                         |

|          |           | AF1                               | CS0_5      | DSPI_5     | I/O                          |          |                                       |             |             |             |                         |

| PJ[2]    | PCR[146]  | AF2                               | —          | —          | —                            | J        | Tristate                              | —           | —           | 72          | P4                      |

|          |           | AF3                               | —          | —          |                              |          |                                       |             |             |             |                         |

|          |           | —                                 | ADC0_S[26] | ADC_0      | I                            |          |                                       |             |             |             |                         |

|          |           | AF0                               | GPIO[147]  | SIUL       | I/O                          |          |                                       |             |             |             |                         |

|          |           | AF1                               | CS1_5      | DSPI_5     | 0                            |          |                                       |             |             |             |                         |

| PJ[3]    | PCR[147]  | AF2                               | —          | —          | —                            | J        | Tristate                              | —           | —           | 71          | P2                      |

|          |           | AF3                               | —          | —          | —                            |          |                                       |             |             |             |                         |

|          |           | —                                 | ADC0_S[27] | ADC_0      | I                            |          |                                       |             |             |             |                         |

|          |           | AF0                               | GPIO[148]  | SIUL       | I/O                          |          |                                       |             |             |             |                         |

| PJ[4]    | PCR[148]  | AF1                               | SCK_5      | DSPI_5     | I/O                          | М        | Tristate                              |             |             | 5           | A4                      |

| 1.2[4]   | 1.01(140] | AF2                               | E1UC[18]   | eMIOS_1    | I/O                          | IVI      | msiale                                | _           |             | 5           | A4                      |

|          |           | AF3                               | _          | —          | —                            |          |                                       |             |             |             |                         |

Table 6. Functional port pin descriptions (continued)

1. Alternate functions are chosen by setting the values of the PCR.PA bitfields inside the SIUL module. PCR.PA = 00 → AF0; PCR.PA = 01 → AF1; PCR.PA = 10 → AF2; PCR.PA = 11 → AF2. This is intended to select the output functions; to use one of the input functions, the PCR.IBE bit must be written to '1', regardless of the values selected in the PCR.PA bitfields. For this reason, the value corresponding to an input only function is reported as "--".

2. Multiple inputs are routed to all respective modules internally. The input of some modules must be configured by setting the values of the PSMIO.PADSELx bitfields inside the SIUL module.

- 3. The RESET configuration applies during and after reset.

- 4. LBGA208 available only as development package for Nexus2+

- 5. All WKPU pins also support external interrupt capability. See the WKPU chapter for further details.

- 6. NMI has higher priority than alternate function. When NMI is selected, the PCR.AF field is ignored.

- 7. "Not applicable" because these functions are available only while the device is booting. Refer to the BAM information for details.

- 8. Value of PCR.IBE bit must be 0.

- 9. This wakeup input cannot be used to exit STANDBY mode.

- 53/133

DocID15131 Rev 9

# 3.8 Nexus 2+ pins

In the LBGA208 package, eight additional debug pins are available (see Table 7).

|          |                       | I/O       |          | Function    | Pin number  |             |                            |  |  |  |

|----------|-----------------------|-----------|----------|-------------|-------------|-------------|----------------------------|--|--|--|

| Port pin | Function              | direction | Pad type | after reset | LQFP<br>100 | LQFP<br>144 | LBGA<br>208 <sup>(1)</sup> |  |  |  |

| MCKO     | Message clock out     | 0         | F        | —           |             | —           | T4                         |  |  |  |

| MDO0     | Message data out 0    | 0         | М        | —           |             | _           | H15                        |  |  |  |

| MDO1     | Message data out 1    | 0         | М        | —           |             | _           | H16                        |  |  |  |

| MDO2     | Message data out 2    | 0         | М        | —           |             | _           | H14                        |  |  |  |

| MDO3     | Message data out 3    | 0         | М        | —           |             | _           | H13                        |  |  |  |

| EVTI     | Event in              | I         | М        | Pull-up     |             |             | K1                         |  |  |  |

| EVTO     | Event out             | 0         | М        | —           |             | —           | L4                         |  |  |  |

| MSEO     | Message start/end out | 0         | М        | —           |             |             | G16                        |  |  |  |

Table 7. Nexus 2+ pin descriptions

1. LBGA208 available only as development package for Nexus2+.

# 4 Electrical characteristics

This section contains electrical characteristics of the device as well as temperature and power considerations.

This product contains devices to protect the inputs against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This could be done by the internal pull-up and pull-down, which is provided by the product for most general purpose pins.

The parameters listed in the following tables represent the characteristics of the device and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

# 4.1 Parameter classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the classifications listed in *Table 8* are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

## Table 8. Parameter classifications

Note: The classification is shown in the column labeled "C" in the parameter tables where appropriate.

# 4.2 NVUSRO register

Bit values in the Non-Volatile User Options (NVUSRO) Register control portions of the device configuration, namely electrical parameters such as high voltage supply and oscillator margin, as well as digital functionality (watchdog enable/disable after reset).

| Symph             |                                          | с                    | Devemeter                        | Conditions <sup>(2)</sup> | Din count |     | l Init |      |         |

|-------------------|------------------------------------------|----------------------|----------------------------------|---------------------------|-----------|-----|--------|------|---------|

| Symb              | 100                                      | C                    | Parameter                        | Conditions                | Pin count | Min | Тур    | Max  | Unit    |

|                   |                                          |                      |                                  |                           | 100       | —   | —      | 36   |         |

|                   |                                          |                      |                                  | Single-layer board — 1s   | 144       |     | _      | 38   |         |

| Б                 | <u> </u>                                 |                      | Thermal resistance, junction-to- |                           | 176       | —   |        | 38   | °C ///  |

| ĸ <sub>θ</sub> jΒ | R <sub>θJB</sub> CC board <sup>(4)</sup> | board <sup>(4)</sup> |                                  | 100                       | —         | _   | 33.6   | °C/W |         |

|                   |                                          |                      |                                  | Four-layer board — 2s2p   | 144       |     | _      | 33.4 |         |

|                   |                                          |                      |                                  |                           | 176       | —   |        | 33.4 |         |

|                   |                                          |                      |                                  |                           | 100       | —   | _      | 23   |         |

|                   |                                          |                      |                                  | Single-layer board — 1s   | 144       |     | _      | 23   |         |

| Р                 | R <sub>θJC</sub> CC                      |                      | Thermal resistance, junction-to- |                           | 176       |     |        | 23   | °C 1.1/ |

| κ <sub>θ</sub> JC |                                          |                      | case <sup>(5)</sup>              |                           | 100       | —   | —      | 19.8 | °C/W    |

|                   |                                          |                      |                                  | Four-layer board — 2s2p   | 144       | —   | —      | 19.2 |         |

|                   |                                          |                      |                                  |                           | 176       | —   | —      | 18.8 |         |

Table 15. LQFP thermal characteristics<sup>(1)</sup> (continued)

1. Thermal characteristics are targets based on simulation.

2.  $V_{DD} = 3.3 \text{ V} \pm 10\% / 5.0 \text{ V} \pm 10\%$ ,  $T_A = -40$  to 125 °C.

Junction-to-ambient thermal resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package. When Greek letters are not available, the symbols are typed as R<sub>thJA</sub> and R<sub>thJMA</sub>.

Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package. When Greek letters are not available, the symbols are typed as R<sub>thJB</sub>.

Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer. When Greek letters are not available, the symbols are typed as R<sub>thJC</sub>.

# 4.5.3 Power considerations

The average chip-junction temperature,  $T_J$ , in degrees Celsius, may be calculated using *Equation 1*:

# Equation 1 $T_J = T_A + (P_D \times R_{\theta JA})$

Where:

T<sub>A</sub> is the ambient temperature in °C.

$R_{\theta JA}$  is the package junction-to-ambient thermal resistance, in °C/W.

$P_D$  is the sum of  $P_{INT}$  and  $P_{I/O} (P_D = P_{INT} + P_{I/O})$ .

$\mathsf{P}_{\mathsf{INT}}$  is the product of  $\mathsf{I}_{\mathsf{DD}}$  and  $\mathsf{V}_{\mathsf{DD}},$  expressed in watts. This is the chip internal power.

$\mathsf{P}_{\mathsf{I/O}}$  represents the power dissipation on input and output pins; user determined.

Most of the time for the applications,  $P_{I/O} < P_{INT}$  and may be neglected. On the other hand,  $P_{I/O}$  may be significant, if the device is configured to continuously drive external modules and/or memories.

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is given by:

| Symph           | Symbol |   | Deremeter                                                | Conditions <sup>(1)</sup> |                                                                    |   | Value                  |                                               |      |   |   |  |  |                        |                                               |   |       |  |

|-----------------|--------|---|----------------------------------------------------------|---------------------------|--------------------------------------------------------------------|---|------------------------|-----------------------------------------------|------|---|---|--|--|------------------------|-----------------------------------------------|---|-------|--|

| Symbol          |        | С | Parameter                                                |                           |                                                                    |   | Тур                    | Max                                           | Unit |   |   |  |  |                        |                                               |   |       |  |

|                 |        | D | Output transition time output pin <sup>(2)</sup> $C_{I}$ | C <sub>L</sub> = 25 pF    | V <sub>DD</sub> = 5.0 V ± 10%,                                     | _ | —                      | 10                                            |      |   |   |  |  |                        |                                               |   |       |  |

|                 |        | Т |                                                          | C <sub>L</sub> = 50 pF    | PAD3V5V = 0                                                        |   |                        | 20                                            |      |   |   |  |  |                        |                                               |   |       |  |

| +               | сс     | D |                                                          | C <sub>L</sub> = 100 pF   | SIUL.PCRx.SRC = 1                                                  | _ | —                      | 40                                            | – ns |   |   |  |  |                        |                                               |   |       |  |

| t <sub>tr</sub> |        | D |                                                          | C <sub>L</sub> = 25 pF    | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1<br>SIUL.PCRx.SRC = 1 | _ | —                      | 12                                            |      |   |   |  |  |                        |                                               |   |       |  |

|                 |        | Т |                                                          | C <sub>L</sub> = 50 pF    |                                                                    | _ | —                      | 25                                            |      |   |   |  |  |                        |                                               |   |       |  |

|                 |        | D | C                                                        | C <sub>L</sub> = 100 pF   |                                                                    |   | —                      | 40                                            |      |   |   |  |  |                        |                                               |   |       |  |

|                 |        |   |                                                          | C <sub>L</sub> = 25 pF    |                                                                    |   | —                      | 4                                             |      |   |   |  |  |                        |                                               |   |       |  |

|                 |        |   |                                                          |                           |                                                                    |   |                        |                                               |      |   |   |  |  | C <sub>L</sub> = 50 pF | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | _ | — — 6 |  |

| +               | сс     | Р | Output transition time output pin <sup>(2)</sup>         | C <sub>L</sub> = 100 pF   |                                                                    |   | —                      | 12                                            | ns   |   |   |  |  |                        |                                               |   |       |  |

| t <sub>tr</sub> |        |   |                                                          | C <sub>L</sub> = 25 pF    |                                                                    | _ | —                      | 4                                             |      |   |   |  |  |                        |                                               |   |       |  |

|                 |        |   |                                                          |                           |                                                                    |   | C <sub>L</sub> = 50 pF | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | —    | — | 7 |  |  |                        |                                               |   |       |  |

|                 |        |   |                                                          |                           | C <sub>L</sub> = 100 pF                                            |   | —                      | —                                             | 12   |   |   |  |  |                        |                                               |   |       |  |

Table 21. Output pin transition times (continued)

1. V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 to 125 °C, unless otherwise specified.

2.  $C_L$  includes device and package capacitances ( $C_{PKG} < 5 \text{ pF}$ ).

# 4.6.5 I/O pad current specification

The I/O pads are distributed across the I/O supply segment. Each I/O supply segment is associated to a  $V_{DD}/V_{SS}$  supply pair as described in *Table 22*.

Table 23 provides I/O consumption figures.

In order to ensure device reliability, the average current of the I/O on a single segment should remain below the  $I_{\rm AVGSEG}$  maximum value.

| Package        | Supply segment   |                  |                    |                    |                    |                  |   |   |  |  |  |

|----------------|------------------|------------------|--------------------|--------------------|--------------------|------------------|---|---|--|--|--|

|                | 1                | 2                | 3                  | 4                  | 5                  | 6                | 7 | 8 |  |  |  |

| LBGA208<br>(1) |                  | Equivalent       | МСКО               | MDOn<br>/MSEO      |                    |                  |   |   |  |  |  |

| LQFP176        | pin7 –<br>pin27  | pin28 –<br>pin57 | pin59 –<br>pin85   | pin86 –<br>pin123  | pin124 –<br>pin150 | pin151 –<br>pin6 | _ | — |  |  |  |

| LQFP144        | pin20 –<br>pin49 | pin51 –<br>pin99 | pin100 –<br>pin122 | pin 123 –<br>pin19 | —                  | —                | — | — |  |  |  |

| LQFP100        | pin16 –<br>pin35 | pin37 –<br>pin69 | pin70 –<br>pin83   | pin84 –<br>pin15   | _                  | _                |   |   |  |  |  |

### Table 22. I/O supply segments

1. LBGA208 available only as development package for Nexus2+.

### **Electrical characteristics**

| •           |             |             |        | LQFP176                   |         |         |         | LQFP144/100 |         |              |         |  |

|-------------|-------------|-------------|--------|---------------------------|---------|---------|---------|-------------|---------|--------------|---------|--|

| Sup         | ply segr    | nent        | Pad    | Weight 5 V                |         | Weigh   | t 3.3 V | Weight 5 V  |         | Weight 3.3 V |         |  |

| LQFP<br>176 | LQFP<br>144 | LQFP<br>100 |        | SRC <sup>(2)</sup> =<br>0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0     | SRC = 1 | SRC = 0      | SRC = 1 |  |

|             |             |             | PC[0]  | 6%                        | 9%      | 7%      | 8%      | 7%          | 10%     | 8%           | 8%      |  |

|             |             |             | PH[9]  | 7%                        | _       | 8%      |         | 7%          | _       | 9%           | _       |  |

|             |             |             | PE[2]  | 7%                        | 10%     | 8%      | 9%      | 8%          | 11%     | 9%           | 10%     |  |

|             |             | 4           | PE[3]  | 7%                        | 10%     | 9%      | 9%      | 8%          | 12%     | 10%          | 10%     |  |

|             |             | 4           | PC[5]  | 7%                        | 11%     | 9%      | 9%      | 8%          | 12%     | 10%          | 11%     |  |

|             |             |             | PC[4]  | 8%                        | 11%     | 9%      | 10%     | 9%          | 13%     | 10%          | 11%     |  |

|             |             |             | PE[4]  | 8%                        | 11%     | 9%      | 10%     | 9%          | 13%     | 11%          | 12%     |  |

|             | 4           |             | PE[5]  | 8%                        | 11%     | 10%     | 10%     | 9%          | 14%     | 11%          | 12%     |  |

|             |             | _           | PH[4]  | 8%                        | 12%     | 10%     | 10%     | 10%         | 14%     | 12%          | 12%     |  |

|             |             | _           | PH[5]  | 8%                        | _       | 10%     | _       | 10%         | _       | 12%          | _       |  |

|             |             | _           | PH[6]  | 8%                        | 12%     | 10%     | 11%     | 10%         | 15%     | 12%          | 13%     |  |

| 6           |             | _           | PH[7]  | 9%                        | 12%     | 10%     | 11%     | 11%         | 15%     | 13%          | 13%     |  |

|             |             | _           | PH[8]  | 9%                        | 12%     | 10%     | 11%     | 11%         | 16%     | 13%          | 14%     |  |

|             |             |             | PE[6]  | 9%                        | 12%     | 10%     | 11%     | 11%         | 16%     | 13%          | 14%     |  |

|             |             | 4           | PE[7]  | 9%                        | 12%     | 10%     | 11%     | 11%         | 16%     | 14%          | 14%     |  |

|             | _           | _           | PI[3]  | 9%                        | _       | 10%     | _       | _           | _       | _            | _       |  |

|             | _           | _           | PI[2]  | 9%                        | —       | 10%     |         | —           | _       | _            | _       |  |

|             | _           | _           | PI[1]  | 9%                        | _       | 10%     | _       | _           | _       | —            | _       |  |

|             |             | _           | PI[0]  | 9%                        | _       | 10%     | _       | _           |         |              | _       |  |

|             |             |             | PC[12] | 8%                        | 12%     | 10%     | 11%     | 12%         | 18%     | 15%          | 16%     |  |

|             |             |             | PC[13] | 8%                        | _       | 10%     | _       | 13%         | _       | 15%          | _       |  |

|             | 4           | 4           | PC[8]  | 8%                        | _       | 10%     | _       | 13%         |         | 15%          | _       |  |

|             |             |             | PB[2]  | 8%                        | 11%     | 9%      | 10%     | 13%         | 18%     | 15%          | 16%     |  |

Table 24. I/O weight<sup>(1)</sup> (continued)

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

2. SRC: "Slew Rate Control" bit in SIU\_PCRx.

# 4.7 **RESET** electrical characteristics

The device implements a dedicated bidirectional  $\overline{\text{RESET}}$  pin.

The internal voltage regulator requires external capacitance ( $C_{REGn}$ ) to be connected to the device in order to provide a stable low voltage digital supply to the device. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the board to less than 5 nH.

Each decoupling capacitor must be placed between each of the three  $V_{DD_LV}/V_{SS_LV}$  supply pairs to ensure stable voltage (see Section 4.4: Recommended operating conditions).

| Cumhal                |                        | ~ | Devenueter                                                                      | Conditions <sup>(1)</sup>                                                           |                    | Unit               |                    |    |  |

|-----------------------|------------------------|---|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|----|--|

| Symbol                |                        | С | Parameter                                                                       | Conditions                                                                          | Min                | Тур                | Max                |    |  |

| C <sub>REGn</sub>     | SR                     |   | Internal voltage regulator external<br>capacitance                              | —                                                                                   | 200                | —                  | 500                | nF |  |

| R <sub>REG</sub>      | SR                     |   | Stability capacitor equivalent serial resistance                                | Range:<br>10 kHz to 20 MHz                                                          | _                  | _                  | 0.2                | W  |  |

| C                     | SR                     |   | Decoupling capacitance <sup>(2)</sup> ballast                                   | V <sub>DD_BV</sub> /V <sub>SS_LV</sub> pair:<br>V <sub>DD_BV</sub> = 4.5 V to 5.5 V | 100 <sup>(3)</sup> | 470 <sup>(4)</sup> | _                  | ьE |  |

| C <sub>DEC1</sub>     | SK                     |   |                                                                                 | V <sub>DD_BV</sub> /V <sub>SS_LV</sub> pair:<br>V <sub>DD_BV</sub> = 3 V to 3.6 V   | 400                | 470                |                    | nF |  |

| $C_{DEC2}$            | SR                     |   | Decoupling capacitance regulator supply                                         | V <sub>DD</sub> /V <sub>SS</sub> pair                                               | 10                 | 100                | _                  | nF |  |

| M                     | <u> </u>               | Т |                                                                                 | Before exiting from reset                                                           | _                  | 1.32               | —                  | V  |  |

| <sup>V</sup> MREG     | V <sub>MREG</sub> CC F |   | Main regulator output voltage                                                   | After trimming                                                                      | 1.16               | 1.28               | V                  |    |  |

| I <sub>MREG</sub>     | SR                     |   | Main regulator current provided to V <sub>DD_LV</sub> domain                    | —                                                                                   | _                  | _                  | 150                | mA |  |

| 1 .                   | сс                     | D | Main regulator module current                                                   | I <sub>MREG</sub> = 200 mA                                                          | _                  | _                  | 2                  | mA |  |

| IMREGINT              | 00                     |   | consumption                                                                     | I <sub>MREG</sub> = 0 mA                                                            | _                  | _                  | 1                  |    |  |

| V <sub>LPREG</sub>    | СС                     | Ρ | Low-power regulator output voltage                                              | After trimming                                                                      | 1.16               | 1.28               | —                  | V  |  |

| I <sub>LPREG</sub>    | SR                     |   | Low-power regulator current provided to V <sub>DD_LV</sub> domain               | _                                                                                   |                    |                    | 15                 | mA |  |

| L                     | сс                     | D | Low-power regulator module current                                              | I <sub>LPREG</sub> = 15 mA;<br>T <sub>A</sub> = 55 °C                               | _                  | _                  | 600                | μA |  |

| I <sub>LPREGINT</sub> | 00                     |   | consumption                                                                     | I <sub>LPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C                                |                    | 5 —                |                    | μΛ |  |

| V <sub>ULPREG</sub>   | сс                     | Ρ | Ultra low power regulator output voltage                                        | After trimming                                                                      | 1.16               | 1.28               | _                  | V  |  |

| I <sub>ULPREG</sub>   | SR                     |   | Ultra low power regulator current provided to V <sub>DD_LV</sub> domain         | _                                                                                   | _                  | _                  | 5                  | mA |  |

|                       | сс                     | П | Ultra low power regulator module                                                | I <sub>ULPREG</sub> = 5 mA;<br>T <sub>A</sub> = 55 °C                               |                    |                    | 100                |    |  |

| IULPREGINT            |                        | U | current consumption                                                             | I <sub>ULPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C                               | _                  | 2                  | _                  | μA |  |

| I <sub>DD_BV</sub>    | сс                     | D | In-rush average current on V <sub>DD_BV</sub><br>during power-up <sup>(5)</sup> | —                                                                                   |                    |                    | 300 <sup>(6)</sup> | mA |  |

Table 26. Voltage regulator electrical characteristics

- 1.  $V_{DD} = 3.3 \text{ V} \pm 10\% / 5.0 \text{ V} \pm 10\%$ ,  $T_A = -40$  to 125 °C, unless otherwise specified.

- This capacitance value is driven by the constraints of the external voltage regulator supplying the V<sub>DD\_BV</sub> voltage. A typical value is in the range of 470 nF.

- 3. This value is acceptable to guarantee operation from 4.5 V to 5.5 V.

- External regulator and capacitance circuitry must be capable of providing I<sub>DD\_BV</sub> while maintaining supply V<sub>DD\_BV</sub> in operating range.

- 5. In-rush average current is seen only for short time during power-up and on standby exit (maximum 20 µs, depending on external capacitances to be loaded).

- The duration of the in-rush current depends on the capacitance placed on LV pins. BV decoupling capacitors must be sized accordingly. Refer to I<sub>MREG</sub> value for minimum amount of current to be provided in cc.

## 4.8.2 Low voltage detector electrical characteristics

The device implements a power-on reset (POR) module to ensure correct power-up initialization, as well as five low voltage detectors (LVDs) to monitor the  $V_{DD}$  and the  $V_{DD_{-LV}}$  voltage while device is supplied:

- POR monitors V<sub>DD</sub> during the power-up phase to ensure device is maintained in a safe reset state (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_POR in device reference manual)

- LVDHV3 monitors V<sub>DD</sub> to ensure device reset below minimum functional supply (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD27 in device reference manual)

- LVDHV3B monitors V<sub>DD\_BV</sub> to ensure device reset below minimum functional supply (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD27\_VREG in device reference manual)

- LVDHV5 monitors V<sub>DD</sub> when application uses device in the 5.0 V ± 10% range (refer to RGM Functional Event Status (RGM\_FES) Register flag F\_LVD45 in device reference manual)

- LVDLVCOR monitors power domain No. 1 (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD12\_PD1 in device reference manual)

- LVDLVBKP monitors power domain No. 0 (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD12\_PD0 in device reference manual)

- Note: When enabled, power domain No. 2 is monitored through LVDLVBKP.

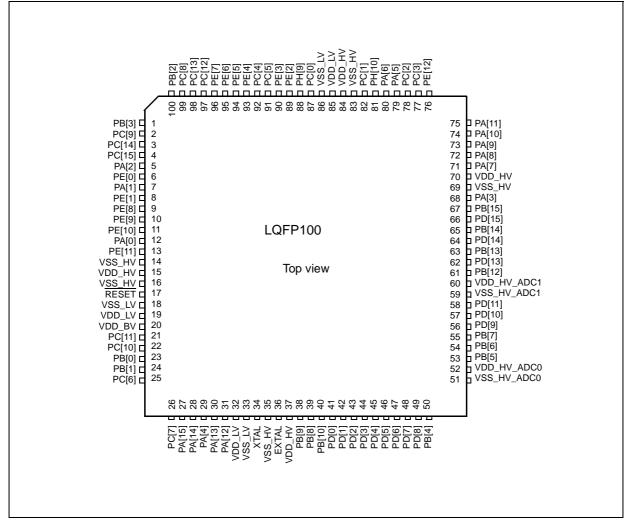

### Figure 11. Crystal oscillator and resonator connection scheme

### Table 37. Crystal description Shunt Crystal Load on capacitance Crystal Crystal Nominal equivalent xtalin/xtalout NDK crystal motional motional between frequency series reference capacitance inductance C1 = C2 xtalout resistance (MHz) (pF)<sup>(1)</sup> and xtalin (C<sub>m</sub>) fF (L<sub>m</sub>) mH **ESR** $\Omega$ C0<sup>(2)</sup> (pF) 4 NX8045GB 300 2.68 591.0 21 2.93 8 300 2.46 160.7 17 3.01 10 150 2.93 86.6 15 2.91 NX5032GA 12 120 3.11 56.5 15 2.93 16 120 3.90 25.3 10 3.00

1. The values specified for C1 and C2 are the same as used in simulations. It should be ensured that the testing includes all the parasitics (from the board, probe, crystal, etc.) as the AC / transient behavior depends upon them.

2. The value of C0 specified here includes 2 pF additional capacitance for parasitics (to be seen with bond-pads, package, etc.).

| Symbol             |    | ~ | C Parameter Conditions <sup>(1)</sup>                                                                                                                |                              |     | llmit |     |      |

|--------------------|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|-------|-----|------|

| Symbol             |    | C | Parameter                                                                                                                                            | Conditions                   | Min | Тур   | Max | Unit |

| $\Delta_{SIRCPRE}$ | сс | С | Slow internal RC oscillator precision after software trimming of f <sub>SIRC</sub>                                                                   | T <sub>A</sub> = 25 °C       | -2  | _     | 2   | %    |

|                    | сс | С | Slow internal RC oscillator trimming step                                                                                                            | —                            | _   | 2.7   | _   | /0   |

| $\Delta_{SIRCVAR}$ | сс | С | Slow internal RC oscillator variation<br>in temperature and supply with<br>respect to $f_{SIRC}$ at $T_A = 55$ °C in high<br>frequency configuration | High frequency configuration | -10 | _     | 10  | %    |

| Table 43. Slow internal RC oscillator (1 | 28 kHz) electrical characteristics (continued) |

|------------------------------------------|------------------------------------------------|

|------------------------------------------|------------------------------------------------|

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

2. This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

# 4.17 ADC electrical characteristics

# 4.17.1 Introduction

The device provides two Successive Approximation Register (SAR) analog-to-digital converters (10-bit and 12-bit).

### **Equation 11**

$$V_{A2} \bullet (C_{S} + C_{P1} + C_{P2} + C_{F}) = V_{A} \bullet C_{F} + V_{A1} \bullet (C_{P1} + C_{P2} + C_{S})$$

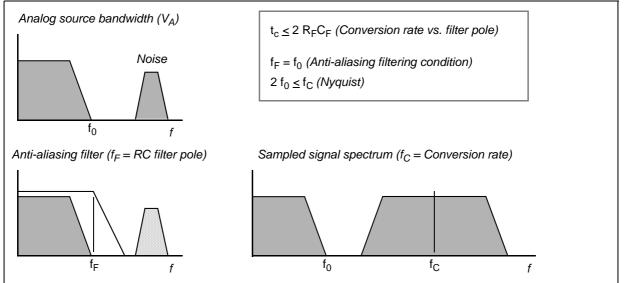

The two transients above are not influenced by the voltage source that, due to the presence of the  $R_FC_F$  filter, is not able to provide the extra charge to compensate the voltage drop on  $C_S$  with respect to the ideal source  $V_A$ ; the time constant  $R_FC_F$  of the filter is very high with respect to the sampling time (t<sub>s</sub>). The filter is typically designed to act as antialiasing.

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the antialiasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period ( $t_c$ ). Again the conversion period  $t_c$  is longer than the sampling time  $t_s$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $t_s$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive *Equation 12* between the ideal and real sampled voltage on  $C_S$ :

### **Equation 12**

$$\frac{v_{A2}}{v_A} = \frac{c_{P1} + c_{P2} + c_F}{c_{P1} + c_{P2} + c_F + c_S}$$

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

### Equation 13 ADC\_0 (10-bit)

$C_F > 2048 \bullet C_S$

DocID15131 Rev 9

# 4.18 On-chip peripherals

# 4.18.1 Current consumption

# Table 47. On-chip peripherals current consumption<sup>(1)</sup>

| Symbol                    |          | с | Parameter                                                |                                                                                                  | Conditions                                                                                                                                                 | Typical<br>value <sup>(2)</sup> | Unit |                    |  |                                                           |                          |  |

|---------------------------|----------|---|----------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|--------------------|--|-----------------------------------------------------------|--------------------------|--|

|                           |          |   |                                                          | Bitrate:<br>500 Kbyte/s                                                                          | Total (static + dynamic)<br>consumption:                                                                                                                   | 8 * f <sub>periph</sub> + 85    |      |                    |  |                                                           |                          |  |

| I <sub>DD_BV</sub> (CAN)  | сс       | т | CAN (FlexCAN)<br>supply current on<br>V <sub>DD_BV</sub> | Bitrate:<br>125 Kbyte/s                                                                          | <ul> <li>FlexCAN in loop-back<br/>mode</li> <li>XTAL at 8 MHz used as<br/>CAN engine clock source</li> <li>Message sending period is<br/>580 µs</li> </ul> | 8 * f <sub>periph</sub> + 27    | μA   |                    |  |                                                           |                          |  |

| I <sub>DD_BV(eMIOS)</sub> | 22       | т | eMIOS supply current                                     | Static consumptio<br>– eMIOS channel<br>– Global prescale                                        | OFF                                                                                                                                                        | 29 * f <sub>periph</sub>        | μA   |                    |  |                                                           |                          |  |

|                           |          | 1 | on V <sub>DD_BV</sub>                                    | Dynamic consum<br>– It does not char<br>(0.003 mA)                                               | 3                                                                                                                                                          |                                 |      |                    |  |                                                           |                          |  |

| I <sub>DD_BV(SCI)</sub>   | сс       | т | SCI (LINFlex) supply current on V <sub>DD_BV</sub>       | Total (static + dyn<br>– LIN mode<br>– Baudrate: 20 Kl                                           | 5 * f <sub>periph</sub> + 31                                                                                                                               | μA                              |      |                    |  |                                                           |                          |  |

|                           |          |   |                                                          | Ballast static cons                                                                              | sumption (only clocked)                                                                                                                                    | 1                               |      |                    |  |                                                           |                          |  |

| I <sub>DD_BV(SPI)</sub>   | сс       | т | SPI (DSPI) supply<br>current on V <sub>DD_BV</sub>       | Ballast dynamic c<br>communication):<br>– Baudrate: 2 Mb<br>– Transmission e<br>– Frame: 16 bits |                                                                                                                                                            | 16 * f <sub>periph</sub>        | μA   |                    |  |                                                           |                          |  |

| I <sub>DD BV</sub>        | ~~~      | _ | _                                                        | _                                                                                                | _                                                                                                                                                          | Ŧ                               | -    | ADC_0/ADC_1 supply |  | Ballast static consumption (no conversion) <sup>(3)</sup> | 41 * f <sub>periph</sub> |  |

| (ADC_0/ADC_1)             | CC       | 1 | ADC_0/ADC_1 supply current on V <sub>DD_BV</sub>         | V <sub>DD</sub> = 5.5 V                                                                          | Ballast dynamic consumption (continuous conversion) <sup>(3)</sup>                                                                                         | 46 * f <sub>periph</sub>        | μA   |                    |  |                                                           |                          |  |

| 1                         | <u> </u> | т | ADC_0 supply current                                     |                                                                                                  | Analog static consumption<br>(no conversion)                                                                                                               | 200                             | μA   |                    |  |                                                           |                          |  |

| IDD_HV_ADC0               |          |   | on V <sub>DD_HV_ADC0</sub>                               | V <sub>DD</sub> = 5.5 V                                                                          | Analog dynamic consumption (continuous conversion)                                                                                                         | 3                               | mA   |                    |  |                                                           |                          |  |

|                           | <u> </u> |   | ADC_1 supply current                                     | V <sub>DD</sub> = 5.5 V                                                                          | Analog static consumption<br>(no conversion)                                                                                                               | 300 * f <sub>periph</sub>       | μA   |                    |  |                                                           |                          |  |