Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI, UART/USART                   |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                  |

| Number of I/O              | 149                                                                      |

| Program Memory Size        | 1.5MB (1.5M x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 96K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 53x10/12b                                                            |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 176-LQFP                                                                 |

| Supplier Device Package    | 176-LQFP (24x24)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560b64l7c6e0y |

Introduction SPC560B54x/6x

## 1 Introduction

## 1.1 Document overview

This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the device.

## 1.2 Description

This family of 32-bit system-on-chip (SoC) microcontrollers is the latest achievement in integrated automotive application controllers. It belongs to an expanding family of automotive-focused products designed to address the next wave of body electronics applications within the vehicle.

The advanced and cost-efficient e200z0h host processor core of this automotive controller family complies with the Power Architecture technology and only implements the VLE (variable-length encoding) APU (Auxiliary Processor Unit), providing improved code density. It operates at speeds of up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

Table 2. SPC560B54/6x family comparison<sup>(1)</sup>

| Feature                                            | SPC5             | 60B54              | S                | PC560B           | 60               |                  | SPC              | C560B64          |                  |  |  |

|----------------------------------------------------|------------------|--------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|--|--|

| CPU                                                | e200z0h          |                    |                  |                  |                  |                  |                  |                  |                  |  |  |

| Execution speed <sup>(2)</sup>                     |                  | Up to 64 MHz       |                  |                  |                  |                  |                  |                  |                  |  |  |

| Code flash memory                                  | 768              | 768 KB 1 MB 1.5 MB |                  |                  |                  |                  |                  |                  |                  |  |  |

| Data flash memory                                  |                  | 64 (4 × 16) KB     |                  |                  |                  |                  |                  |                  |                  |  |  |

| SRAM                                               | 64               | KB                 |                  | 80 KB            |                  |                  | Ç                | 96 KB            |                  |  |  |

| MPU                                                |                  |                    | •                |                  | 8-entr           | у                |                  |                  |                  |  |  |

| eDMA                                               |                  |                    |                  |                  | 16 ch            | l                |                  |                  |                  |  |  |

| 10-bit ADC                                         |                  | Yes                |                  |                  |                  |                  |                  |                  |                  |  |  |

| dedicated <sup>(3)</sup>                           | 7 ch             | 15 ch              | 7 ch             | 15 ch            | 29 ch            | 7 ch             | 15 ch            | 29 ch            | 29 ch            |  |  |

| shared with 12-bit ADC                             | 19 ch            |                    |                  |                  |                  |                  |                  |                  |                  |  |  |

| 12-bit ADC                                         | Yes              |                    |                  |                  |                  |                  |                  |                  |                  |  |  |

| dedicated <sup>(4)</sup>                           | 5 ch             |                    |                  |                  |                  |                  |                  |                  |                  |  |  |

| shared with 10-bit ADC                             |                  |                    |                  |                  | 19 ch            | l                |                  |                  |                  |  |  |

| Total timer I/O <sup>(5)</sup> eMIOS               | 37 ch,<br>16-bit | 64 ch,<br>16-bit   | 37 ch,<br>16-bit | 64 ch,<br>16-bit | 64 ch,<br>16-bit | 37 ch,<br>16-bit | 64 ch,1<br>6-bit | 64 ch,<br>16-bit | 64 ch,<br>16-bit |  |  |

| Counter / OPWM / ICOC <sup>(6)</sup>               |                  |                    | l .              |                  | 10 ch            |                  |                  |                  |                  |  |  |

| O(I)PWM / OPWFMB /<br>OPWMCB / ICOC <sup>(7)</sup> |                  | 7 ch               |                  |                  |                  |                  |                  |                  |                  |  |  |

| O(I)PWM / ICOC <sup>(8)</sup>                      | 7 ch             | 14 ch              | 7 ch             | 14 ch            | 14 ch            | 7 ch             | 14 ch            | 14 ch            | 14 ch            |  |  |

8/133 DocID15131 Rev 9

Block diagram SPC560B54x/6x

Table 3. SPC560B54/6x series block summary (continued)

| Block                                         | Function                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode entry module (MC_ME)                     | Provides a mechanism for controlling the device operational mode and mode transition sequences in all functional states; also manages the power control unit, reset generation module and clock generation module, and holds the configuration, control and status registers accessible for applications |

| Non-maskable interrupt (NMI)                  | Handles external events that must produce an immediate response, such as power down detection                                                                                                                                                                                                            |

| Periodic interrupt timer (PIT)                | Produces periodic interrupts and triggers                                                                                                                                                                                                                                                                |

| Power control unit (MC_PCU)                   | Reduces the overall power consumption by disconnecting parts of the device from the power supply via a power switching device; device components are grouped into sections called "power domains" which are controlled by the PCU                                                                        |

| Real-time counter (RTC)                       | A free running counter used for time keeping applications, the RTC can be configured to generate an interrupt at a predefined interval independent of the mode of operation (run mode or low-power mode)                                                                                                 |

| Reset generation module (MC_RGM)              | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                                                                                            |

| Static random-access memory (SRAM)            | Provides storage for program code, constants, and variables                                                                                                                                                                                                                                              |

| System integration unit lite (SIUL)           | Provides control over all the electrical pad controls and up 32 ports with 16 bits of bidirectional, general-purpose input and output signals and supports up to 32 external interrupts with trigger event configuration                                                                                 |

| System status and configuration module (SSCM) | Provides system configuration and status data (such as memory size and status, device mode and security status), device identification data, debug status port enable and selection, and bus and peripheral abort enable/disable                                                                         |

| System timer module (STM)                     | Provides a set of output compare events to support AUTOSAR (Automotive Open System Architecture) and operating system tasks                                                                                                                                                                              |

| Software watchdog timer (SWT)                 | Provides protection from runaway code                                                                                                                                                                                                                                                                    |

| Wakeup unit (WKPU)                            | The wakeup unit supports up to 27 external sources that can generate interrupts or wakeup events, of which 1 can cause non-maskable interrupt requests or wakeup events.                                                                                                                                 |

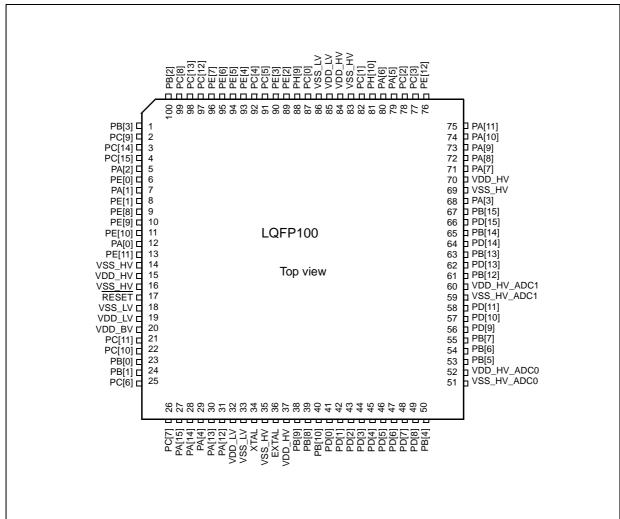

Figure 4. LQFP100 pin configuration

Figure 5 shows the SPC560B54/6x in the LBGA208 package.

Package pinouts and signal descriptions

|                       |         |                                    | Table 6. Fund                                       | tional port pin                                 | descr                          | iption            | s (continue                           | ed)         |             |             |                            |

|-----------------------|---------|------------------------------------|-----------------------------------------------------|-------------------------------------------------|--------------------------------|-------------------|---------------------------------------|-------------|-------------|-------------|----------------------------|

|                       |         | n(1)                               |                                                     |                                                 | (;                             |                   | 3)                                    |             | Pin nı      | umber       |                            |

| Port pin              | PCR     | Alternate function <sup>(1)</sup>  | Function                                            | Peripheral                                      | I/O direction <sup>(2)</sup>   | Pad type          | RESET<br>configuration <sup>(3)</sup> | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 | LBGA<br>208 <sup>(4)</sup> |

|                       |         |                                    |                                                     | Port                                            | С                              |                   |                                       |             |             |             |                            |

| PC[0] <sup>(10)</sup> | PCR[32] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[32]<br>—<br>TDI<br>—                           | SIUL<br>—<br>JTAGC<br>—                         | I/O<br>—<br>I<br>—             | М                 | Input,<br>weak pull-<br>up            | 87          | 126         | 154         | A8                         |

| PC[1] <sup>(10)</sup> | PCR[33] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[33]<br>—<br>TDO<br>—                           | SIUL<br>—<br>JTAGC<br>—                         | I/O<br>-<br>0<br>-             | F <sup>(11)</sup> | Tristate                              | 82          | 121         | 149         | C9                         |

| PC[2]                 | PCR[34] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[34]<br>SCK_1<br>CAN4TX<br>DEBUG[0]<br>EIRQ[5]  | SIUL<br>DSPI_1<br>FlexCAN_4<br>SSCM<br>SIUL     | I/O<br>I/O<br>O<br>O           | М                 | Tristate                              | 78          | 117         | 145         | A11                        |

| PC[3]                 | PCR[35] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[35] CS0_1 MA[0] DEBUG[1] EIRQ[6] CAN1RX CAN4RX | SIUL DSPI_1 ADC_0 SSCM SIUL FlexCAN_1 FlexCAN_4 | I/O<br>I/O<br>O<br>O<br>I<br>I | S                 | Tristate                              | 77          | 116         | 144         | B11                        |

| 1 |

|---|

|   |

Table 6. Functional port pin descriptions (continued)

|          |         | )u                                |                                                |                                        | <u> </u>                     |          | (6)                                   |             | Pin nu      | umber       |                            |

|----------|---------|-----------------------------------|------------------------------------------------|----------------------------------------|------------------------------|----------|---------------------------------------|-------------|-------------|-------------|----------------------------|

| Port pin | PCR     | Alternate function <sup>(1)</sup> | Function                                       | Peripheral                             | I/O direction <sup>(2)</sup> | Pad type | RESET<br>configuration <sup>(3)</sup> | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 | LBGA<br>208 <sup>(4)</sup> |

| PC[12]   | PCR[44] | AF0<br>AF1<br>AF2<br>AF3<br>—     | GPIO[44] E0UC[12] EIRQ[19] SIN_2               | SIUL eMIOS_0 SIUL DSPI_2               | I/O<br>I/O<br>—<br>—<br>I    | М        | Tristate                              | 97          | 141         | 173         | B4                         |

| PC[13]   | PCR[45] | AF0<br>AF1<br>AF2<br>AF3          | GPIO[45]<br>E0UC[13]<br>SOUT_2<br>—            | SIUL<br>eMIOS_0<br>DSPI_2<br>—         | I/O<br>I/O<br>O              | S        | Tristate                              | 98          | 142         | 174         | A2                         |

| PC[14]   | PCR[46] | AF0<br>AF1<br>AF2<br>AF3          | GPIO[46]<br>E0UC[14]<br>SCK_2<br>—<br>EIRQ[8]  | SIUL<br>eMIOS_0<br>DSPI_2<br>—<br>SIUL | I/O<br>I/O<br>I/O<br>—       | S        | Tristate                              | 3           | 3           | 3           | C1                         |

| PC[15]   | PCR[47] | AF0<br>AF1<br>AF2<br>AF3          | GPIO[47]<br>E0UC[15]<br>CS0_2<br>—<br>EIRQ[20] | SIUL<br>eMIOS_0<br>DSPI_2<br>—<br>SIUL | I/O<br>I/O<br>I/O<br>—       | M        | Tristate                              | 4           | 4           | 4           | D3                         |

| 577 |

|-----|

| •   |

Table 6. Functional port pin descriptions (continued)

|          |                | on <sup>(1)</sup>                 |                                                  |                                        | 2)                          |          | (3)                                   |             | Pin nu      | umber       |                            |

|----------|----------------|-----------------------------------|--------------------------------------------------|----------------------------------------|-----------------------------|----------|---------------------------------------|-------------|-------------|-------------|----------------------------|

| Port pin | PCR            | Alternate function <sup>(1)</sup> | Function                                         | Peripheral                             | VO direction <sup>(2)</sup> | Pad type | RESET<br>configuration <sup>(3)</sup> | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 | LBGA<br>208 <sup>(4)</sup> |

| PE[14]   | PCR[78]        | AF0<br>AF1<br>AF2<br>AF3          | GPIO[78]<br>SCK_2<br>E1UC[21]<br>—<br>EIRQ[12]   | SIUL<br>DSPI_2<br>eMIOS_1<br>—<br>SIUL | I/O<br>I/O<br>I/O<br>—      | S        | Tristate                              | _           | 112         | 136         | C13                        |

| PE[15]   | PE[15] PCR[79] |                                   | GPIO[79]<br>CS0_2<br>E1UC[22]<br>—               | SIUL<br>DSPI_2<br>eMIOS_1<br>—         | I/O<br>I/O<br>I/O           | M        | Tristate                              | _           | 113         | 137         | A13                        |

|          |                |                                   |                                                  | Port                                   | F                           |          |                                       |             |             |             |                            |

| PF[0]    | PCR[80]        | AF0<br>AF1<br>AF2<br>AF3          | GPIO[80] E0UC[10] CS3_1 — ADC0_S[8]              | SIUL eMIOS_0 DSPI_1 ADC_0              | I/O<br>I/O<br>O<br>—        | J        | Tristate                              | _           | 55          | 63          | N10                        |

| PF[1]    | PF[1] PCR[81]  |                                   | GPIO[81]<br>E0UC[11]<br>CS4_1<br>—<br>ADC0_S[9]  | SIUL eMIOS_0 DSPI_1 ADC_0              | I/O<br>I/O<br>O<br>—        | J        | Tristate                              |             | 56          | 64          | P10                        |

| PF[2]    | PCR[82]        | AF0<br>AF1<br>AF2<br>AF3          | GPIO[82]<br>E0UC[12]<br>CS0_2<br>—<br>ADC0_S[10] | SIUL eMIOS_0 DSPI_2 ADC_0              | I/O<br>I/O<br>I/O<br>—      | J        | Tristate                              | _           | 57          | 65          | T10                        |

Package pinouts and signal descriptions

|          |         |                                   | Table 6. Fund                                    | tional port pin           | descr                        | iption   | s (continue                           | ed)         |             |             |                            |

|----------|---------|-----------------------------------|--------------------------------------------------|---------------------------|------------------------------|----------|---------------------------------------|-------------|-------------|-------------|----------------------------|

|          |         | n(1)                              |                                                  |                           | (3)                          |          | 3)                                    |             | Pin nı      | umber       |                            |

| Port pin | PCR     | Alternate function <sup>(1)</sup> | Function                                         | Peripheral                | I/O direction <sup>(2)</sup> | Pad type | RESET<br>configuration <sup>(3)</sup> | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 | LBGA<br>208 <sup>(4)</sup> |

| PF[3]    | PCR[83] | AF0<br>AF1<br>AF2<br>AF3          | GPIO[83]<br>E0UC[13]<br>CS1_2<br>—<br>ADC0_S[11] | SIUL eMIOS_0 DSPI_2 ADC_0 | I/O<br>I/O<br>O<br>—         | J        | Tristate                              | _           | 58          | 66          | R10                        |

| PF[4]    | PCR[84] | AF0<br>AF1<br>AF2<br>AF3          | GPIO[84]<br>E0UC[14]<br>CS2_2<br>—<br>ADC0_S[12] | SIUL eMIOS_0 DSPI_2 ADC_0 | I/O<br>I/O<br>O<br>—         | J        | Tristate                              | _           | 59          | 67          | N11                        |

| PF[5]    | PCR[85] | AF0<br>AF1<br>AF2<br>AF3          | GPIO[85]<br>E0UC[22]<br>CS3_2<br>—<br>ADC0_S[13] | SIUL eMIOS_0 DSPI_2 ADC_0 | I/O<br>I/O<br>O<br>—         | J        | Tristate                              | _           | 60          | 68          | P11                        |

| PF[6]    | PCR[86] | AF0<br>AF1<br>AF2<br>AF3          | GPIO[86]<br>E0UC[23]<br>CS1_1<br>—<br>ADC0_S[14] | SIUL eMIOS_0 DSPI_1 ADC_0 | I/O<br>I/O<br>O<br>—         | J        | Tristate                              | _           | 61          | 69          | T11                        |

| PF[7]    | PCR[87] | AF0<br>AF1<br>AF2<br>AF3          | GPIO[87]<br>—<br>CS2_1<br>—<br>ADC0_S[15]        | SIUL  DSPI_1  ADC_0       | I/O<br>-<br>0<br>-<br>I      | J        | Tristate                              | _           | 62          | 70          | R11                        |

Table 6. Functional port pin descriptions (continued)

|          |          | on <sup>(1)</sup>                 |                                            |                                   | 2)                           |          | (3)                                   |             | Pin n       | umber       |                            |

|----------|----------|-----------------------------------|--------------------------------------------|-----------------------------------|------------------------------|----------|---------------------------------------|-------------|-------------|-------------|----------------------------|

| Port pin | PCR      | Alternate function <sup>(1)</sup> | Function                                   | Peripheral                        | I/O direction <sup>(2)</sup> | Pad type | RESET<br>configuration <sup>(3)</sup> | LQFP<br>100 | LQFP<br>144 | LQFP<br>176 | LBGA<br>208 <sup>(4)</sup> |

| PJ[2]    | PCR[146] | AF0<br>AF1<br>AF2<br>AF3          | GPIO[146]<br>CS0_5<br>—<br>—<br>ADC0_S[26] | SIUL<br>DSPI_5<br>—<br>—<br>ADC_0 | I/O<br>I/O<br>—<br>—<br>I    | J        | Tristate                              | _           | I           | 72          | P4                         |

| PJ[3]    | PCR[147] | AF0<br>AF1<br>AF2<br>AF3          | GPIO[147]<br>CS1_5<br>—<br>—<br>ADC0_S[27] | SIUL<br>DSPI_5<br>—<br>—<br>ADC_0 | I/O<br>O<br>—<br>—<br>I      | J        | Tristate                              | _           | I           | 71          | P2                         |

| PJ[4]    | PCR[148] | AF0<br>AF1<br>AF2<br>AF3          | GPIO[148]<br>SCK_5<br>E1UC[18]<br>—        | SIUL<br>DSPI_5<br>eMIOS_1<br>—    | I/O<br>I/O<br>I/O            | M        | Tristate                              | _           |             | 5           | A4                         |

Alternate functions are chosen by setting the values of the PCR.PA bitfields inside the SIUL module. PCR.PA =  $00 \rightarrow AF0$ ; PCR.PA =  $01 \rightarrow AF1$ ; PCR.PA =  $10 \rightarrow AF2$ ; PCR.PA =  $11 \rightarrow AF2$ . This is intended to select the output functions; to use one of the input functions, the PCR.IBE bit must be written to '1', regardless of the values selected in the PCR.PA bitfields. For this reason, the value corresponding to an input only function is reported as "--".

- 2. Multiple inputs are routed to all respective modules internally. The input of some modules must be configured by setting the values of the PSMIO.PADSELx bitfields inside the SIUL module.

- 3. The RESET configuration applies during and after reset.

- LBGA208 available only as development package for Nexus2+

- 5. All WKPU pins also support external interrupt capability. See the WKPU chapter for further details.

- 6. NMI has higher priority than alternate function. When NMI is selected, the PCR.AF field is ignored.

- 7. "Not applicable" because these functions are available only while the device is booting. Refer to the BAM information for details.

- Value of PCR.IBE bit must be 0.

- 9. This wakeup input cannot be used to exit STANDBY mode.

DocID15131 Rev 9

Electrical characteristics SPC560B54x/6x

## 4 Electrical characteristics

This section contains electrical characteristics of the device as well as temperature and power considerations.

This product contains devices to protect the inputs against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This could be done by the internal pull-up and pull-down, which is provided by the product for most general purpose pins.

The parameters listed in the following tables represent the characteristics of the device and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

#### 4.1 Parameter classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the classifications listed in *Table 8* are used and the parameters are tagged accordingly in the tables where appropriate.

Classification tag

Tag description

P

Those parameters are guaranteed during production testing on each individual device.

C

Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.

T

Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category.

D

Those parameters are derived mainly from simulations.

**Table 8. Parameter classifications**

Note:

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

## 4.2 NVUSRO register

Bit values in the Non-Volatile User Options (NVUSRO) Register control portions of the device configuration, namely electrical parameters such as high voltage supply and oscillator margin, as well as digital functionality (watchdog enable/disable after reset).

56/133 DocID15131 Rev 9

Electrical characteristics SPC560B54x/6x

Table 18. SLOW configuration output buffer electrical characteristics (continued)

| Symb            | aal      | С | Parameter                              |           | Conditions <sup>(1)</sup>                                                                 |     | Value |                    | Unit |

|-----------------|----------|---|----------------------------------------|-----------|-------------------------------------------------------------------------------------------|-----|-------|--------------------|------|

| Symb            | - Cymbol |   | Farameter                              |           | Conditions                                                                                | Min | Тур   | Max                | Onit |

|                 |          | Р |                                        |           | $I_{OL} = 2 \text{ mA},$ $V_{DD} = 5.0 \text{ V} \pm 10\%,$ $PAD3V5V = 0$ $(recommended)$ | _   | _     | 0.1V <sub>DD</sub> |      |

| V <sub>OL</sub> | C        | С | Output low level<br>SLOW configuration | Push Pull | $I_{OL} = 2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>$PAD3V5V = 1^{(2)}$     | _   | _     | 0.1V <sub>DD</sub> | V    |

|                 |          | С |                                        |           | $I_{OL} = 1 \text{ mA},$ $V_{DD} = 3.3 \text{ V} \pm 10\%,$ $PAD3V5V = 1$ $(recommended)$ | _   | _     | 0.5                |      |

<sup>1.</sup>  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%,  $T_A$  = -40 to 125 °C, unless otherwise specified.

Table 19. MEDIUM configuration output buffer electrical characteristics

| Sym             | hal                | 2 | Parameter                                 |           | Conditions <sup>(1)</sup>                                                                           | V                     | Unit |                    |      |

|-----------------|--------------------|---|-------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------|-----------------------|------|--------------------|------|

| Sylli           | iboi               | C | rarameter                                 |           | Conditions                                                                                          | Min                   | Тур  | Max                | Unit |

|                 |                    | С |                                           |           | $I_{OH} = -3.8 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$               | 0.8V <sub>DD</sub>    | _    | _                  |      |

|                 |                    | Р |                                           |           | $I_{OH} = -2$ mA,<br>$V_{DD} = 5.0$ V ± 10%, PAD3V5V = 0<br>(recommended)                           | 0.8V <sub>DD</sub>    | _    | _                  |      |

| V <sub>OH</sub> | V <sub>OH</sub> CC |   | Output high level<br>MEDIUM configuration | Push Pull | $I_{OH} = -1 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1^{(2)}$           | 0.8V <sub>DD</sub>    | _    | -                  | V    |

|                 |                    | С |                                           |           | $I_{OH} = -1$ mA,<br>$V_{DD} = 3.3$ V ± 10%, PAD3V5V = 1<br>(recommended)                           | V <sub>DD</sub> – 0.8 | _    | _                  |      |

|                 |                    | С |                                           |           | $I_{OH} = -100 \mu A,$<br>$V_{DD} = 5.0 V \pm 10\%, PAD3V5V = 0$                                    | 0.8V <sub>DD</sub>    |      | -                  |      |

|                 |                    | С | <u> </u>                                  |           | $I_{OL} = 3.8 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$                | _                     | _    | 0.2V <sub>DD</sub> |      |

|                 |                    | Р |                                           |           | $I_{OL} = 2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$<br>(recommended) | _                     | _    | 0.1V <sub>DD</sub> |      |

| V <sub>OL</sub> | СС                 |   | Output low level<br>MEDIUM configuration  | Push Pull | $I_{OL} = 1 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1^{(2)}$            | _                     | _    | 0.1V <sub>DD</sub> | V    |

|                 |                    | С |                                           |           | $I_{OL} = 1 \text{ mA},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$<br>(recommended) | _                     | _    | 0.5                |      |

|                 |                    | С |                                           |           | $I_{OL} = 100 \mu A,$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$                     | _                     | _    | 0.1V <sub>DD</sub> |      |

<sup>2.</sup> The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only a transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

Table 28. Power consumption on VDD\_BV and VDD\_HV

| Cumba                             | Symbol |    | Davamatav                                       | Parameter Conditions <sup>(1)</sup>                                 |                         | Value |     |                    | Unit     |    |   |                                  |                              |                         |   |    |    |    |

|-----------------------------------|--------|----|-------------------------------------------------|---------------------------------------------------------------------|-------------------------|-------|-----|--------------------|----------|----|---|----------------------------------|------------------------------|-------------------------|---|----|----|----|

| Symbo                             |        |    | Parameter                                       | Condition                                                           | is' '                   | Min   | Тур | Max                | Jint     |    |   |                                  |                              |                         |   |    |    |    |

| I <sub>DDMAX</sub> <sup>(2)</sup> | СС     | D  | RUN mode maximum average current                | _                                                                   |                         | _     | 115 | 140 <sup>(3)</sup> | mA       |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | Т  |                                                 | f <sub>CPU</sub> = 8 MHz                                            |                         | _     | 12  | _                  |          |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | Т  |                                                 | f <sub>CPU</sub> = 16 MHz                                           |                         | _     | 27  | _                  |          |    |   |                                  |                              |                         |   |    |    |    |

| I <sub>DDRUN</sub> <sup>(4)</sup> | СС     | Т  | RUN mode typical average current <sup>(5)</sup> | f <sub>CPU</sub> = 32 MHz                                           |                         | _     | 43  | _                  | mA       |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | Р  |                                                 | f <sub>CPU</sub> = 48 MHz                                           |                         | _     | 56  | 100                |          |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | Р  |                                                 | f <sub>CPU</sub> = 64 MHz                                           |                         | _     | 70  | 125                |          |    |   |                                  |                              |                         |   |    |    |    |

|                                   | -      | С  | (=)                                             | Slow internal RC                                                    | T <sub>A</sub> = 25 °C  | _     | 10  | 18                 |          |    |   |                                  |                              |                         |   |    |    |    |

| I <sub>DDHALT</sub>               | СС     | CC | CC                                              | CC                                                                  | CC                      | CC    | CC  | CC                 | CC       | CC | Р | HALT mode current <sup>(6)</sup> | oscillator (128 kHz) running | T <sub>A</sub> = 125 °C | _ | 17 | 28 | mA |

|                                   | СС     | Р  | STOP mode current <sup>(7)</sup>                | Slow internal RC oscillator (128 kHz) $T_A = 55$ running $T_A = 10$ | T <sub>A</sub> = 25 °C  | _     | 350 | 900 <sup>(8)</sup> | μA<br>mA |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | D  |                                                 |                                                                     | T <sub>A</sub> = 55 °C  | _     | 750 | _                  |          |    |   |                                  |                              |                         |   |    |    |    |

| I <sub>DDSTOP</sub>               |        | D  |                                                 |                                                                     | T <sub>A</sub> = 85 °C  | _     | 2   | 7                  |          |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | D  |                                                 |                                                                     | T <sub>A</sub> = 105 °C | _     | 4   | 10                 |          |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | Р  |                                                 |                                                                     | T <sub>A</sub> = 125 °C | _     | 7   | 14                 |          |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | Р  |                                                 |                                                                     | T <sub>A</sub> = 25 °C  | _     | 30  | 100                |          |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | D  |                                                 | Slow internal RC<br>oscillator (128 kHz)<br>running                 | T <sub>A</sub> = 55 °C  | _     | 75  | _                  | μΑ       |    |   |                                  |                              |                         |   |    |    |    |

| I <sub>DDSTDBY2</sub>             | СС     | D  | STANDBY2 mode current <sup>(9)</sup>            |                                                                     | T <sub>A</sub> = 85 °C  | _     | 180 | 700                |          |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | D  |                                                 |                                                                     | T <sub>A</sub> = 105 °C | _     | 315 | 1000               |          |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | Р  |                                                 |                                                                     | T <sub>A</sub> = 125 °C | _     | 560 | 1700               |          |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | Т  |                                                 | Slow internal RC<br>oscillator (128 kHz)<br>running                 | T <sub>A</sub> = 25 °C  | _     | 20  | 60                 |          |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | D  | D STANDBY1 mode current <sup>(10)</sup>         |                                                                     | T <sub>A</sub> = 55 °C  |       | 45  |                    | μΑ       |    |   |                                  |                              |                         |   |    |    |    |

| I <sub>DDSTDBY1</sub>             | СС     | CD |                                                 |                                                                     | T <sub>A</sub> = 85 °C  | _     | 100 | 350                |          |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | D  |                                                 |                                                                     | T <sub>A</sub> = 105 °C | _     | 165 | 500                |          |    |   |                                  |                              |                         |   |    |    |    |

|                                   |        | D  |                                                 |                                                                     | T <sub>A</sub> = 125 °C | _     | 280 | 900                |          |    |   |                                  |                              |                         |   |    |    |    |

- 1.  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%,  $T_A$  = -40 to 125 °C, unless otherwise specified.

- 2. I<sub>DDMAX</sub> is drawn only from the VDD\_BV pin. Running consumption does not include I/Os toggling which is highly dependent on the application. The given value is thought to be a worst case value with all peripherals running, and code fetched from code flash while modify operation ongoing on data flash. Notice that this value can be significantly reduced by application: switch off not used peripherals (default), reduce peripheral frequency through internal prescaler, fetch from RAM most used functions, use low power mode when possible.

- 3. Higher current may be sunk by device during power-up and standby exit. Please refer to in-rush average current in *Table 26*.

- I<sub>DDRUN</sub> is drawn only from the VDD\_BV pin. RUN current measured with typical application with accesses on both Flash and RAM.

- Only for the "P" classification: Data and Code Flash in Normal Power. Code fetched from RAM: Serial IPs CAN and LIN in loop back mode, DSPI as Master, PLL as system clock (4 x Multiplier) peripherals on (eMIOS/CTU/ADC) and running at max frequency, periodic SW/WDG timer reset enabled.

Therefore it is recommended that the user apply EMC software optimization and prequalification tests in relation with the EMC level requested for the application.

- Software recommendations The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

- Prequalification trials Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the reset pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note *Software Techniques For Improving Microcontroller EMC Performance* (AN1015)).

## 4.11.2 Electromagnetic interference (EMI)

The product is monitored in terms of emission based on a typical application. This emission test conforms to the IEC61967-1 standard, which specifies the general conditions for EMI measurements.

| Symbol             |    | С | Parameter             | Conditions                                                                                         |                                  |           | Value |      |          |  |

|--------------------|----|---|-----------------------|----------------------------------------------------------------------------------------------------|----------------------------------|-----------|-------|------|----------|--|

|                    |    | C | Farameter             | Cond                                                                                               | Conditions                       |           |       | Max  | Unit     |  |

| _                  | SR | _ | Scan range            | -                                                                                                  | _                                | 0.15<br>0 |       | 1000 | MHz      |  |

| f <sub>CPU</sub>   | SR | — | Operating frequency   | -                                                                                                  | _                                | 64        | _     | MHz  |          |  |

| V <sub>DD_LV</sub> | SR | _ | LV operating voltages | -                                                                                                  | _                                | _         | 1.28  | _    | V        |  |

|                    |    |   |                       | $V_{DD} = 5 \text{ V},$ $T_{A} = 25 \text{ °C},$                                                   | No PLL frequency modulation      | _         | _     | 18   | dBµ<br>V |  |

| S <sub>EMI</sub>   | СС | Т | Peak level            | LQFP144 package Test conforming to IEC 61967-2, f <sub>OSC</sub> = 8 MHz/f <sub>CPU</sub> = 64 MHz | ± 2% PLL frequency<br>modulation | _         | _     | 14   | dBµ<br>V |  |

Table 34. EMI radiated emission measurement<sup>(1)(2)</sup>

## 4.11.3 Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity.

<sup>1.</sup> EMI testing and I/O port waveforms per IEC 61967-1, -2, -4.

<sup>2.</sup> For information on conducted emission and susceptibility measurement (norm IEC 61967-4), please contact your local marketing representative.

Value Conditions<sup>(1)</sup> **Symbol** C Unit **Parameter** Min Typ Max sysclk = off500 sysclk = 2 MHz 600 Fast internal RC oscillator high CC T frequency and system clock  $T_A = 25 \, ^{\circ}C$ sysclk = 4 MHz 700 μΑ **IFIRCSTOP** current in stop mode sysclk = 8 MHz 900 sysclk = 16 MHz 1250 Fast internal RC oscillator start-С CC  $V_{DD} = 5.0 \text{ V} \pm 10\%$ 1.1 2.0 μs t<sub>FIRCSU</sub> up time Fast internal RC oscillator CC С precision after software  $T_A = 25 \, ^{\circ}C$ -1 1 %  $\Delta_{\mathsf{FIRCPRE}}$ trimming of f<sub>FIRC</sub> Fast internal RC oscillator CCС  $T_A = 25 \, ^{\circ}C$ 1.6 %  $\Delta_{\text{FIRCTRIM}}$ trimming step Fast internal RC oscillator variation over temperature and CC C supply with respect to f<sub>FIRC</sub> at % -5 5  $\Delta_{\mathsf{FIRCVAR}}$ T<sub>A</sub> = 25 °C in high-frequency

Table 42. Fast internal RC oscillator (16 MHz) electrical characteristics (continued)

configuration

# 4.16 Slow internal RC oscillator (128 kHz) electrical characteristics

The device provides a 128 kHz low power internal RC oscillator. This can be used as the reference clock for the RTC module.

Table 43. Slow internal RC oscillator (128 kHz) electrical characteristics

| Symbol                           |    | С | C Parameter Conditions <sup>(1)</sup>             |                                                                      | Value |     |     | Unit  |

|----------------------------------|----|---|---------------------------------------------------|----------------------------------------------------------------------|-------|-----|-----|-------|

|                                  |    |   | Farameter                                         | Conditions                                                           | Min   | Тур | Max | Oill  |

| f                                | СС | Р | Slow internal RC oscillator low                   | T <sub>A</sub> = 25 °C, trimmed                                      | _     | 128 |     | kHz   |

| f <sub>SIRC</sub>                | SR | _ | frequency                                         | _                                                                    | 100   | _   | 150 | KI IZ |

| I <sub>SIRC</sub> <sup>(2)</sup> | СС |   | Slow internal RC oscillator low frequency current | T <sub>A</sub> = 25 °C, trimmed                                      | -     |     | 5   | μΑ    |

| t <sub>SIRCSU</sub>              | СС | Р | Slow internal RC oscillator start-up time         | $T_A = 25 ^{\circ}\text{C},  V_{DD} = 5.0 ^{\circ}\text{V} \pm 10\%$ | _     | 8   | 12  | μs    |

<sup>1.</sup>  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%,  $T_A$  = -40 to 125 °C, unless otherwise specified.

<sup>2.</sup> This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

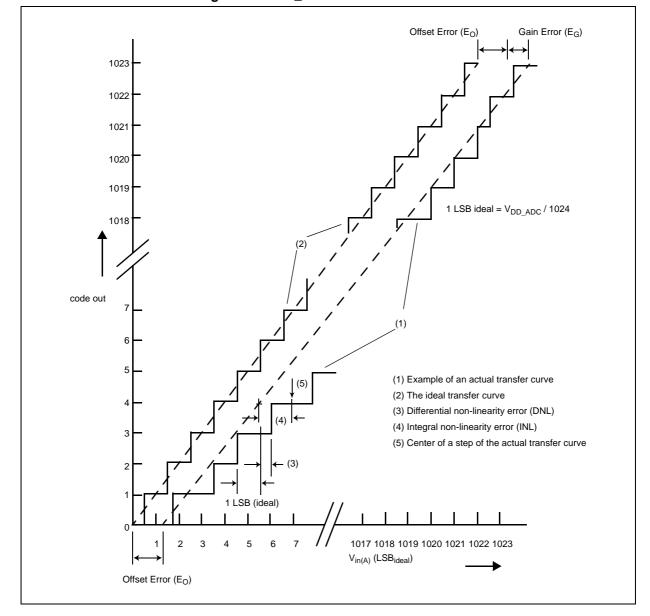

Figure 16. ADC 0 characteristic and error definitions

## 4.17.2 Input impedance and ADC accuracy

In the following analysis, the input circuit corresponding to the precise channels is considered.

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuating the noise present on the input pin; furthermore, it sources charge during the sampling phase, when the analog signal source is a high-impedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the value of source

**EXTERNAL CIRCUIT** INTERNAL CIRCUIT SCHEME Channel Extended Sampling Selection Switch Filter Source **Current Limiter** R<sub>S</sub> Source Impedance R<sub>F</sub> Filter Resistance C<sub>F</sub> Filter Capacitance R<sub>I</sub> Current Limiter Resistance  $R_{SW}$  Channel Selection Switch Impedance (two contributions  $R_{SW1}$  and  $R_{SW2}$ ) R<sub>AD</sub>Sampling Switch Impedance  $C_{P}$  Pin Capacitance (three contributions,  $C_{P1},\,C_{P2}$  and  $C_{P3})$ C<sub>S</sub> Sampling Capacitance

Figure 18. Input equivalent circuit (extended channels)

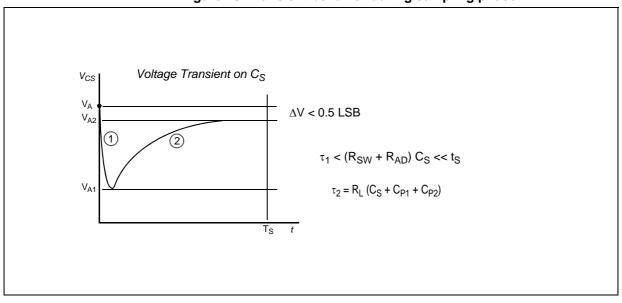

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_F$ ,  $C_{P1}$  and  $C_{P2}$  are initially charged at the source voltage  $V_A$  (refer to the equivalent circuit reported in *Figure 17*): A charge sharing phenomenon is installed when the sampling phase is started (A/D switch close).

Figure 19. Transient behavior during sampling phase

In particular two different transient periods can be distinguished:

A first and quick charge transfer from the internal capacitance C<sub>P1</sub> and C<sub>P2</sub> to the sampling capacitance C<sub>S</sub> occurs (C<sub>S</sub> is supposed initially completely discharged): considering a worst case (since the time constant in reality would be faster) in which C<sub>P2</sub> is reported in parallel to C<sub>P1</sub> (call C<sub>P</sub> = C<sub>P1</sub> + C<sub>P2</sub>), the two capacitances C<sub>P</sub> and C<sub>S</sub> are in series, and the time constant is

#### **Equation 5**

$$\tau_1 = (R_{SW} + R_{AD}) \bullet \frac{C_P \bullet C_S}{C_P + C_S}$$

Equation 5 can again be simplified considering only  $C_S$  as an additional worst condition. In reality, the transient is faster, but the A/D converter circuitry has been designed to be robust also in the very worst case: the sampling time  $t_S$  is always much longer than the internal time constant:

#### **Equation 6**

$$\tau_1 < (R_{SW} + R_{AD}) \cdot C_S \ll t_s$$

The charge of  $C_{P1}$  and  $C_{P2}$  is redistributed also on  $C_S$ , determining a new value of the voltage  $V_{A1}$  on the capacitance according to *Equation 7*:

#### **Equation 7**

$$V_{A1} \bullet (C_S + C_{P1} + C_{P2}) = V_A \bullet (C_{P1} + C_{P2})$$

2. A second charge transfer involves also  $C_F$  (that is typically bigger than the on-chip capacitance) through the resistance  $R_L$ : again considering the worst case in which  $C_{P2}$  and  $C_S$  were in parallel to  $C_{P1}$  (since the time constant in reality would be faster), the time constant is:

### **Equation 8**

$$\tau_2 < R_L \bullet (C_S + C_{P1} + C_{P2})$$

In this case, the time constant depends on the external circuit: in particular imposing that the transient is completed well before the end of sampling time  $t_s$ , a constraints on  $R_1$  sizing is obtained:

## Equation 9 ADC\_0 (10-bit)

$$8.5 \bullet \tau_2 = 8.5 \bullet R_L \bullet (C_S + C_{P1} + C_{P2}) < t_s$$

#### Equation 10 ADC\_1 (12-bit)

$$10 \bullet \tau_2 = 10 \bullet R_L \bullet (C_S + C_{P1} + C_{P2}) < t_s$$

Of course,  $R_L$  shall be sized also according to the current limitation constraints, in combination with  $R_S$  (source impedance) and  $R_F$  (filter resistance). Being  $C_F$  definitively bigger than  $C_{P1}$ ,  $C_{P2}$  and  $C_S$ , then the final voltage  $V_{A2}$  (at the end of the charge transfer transient) will be much higher than  $V_{A1}$ . Equation 11 must be respected (charge balance assuming now  $C_S$  already charged at  $V_{A1}$ ):

100/133 DocID15131 Rev 9

#### **Equation 11**

$$V_{A2} \bullet (C_S + C_{P1} + C_{P2} + C_F) = V_A \bullet C_F + V_{A1} \bullet (C_{P1} + C_{P2} + C_S)$$

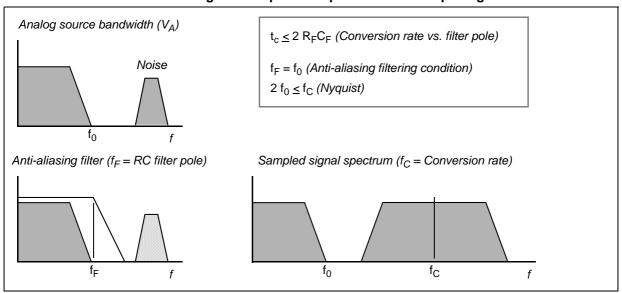

The two transients above are not influenced by the voltage source that, due to the presence of the  $R_FC_F$  filter, is not able to provide the extra charge to compensate the voltage drop on  $C_S$  with respect to the ideal source  $V_A$ ; the time constant  $R_FC_F$  of the filter is very high with respect to the sampling time ( $t_s$ ). The filter is typically designed to act as antialiasing.

Figure 20. Spectral representation of input signal

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the antialiasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period ( $t_c$ ). Again the conversion period  $t_c$  is longer than the sampling time  $t_s$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $t_s$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive *Equation 12* between the ideal and real sampled voltage on  $C_S$ :

#### **Equation 12**

$$\frac{V_{A2}}{V_{A}} = \frac{C_{P1} + C_{P2} + C_{F}}{C_{P1} + C_{P2} + C_{F} + C_{S}}$$

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

#### Equation 13 ADC\_0 (10-bit)

$$C_F > 2048 \cdot C_S$$

## 4.18 On-chip peripherals

## 4.18.1 Current consumption

Table 47. On-chip peripherals current consumption<sup>(1)</sup>

| Symbol                     |           | С  | Parameter                                                |                                                                                        | Conditions Typical value <sup>(2)</sup>                                                                                                        |                              |                                           |                                           |                           |                                                           |                          |   |                      |       |                                           |     |    |

|----------------------------|-----------|----|----------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------|-------------------------------------------|---------------------------|-----------------------------------------------------------|--------------------------|---|----------------------|-------|-------------------------------------------|-----|----|

|                            |           |    |                                                          |                                                                                        |                                                                                                                                                | Bitrate:<br>500 Kbyte/s      | Total (static + dynamic) consumption:     | 8 * f <sub>periph</sub> + 85              |                           |                                                           |                          |   |                      |       |                                           |     |    |

| I <sub>DD_BV(CAN)</sub>    | СС        | Т  | CAN (FlexCAN)<br>supply current on<br>V <sub>DD_BV</sub> | Bitrate:<br>125 Kbyte/s                                                                | <ul> <li>FlexCAN in loop-back mode</li> <li>XTAL at 8 MHz used as CAN engine clock source</li> <li>Message sending period is 580 µs</li> </ul> | 8 * f <sub>periph</sub> + 27 | μА                                        |                                           |                           |                                                           |                          |   |                      |       |                                           |     |    |

| IDD DW-MOC                 | IOS) CC T |    | eMIOS supply current                                     | Static consumption - eMIOS channe - Global prescale                                    | OFF                                                                                                                                            | 29 * f <sub>periph</sub>     | μA                                        |                                           |                           |                                                           |                          |   |                      |       |                                           |     |    |

| I <sub>DD_BV</sub> (eMIOS) |           |    | on V <sub>DD_BV</sub>                                    | Dynamic consumption:  — It does not change varying the frequency (0.003 mA)            |                                                                                                                                                | 3                            | μ, ,                                      |                                           |                           |                                                           |                          |   |                      |       |                                           |     |    |

| I <sub>DD_BV(SCI)</sub>    | СС        | Т  | SCI (LINFlex) supply current on V <sub>DD_BV</sub>       | Total (static + dyn<br>– LIN mode<br>– Baudrate: 20 K                                  | 5 * f <sub>periph</sub> + 31                                                                                                                   | μΑ                           |                                           |                                           |                           |                                                           |                          |   |                      |       |                                           |     |    |

|                            |           |    |                                                          |                                                                                        |                                                                                                                                                |                              | Ballast static consumption (only clocked) |                                           | 1                         |                                                           |                          |   |                      |       |                                           |     |    |

| I <sub>DD_BV(SPI)</sub>    | СС        | Т  | SPI (DSPI) supply<br>current on V <sub>DD_BV</sub>       | Ballast dynamic ocommunication):  - Baudrate: 2 Mb  - Transmission e  - Frame: 16 bits | 16 * f <sub>periph</sub>                                                                                                                       | μА                           |                                           |                                           |                           |                                                           |                          |   |                      |       |                                           |     |    |

| I <sub>DD_BV</sub>         | СС        | _  | _                                                        | _                                                                                      | _                                                                                                                                              | _                            | +                                         | ADC_0/ADC_1 supply                        | V 55V                     | Ballast static consumption (no conversion) <sup>(3)</sup> | 41 * f <sub>periph</sub> |   |                      |       |                                           |     |    |

| (ADC_0/ADC_1)              |           | I  | current on V <sub>DD_BV</sub>                            | V <sub>DD</sub> = 5.5 V                                                                | Ballast dynamic consumption (continuous conversion) <sup>(3)</sup>                                                                             | 46 * f <sub>periph</sub>     | μA                                        |                                           |                           |                                                           |                          |   |                      |       |                                           |     |    |

|                            | 00        | _  | _                                                        | _                                                                                      | +                                                                                                                                              | _                            | _                                         | _                                         | +                         | -                                                         | _                        | _ | ADC_0 supply current | V 55V | Analog static consumption (no conversion) | 200 | μА |

| IDD_HV_ADC0                | CC        | I  | on V <sub>DD_HV_ADC0</sub>                               | V <sub>DD</sub> = 5.5 V                                                                | Analog dynamic consumption (continuous conversion)                                                                                             | 3                            | mA                                        |                                           |                           |                                                           |                          |   |                      |       |                                           |     |    |

|                            | CC        | СТ | _                                                        | -                                                                                      | _                                                                                                                                              | ADC_1 supply current         | V <sub>DD</sub> = 5.5 V                   | Analog static consumption (no conversion) | 300 * f <sub>periph</sub> | μΑ                                                        |                          |   |                      |       |                                           |     |    |

| I <sub>DD_HV_ADC1</sub>    |           |    | on V <sub>DD_HV_ADC1</sub>                               | י סט – ט.ט י                                                                           | Analog dynamic consumption (continuous conversion)                                                                                             | 4                            | mA                                        |                                           |                           |                                                           |                          |   |                      |       |                                           |     |    |

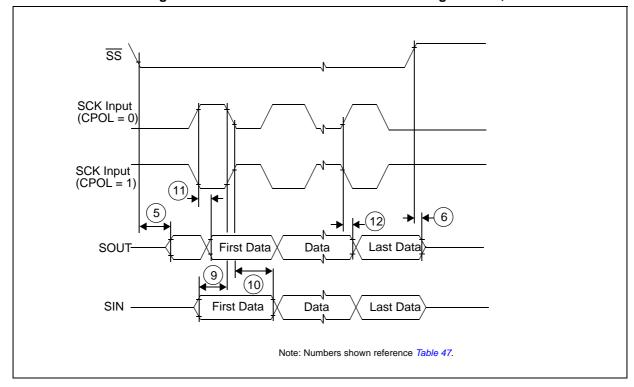

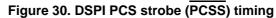

Figure 29. DSPI modified transfer format timing — slave, CPHA = 1

## 4.18.3 Nexus characteristics

**Table 49. Nexus characteristics**

| No.        | Symbol             |    | С         | Parameter                     |     | Unit |   |    |

|------------|--------------------|----|-----------|-------------------------------|-----|------|---|----|

| No. Symbol |                    |    | Farameter | Min                           | Тур | Max  |   |    |

| 1          | t <sub>TCYC</sub>  | СС | D         | TCK cycle time                | 64  | _    | _ | ns |

| 2          | t <sub>MCYC</sub>  | СС | D         | MCKO cycle time               | 32  | _    | _ | ns |

| 3          | t <sub>MDOV</sub>  | CC | D         | MCKO low to MDO data valid    | _   | _    | 8 | ns |

| 4          | t <sub>MSEOV</sub> | CC | D         | MCKO low to MSEO_b data valid | _   | _    | 8 | ns |

Revision history SPC560B54x/6x

Table 56. Revision history (continued)

| Date         | Revision     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13-Sep-2010  | 4<br>(cont.) | Table 26  - Updated all values  - Removed I <sub>VREGREF</sub> and I <sub>VREDLVD12</sub> rows  - Added the footnote "The duration of the in-rush current depends on the capacitance placed on LV pins. BV decaps must be sized accordingly. Refer to IMREG value for minimum amount of current to be provided in cc." to the I <sub>DD_BV</sub> specification.  Table 27  - Updated V <sub>PORH</sub> min/max value  - Updated V <sub>LVDLVCORL</sub> min value  Updated Table 28  Table 29  - T <sub>dwprogram</sub> : added initial max value  - Inserted T <sub>eslat</sub> row  Table 30: removed the "To be confirmed" footnote In the "Crystal oscillator and resonator connection scheme" figure, removed R <sub>P</sub> .  Table 40  - Removed g <sub>mSXOSC</sub> row  - I <sub>SXOSCBIAS</sub> : added min/typ/max value  Table 41:  - Added Λ <sub>tCTJIT</sub> row  Table 42  - I <sub>FIRCPWD</sub> : removed row for T <sub>A</sub> = 55 °C  - Updated T <sub>FIRCSU</sub> row  Table 45: Added two rows: I <sub>ADC0pwd</sub> and I <sub>ADC0run</sub> Table 46  - Added two rows: I <sub>ADC1pwd</sub> and I <sub>ADC1run</sub> - Updated values of f <sub>ADC_1</sub> and t <sub>ADC1-PU</sub> - Updated Table 47  Updated Table 47  Updated Table 47  Updated Table 48  Added Table 55 |

| 29-Oct- 2010 | 5            | Removed "Preliminary—Subject to Change Without Notice" marking. This data sheet contains specifications based on characterization data.  Updated <i>Table 55</i> Added <i>Table 56</i> Updated <i>Figure 37</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |