Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2012.02                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | XCore                                                        |

| Core Size                  | 32-Bit 8-Core                                                |

| Speed                      | 1000MIPS                                                     |

| Connectivity               | -                                                            |

| Peripherals                |                                                              |

| Number of I/O              | 42                                                           |

| Program Memory Size        | -                                                            |

| Program Memory Type        | ROMIess                                                      |

| EEPROM Size                | -                                                            |

| RAM Size                   | 256K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                 |

| Data Converters            | -                                                            |

| Oscillator Type            | External                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 64-TQFP Exposed Pad                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xl208-256-tq64-c10 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

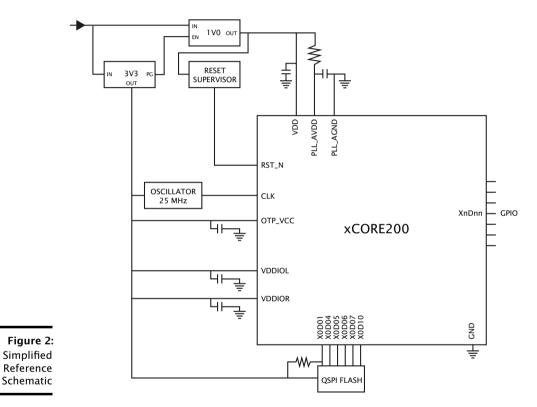

# 5 Example Application Diagram

▶ see Section 11 for details on the power supplies and PCB design

If a large boot image is to be read in, it is faster to first load a small boot-loader that reads the large image using a faster SPI clock, for example 50 MHz or as fast as the flash device supports.

The pins used for SPI boot are hardcoded in the boot ROM and cannot be changed. If required, an SPI boot program can be burned into OTP that uses different pins.

#### 8.3 Boot from SPI slave

If set to boot from SPI slave, the processor enables the three pins specified in Figure 12 and expects a boot image to be clocked in. The supported clock polarity and phase are 0/0 and 1/1.

Figure 12 SPI slave pins

|       | Pin   | Signal | Description                |

|-------|-------|--------|----------------------------|

|       | X0D00 | SS     | Slave Select               |

| e 12: | X0D10 | SCLK   | Clock                      |

| pins  | X0D11 | MOSI   | Master Out Slave In (Data) |

The xCORE Tile expects each byte to be transferred with the *least-significant bit first*. The pins used for SPI boot are hardcoded in the boot ROM and cannot be changed. If required, an SPI boot program can be burned into OTP that uses different pins.

#### 8.4 Boot from xConnect Link

If set to boot from an xConnect Link, the processor enables its link(s) around 2 us after the boot process starts. Enabling the Link switches off the pull-down resistors on the link, drives all the TX wires low (the initial state for the Link), and monitors the RX pins for boot-traffic; they must be low at this stage. If the internal pull-down is too weak to drain any residual charge, external pull-downs of 10K may be required on those pins.

The boot-rom on the core will then:

- 1. Allocate channel-end 0.

- 2. Input a word on channel-end 0. It will use this word as a channel to acknowledge the boot. Provide the null-channel-end 0x0000FF02 if no acknowledgment is required.

- 3. Input the boot image specified above, including the CRC.

- 4. Input an END control token.

- 5. Output an END control token to the channel-end received in step 2.

- 6. Free channel-end 0.

- 7. Jump to the loaded code.

The following ground pins are provided:

- PLL\_AGND for PLL\_AVDD

- ▶ GND for all other supplies

All ground pins must be connected directly to the board ground.

The VDD and VDDIO supplies should be decoupled close to the chip by several 100 nF low inductance multi-layer ceramic capacitors between the supplies and GND (for example, 100nF 0402 for each supply pin). The ground side of the decoupling capacitors should have as short a path back to the GND pins as possible. A bulk decoupling capacitor of at least 10 uF should be placed on each of these supplies.

RST\_N is an active-low asynchronous-assertion global reset signal. Following a reset, the PLL re-establishes lock after which the device boots up according to the boot mode (*see* §8). RST\_N and must be asserted low during and after power up for 100 ns.

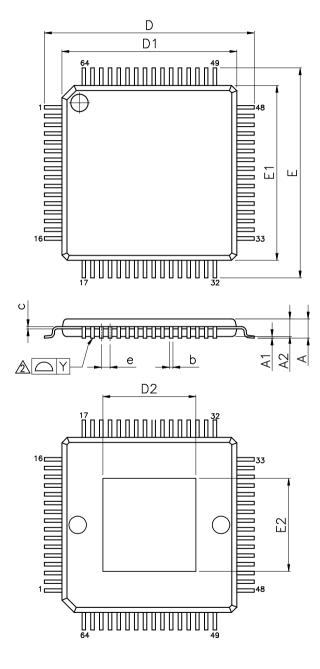

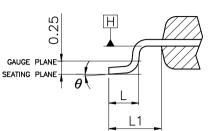

#### 11.1 Land patterns and solder stencils

The package is a 64 pin Thin Quad Flat Package (TQFP) with exposed ground paddle/heat slug on a 0.5mm pitch.

The land patterns and solder stencils will depend on the PCB manufacturing process. We recommend you design them with using the IPC specifications *"Generic Requirements for Surface Mount Design and Land Pattern Standards"* IPC-7351B. This standard aims to achieve desired targets of heel, toe and side fillets for solder-joints. The mechanical drawings in Section 13 specify the dimensions and tolerances.

## 11.2 Ground and Thermal Vias

Vias under the heat slug into the ground plane of the PCB are recommended for a low inductance ground connection and good thermal performance. Typical designs could use 16 vias in a 4  $\times$  4 grid, equally spaced across the heat slug.

## 11.3 Moisture Sensitivity

XMOS devices are, like all semiconductor devices, susceptible to moisture absorption. When removed from the sealed packaging, the devices slowly absorb moisture from the surrounding environment. If the level of moisture present in the device is too high during reflow, damage can occur due to the increased internal vapour pressure of moisture. Example damage can include bond wire damage, die lifting, internal or external package cracks and/or delamination.

All XMOS devices are Moisture Sensitivity Level (MSL) 3 - devices have a shelf life of 168 hours between removal from the packaging and reflow, provided they are stored below 30C and 60% RH. If devices have exceeded these values or an included moisture indicator card shows excessive levels of moisture, then the parts should be baked as appropriate before use. This is based on information from *Joint*

# 13 Package Information

VARIATIONS (ALL DIMENSIONS SHOWN IN MM)

| WARRANDING (ALL DIMILINGIONS SHOWIN IN M |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SYMBOLS                                  | MIN.                                                                                                        | NOM.                                                                                                                                                                                                                                                                                                                                                                                                      | MAX.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| А                                        | _                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                         | 1.20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| A1                                       | 0.05                                                                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                         | 0.15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| A2                                       | 0.95                                                                                                        | 1.00                                                                                                                                                                                                                                                                                                                                                                                                      | 1.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| D                                        | 11.75                                                                                                       | 12.00                                                                                                                                                                                                                                                                                                                                                                                                     | 12.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| D1                                       | 9.90                                                                                                        | 10.00                                                                                                                                                                                                                                                                                                                                                                                                     | 10.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| D2                                       | 5.13                                                                                                        | _                                                                                                                                                                                                                                                                                                                                                                                                         | 5.48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| E                                        | 11.75                                                                                                       | 12.00                                                                                                                                                                                                                                                                                                                                                                                                     | 12.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| E1                                       | 9.90                                                                                                        | 10.00                                                                                                                                                                                                                                                                                                                                                                                                     | 10.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| E2                                       | 5.13                                                                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                         | 5.48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| b                                        | 0.17                                                                                                        | 0.22                                                                                                                                                                                                                                                                                                                                                                                                      | 0.27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| с                                        | 0.09                                                                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                         | 0.20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| L                                        | 0.45                                                                                                        | 0.60                                                                                                                                                                                                                                                                                                                                                                                                      | 0.75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| L1                                       |                                                                                                             | 1.00 REF                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| е                                        | (                                                                                                           | 0.50 BSC                                                                                                                                                                                                                                                                                                                                                                                                  | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| θ                                        | 0°                                                                                                          | 3.5°                                                                                                                                                                                                                                                                                                                                                                                                      | 7 <b>°</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Y                                        |                                                                                                             | 0.08                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                          | SYMBOLS<br>A<br>A1<br>A1<br>D<br>D1<br>D2<br>E<br>E1<br>E1<br>E2<br>b<br>c<br>C<br>L<br>L1<br>e<br><b>θ</b> | SYMBOLS         MIN.           A         -           A1         0.05           A2         0.95           D         11.75           D1         9.90           D2         5.13           E         11.75           E1         9.90           E2         5.13           b         0.17           c         0.09           L         0.45           L1         -           e         -           Ø         0' | SYMBOLS         MIN.         NOM.           A         -         -           A1         0.05         -           A2         0.95         1.00           D         11.75         12.00           D1         9.90         10.00           D2         5.13         -           E         11.75         12.00           E1         9.90         10.00           E2         5.13         -           b         0.17         0.22           c         0.09         -           L         0.45         0.60           L1         1.00 REF         e           e         0.50 BSC         0°           Ø         0°         3.5° |  |  |

NOTES:

XMOS

1.JEDEC OUTLINE :

MS-026 ACD-HD

- 2.DATUM PLANE H IS LOCATED AT THE BOTTOM OF THE MOLD PARTING LINE COINCIDENT WITH WHERE THE LEAD EXITS THE BODY.

- 3.DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 mm PER SIDE. DIMENSIONS D1 AND E1 DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE H.

- 4.DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION.

# Appendices

# A Configuration of the XL208-256-TQ64

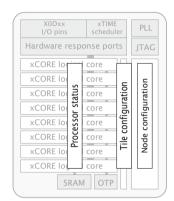

The device is configured through banks of registers, as shown in Figure 29.

Figure 29: Registers

> The following communication sequences specify how to access those registers. Any messages transmitted contain the most significant 24 bits of the channel-end to which a response is to be sent. This comprises the node-identifier and the channel number within the node. if no response is required on a write operation, supply 24-bits with the last 8-bits set, which suppresses the reply message. Any multi-byte data is sent most significant byte first.

#### A.1 Accessing a processor status register

The processor status registers are accessed directly from the processor instruction set. The instructions GETPS and SETPS read and write a word. The register number should be translated into a processor-status resource identifier by shifting the register number left 8 places, and ORing it with 0x0B. Alternatively, the functions getps(reg) and setps(reg, value) can be used from XC.

## A.2 Accessing an xCORE Tile configuration register

xCORE Tile configuration registers can be accessed through the interconnect using the functions write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tile  $\rightarrow$  ref, ...), where tileref is the name of the xCORE Tile, e.g. tile[1]. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the xCORE tile configuration registers. The destination of the channel-end should be set to 0xnnnnC20C where nnnnnn is the tile-identifier.

A write message comprises the following:

27

| control-token | 24-bit response        | 16-bit          | 32-bit | control-token |

|---------------|------------------------|-----------------|--------|---------------|

| 192           | channel-end identifier | register number | data   | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to the read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

#### A.3 Accessing node configuration

Node configuration registers can be accessed through the interconnect using the functions write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device,  $\rightarrow$  ...), where device is the name of the node. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the node configuration registers. The destination of the channel-end should be set to 0xnnnnC30C where nnnn is the node-identifier.

A write message comprises the following:

control-token

24-bit response

16-bit

32-bit

control-token

192

channel-end identifier

register number

data

1

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to a read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

### B.6 Ring Oscillator Control: 0x06

There are four free-running oscillators that clock four counters. The oscillators can be started and stopped using this register. The counters should only be read when the ring oscillator has been stopped for at least 10 core clock cycles (this can be achieved by inserting two nop instructions between the SETPS and GETPS). The counter values can be read using four subsequent registers. The ring oscillators are asynchronous to the xCORE tile clock and can be used as a source of random bits.

**0x06:** Ring Oscillator Control

| _       | Bits | Perm | Init | Description                        |

|---------|------|------|------|------------------------------------|

| 6:      | 31:2 | RO   | -    | Reserved                           |

| g<br>or | 1    | RW   | 0    | Core ring oscillator enable.       |

| ol      | 0    | RW   | 0    | Peripheral ring oscillator enable. |

#### B.7 Ring Oscillator Value: 0x07

This register contains the current count of the xCORE Tile Cell ring oscillator. This value is not reset on a system reset.

**0x07** Ring Oscillator Value

| : <b>07:</b><br>ing | Bits  | Perm | Init | Description                   |

|---------------------|-------|------|------|-------------------------------|

| tor                 | 31:16 | RO   | -    | Reserved                      |

| lue                 | 15:0  | RO   | 0    | Ring oscillator Counter data. |

#### B.8 Ring Oscillator Value: 0x08

This register contains the current count of the xCORE Tile Wire ring oscillator. This value is not reset on a system reset.

**0x08:** Ring Oscillator Value

| 3:<br>a | Bits  | Perm | Init | Description                   |

|---------|-------|------|------|-------------------------------|

| g<br>or | 31:16 | RO   | -    | Reserved                      |

| e       | 15:0  | RO   | 0    | Ring oscillator Counter data. |

## B.9 Ring Oscillator Value: 0x09

This register contains the current count of the Peripheral Cell ring oscillator. This value is not reset on a system reset.

-XMOS<sup>®</sup>

| 0x13:                | Bits | Perm | Init | Description              |

|----------------------|------|------|------|--------------------------|

| DGETREG<br>operand 1 | 31:8 | RO   | -    | Reserved                 |

|                      | 7:0  | DRW  |      | Thread number to be read |

#### B.16 DGETREG operand 2: 0x14

Register number to be read by DGETREG

0x14 DGETREG operand 2

| -<br>4: | Bits | Perm | Init | Description                |

|---------|------|------|------|----------------------------|

| т.<br>G | 31:5 | RO   | -    | Reserved                   |

| 2       | 4:0  | DRW  |      | Register number to be read |

#### B.17 Debug interrupt type: 0x15

Register that specifies what activated the debug interrupt.

| Bits  | Perm | Init | Description                                                                                                                                                                                                              |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:18 | RO   | -    | Reserved                                                                                                                                                                                                                 |

| 17:16 | DRW  |      | Number of the hardware breakpoint/watchpoint which caused<br>the interrupt (always 0 for =HOST= and =DCALL=). If multiple<br>breakpoints/watchpoints trigger at once, the lowest number is<br>taken.                     |

| 15:8  | DRW  |      | Number of thread which caused the debug interrupt (always 0 in the case of =HOST=).                                                                                                                                      |

| 7:3   | RO   | -    | Reserved                                                                                                                                                                                                                 |

| 2:0   | DRW  | 0    | Indicates the cause of the debug interrupt<br>1: Host initiated a debug interrupt through JTAG<br>2: Program executed a DCALL instruction<br>3: Instruction breakpoint<br>4: Data watch point<br>5: Resource watch point |

**0x15:** Debug interrupt type

## B.18 Debug interrupt data: 0x16

On a data watchpoint, this register contains the effective address of the memory operation that triggered the debugger. On a resource watchpoint, it countains the resource identifier.

-XMOS-

35

|                | Bits  | Perm | Init | Description                                        |

|----------------|-------|------|------|----------------------------------------------------|

|                | 31:24 | CRO  |      | Processor ID of this XCore.                        |

| 0x00:          | 23:16 | CRO  |      | Number of the node in which this XCore is located. |

| Device         | 15:8  | CRO  |      | XCore revision.                                    |

| identification | 7:0   | CRO  |      | XCore version.                                     |

#### C.2 xCORE Tile description 1: 0x01

This register describes the number of logical cores, synchronisers, locks and channel ends available on this xCORE tile.

| Bits  | Perm | Init | Description              |

|-------|------|------|--------------------------|

| 31:24 | CRO  |      | Number of channel ends.  |

| 23:16 | CRO  |      | Number of the locks.     |

| 15:8  | CRO  |      | Number of synchronisers. |

| 7:0   | RO   | -    | Reserved                 |

0x01: xCORE Tile description 1

### C.3 xCORE Tile description 2: 0x02

This register describes the number of timers and clock blocks available on this xCORE tile.

0x02: xCORE Tile description 2

|      | Bits  | Perm | Init | Description             |

|------|-------|------|------|-------------------------|

| x02: | 31:16 | RO   | -    | Reserved                |

| Tile | 15:8  | CRO  |      | Number of clock blocks. |

| on 2 | 7:0   | CRO  |      | Number of timers.       |

## C.4 Control PSwitch permissions to debug registers: 0x04

This register can be used to control whether the debug registers (marked with permission CRW) are accessible through the tile configuration registers. When this bit is set, write -access to those registers is disabled, preventing debugging of the xCORE tile over the interconnect.

0x04: Control PSwitch permissions to debug registers

| Bits | Perm | Init | Description                                                                                                     |

|------|------|------|-----------------------------------------------------------------------------------------------------------------|

| 31   | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch, XCore(PS_DBG_Scratch) and JTAG |

| 30:1 | RO   | -    | Reserved                                                                                                        |

| 0    | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch                                 |

## C.5 Cause debug interrupts: 0x05

This register can be used to raise a debug interrupt in this xCORE tile.

**0x05:** Cause debug interrupts

|     | Bits | Perm | Init | Description                                 |

|-----|------|------|------|---------------------------------------------|

|     | 31:2 | RO   | -    | Reserved                                    |

| · ( | 1    | CRW  | 0    | 1 when the processor is in debug mode.      |

|     | 0    | CRW  | 0    | Request a debug interrupt on the processor. |

## C.6 xCORE Tile clock divider: 0x06

This register contains the value used to divide the PLL clock to create the xCORE tile clock. The divider is enabled under control of the tile control register

0x06: xCORE Tile clock divider

| Bits  | Perm | Init | Description                                                   |

|-------|------|------|---------------------------------------------------------------|

| 31    | CRW  | 0    | Clock disable. Writing '1' will remove the clock to the tile. |

| 30:16 | RO   | -    | Reserved                                                      |

| 15:0  | CRW  | 0    | Clock divider.                                                |

## C.7 Security configuration: 0x07

Copy of the security register as read from OTP.

Bits

31:0

#### C.15 PC of logical core 6: 0x46

Value of the PC of logical core 6.

**0x46:** PC of logical core 6

Perm

Init

Description

CRO

Value.

#### C.16 PC of logical core 7: 0x47

Value of the PC of logical core 7.

0x47 PC of logical core 7

| 0x47:<br>gical | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| ore 7          | 31:0 | CRO  |      | Value.      |

## C.17 SR of logical core 0: 0x60

Value of the SR of logical core 0

**0x60:** SR of logical core 0

| <b>0x60:</b><br>ogical | Bits | Perm | Init | Description |

|------------------------|------|------|------|-------------|

| ore 0                  | 31:0 | CRO  |      | Value.      |

## C.18 SR of logical core 1: 0x61

Value of the SR of logical core 1

**0x61** SR of logical core 1

| 51:<br>cal | Bits | Perm | Init | Description |

|------------|------|------|------|-------------|

| 21         | 31:0 | CRO  |      | Value.      |

## C.19 SR of logical core 2: 0x62

Value of the SR of logical core 2

**0x62:** SR of logical core 2

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRO  |      | Value.      |

## C.20 SR of logical core 3: 0x63

Value of the SR of logical core 3

0x63: SR of logical core 3

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRO  |      | Value.      |

## C.21 SR of logical core 4: 0x64

Value of the SR of logical core 4

Ox64: SR of logical core 4

Bits

Perm

Init

Description

31:0

CRO

Value.

## C.22 SR of logical core 5: 0x65

Value of the SR of logical core 5

**0x65** SR of logical core 5

| <b>0x65:</b><br>ogical | Bits | Perm | Init | Description |

|------------------------|------|------|------|-------------|

| ore 5                  | 31:0 | CRO  |      | Value.      |

## C.23 SR of logical core 6: 0x66

Value of the SR of logical core 6

**0x66:** SR of logical core 6

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRO  |      | Value.      |

## **D** Node Configuration

The digital node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device,  $\rightarrow$  ...) for reads and writes).

| Number    | Perm | Description                           |

|-----------|------|---------------------------------------|

| 0x00      | RO   | Device identification                 |

| 0x01      | RO   | System switch description             |

| 0x04      | RW   | Switch configuration                  |

| 0x05      | RW   | Switch node identifier                |

| 0x06      | RW   | PLL settings                          |

| 0x07      | RW   | System switch clock divider           |

| 0x08      | RW   | Reference clock                       |

| 0x09      | R    | System JTAG device ID register        |

| 0x0A      | R    | System USERCODE register              |

| 0x0C      | RW   | Directions 0-7                        |

| 0x0D      | RW   | Directions 8-15                       |

| 0x10      | RW   | Reserved                              |

| 0x11      | RW   | Reserved.                             |

| 0x1F      | RO   | Debug source                          |

| 0x20 0x28 | RW   | Link status, direction, and network   |

| 0x40 0x47 | RO   | PLink status and network              |

| 0x80 0x88 | RW   | Link configuration and initialization |

| 0xA0 0xA7 | RW   | Static link configuration             |

Figure 32: Summary

## D.1 Device identification: 0x00

This register contains version and revision identifiers and the mode-pins as sampled at boot-time.

|             | Bits  | Perm | Init | Description                                       |

|-------------|-------|------|------|---------------------------------------------------|

|             | 31:24 | RO   | -    | Reserved                                          |

| 0x00:       | 23:16 | RO   |      | Sampled values of BootCtl pins on Power On Reset. |

| Device      | 15:8  | RO   |      | SSwitch revision.                                 |

| ntification | 7:0   | RO   |      | SSwitch version.                                  |

-XMOS<sup>®</sup>

ident

| Bits  | Perm | Init | Description                                                                                                      |

|-------|------|------|------------------------------------------------------------------------------------------------------------------|

| 31    | RW   |      | If set to 1, the chip will not be reset                                                                          |

| 30    | RW   |      | If set to 1, the chip will not wait for the PLL to re-lock. Only use this if a gradual change is made to the PLL |

| 29    | DW   |      | If set to 1, set the PLL to be bypassed                                                                          |

| 28    | DW   |      | If set to 1, set the boot mode to boot from JTAG                                                                 |

| 27:26 | RO   | -    | Reserved                                                                                                         |

| 25:23 | RW   |      | Output divider value range from 1 (8'h0) to 250 (8'hF9). P value.                                                |

| 22:21 | RO   | -    | Reserved                                                                                                         |

| 20:8  | RW   |      | Feedback multiplication ratio, range from 1 (8'h0) to 255 (8'hFE).<br>M value.                                   |

| 7     | RO   | -    | Reserved                                                                                                         |

| 6:0   | RW   |      | Oscilator input divider value range from 1 (8'h0) to 32 (8'h0F).<br>N value.                                     |

0x06: PLL settings

## D.6 System switch clock divider: 0x07

Sets the ratio of the PLL clock and the switch clock.

0x02 Systen switch cloc divide

| :      | Bits  | Perm | Init | Description              |

|--------|-------|------|------|--------------------------|

| n<br>k | 31:16 | RO   | -    | Reserved                 |

| r      | 15:0  | RW   | 0    | SSwitch clock generation |

### D.7 Reference clock: 0x08

Sets the ratio of the PLL clock and the reference clock used by the node.

| 0x08:     | Bits  | Perm | Init | Description                 |

|-----------|-------|------|------|-----------------------------|

| Reference | 31:16 | RO   | -    | Reserved                    |

| clock     | 15:0  | RW   | 3    | Software ref. clock divider |

-XMOS

Re

X006992,

| Bits  | Perm | Init | Description                                     |

|-------|------|------|-------------------------------------------------|

| 31:28 | RW   | 0    | The direction for packets whose dimension is F. |

| 27:24 | RW   | 0    | The direction for packets whose dimension is E. |

| 23:20 | RW   | 0    | The direction for packets whose dimension is D. |

| 19:16 | RW   | 0    | The direction for packets whose dimension is C. |

| 15:12 | RW   | 0    | The direction for packets whose dimension is B. |

| 11:8  | RW   | 0    | The direction for packets whose dimension is A. |

| 7:4   | RW   | 0    | The direction for packets whose dimension is 9. |

| 3:0   | RW   | 0    | The direction for packets whose dimension is 8. |

**0x0D:** Directions 8-15

## D.12 Reserved: 0x10

Reserved.

|          | 31: |

|----------|-----|

| 0x10:    |     |

| Reserved |     |

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:2 | RO   | -    | Reserved    |

| 1    | RW   | 0    | Reserved.   |

| 0    | RW   | 0    | Reserved.   |

## D.13 Reserved.: 0x11

Reserved.

**0x11:** Reserved.

| I | Bits | Perm | Init | Description |

|---|------|------|------|-------------|

| 3 | 31:2 | RO   | -    | Reserved    |

|   | 1    | RW   | 0    | Reserved.   |

|   | 0    | RW   | 0    | Reserved.   |

## D.14 Debug source: 0x1F

Contains the source of the most recent debug event.

| Bits | Perm | Init | Description                                             |

|------|------|------|---------------------------------------------------------|

| 31:5 | RO   | -    | Reserved                                                |

| 4    | RW   |      | Reserved.                                               |

| 3:2  | RO   | -    | Reserved                                                |

| 1    | RW   |      | If set, XCore1 is the source of last GlobalDebug event. |

| 0    | RW   |      | If set, XCore0 is the source of last GlobalDebug event. |

**0x1F:** Debug source

## D.15 Link status, direction, and network: 0x20 .. 0x28

These registers contain status information for low level debugging (read-only), the network number that each link belongs to, and the direction that each link is part of. The registers control links 0..7.

| Bits  | Perm | Init | Description                                                                                 |

|-------|------|------|---------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                    |

| 25:24 | RO   |      | Identify the SRC_TARGET type 0 - SLink, 1 - PLink, 2 - SSCTL, 3 - Undefine.                 |

| 23:16 | RO   |      | When the link is in use, this is the destination link number to which all packets are sent. |

| 15:12 | RO   | -    | Reserved                                                                                    |

| 11:8  | RW   | 0    | The direction that this link operates in.                                                   |

| 7:6   | RO   | -    | Reserved                                                                                    |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, reset as 0.                              |

| 3     | RO   | -    | Reserved                                                                                    |

| 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                       |

| 1     | RO   |      | 1 when the dest side of the link is in use.                                                 |

| 0     | RO   |      | 1 when the source side of the link is in use.                                               |

0x20 .. 0x28: Link status, direction, and network

## D.16 PLink status and network: 0x40 .. 0x47

These registers contain status information and the network number that each processor-link belongs to.

| Bits  | Perm | Init | Description                                                                                 |

|-------|------|------|---------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                    |

| 25:24 | RO   |      | Identify the SRC_TARGET type 0 - SLink, 1 - PLink, 2 - SSCTL, 3 - Undefine.                 |

| 23:16 | RO   |      | When the link is in use, this is the destination link number to which all packets are sent. |

| 15:6  | RO   | -    | Reserved                                                                                    |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, reset as 0.                              |

| 3     | RO   | -    | Reserved                                                                                    |

| 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                       |

| 1     | RO   |      | 1 when the dest side of the link is in use.                                                 |

| 0     | RO   |      | 1 when the source side of the link is in use.                                               |

**0x40 .. 0x47:** PLink status and network

#### D.17 Link configuration and initialization: 0x80 .. 0x88

These registers contain configuration and debugging information specific to external links. The link speed and width can be set, the link can be initialized, and the link status can be monitored. The registers control links 0..7.

| Bits  | Perm | Init | Description                                                                                                                                   |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | RW   |      | Write to this bit with '1' will enable the XLink, writing '0' will disable it. This bit controls the muxing of ports with overlapping xlinks. |

| 30    | RW   | 0    | 0: operate in 2 wire mode; 1: operate in 5 wire mode                                                                                          |

| 29:28 | RO   | -    | Reserved                                                                                                                                      |

| 27    | RO   |      | Rx buffer overflow or illegal token encoding received.                                                                                        |

| 26    | RO   | 0    | This end of the xlink has issued credit to allow the remote end to transmit                                                                   |

| 25    | RO   | 0    | This end of the xlink has credit to allow it to transmit.                                                                                     |

| 24    | WO   |      | Clear this end of the xlink's credit and issue a HELLO token.                                                                                 |

| 23    | WO   |      | Reset the receiver. The next symbol that is detected will be the first symbol in a token.                                                     |

| 22    | RO   | -    | Reserved                                                                                                                                      |

| 21:11 | RW   | 0    | Specify min. number of idle system clocks between two contin-<br>uous symbols witin a transmit token -1.                                      |

| 10:0  | RW   | 0    | Specify min. number of idle system clocks between two contin-<br>uous transmit tokens -1.                                                     |

-XMOS"

0x80 .. 0x88: Link configuration and initialization

#### F.5 Boot

- □ The device is connected to a QSPI flash for booting, connected to X0D01, X0D04..X0D07, and X0D10 (Section 8). If not, you must boot the device through OTP or JTAG, or set it to boot from SPI and connect a SPI flash.

- ☐ The Flash that you have chosen is supported by **xflash**, or you have created a specification file for it.

#### F.6 JTAG, XScope, and debugging

- $\Box$  You have decided as to whether you need an XSYS header or not (Section E)

- ☐ If you have not included an XSYS header, you have devised a method to program the SPI-flash or OTP (Section E).

#### F.7 GPIO

- □ You have not mapped both inputs and outputs to the same multi-bit port.

- Pins X0D04, X0D05, X0D06, and X0D07 are output only and are, during and after reset, pulled high and low appropriately (Section 8)

#### F.8 Multi device designs

Skip this section if your design only includes a single XMOS device.

- $\Box$  One device is connected to a QSPI or SPI flash for booting.

- Devices that boot from link have, for example, X0D06 pulled high and have link XL0 connected to a device to boot from (Section 8).

# G PCB Layout Design Check List

This section is a checklist for use by PCB designers using the XS2-L8A-256-TQ64. Each of the following sections contains items to check for each design.

#### G.1 Ground Plane

- □ Multiple vias (eg, 9) have been used to connect the center pad to the PCB ground plane. These minimize impedance and conduct heat away from the device. (Section 11.2).

- Other than ground vias, there are no (or only a few) vias underneath or closely around the device. This create a good, solid, ground plane.

#### G.2 Power supply decoupling

- The decoupling capacitors are all placed close to a supply pin (Section 11).

- $\Box$  The decoupling capacitors are spaced around the device (Section 11).

- The ground side of each decoupling capacitor has a direct path back to the center ground of the device.

#### G.3 PLL\_AVDD

The PLL\_AVDD filter (especially the capacitor) is placed close to the PLL\_AVDD pin (Section 11).

# J Revision History

| Date       | Description                                                                                      |

|------------|--------------------------------------------------------------------------------------------------|

| 2015-03-20 | Preliminary release                                                                              |

| 2015-04-14 | Added RST to pins to be pulled hard, and removed reference to TCK from Errata                    |

|            | Removed TRST_N references in packages that have no TRST_N                                        |

| 2015-05-06 | Removed references to DEBUG_N                                                                    |

| 2015-07-09 | Updated electrical characteristics - Section 12                                                  |

| 2015-08-27 | Updated part marking - Section 14                                                                |

| 2016-01-05 | Updated Power Supply and Multi Device Designs in Schematics Checklist - Section $\ensuremath{F}$ |

| 2016-04-20 | Typical internal pull-up and pull down current diagrams added - Section 12                       |

XMOS®

Copyright © 2016, All Rights Reserved.

Xmos Ltd. is the owner or licensee of this design, code, or Information (collectively, the "Information") and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. Xmos Ltd. makes no representation that the Information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.