#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 67MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                               |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                            |

| Number of I/O              | 62                                                                           |

| Program Memory Size        | 128KB (128K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 32K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                 |

| Data Converters            | A/D 1x12b; D/A 1x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-LQFP                                                                     |

| Supplier Device Package    | 100-TQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c5267axi-lp051 |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1. Architectural Overview             | 4  |

|---------------------------------------|----|

| 2. Pinouts                            | 6  |

| 3. Pin Descriptions                   | 11 |

| 4. CPU                                |    |

| 4.1 ARM Cortex-M3 CPU                 | 13 |

| 4.2 Cache Controller                  | 14 |

| 4.3 DMA and PHUB                      | 14 |

| 4.4 Interrupt Controller              | 17 |

| 5. Memory                             | 19 |

| 5.1 Static RAM                        | 19 |

| 5.2 Flash Program Memory              | 19 |

| 5.3 Flash Security                    | 19 |

| 5.4 EEPROM                            |    |

| 5.5 Nonvolatile Latches (NVLs)        | 20 |

| 5.6 External Memory Interface         |    |

| 5.7 Memory Map                        | 22 |

| 6. System Integration                 | 23 |

| 6.1 Clocking System                   | 23 |

| 6.2 Power System                      | 26 |

| 6.3 Reset                             |    |

| 6.4 I/O System and Routing            | 32 |

| 7. Digital Subsystem                  | 39 |

| 7.1 Example Peripherals               |    |

| 7.2 Universal Digital Block           | 41 |

| 7.3 UDB Array Description             | 44 |

| 7.4 DSI Routing Interface Description | 44 |

| 7.5 USB                               |    |

| 7.6 Timers, Counters, and PWMs        | 46 |

| 7.7 I <sup>2</sup> C                  | 47 |

| 8. Analog Subsystem                   | 49 |

| 8.1 Analog Routing                    | 50 |

| 8.2 Successive Approximation ADC      |    |

| 8.3 Comparators                       |    |

| 8.4 LCD Direct Drive                  | 53 |

| 8.5 CapSense                          |    |

| 8.6 Temp Sensor                       |    |

| 8.7 DAC                               | 54 |

| 9. Programming, Debug Interfaces, Resources |

|---------------------------------------------|

| 9.1 JTAG Interface                          |

| 9.2 SWD Interface57                         |

| 9.3 Debug Features58                        |

| 9.4 Trace Features58                        |

| 9.5 SWV and TRACEPORT Interfaces58          |

| 9.6 Programming Features58                  |

| 9.7 Device Security58                       |

| 9.8 CSP Package Bootloader59                |

| 10. Development Support59                   |

| 10.1 Documentation59                        |

| 10.2 Online59                               |

| 10.3 Tools59                                |

| 11. Electrical Specifications60             |

| 11.1 Absolute Maximum Ratings60             |

| 11.2 Device Level Specifications61          |

| 11.3 Power Regulators64                     |

| 11.4 Inputs and Outputs68                   |

| 11.5 Analog Peripherals75                   |

| 11.6 Digital Peripherals                    |

| 11.7 Memory                                 |

| 11.8 PSoC System Resources                  |

| 11.9 Clocking100                            |

| 12. Ordering Information                    |

| 12.1 Part Numbering Conventions105          |

| 13. Packaging 106                           |

| 14. Acronyms 109                            |

| 15. Reference Documents 110                 |

| 16. Document Conventions111                 |

| 16.1 Units of Measure                       |

| Document History Page112                    |

| Sales, Solutions, and Legal Information 114 |

| Worldwide Sales and Design Support          |

| Products                                    |

| PSoC®Solutions                              |

| Cypress Developer Community 114             |

| Technical Support 114                       |

In addition to the flexibility of the UDB array, PSoC also provides configurable digital blocks targeted at specific functions. For the CY8C52LP family these blocks can include four 16-bit timers, counters, and PWM blocks; I<sup>2</sup>C slave, master, and multimaster; Full-Speed USB.

For more details on the peripherals see the "Example Peripherals" section on page 39 of this datasheet. For information on UDBs, DSI, and other digital blocks, see the "Digital Subsystem" section on page 39 of this datasheet.

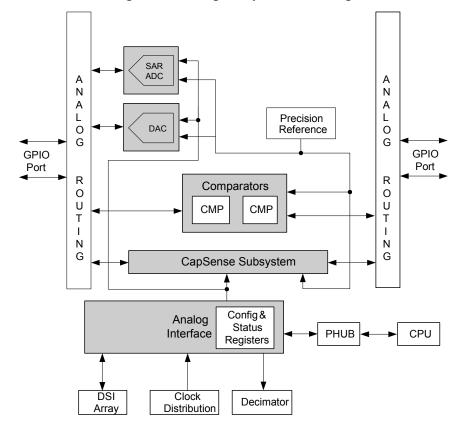

PSoC's analog subsystem is the second half of its unique configurability. All analog performance is based on a highly accurate absolute voltage reference with less than 1% error over temperature and voltage. The configurable analog subsystem includes:

- Analog muxes

- Comparators

- Voltage references

- ADC

- DAC

All GPIO pins can route analog signals into and out of the device using the internal analog bus. This allows the device to interface up to 62 discrete analog signals.

The CY8C52LP family offers a SAR ADC. Featuring 12-bit conversions at up to 1 M samples per second, it also offers low nonlinearity and offset errors and SNR better than 70 dB. It is well suited for a variety of higher speed analog applications.

A high-speed voltage or current DAC supports 8-bit output signals at an update rate of 8 Msps in IDAC and 1 Msps in VDAC. It can be routed out of any GPIO pin. You can create higher resolution voltage PWM DAC outputs using the UDB array. This can be used to create a pulse width modulated (PWM) DAC of up to 10 bits, at up to 48 kHz. The digital DACs in each UDB support PWM, PRS, or delta-sigma algorithms with programmable widths.

In addition to the ADC and DAC, the analog subsystem provides multiple comparators. See the "Analog Subsystem" section on page 49 of this datasheet for more details.

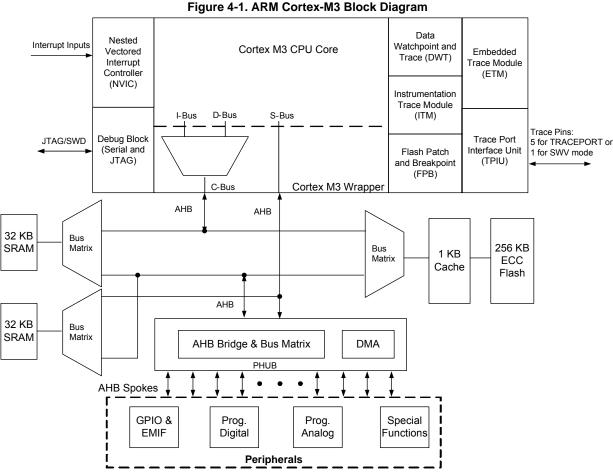

PSoC's CPU subsystem is built around a 32-bit three-stage pipelined ARM Cortex-M3 processor running at up to 80 MHz. The Cortex-M3 includes a tightly integrated nested vectored interrupt controller (NVIC) and various debug and trace modules. The overall CPU subsystem includes a DMA controller, flash cache, and RAM. The NVIC provides low latency, nested interrupts, and tail-chaining of interrupts and other features to increase the efficiency of interrupt handling. The DMA controller enables peripherals to exchange data without CPU involvement. This allows the CPU to run slower (saving power) or use those CPU cycles to improve the performance of firmware algorithms. The flash cache also reduces system power consumption by allowing less frequent flash access.

PSoC's nonvolatile subsystem consists of flash, byte-writeable EEPROM, and nonvolatile configuration options. It provides up to 256 KB of on-chip flash. The CPU can reprogram individual blocks of flash, enabling boot loaders. You can enable an ECC for high-reliability applications. A powerful and flexible protection model secures your sensitive information, allowing selective memory block locking for read and write protection. Two KB of byte-writable EEPROM is available on-chip to store application data. Additionally, selected configuration options such as boot speed and pin drive mode are stored in nonvolatile memory. This allows settings to activate immediately after power-on reset (POR).

The three types of PSoC I/O are extremely flexible. All I/Os have many drive modes that are set at POR. PSoC also provides up to four I/O voltage domains through the VDDIO pins. Every GPIO has analog I/O, LCD drive, CapSense, flexible interrupt generation, slew rate control, and digital I/O capability. The SIOs on PSoC allow  $V_{OH}$  to be set independently of VDDIO when used as outputs. When SIOs are in input mode they are high impedance. This is true even when the device is not powered or when the pin voltage goes above the supply voltage. This makes the SIO ideally suited for use on an I<sup>2</sup>C bus where the PSoC may not be powered when other devices on the bus are. The SIO pins also have high current sink capability for applications such as LED drives. The programmable input threshold feature of the SIO can be used to make the SIO function as a general purpose analog comparator. For devices with Full-Speed USB, the USB physical interface is also provided (USBIO). When not using USB these pins may also be used for limited digital functionality and device programming. All the features of the PSoC I/Os are covered in detail in the "I/O System and Routing" section on page 32 of this datasheet.

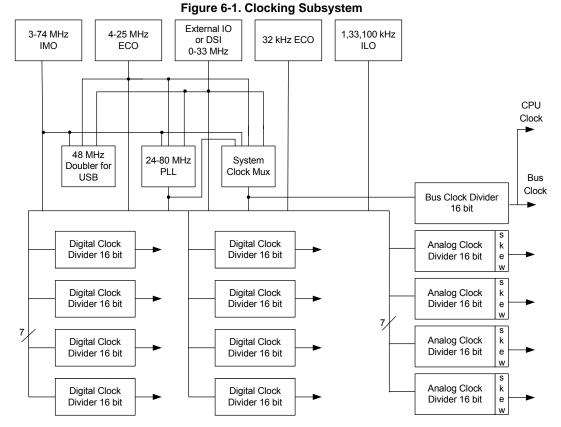

The PSoC device incorporates flexible internal clock generators, designed for high stability and factory trimmed for high accuracy. The internal main oscillator (IMO) is the master clock base for the system and has 2% accuracy at 3 MHz. The IMO can be configured to run from 3 MHz up to 74 MHz. Multiple clock derivatives can be generated from the main clock frequency to meet application needs. The device provides a PLL to generate system clock frequencies up to 80 MHz from the IMO, external crystal, or external reference clock. It also contains a separate, very low-power internal low-speed oscillator (ILO) for the sleep and watchdog timers. A 32.768-kHz external watch crystal is also supported for use in RTC applications. The clocks, together with programmable clock dividers, provide the flexibility to integrate most timing requirements.

The CY8C52LP family supports a wide supply operating range from 1.71 to 5.5 V. This allows operation from regulated supplies such as 1.8 ± 5%, 2.5 V ±10%, 3.3 V ± 10%, or 5.0 V ± 10%, or directly from a wide range of battery types. In addition, it provides an integrated high-efficiency synchronous boost converter that can power the device from supply voltages as low as 0.5 V. This enables the device to be powered directly from a single battery. In addition, you can use the boost converter to generate other voltages required by the device, such as a 3.3 V supply for LCD glass drive. The boost's output is available on the V<sub>BOOST</sub> pin, allowing other devices in the application to be powered from the PSoC.

PSoC supports a wide range of low-power modes. These include a 300 nA hibernate mode with RAM retention and a 2- $\mu$ A sleep mode with RTC. In the second mode the optional 32.768-kHz watch crystal runs continuously and maintains an accurate RTC. Power to all major functional blocks, including the programmable digital and analog peripherals, can be controlled independently by firmware. This allows low-power background processing when some peripherals are not in use. This, in turn, provides a total device current of only 3.1 mA when the CPU is running at

6 MHz.

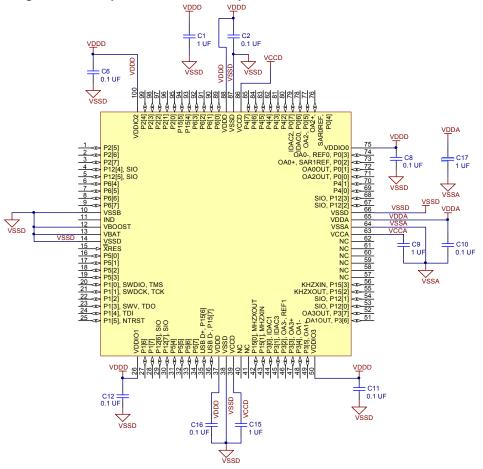

# Figure 2-5. Example Schematic for 100-pin TQFP Part with Power Connections

**Note** The two VCCD pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-6.

For more information on pad layout, refer to http://www.cypress.com/cad-resources/psoc-5lp-cad-libraries.

# 4. CPU

# 4.1 ARM Cortex-M3 CPU

The CY8C52LP family of devices has an ARM Cortex-M3 CPU core. The Cortex-M3 is a low power 32-bit three-stage pipelined Harvard architecture CPU that delivers 1.25 DMIPS/MHz. It is intended for deeply embedded applications that require fast interrupt handling features.

The Cortex-M3 CPU subsystem includes these features:

- ARM Cortex-M3 CPU

- Programmable nested vectored interrupt controller (NVIC), tightly integrated with the CPU core

- Full-featured debug and trace modules, tightly integrated with the CPU core

- Up to 256 KB of flash memory, 2 KB of EEPROM, and 64 KB of SRAM

- Cache controller

- Peripheral HUB (PHUB)

- DMA controller

- External memory interface (EMIF)

4.1.1 Cortex-M3 Features

The Cortex-M3 CPU features include:

- 4-GB address space. Predefined address regions for code, data, and peripherals. Multiple buses for efficient and simultaneous accesses of instructions, data, and peripherals.

- The Thumb<sup>®</sup>-2 instruction set, which offers ARM-level performance at Thumb-level code density. This includes 16-bit and 32-bit instructions. Advanced instructions include:

Bit-field control

- Hardware multiply and divide

- Saturation

- □ If-Then

- Wait for events and interrupts

- Exclusive access and barrier

- Special register access

The Cortex-M3 does not support ARM instructions.

There are two PHUB masters: the CPU and the DMA controller. Both masters may initiate transactions on the bus. The DMA channels can handle peripheral communication without CPU intervention. The arbiter in the central hub determines which DMA channel is the highest priority if there are multiple requests.

## 4.3.1 PHUB Features

- CPU and DMA controller are both bus masters to the PHUB

- Eight multi-layer AHB bus parallel access paths (spokes) for peripheral access

- Simultaneous CPU and DMA access to peripherals located on different spokes

- Simultaneous DMA source and destination burst transactions on different spokes

- Supports 8-, 16-, 24-, and 32-bit addressing and data

#### Table 4-3. PHUB Spokes and Peripherals

| PHUB Spokes | Peripherals                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| 0           | SRAM                                                                                                |

| 1           | IOs, PICU, EMIF                                                                                     |

| 2           | PHUB local configuration, Power manager,<br>Clocks, IC, SWV, EEPROM, Flash<br>programming interface |

| 3           | Analog interface and trim, Decimator                                                                |

| 4           | USB, I <sup>2</sup> C, Timers, Counters, and PWMs                                                   |

| 5           | Reserved                                                                                            |

| 6           | UDBs group 1                                                                                        |

| 7           | UDBs group 2                                                                                        |

## 4.3.2 DMA Features

- 24 DMA channels

- Each channel has one or more transaction descriptors (TDs) to configure channel behavior. Up to 128 total TDs can be defined

- TDs can be dynamically updated

- Eight levels of priority per channel

- Any digitally routable signal, the CPU, or another DMA channel, can trigger a transaction

- Each channel can generate up to two interrupts per transfer

- Transactions can be stalled or canceled

- Supports transaction size of infinite or 1 to 64 k bytes

- Large transactions may be broken into smaller bursts of 1 to 127 bytes

- TDs may be nested and/or chained for complex transactions

#### 4.3.3 Priority Levels

The CPU always has higher priority than the DMA controller when their accesses require the same bus resources. Due to the system architecture, the CPU can never starve the DMA. DMA channels of higher priority (lower priority number) may interrupt current DMA transfers. In the case of an interrupt, the current transfer is allowed to complete its current transaction. To ensure latency limits when multiple DMA accesses are requested simultaneously, a fairness algorithm guarantees an interleaved minimum percentage of bus bandwidth for priority levels 2 through 7. Priority levels 0 and 1 do not take part in the fairness algorithm and may use 100% of the bus bandwidth. If a tie occurs on two DMA requests of the same priority level, a simple round robin method is used to evenly share the allocated bandwidth. The round robin allocation can be disabled for each DMA channel, allowing it to always be at the head of the line. Priority levels 2 to 7 are guaranteed the minimum bus bandwidth shown in Table 4-4 after the CPU and DMA priority levels 0 and 1 have satisfied their requirements.

| Priority Level | % Bus Bandwidth |  |  |  |

|----------------|-----------------|--|--|--|

| 0              | 100.0           |  |  |  |

| 1 100.0        |                 |  |  |  |

| 2 50.0         |                 |  |  |  |

| 3              | 25.0            |  |  |  |

| 4 12.5         |                 |  |  |  |

| 5 6.2          |                 |  |  |  |

| 6              | 3.1             |  |  |  |

| 7              | 1.5             |  |  |  |

#### Table 4-4. Priority Levels

When the fairness algorithm is disabled, DMA access is granted based solely on the priority level; no bus bandwidth guarantees are made.

#### 4.3.4 Transaction Modes Supported

The flexible configuration of each DMA channel and the ability to chain multiple channels allow the creation of both simple and complex use cases. General use cases include, but are not limited to:

#### 4.3.4.1 Simple DMA

In a simple DMA case, a single TD transfers data between a source and sink (peripherals or memory location). The basic timing diagrams of DMA read and write cycles are shown in Figure 4-2. For more description on other transfer modes, refer to the Technical Reference Manual.

## 6.1.1 Internal Oscillators

Figure 6-1 shows that there are two internal oscillators. They can be routed directly or divided. The direct routes may not have a 50% duty cycle. Divided clocks have a 50% duty cycle.

#### 6.1.1.1 Internal Main Oscillator

In most designs the IMO is the only clock source required, due to its  $\pm 2\%$  accuracy. The IMO operates with no external components and outputs a stable clock. A factory trim for each frequency range is stored in the device. With the factory trim, tolerance varies from  $\pm 2\%$  at 3 MHz, up to  $\pm 7\%$  at 74 MHz. The IMO, in conjunction with the PLL, allows generation of CPU and system clocks up to the device's maximum frequency (see USB Clock Domain). The IMO provides clock outputs at 3, 6, 12, 24, 48 and 74 MHz.

#### 6.1.1.2 Clock Doubler

The clock doubler outputs a clock at twice the frequency of the input clock. The doubler works at input frequency of 24 MHz, providing 48 MHz for the USB. It can be configured to use a clock from the IMO, MHzECO, or the DSI (external pin).

### 6.1.1.3 Phase-Locked Loop

The PLL allows low frequency, high accuracy clocks to be multiplied to higher frequencies. This is a tradeoff between higher clock frequency and accuracy and, higher power consumption and increased startup time. The PLL block provides a mechanism for generating clock frequencies based upon a variety of input sources. The PLL outputs clock frequencies in the range of 24 to 80 MHz. Its input and feedback dividers supply 4032 discrete ratios to create almost any desired system clock frequency. The accuracy of the PLL output depends on the accuracy of the PLL input source. The most common PLL use is to multiply the IMO clock at 3 MHz, where it is most accurate, to generate the CPU and system clocks up to the device's maximum frequency.

The PLL achieves phase lock within 250  $\mu$ s (verified by bit setting). It can be configured to use a clock from the IMO, MHZECO, or DSI (external pin). The PLL clock source can be used until lock is complete and signaled with a lock bit. The lock signal can be routed through the DSI to generate an interrupt. Disable the PLL before entering low power modes.

#### 6.1.1.4 Internal Low Speed Oscillator

The ILO provides clock frequencies for low power consumption, including the watchdog timer, and sleep timer. The ILO generates up to three different clocks: 1 kHz, 33 kHz, and 100 kHz.

The 1-kHz clock (CLK1K) is typically used for a background 'heartbeat' timer. This clock inherently lends itself to low power supervisory operations such as the watchdog timer and long sleep intervals using the central timewheel (CTW).

The central timewheel is a 1-kHz, free-running, 13-bit counter clocked by the ILO. The central timewheel is always enabled except in hibernate mode and when the CPU is stopped during debug on chip mode. It can be used to generate periodic interrupts for timing purposes or to wake the system from a low power mode. Firmware can reset the central timewheel.

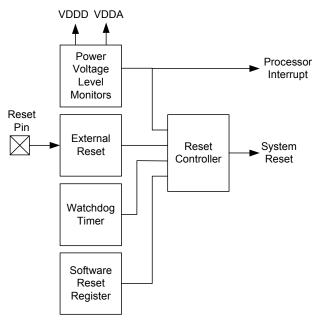

# Figure 6-8. Resets

The term **system reset** indicates that the processor as well as analog and digital peripherals and registers are reset.

A reset status register shows some of the resets or power voltage monitoring interrupts. The program may examine this register to detect and report certain exception conditions. This register is cleared after a power-on reset. For details see the Technical Reference Manual.

#### 6.3.1 Reset Sources

- 6.3.1.1 Power Voltage Level Monitors

- IPOR Initial Power-on-Reset

At initial power on, IPOR monitors the power voltages  $V_{DDD}$ ,  $V_{DDA}$ ,  $V_{CCD}$  and  $V_{CCA}$ . The trip level is not precise. It is set to approximately 1 volt (0.75 V to 1.45 V). This is below the lowest specified operating voltage but high enough for the internal circuits to be reset and to hold their reset state. The monitor generates a reset pulse that is at least 150 ns wide. It may be much wider if one or more of the voltages ramps up slowly.

After boot, the IPOR circuit is disabled and voltage supervision is handed off to the precise low-voltage reset (PRES) circuit.

PRES - Precise Low-Voltage Reset

This circuit monitors the outputs of the analog and digital internal regulators after power up. The regulator outputs are compared to a precise reference voltage. The response to a PRES trip is identical to an IPOR reset.

In normal operating mode, the program cannot disable the digital PRES circuit. The analog regulator can be disabled, which also disables the analog portion of the PRES. The PRES circuit is disabled automatically during sleep and hibernate modes, with one exception: During sleep mode the regulators are periodically activated (buzzed) to provide supervisory services and to reduce wakeup time. At these times the PRES circuit is also buzzed to allow periodic voltage monitoring.

ALVI, DLVI, AHVI - Analog/Digital Low Voltage Interrupt, Analog High Voltage Interrupt

Interrupt circuits are available to detect when VDDA and VDDD go outside a voltage range. For AHVI,  $V_{DDA}$  is compared to a fixed trip level. For ALVI and DLVI, VDDA and VDDD are compared to trip levels that are programmable, as listed in Table 6-5. ALVI and DLVI can also be configured to generate a device reset instead of an interrupt.

| Table 6-5. Analog/Digital Low Voltage Interrupt, Analog High |

|--------------------------------------------------------------|

| Voltage Interrupt                                            |

| Interrupt | Supply | Normal Voltage<br>Range | Available Trip Settings            |

|-----------|--------|-------------------------|------------------------------------|

| DLVI      | VDDD   | 1.71 V-5.5 V            | 1.70 V-5.45 V in 250 mV increments |

| ALVI      | VDDA   | 1.71 V-5.5 V            | 1.70 V-5.45 V in 250 mV increments |

| AHVI      | VDDA   | 1.71 V-5.5 V            | 5.75 V                             |

The monitors are disabled until after IPOR. During sleep mode these circuits are periodically activated (buzzed). If an interrupt occurs during buzzing then the system first enters its wakeup sequence. The interrupt is then recognized and may be serviced.

The buzz frequency is adjustable, and should be set to be less than the minimum time that any voltage is expected to be out of range. For details on how to adjust the buzz frequency, see the TRM.

#### 6.3.1.2 Other Reset Sources

XRES - External Reset

PSoC 5LP has a dedicated XRES pin, which holds the part in reset while held active (low). The response to an XRES is the same as to an IPOR reset.

The external reset is active low. It includes an internal pull up resistor. XRES is active during sleep and hibernate modes.

After XRES has been deasserted, at least 10  $\mu s$  must elapse before it can be reasserted.

SRES - Software Reset

A reset can be commanded under program control by setting a bit in the software reset register. This is done either directly by the program or indirectly by DMA access. The response to a SRES is the same as after an IPOR reset.

Another register bit exists to disable this function.

WRES - Watchdog Timer Reset

The watchdog reset detects when the software program is no longer being executed correctly. To indicate to the watchdog timer that it is running correctly, the program must periodically reset the timer. If the timer is not reset before a user-specified amount of time, then a reset is generated.

**Note** IPOR disables the watchdog function. The program must enable the watchdog function at an appropriate point in the code by setting a register bit. When this bit is set, it cannot be cleared again except by an IPOR power on reset event.

# 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the VDDIO pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both GPIO and special I/O (SIO) provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[8]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of VDDA and for programmable output voltages.

- Features supported by both GPIO and SIO:

- User programmable port reset state

- Separate I/O supplies and voltages for up to four groups of I/O

- Digital peripherals use DSI to connect the pins

Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- LCD segment drive on LCD equipped devices

- CapSense<sup>[8]</sup>

- Analog input and output capability

- □ Continuous 100 µA clamp current capability

- Standard drive strength down to 1.71 V

- Additional features only provided on SIO pins:

- B Higher drive strength than GPIO

- Hot swap capability (5 V tolerance at any operating VDD)

Programmable and regulated high input and output drive

- le Programmable and regulated high input and output drive levels down to 1.2 V

- No analog input, CapSense, or LCD capability

- $\blacksquare$  Over voltage tolerance up to 5.5 V

- SIO can act as a general purpose analog comparator

<sup>8.</sup> GPIOs with opamp outputs are not recommended for use with CapSense.

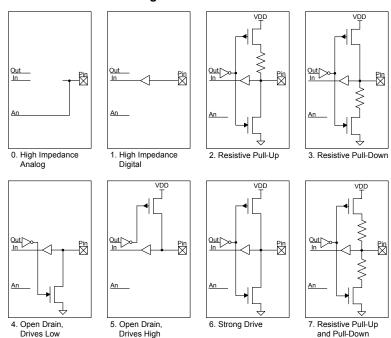

# 6.4.1 Drive Modes

Each GPIO and SIO pin is individually configurable into one of the eight drive modes listed in Table 6-6. Three configuration bits are used for each pin (DM[2:0]) and set in the PRTxDM[2:0] registers. Figure 6-12 depicts a simplified pin view based on each of the eight drive modes. Table 6-6 shows the I/O pin's drive state based on the port data register value or digital array signal

if bypass mode is selected. Note that the actual I/O pin voltage is determined by a combination of the selected drive mode and the load at the pin. For example, if a GPIO pin is configured for resistive pull up mode and driven high while the pin is floating, the voltage measured at the pin is a high logic state. If the same GPIO pin is externally tied to ground then the voltage unmeasured at the pin is a low logic state.

Figure 6-12. Drive Mode

The 'Out' connection is driven from either the Digital System (when the Digital Output terminal is connected) or the Data Register (when HW connection is disabled). The 'In' connection drives the Pin State register, and the Digital System if the Digital Input terminal is enabled and connected

The 'An' connection connects to the Analog System

#### Table 6-6. Drive Modes

| Diagram | Drive Mode                                     | PRTxDM2 | PRTxDM1 | PRTxDM0 | PRTxDR = 1    | PRTxDR = 0   |

|---------|------------------------------------------------|---------|---------|---------|---------------|--------------|

| 0       | High impedance analog                          | 0       | 0       | 0       | High-Z        | High-Z       |

| 1       | High Impedance digital                         | 0       | 0       | 1       | High-Z        | High-Z       |

| 2       | Resistive pull-up <sup>[9]</sup>               | 0       | 1       | 0       | Res High (5K) | Strong Low   |

| 3       | Resistive pull-down <sup>[9]</sup>             | 0       | 1       | 1       | Strong High   | Res Low (5K) |

| 4       | Open drain, drives low                         | 1       | 0       | 0       | High-Z        | Strong Low   |

| 5       | Open drain, drive high                         | 1       | 0       | 1       | Strong High   | High-Z       |

| 6       | Strong drive                                   | 1       | 1       | 0       | Strong High   | Strong Low   |

| 7       | Resistive pull-up and pull-down <sup>[9]</sup> | 1       | 1       | 1       | Res High (5K) | Res Low (5K) |

# 6.4.5 Pin Interrupts

All GPIO and SIO pins are able to generate interrupts to the system. All eight pins in each port interface to their own port interrupt control unit (PICU) and associated interrupt vector. Each pin of the port is independently configurable to detect rising edge, falling edge, both edge interrupts, or to not generate an interrupt.

Depending on the configured mode for each pin, each time an interrupt event occurs on a pin, its corresponding status bit of the interrupt status register is set to "1" and an interrupt request is sent to the interrupt controller. Each PICU has its own interrupt vector in the interrupt controller and the pin status register providing easy determination of the interrupt source down to the pin level.

Port pin interrupts remain active in all sleep modes allowing the PSoC device to wake from an externally generated interrupt.

While level sensitive interrupts are not directly supported; UDBs provide this functionality to the system when needed.

#### 6.4.6 Input Buffer Mode

GPIO and SIO input buffers can be configured at the port level for the default CMOS input thresholds or the optional LVTTL input thresholds. All input buffers incorporate Schmitt triggers for input hysteresis. Additionally, individual pin input buffers can be disabled in any drive mode.

#### 6.4.7 I/O Power Supplies

Up to four I/O pin power supplies are provided depending on the device and package. Each I/O supply must be less than or equal to the voltage on the chip's analog (VDDA) pin. This feature allows you to provide different I/O voltage levels for different pins on the device. Refer to the specific device package pinout to determine VDDIO capability for a given port and pin.

The SIO port pins support an additional regulated high output capability, as described in Adjustable Output Level.

#### 6.4.8 Analog Connections

These connections apply only to GPIO pins. All GPIO pins may be used as analog inputs or outputs. The analog voltage present on the pin must not exceed the VDDIO supply voltage to which the GPIO belongs. Each GPIO may connect to one of the analog global busses or to one of the analog mux buses to connect any pin to any internal analog resource such as ADC or comparators. In addition, one select pin provides direct connection to the high current DAC.

### 6.4.9 CapSense

This section applies only to GPIO pins. All GPIO pins may be used to create CapSense buttons and sliders<sup>[10]</sup>. See the "CapSense" section on page 54 for more information.

## 6.4.10 LCD Segment Drive

This section applies only to GPIO pins. All GPIO pins may be used to generate Segment and Common drive signals for direct glass drive of LCD glass. See the "LCD Direct Drive" section on page 53 for details.

#### 6.4.11 Adjustable Output Level

This section applies only to SIO pins. SIO port pins support the ability to provide a regulated high output level for interface to external signals that are lower in voltage than the SIO's respective VDDIO. SIO pins are individually configurable to output either the standard VDDIO level or the regulated output, which is based on an internally generated reference. Typically the voltage DAC (VDAC) is used to generate the reference (see Figure 6-13). The DAC on page 54 has more details on VDAC use and reference routing to the SIO pins. Resistive pull up and pull down drive modes are not available with SIO in regulated output mode.

## 6.4.12 Adjustable Input Level

This section applies only to SIO pins. SIO pins by default support the standard CMOS and LVTTL input levels but also support a differential mode with programmable levels. SIO pins are grouped into pairs. Each pair shares a reference generator block which, is used to set the digital input buffer reference level for interface to external signals that differ in voltage from VDDIO. The reference sets the pins voltage threshold for a high logic level (see Figure 6-13). Available input thresholds are:

- 0.5 × VDDIO

- 0.4 × VDDIO

- 0.5 × VREF

- VREF

Typically the voltage DAC (VDAC) generates the VREF reference. The DAC on page 54 has more details on VDAC use and reference routing to the SIO pins.

# 7. Digital Subsystem

The digital programmable system creates application specific combinations of both standard and advanced digital peripherals and custom logic functions. These peripherals and logic are then interconnected to each other and to any pin on the device, providing a high level of design flexibility and IP security.

The features of the digital programmable system are outlined here to provide an overview of capabilities and architecture. You do not need to interact directly with the programmable digital system at the hardware and register level. PSoC Creator provides a high level schematic capture graphical interface to automatically place and route resources similar to PLDs.

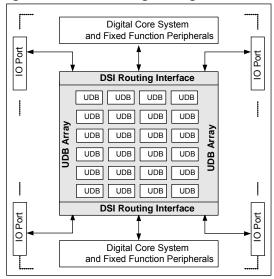

The main components of the digital programmable system are:

- Universal digital blocks (UDB) These form the core functionality of the digital programmable system. UDBs are a collection of uncommitted logic (PLD) and structural logic (Datapath) optimized to create all common embedded peripherals and customized functionality that are application or design specific.

- Universal digital block array UDB blocks are arrayed within a matrix of programmable interconnect. The UDB array structure is homogeneous and allows for flexible mapping of digital functions onto the array. The array supports extensive and flexible routing interconnects between UDBs and the digital system interconnect.

- Digital system interconnect (DSI) Digital signals from UDBs, fixed function peripherals, I/O pins, interrupts, DMA, and other system core signals are attached to the DSI to implement full featured device connectivity. The DSI allows any digital function to any pin or other feature routability when used with the UDB array.

#### Figure 7-1. CY8C52LP Digital Programmable Architecture

# 7.1 Example Peripherals

The flexibility of the CY8C52LP family's UDBs and analog blocks allow you to create a wide range of components (peripherals). The most common peripherals were built and characterized by Cypress and are shown in the PSoC Creator component catalog. However, you may also create your own custom components using PSoC Creator. Using PSoC Creator, you may also create their own components for reuse within their organization, for example sensor interfaces, proprietary algorithms, and display interfaces.

The number of components available through PSoC Creator is too numerous to list in the datasheet, and the list is always growing. An example of a component available for use in CY8C52LP family, but, not explicitly called out in this datasheet is the UART component.

#### 7.1.1 Example Digital Components

The following is a sample of the digital components available in PSoC Creator for the CY8C52LP family. The exact amount of hardware resources (UDBs, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- Communications

- □ I<sup>2</sup>C

- UART

- 🛛 SPI

- Functions

- □ EMIF

- □ PWMs

- Timers

- Counters

- Logic

- D NOT

- o OR

- □ XOR

- AND

# 7.1.2 Example Analog Components

The following is a sample of the analog components available in PSoC Creator for the CY8C52LP family. The exact amount of hardware resources (SC/CT blocks, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- ADC

- Successive Approximation (SAR ADC)

- DACs

- Current

- Voltage

- □ PWM

- Comparators

# 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses

- Successive approximation (SAR) ADC

- One 8-bit DAC that provides either voltage or current output

- Two comparators with optional connection to configurable LUT outputs

- CapSense subsystem to enable capacitive touch sensing

- Precision reference for generating an accurate analog voltage for internal analog blocks

# Figure 8-1. Analog Subsystem Block Diagram

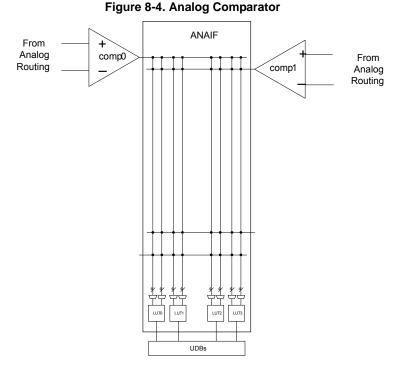

# 8.3.2 LUT

The CY8C52LP family of devices contains two LUTs. The LUT is a two input, one output lookup table that is driven by one or two of the comparators in the chip. The output of any LUT is routed to the digital system interface of the UDB array. From the digital system interface of the UDB array, these signals can be connected to UDBs, DMA controller, I/O, or the interrupt controller. The LUT control word written to a register sets the logic function on the output. The available LUT functions and the associated control word is shown in Table 8-1.

## Table 8-1. LUT Function vs. Program Word and Inputs

| Control Word | Output (A and B are LUT inputs) |

|--------------|---------------------------------|

| 0000b        | <b>FALSE</b> ('0')              |

| 0001b        | A AND B                         |

| 0010b        | A AND (NOT B)                   |

| 0011b        | A                               |

| 0100b        | (NOT A) AND B                   |

| 0101b        | В                               |

| 0110b        | A XOR B                         |

| 0111b        | A OR B                          |

| 1000b        | A NOR B                         |

| 1001b        | A XNOR B                        |

| 1010b        | NOT <b>B</b>                    |

| 1011b        | A OR (NOT B)                    |

| 1100b        | NOT A                           |

| 1101b        | (NOT A) OR B                    |

| 1110b        | A NAND B                        |

| 1111b        | <b>TRUE</b> ('1')               |

# 8.4 LCD Direct Drive

The PSoC LCD driver system is a highly configurable peripheral designed to allow PSoC to directly drive a broad range of LCD glass. All voltages are generated on chip, eliminating the need for external components. With a high multiplex ratio of up to 1/16, the CY8C52LP family LCD driver system can drive a maximum of 736 segments. The PSoC LCD driver module was also designed with the conservative power budget of portable devices in mind, enabling different LCD drive modes and power down modes to conserve power.

PSoC Creator provides an LCD segment drive component. The component wizard provides easy and flexible configuration of LCD resources. You can specify pins for segments and commons along with other options. The software configures the device to meet the required specifications. This is possible because of the programmability inherent to PSoC devices.

Key features of the PSoC LCD segment system are:

- LCD panel direct driving

- Type A (standard) and Type B (low power) waveform support

- Wide operating voltage range support (2 V to 5 V) for LCD panels

- Static, 1/2, 1/3, 1/4, 1/5 bias voltage levels

- Internal bias voltage generation through internal resistor ladder

- Up to 62 total common and segment outputs

- Up to 1/16 multiplex for a maximum of 16 backplane/common outputs

- Up to 62 front plane/segment outputs for direct drive

- Drives up to 736 total segments (16 backplane × 46 front plane)

- Up to 64 levels of software controlled contrast

- Ability to move display data from memory buffer to LCD driver through DMA (without CPU intervention)

# 9.2 SWD Interface

The SWD interface is the preferred alternative to the JTAG interface. It requires only two pins instead of the four or five needed by JTAG. SWD provides all of the programming and debugging features of JTAG at the same speed. SWD does not provide access to scan chains or device chaining. The SWD clock frequency can be up to 1/3 of the CPU clock frequency.

SWD uses two pins, either two of the JTAG pins (TMS and TCK) or the USBIO D+ and D- pins. The USBIO pins are useful for in system programming of USB solutions that would otherwise require a separate programming connector. One pin is used for the data clock and the other is used for data input and output.

SWD can be enabled on only one of the pin pairs at a time. This only happens if, within 8 µs (key window) after reset, that pin pair

(JTAG or USB) receives a predetermined acquire sequence of 1s and 0s. If the NVL latches are set for SWD (see Section 5.5), this sequence need not be applied to the JTAG pin pair. The acquire sequence must always be applied to the USB pin pair.

SWD is used for debugging or for programming the flash memory.

The SWD interface can be enabled from the JTAG interface or disabled, allowing its pins to be used as GPIO. Unlike JTAG, the SWD interface can always be reacquired on any device during the key window. It can then be used to reenable the JTAG interface, if desired. When using SWD or JTAG pins as standard GPIO, make sure that the GPIO functionality and PCB circuits do not interfere with SWD or JTAG use.

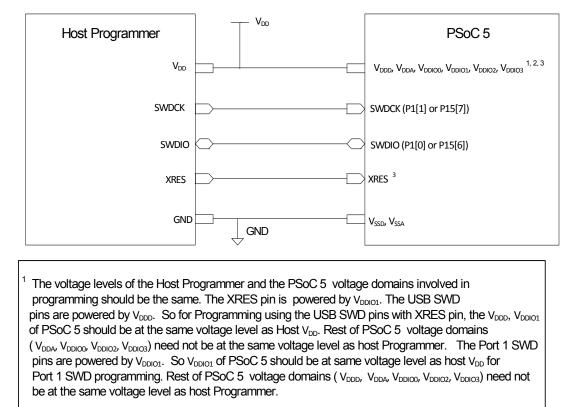

Figure 9-2. SWD Interface Connections between PSoC 5LP and Programmer

<sup>2</sup> Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 5.

For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 5. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

# 11.4 Inputs and Outputs

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. Unless otherwise specified, all charts and graphs show typical values.

When the power supplies ramp up, there are low-impedance connections between each GPIO pin and its  $V_{DDIO}$  supply. This causes the pin voltages to track  $V_{DDIO}$  until both  $V_{DDIO}$  and  $V_{DDA}$  reach the IPOR voltage, which can be as high as 1.45 V. At that point the low-impedance connections no longer exist, and the pins change to their normal NVL settings.

Also, if  $V_{DDA}$  is less than  $V_{DDIO}$ , a low-impedance path may exist between a GPIO and  $V_{DDA}$ , causing the GPIO to track  $V_{DDA}$  until  $V_{DDA}$  becomes greater than or equal to  $V_{DDIO}$ .

#### 11.4.1 GPIO

#### Table 11-8. GPIO DC Specifications

| Parameter       | Description                                                   | Conditions                                               | Min                     | Тур | Max                        | Units |

|-----------------|---------------------------------------------------------------|----------------------------------------------------------|-------------------------|-----|----------------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                  | CMOS Input, PRT[x]CTL = 0                                | $0.7 \times V_{DDIO}$   | _   | _                          | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | CMOS Input, PRT[x]CTL = 0                                | _                       | -   | 0.3 ×<br>V <sub>DDIO</sub> | V     |

| V <sub>IH</sub> | Input voltage high threshold                                  | LVTTL Input, PRT[x]CTL = 1,V <sub>DDIO</sub><br>< 2.7 V  | $0.7 \times V_{DDIO}$   | _   | _                          | V     |

| V <sub>IH</sub> | Input voltage high threshold                                  | LVTTL Input, PRT[x]CTL = 1, $V_{DDIO} \ge 2.7 \text{ V}$ | 2.0                     | -   | -                          | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | LVTTL Input, PRT[x]CTL = 1,V <sub>DDIO</sub><br>< 2.7 V  | -                       | -   | 0.3 ×<br>V <sub>DDIO</sub> | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | LVTTL Input, PRT[x]CTL = 1, $V_{DDIO} \ge 2.7 \text{ V}$ | -                       | _   | 0.8                        | V     |

| V <sub>OH</sub> | Output voltage high                                           | I <sub>OH</sub> = 4 mA at 3.3 V <sub>DDIO</sub>          | V <sub>DDIO</sub> – 0.6 | -   | _                          | V     |

|                 |                                                               | I <sub>OH</sub> = 1 mA at 1.8 V <sub>DDIO</sub>          | $V_{DDIO} - 0.5$        | -   | -                          | V     |

| V <sub>OL</sub> | Output voltage low                                            | I <sub>OL</sub> = 8 mA at 3.3 V <sub>DDIO</sub>          | —                       | -   | 0.6                        | V     |

|                 |                                                               | I <sub>OL</sub> = 3 mA at 3.3 V <sub>DDIO</sub>          | —                       | -   | 0.4                        | V     |

|                 |                                                               | I <sub>OL</sub> = 4 mA at 1.8 V <sub>DDIO</sub>          | —                       | -   | 0.6                        | V     |

| Rpullup         | Pull up resistor                                              |                                                          | 3.5                     | 5.6 | 8.5                        | kΩ    |

| Rpulldown       | Pull down resistor                                            |                                                          | 3.5                     | 5.6 | 8.5                        | kΩ    |

| IIL             | Input leakage current (absolute value) <sup>[31]</sup>        | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | _                       | -   | 2                          | nA    |

| C <sub>IN</sub> | Input capacitance <sup>[31]</sup>                             | P0.0, P0.1, P0.2, P3.6, P3.7                             | _                       | 17  | 20                         | pF    |

|                 |                                                               | P0.3, P0.4, P3.0, P3.1, P3.2                             | _                       | 10  | 15                         | pF    |

|                 |                                                               | P0.6, P0.7, P15.0, P15.6, P15.7 <sup>[32]</sup>          | _                       | 7   | 12                         | pF    |

|                 |                                                               | All other GPIOs                                          | _                       | 5   | 9                          | pF    |

| V <sub>H</sub>  | Input voltage hysteresis (Schmitt-Trigger) <sup>[31]</sup>    |                                                          | _                       | 40  | -                          | mV    |

| Idiode          | Current through protection diode to $V_{DDIO}$ and $V_{SSIO}$ |                                                          | -                       | _   | 100                        | μA    |

| Rglobal         | Resistance pin to analog global bus                           | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | _                       | 320 | _                          | Ω     |

| Rmux            | Resistance pin to analog mux bus                              | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | _                       | 220 | -                          | Ω     |

Notes

32. For information on designing with PSoC oscillators, refer to the application note, AN54439 - PSoC<sup>®</sup> 3 and PSoC 5 External Oscillator.

<sup>31.</sup> Based on device characterization (Not production tested).

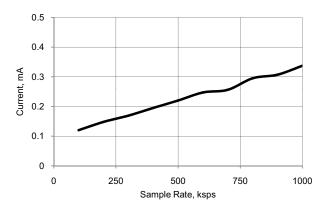

# Figure 11-27. SAR ADC $I_{DD}$ vs sps, $V_{DDA}$ = 5 V, Continuous Sample Mode, External Reference Mode

# Table 11-20. SAR ADC AC Specifications<sup>[42]</sup>

| Parameter | Description                                                    | Conditions | Min | Тур | Max  | Units |

|-----------|----------------------------------------------------------------|------------|-----|-----|------|-------|

| A_SAMP_1  | Sample rate with external reference bypass cap                 |            | -   | -   | 1    | Msps  |

| A_SAMP_2  | Sample rate with no bypass cap.<br>Reference = V <sub>DD</sub> |            | -   | -   | 500  | Ksps  |

| A_SAMP_3  | Sample rate with no bypass cap.<br>Internal reference          |            | -   | -   | 100  | Ksps  |

|           | Startup time                                                   |            | -   | -   | 10   | μs    |

| SINAD     | Signal-to-noise ratio                                          |            | 68  | -   | -    | dB    |

| THD       | Total harmonic distortion                                      |            | _   | _   | 0.02 | %     |

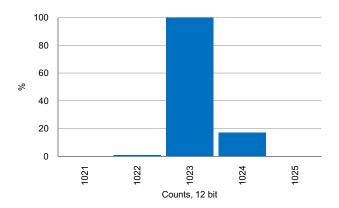

# Figure 11-28. SAR ADC Noise Histogram, 100 ksps, Internal Reference No Bypass

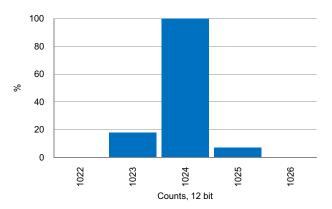

# Figure 11-29. SAR ADC Noise Histogram, 1 msps, Internal Reference Bypassed

#### Note 42. Based on device characterization (Not production tested).

# 11.5.7 Temperature Sensor

# Table 11-29. Temperature Sensor Specifications

| Parameter | Description          | Conditions              | Min | Тур | Max | Units |

|-----------|----------------------|-------------------------|-----|-----|-----|-------|

|           | Temp sensor accuracy | Range: –40 °C to +85 °C | -   | ±5  | -   | °C    |

11.5.8 LCD Direct Drive

# Table 11-30. LCD Direct Drive DC Specifications<sup>[54]</sup>

| Parameter           | Description                                                                         | Conditions                                                                                                                                                                                    | Min | Тур                    | Max  | Units |

|---------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|------|-------|

| lcc                 | LCD Block (no glass)                                                                | Device sleep mode with wakeup at<br>400Hz rate to refresh LCD, bus,<br>clock = 3MHz, Vddio = Vdda = 3V, 8<br>commons, 16 segments, 1/5 duty<br>cycle, 40 Hz frame rate, no glass<br>connected | -   | 81                     | -    | μΑ    |

| I <sub>CC_SEG</sub> | Current per segment driver                                                          | Strong drive mode                                                                                                                                                                             | -   | 260                    | -    | μA    |

| V <sub>BIAS</sub>   | LCD bias range (V <sub>BIAS</sub> refers to the main output voltage(V0) of LCD DAC) | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                   | 2   | -                      | 5    | V     |

|                     | LCD bias step size                                                                  | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                   | -   | 9.1 × V <sub>DDA</sub> | _    | mV    |

|                     | LCD capacitance per<br>segment/common driver                                        | Drivers may be combined                                                                                                                                                                       | -   | 500                    | 5000 | pF    |

|                     | Maximum segment DC offset                                                           | Vdda $\ge$ 3V and Vdda $\ge$ Vbias                                                                                                                                                            | -   | -                      | 20   | mV    |

| I <sub>OUT</sub>    | Output drive current per segment driver)                                            | V <sub>DDIO</sub> = 5.5V, strong drive mode                                                                                                                                                   | 355 | -                      | 710  | μA    |

# Table 11-31. LCD Direct Drive AC Specifications<sup>[54]</sup>

| Parameter        | Description    | Conditions | Min | Тур | Max | Units |

|------------------|----------------|------------|-----|-----|-----|-------|

| f <sub>LCD</sub> | LCD frame rate |            | 10  | 50  | 150 | Hz    |

<sup>54.</sup> Based on device characterization (Not production tested).

# 11.6 Digital Peripherals

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

# 11.6.1 Timer

The following specifications apply to the Timer/Counter/PWM peripheral in timer mode. Timers can also be implemented in UDBs; for more information, see the Timer component datasheet in PSoC Creator.

# Table 11-32. Timer DC Specifications<sup>[55]</sup>

| Parameter | Description               | Conditions                                    | Min | Тур | Max | Units |

|-----------|---------------------------|-----------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit timer, at listed input clock frequency | -   | _   | _   | μA    |

|           | 3 MHz                     |                                               | -   | 15  | _   | μA    |

|           | 12 MHz                    |                                               | -   | 60  | -   | μA    |

|           | 48 MHz                    |                                               | -   | 260 | -   | μA    |

|           | 80 MHz                    |                                               | -   | 360 | _   | μA    |

# Table 11-33. Timer AC Specifications<sup>[55]</sup>

| Parameter | Description                                    | Conditions | Min | Тур | Max   | Units |

|-----------|------------------------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency                            |            | DC  | -   | 80.01 | MHz   |

|           | Capture pulse width (Internal) <sup>[56]</sup> |            | 15  | _   | _     | ns    |

|           | Capture pulse width (external)                 |            | 30  | -   | -     | ns    |

|           | Timer resolution <sup>[56]</sup>               |            | 15  | -   | -     | ns    |

|           | Enable pulse width <sup>[56]</sup>             |            | 15  | _   | _     | ns    |

|           | Enable pulse width (external)                  |            | 30  | -   | -     | ns    |

|           | Reset pulse width <sup>[56]</sup>              |            | 15  | -   | -     | ns    |

|           | Reset pulse width (external)                   |            | 30  | -   | -     | ns    |

## 11.6.2 Counter

The following specifications apply to the Timer/Counter/PWM peripheral, in counter mode. Counters can also be implemented in UDBs; for more information, see the Counter component datasheet in PSoC Creator.

# Table 11-34. Counter DC Specifications<sup>[55]</sup>

| Parameter | Description               | Conditions                                      | Min | Тур | Max | Units |

|-----------|---------------------------|-------------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit counter, at listed input clock frequency | -   | -   | -   | μA    |

|           | 3 MHz                     |                                                 | -   | 15  | _   | μA    |

|           | 12 MHz                    |                                                 | -   | 60  | -   | μA    |

|           | 48 MHz                    |                                                 | -   | 260 | -   | μA    |

|           | 80 MHz                    |                                                 | -   | 360 | -   | μA    |

# Table 11-35. Counter AC Specifications<sup>[55]</sup>

| Parameter | Description                   | Conditions | Min | Тур | Max   | Units |

|-----------|-------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency           |            | DC  | -   | 80.01 | MHz   |

|           | Capture pulse <sup>[56]</sup> |            | 15  | -   | -     | ns    |

|           | Resolution <sup>[56]</sup>    |            | 15  | -   | -     | ns    |

|           | Pulse width <sup>[56]</sup>   |            | 15  | -   | -     | ns    |

|           | Pulse width (external)        |            | 30  |     |       | ns    |

Notes

56. For correct operation, the minimum Timer/Counter/PWM input pulse width is the period of bus clock.

<sup>55.</sup> Based on device characterization (Not production tested).

# **Document History Page**

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|---------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 3825653 | MKEA               | 12/07/2012         | Datasheet for new CY8C52LP family.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| *A       | 3897878 | MKEA               | 02/07/2013         | Removed Preliminary status<br>Updated characterization footnotes in Electrical Specifications.<br>Updated conditions for SAR ADC INL and DNL specifications in Table 11-19<br>Updated Table 11-63 (ILO AC Specifications).<br>Changed "UDB Configuration" to "UDB Working Registers" in Table 5-5.<br>Removed references to CAN.<br>Updated VREF accuracy.<br>Updated INL VIDAC spec.<br>Removed drift specs from Voltage Reference Specifications.                                                                                                                                                                                                                                                                                                                                                                                   |

| *В       | 3902085 | MKEA               | 02/12/2013         | Changed Hibernate wakeup time from 125 $\mu s$ to 200 $\mu s$ in Table 6-3 and Table 11-3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| *C       | 4114902 | MKEA               | 09/30/2013         | Added information about 1 KB cache in Features.<br>Added warning on reset devices in the EEPROM section.<br>Added DBGEN field in Table 5-3.<br>Deleted statement about repeat start from the $I^2C$ section.<br>Removed T <sub>STG</sub> spec from Table 11-1 and added a note clarifying the<br>maximum storage temperature range.<br>Updated chip Idd, regulator, SAR ADC, IDAC, and VDAC graphs.<br>Added min and max values for the Regulator Output Capacitor parameter.<br>Updated C <sub>IN</sub> specs in GPIO DC Specifications and SIO DC Specifications.<br>Updated rise and fall time specs in Fast Strong mode in Table 11-9, and<br>deleted related graphs.<br>Updated Voltage Reference Specifications and IMO AC Specifications.<br>Updated 100-TQFP package diagram.<br>Added Appendix for CSP package (preliminary. |

| *D       | 4225729 | MKEA               | 12/20/2013         | Added SIO Comparator Specifications.<br>Changed T <sub>HIBERNATE</sub> max value from 200 to 150.<br>Updated CSP package and ordering information.<br>Added 80 MHz parts in Table 12-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *E       | 4386988 | MKEA               | 05/22/2014         | Updated General Description and Features.<br>Added More Information and PSoC Creator sections.<br>Updated JTAG IDs in Ordering Information.<br>Updated 100-TQFP package diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| *F       | 4587100 | MKEA               | 12/08/2014         | Added link to AN72845 in Note 3.<br>Updated interrupt priority numbers in Section 4.4.<br>Updated Section 5.4 to clarify the factory default values of EEPROM.<br>Corrected ECCEN settings in Table 5-3.<br>Updated Section 6.1.1 and Section 6.1.2.<br>Added a note below Figure 6-4.<br>Updated Figure 6-12.<br>Changed 'Control Store RAM' to 'Dynamic Configuration RAM' in Figure 7-4<br>and changed Section 7.2.2.2 heading to 'Dynamic Configuration RAM'.<br>Updated Section 7.7.                                                                                                                                                                                                                                                                                                                                             |

# Document History Page (continued)

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|---------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *G       | 4698847 | MKEA / GJV         | 03/24/2015         | Updated System Integration:<br>Updated Power System:<br>Updated Boost Converter:<br>Updated entire section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |         |                    |                    | Updated Electrical Specifications:<br>Updated Power Regulators:<br>Updated Inductive Boost Regulator:<br>Updated Table 11-6:<br>Updated details of V <sub>BAT</sub> , I <sub>OUT</sub> , V <sub>OUT</sub> , Reg <sub>LOAD</sub> , Reg <sub>LINE</sub> parameters.<br>Removed V <sub>OUT</sub> : V <sub>BAT</sub> parameter and its details.<br>Removed Table "Inductive Boost Regulator AC Specifications".<br>Updated Table 11-7:<br>Updated details of L <sub>BOOST</sub> , C <sub>BOOST</sub> parameters.<br>Added C <sub>BAT</sub> parameter and its details.<br>Added Figure 11-8, Figure 11-9, Figure 11-10, Figure 11-11, Figure 11-12,<br>Figure 11-13, Figure 11-14.<br>Removed Figure "Efficiency vs I <sub>OUT</sub> V <sub>BOOST</sub> = 3.3 V, L <sub>BOOST</sub> = 10 µH".<br>Removed Figure "Efficiency vs I <sub>OUT</sub> V <sub>BOOST</sub> = 3.3 V, L <sub>BOOST</sub> = 22 µH". |

|          |         |                    |                    | Updated Appendix: CSP Package Summary:<br>Updated Packaging:<br>spec 001-88034 – Changed revision from ** to *A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| *H       | 4839323 | МКЕА               | 07/15/2015         | Added reference to code examples in More Information.<br>Updated typ value of $T_{WRITE}$ from 2 to 10 in EEPROM AC specs table.<br>Changed "Device supply for USB operation" to "Device supply (V <sub>DDD</sub> ) for<br>USB operation" in USB DC Specifications.<br>Clarified power supply sequencing and margin for V <sub>DDA</sub> and V <sub>DDD</sub> .<br>Updated Serial Wire Debug Interface with limitations of debugging on Por<br>15.<br>Updated Delta-sigma ADC DC Specifications                                                                                                                                                                                                                                                                                                                                                                                                     |

| *1       | 5030641 | МКЕА               | 11/30/2015         | Added Table 2-1.<br>Removed the configurable XRES information.<br>Updated Section 5.6<br>Updated Section 6.3.1.1.<br>Updated values for DSI Fmax, Fgpioin max, and Fsioin max.<br>Corrected the web link for the PSoC 5 Device Programming Specifications<br>in Section 9.<br>Updated CSP Package Bootloader section.<br>Added MHzECO DC Specifications.<br>Updated 99-WLCSP and 100-pin TQFP package drawings.<br>Added a footnote reference for the "CY8C5287AXI-LP095" part in Table 12-<br>clarifying that it has 256 KB flash.<br>Added the CY8C5667AXQ-LP040 part in Table 12-1.                                                                                                                                                                                                                                                                                                              |