Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 67MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                               |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                            |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 256KB (256K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 64K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                 |

| Data Converters            | A/D 1x12b; D/A 1x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 68-VFQFN Exposed Pad                                                         |

| Supplier Device Package    | 68-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c5268lti-lp030 |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

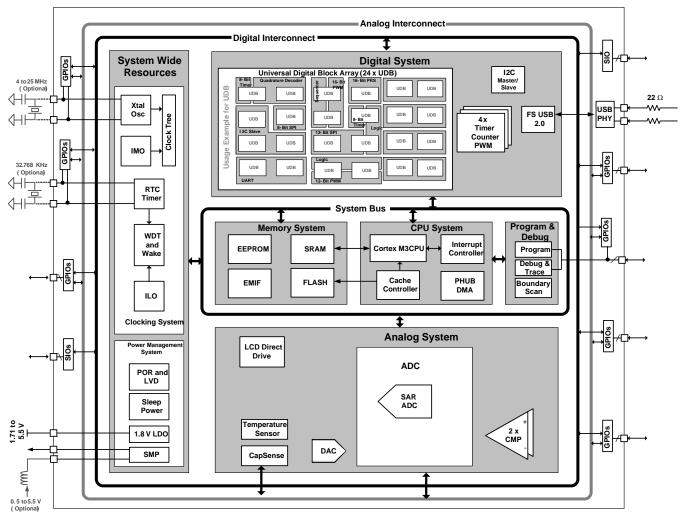

# 1. Architectural Overview

Introducing the CY8C52LP family of ultra low power, flash Programmable System-on-Chip (PSoC) devices, part of a scalable 8-bit PSoC 3 and 32-bit PSoC 5LP platform. The CY8C52LP family provides configurable blocks of analog, digital, and interconnect circuitry around a CPU subsystem. The combination of a CPU with a flexible analog subsystem, digital subsystem, routing, and I/O enables a high level of integration in a wide variety of consumer, industrial, and medical applications.

Figure 1-1 illustrates the major components of the CY8C52LP family. They are:

- ARM Cortex-M3 CPU subsystem

- Nonvolatile subsystem

- Programming, debug, and test subsystem

- Inputs and outputs

- Clocking

- Power

- Digital subsystem

- Analog subsystem

PSoC's digital subsystem provides half of its unique configurability. It connects a digital signal from any peripheral to any pin through the digital system interconnect (DSI). It also provides functional flexibility through an array of small, fast, low power UDBs. PSoC Creator provides a library of pre-built and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. You can also easily create a digital circuit using boolean primitives by means of graphical design entry. Each UDB contains programmable array logic (PAL)/programmable logic device (PLD) functionality, together with a small state machine engine to support a wide variety of peripherals.

The details of the PSoC power modes are covered in the "Power System" section on page 26 of this datasheet.

PSoC uses JTAG (4-wire) or SWD (2-wire) interfaces for programming, debug, and test. Using these standard interfaces you can debug or program the PSoC with a variety of hardware solutions from Cypress or third party vendors. The Cortex-M3 debug and trace modules include FPB, DWT, ETM, and ITM. These modules have many features to help solve difficult debug and trace problems. Details of the programming, test, and debugging interfaces are discussed in the "Programming, Debug Interfaces, Resources" section on page 55 of this datasheet.

## 2. Pinouts

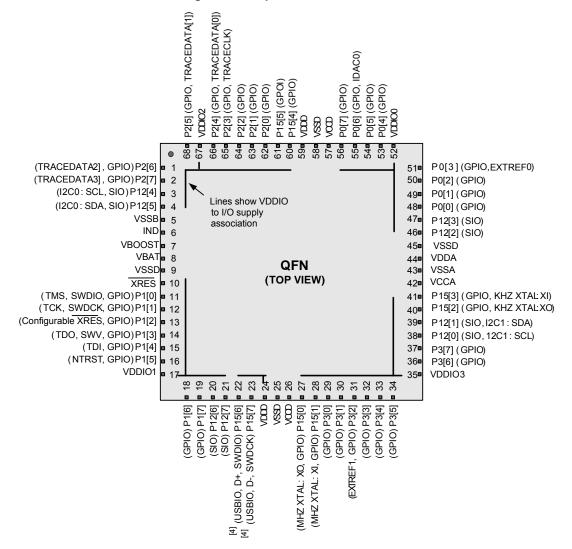

Each VDDIO pin powers a specific set of I/O pins. (The USBIOs are powered from VDDD.) Using the VDDIO pins, a single PSoC can support multiple voltage levels, reducing the need for off-chip level shifters. The black lines drawn on the pinout diagrams in Figure 2-3 and Figure 2-4, as well as Table 2-1, show the pins that are powered by each VDDIO.

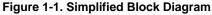

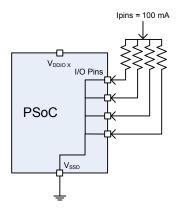

Each VDDIO may source up to 100 mA total to its associated I/O pins, as shown in Figure 2-1.

## Figure 2-1. VDDIO Current Limit

Conversely, for the 100-pin and 68-pin devices, the set of I/O pins associated with any VDDIO may sink up to 100 mA total, as shown in Figure 2-2.

#### Figure 2-2. I/O Pins Current Limit

#### Figure 2-3. 68-pin QFN Part Pinout<sup>[3]</sup>

Notes

The center pad on the QFN package should be connected to digital ground (VSSD) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal. For more information, see AN72845, Design Guidelines for QFN Devices. 3.

4. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

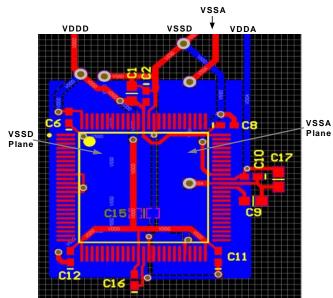

#### Figure 2-6. Example PCB Layout for 100-pin TQFP Part for Optimal Analog Performance

## 3. Pin Descriptions

**IDAC0.** Low resistance output pin for high IDAC.

**Extref0, Extref1.** External reference input to the analog system. **SAR0 EXTREF, SAR1 EXTREF.** External references for SAR ADCs

**GPIO.** General purpose I/O pin provides interfaces to the CPU, digital peripherals, analog peripherals, interrupts, LCD segment drive, and CapSense<sup>[6]</sup>.

**I2C0: SCL, I2C1: SCL.**  $I^2C$  SCL line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SCL if wake from sleep is not required.

**I2C0: SDA, I2C1: SDA.**  $I^2C$  SDA line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SDA if wake from sleep is not required.

Ind. Inductor connection to boost pump.

kHz XTAL: Xo, kHz XTAL: Xi. 32.768-kHz crystal oscillator pin.

**MHz XTAL: Xo, MHz XTAL: Xi.** 4 to 25-MHz crystal oscillator pin.

**nTRST.** Optional JTAG Test Reset programming and debug port connection to reset the JTAG connection.

**SIO.** Special I/O provides interfaces to the CPU, digital peripherals and interrupts with a programmable high threshold voltage, analog comparator, high sink current, and high impedance state when the device is unpowered.

**SWDCK.** Serial wire debug clock programming and debug port connection.

**SWDIO.** Serial wire debug Input and output programming and debug port connection.

Notes

6. GPIOs with opamp outputs are not recommended for use with CapSense.

**TCK.** JTAG test clock programming and debug port connection.

**TDI.** JTAG test data In programming and debug port connection.

**TDO.** JTAG test data out programming and debug port connection.

**TMS.** JTAG test mode select programming and debug port connection.

**TRACECLK.** Cortex-M3 TRACEPORT connection, clocks TRACEDATA pins.

**TRACEDATA[3:0].** Cortex-M3 TRACEPORT connections, output data.

SWV. Single wire viewer output.

**USBIO**, **D+.** Provides D+ connection directly to a USB 2.0 bus. May be used as a digital I/O pin; it is powered from VDDD instead of from a  $V_{DDIO}$ . Pins are Do Not Use (DNU) on devices without USB.

**USBIO**, **D-.** Provides D- connection directly to a USB 2.0 bus. May be used as a digital I/O pin; it is powered from  $V_{DDD}$  instead of from a  $V_{DDIO}$ . Pins are Do Not Use (DNU) on devices without USB.

**VBOOST.** Power sense connection to boost pump.

VBAT. Battery supply to boost pump.

VCCA. Output of the analog core regulator or the input to the analog core. Requires a 1uF capacitor to VSSA. The regulator output is not designed to drive external circuits. Note that if you use the device with an external core regulator (externally regulated mode), the voltage applied to this pin must not exceed the allowable range of 1.71 V to 1.89 V. When using the internal core regulator, (internally regulated mode, the default), do not tie any power to this pin. For details see "Power System" section on page 26.

## 5.5 Nonvolatile Latches (NVLs)

PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-3.

| Table 5-2. | Device | Configuration | NVL | Register Map |

|------------|--------|---------------|-----|--------------|

|------------|--------|---------------|-----|--------------|

| Register Address | 7            | 6         | 5                         | 4 | 3               | 2        | 1            | 0        |                                |  |                                   |  |                     |  |              |  |              |  |      |          |

|------------------|--------------|-----------|---------------------------|---|-----------------|----------|--------------|----------|--------------------------------|--|-----------------------------------|--|---------------------|--|--------------|--|--------------|--|------|----------|

| 0x00             | PRT3RDM[1:0] |           | PRT2RDM[1:0] PRT1RDM[1:0] |   | DM[1:0] PRT2RDM |          | PRT2RDM[1:0] |          | 1:0] PRT2RDM[1:0] PRT1RDM[1:0] |  | DM[1:0] PRT2RDM[1:0] PRT1RDM[1:0] |  | M[1:0] PRT2RDM[1:0] |  | PRT1RDM[1:0] |  | PRT1RDM[1:0] |  | PRT0 | RDM[1:0] |

| 0x01             | PRT12R       | DM[1:0]   | PRT6RDM[1:0] PRT5RDM[1:0] |   | PRT4            | RDM[1:0] |              |          |                                |  |                                   |  |                     |  |              |  |              |  |      |          |

| 0x02             | XRESMEN      | DBGEN     |                           |   |                 | PRT18    | 5RDM[1:0]    |          |                                |  |                                   |  |                     |  |              |  |              |  |      |          |

| 0x03             |              | DIG_PHS_I | DLY[3:0] ECCEN DPS        |   | DLY[3:0]        |          | [1:0]        | CFGSPEED |                                |  |                                   |  |                     |  |              |  |              |  |      |          |

The details for individual fields and their factory default settings are shown in Table 5-3:.

#### Table 5-3. Fields and Factory Default Settings

| Field            | Description                                                                                                                            | Settings                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PRTxRDM[1:0]     |                                                                                                                                        | 00b (default) - high impedance analog<br>01b - high impedance digital<br>10b - resistive pull up<br>11b - resistive pull down |

| XRESMEN          | Controls whether pin P1[2] is used as a GPIO or as an external reset. P1[2] is generally used as a GPIO, and not as an external reset. | 0 (default) - GPIO<br>1 - external reset                                                                                      |

| DBGEN            | Debug Enable allows access to the debug system, for third-party programmers.                                                           | 0 - access disabled<br>1 (default) - access enabled                                                                           |

| CFGSPEED         | Controls the speed of the IMO-based clock during the device boot process, for faster boot or low-power operation.                      | 0 (default) - 12-MHz IMO<br>1 - 48-MHz IMO                                                                                    |

| DPS[1:0]         | Controls the usage of various P1 pins as a debug port.<br>See "Programming, Debug Interfaces, Resources" on<br>page 55.                | 00b - 5-wire JTAG<br>01b (default) - 4-wire JTAG<br>10b - SWD<br>11b - debug ports disabled                                   |

| ECCEN            | Controls whether ECC flash is used for ECC or for general configuration and data storage. See "Flash Program Memory" on page 19.       | 0 - ECC disabled<br>1 (default) - ECC enabled                                                                                 |

| DIG_PHS_DLY[3:0] | Selects the digital clock phase delay.                                                                                                 | See the TRM for details.                                                                                                      |

Although PSoC Creator provides support for modifying the device configuration NVLs, the number of NVL erase/write cycles is limited – see "Nonvolatile Latches (NVL)" on page 94.

Four 16-bit clock dividers generate clocks for the analog system components that require clocking, such as the ADC. The analog clock dividers include skew control to ensure that critical analog events do not occur simultaneously with digital switching events. This is done to reduce analog system noise.

Each clock divider consists of an 8-input multiplexer, a 16-bit clock divider (divide by 2 and higher) that generates ~50% duty cycle clocks, system clock resynchronization logic, and deglitch logic. The outputs from each digital clock tree can be routed into the digital system interconnect and then brought back into the clock system as an input, allowing clock chaining of up to 32 bits.

#### 6.1.4 USB Clock Domain

The USB clock domain is unique in that it operates largely asynchronously from the main clock network. The USB logic contains a synchronous bus interface to the chip, while running on an asynchronous clock to process USB data. The USB logic requires a 48 MHz frequency. This frequency is generated from the doubled value of 24 MHz from internal oscillator, DSI signal, or crystal oscillator.

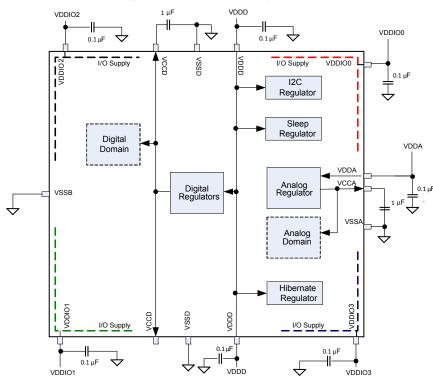

### 6.2 Power System

The power system consists of separate analog, digital, and I/O supply pins, labeled VDDA, VDDD, and VDDIOX, respectively. It also includes two internal 1.8 V regulators that provide the digital (VCCD) and analog (VCCA) supplies for the internal core logic. The output pins of the regulators (VCCD and VCCA) and the VDDIO pins must have capacitors connected as shown in Figure 6-4. The two VCCD pins must be shorted together, with as short a trace as possible, and connected to a 1  $\mu$ F ±10% X5R capacitor. The power system also contains a sleep regulator, an I<sup>2</sup>C regulator, and a hibernate regulator.

## Figure 6-4. PSoC Power System

#### Notes

- The two V<sub>CCD</sub> pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-6.

- You can power the device in internally regulated mode, where the voltage applied to the V<sub>DDx</sub> pins is as high as 5.5 V, and the internal regulators provide the core voltages. In this mode, do not apply power to the V<sub>CCx</sub> pins, and do not tie the V<sub>DDx</sub> pins to the V<sub>CCx</sub> pins.

- You can also power the device in externally regulated mode, that is, by directly powering the V<sub>CCD</sub> and V<sub>CCA</sub> pins. In this configuration, the V<sub>DDD</sub> pins should be shorted to the V<sub>CCD</sub> pins and the V<sub>DDA</sub> pin should be shorted to the V<sub>CCA</sub> pin. The allowed supply range in this configuration is 1.71 V to 1.89 V. After power up in this configuration, the internal regulators are on by default, and should be disabled to reduce power consumption.

- It is good practice to check the datasheets for your bypass capacitors, specifically the working voltage and the DC bias specifications. With some capacitors, the actual capacitance can decrease considerably when the DC bias (V<sub>DDX</sub> or V<sub>CCX</sub> in Figure 6-4) is a significant percentage of the rated working voltage.

consumption of the boost circuit. Only minimal power is provided, typically < 5  $\mu$ A to power the PSoC device in Sleep mode. The boost typically draws 250  $\mu$ A in active mode and 25  $\mu$ A in standby mode. The boost operating modes must be used in conjunction with chip power modes to minimize total power consumption. Table 6-4 lists the boost power modes available in different chip power modes.

| Table 6-4. | Chip and | Boost | Power | Modes | Compatibility | 1 |

|------------|----------|-------|-------|-------|---------------|---|

|------------|----------|-------|-------|-------|---------------|---|

| Chip Power Modes                     | Boost Power Modes                                                                                                                                                                        |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip-active or alternate active mode | Boost must be operated in its active mode.                                                                                                                                               |

| Chip-sleep mode                      | Boost can be operated in either active<br>or standby mode. In boost standby<br>mode, the chip must wake up periodi-<br>cally for boost active-mode refresh.                              |

| Chip-hibernate mode                  | Boost can be operated in its active<br>mode. However, it is recommended not<br>to use the boost in chip hibernate mode<br>due to the higher current consumption<br>in boost active mode. |

### 6.2.2.1 Boost Firmware Requirements

To ensure boost inrush current is within specification at startup, the **Enable Fast IMO During Startup** value must be unchecked in the PSoC Creator IDE. The **Enable Fast IMO During Startup** option is found in PSoC Creator in the design wide resources (cydwr) file **System** tab. Un-checking this option configures the device to run at 12 MHz vs 48 MHz during startup while configuring the device. The slower clock speed results in reduced current draw through the boost circuit.

#### 6.2.2.2 Boost Design Process

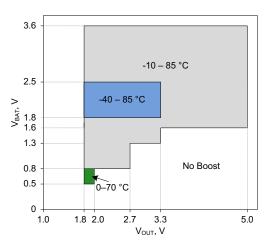

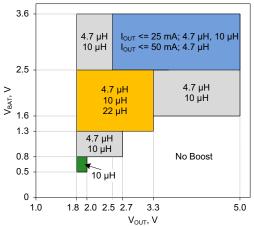

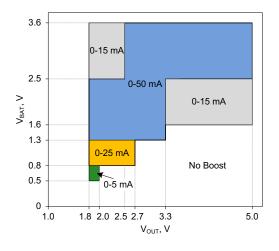

Correct operation of the boost converter requires specific component values determined for each designs unique operating conditions. The  $C_{BAT}$  capacitor, Inductor, Schottky diode, and  $C_{BOOST}$  capacitor components are required with the values specified in the electrical specifications, Table 11-7 on page 66. The only variable component value is the inductor  $L_{BOOST}$  which is primarily sized for correct operation of the boost across operating conditions and secondarily for efficiency. Additional operating region constraints exist for  $V_{OUT}$ ,  $V_{BAT}$ ,  $I_{OUT}$ , and  $T_A$ .

The following steps must be followed to determine boost converter operating parameters and  ${\rm L}_{\rm BOOST}$  value.

- 1. Choose desired  $V_{BAT}$ ,  $V_{OUT}$ ,  $T_A$ , and  $I_{OUT}$  operating condition ranges for the application.

- 2. Determine if  $V_{BAT}$  and  $V_{OUT}$  ranges fit the boost operating range based on the  $T_A$  range over  $V_{BAT}$  and  $V_{OUT}$  chart,

Figure 11-8 on page 66. If the operating ranges are not met, modify the operating conditions or use an external boost regulator.

- 3. Determine if the desired ambient temperature  $(T_A)$  range fits the ambient temperature operating range based on the  $T_A$ **range over V<sub>BAT</sub> and V<sub>OUT</sub>** chart, Figure 11-8 on page 66. If the temperature range is not met, modify the operating conditions and return to step 2, or use an external boost regulator.

- 4. Determine if the desired output current ( $I_{OUT}$ ) range fits the output current operating range based on the  $I_{OUT}$  range over  $V_{BAT}$  and  $V_{OUT}$  chart, Figure 11-9 on page 66. If the output current range is not met, modify the operating conditions and return to step 2, or use an external boost regulator.

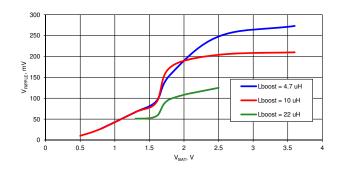

- Find the allowed inductor values based on the L<sub>BOOST</sub> values over V<sub>BAT</sub> and V<sub>OUT</sub> chart, Figure 11-10 on page 66.

- 6. Based on the allowed inductor values, inductor dimensions, inductor cost, boost efficiency, and  $V_{RIPPLE}$  choose the optimum inductor value for the system. Boost efficiency and  $V_{RIPPLE}$  typical values are provided in the **Efficiency vs V<sub>BAT</sub>** and **V<sub>RIPPLE</sub> vs V<sub>BAT</sub>** charts, Figure 11-11 on page 67 through Figure 11-14 on page 67. In general, if high efficiency and low  $V_{RIPPLE}$  are most important, then the highest allowed inductor value should be used. If low inductor cost or small inductor size are most important, then one of the smaller allowed inductor (s) efficiency,  $V_{RIPPLE}$ , cost or dimensions are not acceptable for the application than an external boost regulator should be used.

## 6.3 Reset

CY8C52LP has multiple internal and external reset sources available. The reset sources are:

- Power source monitoring: The analog and digital power voltages, VDDA, VDDD, VCCA, and VCCD are monitored in several different modes during power up, active mode, and sleep mode (buzzing). If any of the voltages goes outside predetermined ranges then a reset is generated. The monitors are programmable to generate an interrupt to the processor under certain conditions before reaching the reset thresholds.

- External: The device can be reset from an external source by pulling the reset pin (XRES) low. The XRES pin includes an internal pull up to VDDIO1. VDDD, VDDA, and VDDIO1 must all have voltage applied before the part comes out of reset.

- Watchdog timer: A watchdog timer monitors the execution of instructions by the processor. If the watchdog timer is not reset by firmware within a certain period of time, the watchdog timer generates a reset.

- Software: The device can be reset under program control.

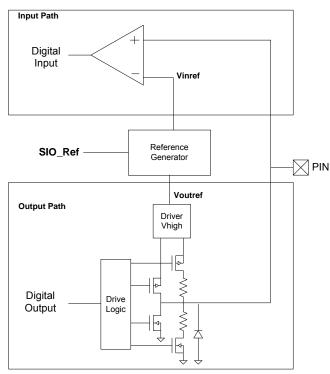

## Figure 6-13. SIO Reference for Input and Output

## 6.4.13 SIO as Comparator

This section applies only to SIO pins. The adjustable input level feature of the SIOs as explained in the Adjustable Input Level section can be used to construct a comparator. The threshold for the comparator is provided by the SIO's reference generator. The reference generator has the option to set the analog signal routed through the analog global line as threshold for the comparator. Note that a pair of SIO pins share the same threshold.

The digital input path in Figure 6-10 on page 34 illustrates this functionality. In the figure, 'Reference level' is the analog signal routed through the analog global. The hysteresis feature can also be enabled for the input buffer of the SIO, which increases noise immunity for the comparator.

#### 6.4.14 Hot Swap

This section applies only to SIO pins. SIO pins support 'hot swap' capability to plug into an application without loading the signals that are connected to the SIO pins even when no power is applied to the PSoC device. This allows the unpowered PSoC to maintain a high impedance load to the external device while also preventing the PSoC from being powered through a SIO pin's protection diode.

Powering the device up or down while connected to an operational I2C bus may cause transient states on the SIO pins. The overall I2C bus design should take this into account.

## 6.4.15 Over Voltage Tolerance

All I/O pins provide an over voltage tolerance feature at any operating VDD.

- There are no current limitations for the SIO pins as they present a high impedance load to the external circuit.

- The GPIO pins must be limited to 100 µA using a current limiting resistor. GPIO pins clamp the pin voltage to approximately one diode above the VDDIO supply.

- In case of a GPIO pin configured for analog input/output, the analog voltage on the pin must not exceed the VDDIO supply voltage to which the GPIO belongs.

A common application for this feature is connection to a bus such as  $I^2C$  where different devices are running from different supply voltages. In the  $I^2C$  case, the PSoC chip is configured into the Open Drain, Drives Low mode for the SIO pin. This allows an external pull up to pull the  $I^2C$  bus voltage above the PSoC pin supply. For example, the PSoC chip could operate at 1.8 V, and an external device could run from 5 V. Note that the SIO pin's VIH and VIL levels are determined by the associated VDDIO supply pin.

The SIO pin must be in one of the following modes: 0 (high impedance analog), 1 (high impedance digital), or 4 (open drain drives low). See Figure 6-12 for details. Absolute maximum ratings for the device must be observed for all I/O pins.

#### 6.4.16 Reset Configuration

While reset is active all I/Os are reset to and held in the High Impedance Analog state. After reset is released, the state can be reprogrammed on a port-by-port basis to pull down or pull up. To ensure correct reset operation, the port reset configuration data is stored in special nonvolatile registers. The stored reset data is automatically transferred to the port reset configuration registers at reset release.

#### 6.4.17 Low Power Functionality

In all low power modes the I/O pins retain their state until the part is awakened and changed or reset. To awaken the part, use a pin interrupt, because the port interrupt logic continues to function in all low power modes.

#### 6.4.18 Special Pin Functionality

Some pins on the device include additional special functionality in addition to their GPIO or SIO functionality. The specific special function pins are listed in "Pinouts" on page 6. The special features are:

#### Digital

- 4- to 25-MHz crystal oscillator

- □ 32.768-kHz crystal oscillator

- $\square$  Wake from sleep on I<sup>2</sup>C address match. Any pin can be used for I<sup>2</sup>C if wake from sleep is not required.

- □ JTAG interface pins

- □ SWD interface pins

- □ SWV interface pins

- TRACEPORT interface pins

- External reset

- Analog

- High current IDAC output

External reference inputs

## 6.4.19 JTAG Boundary Scan

The device supports standard JTAG boundary scan chains on all pins for board level test.

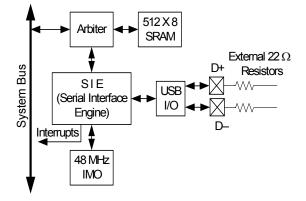

## 7.5 USB

PSoC includes a dedicated Full-Speed (12 Mbps) USB 2.0 transceiver supporting all four USB transfer types: control, interrupt, bulk, and isochronous. PSoC Creator provides full configuration support. USB interfaces to hosts through two dedicated USBIO pins, which are detailed in the "I/O System and Routing" section on page 32.

USB includes the following features:

- Eight unidirectional data endpoints

- One bidirectional control endpoint 0 (EP0)

- Shared 512-byte buffer for the eight data endpoints

- Dedicated 8-byte buffer for EP0

- Three memory modes

- Manual Memory Management with No DMA Access

- Manual Memory Management with Manual DMA Access

Automatic Memory Management with Automatic DMA Access

- Internal 3.3 V regulator for transceiver

- Internal 48 MHz oscillator that auto locks to USB bus clock, requiring no external crystal for USB (USB equipped parts only)

- Interrupts on bus and each endpoint event, with device wakeup

- USB Reset, Suspend, and Resume operations

- Bus powered and self powered modes

#### Figure 7-14. USB

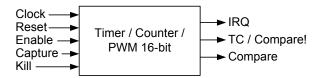

## 7.6 Timers, Counters, and PWMs

The Timer/Counter/PWM peripheral is a 16-bit dedicated peripheral providing three of the most common embedded

peripheral features. As almost all embedded systems use some combination of timers, counters, and PWMs. Four of them have been included on this PSoC device family. Additional and more advanced functionality timers, counters, and PWMs can also be instantiated in Universal Digital Blocks (UDBs) as required. PSoC Creator allows you to choose the timer, counter, and PWM features that they require. The tool set utilizes the most optimal resources available.

The Timer/Counter/PWM peripheral can select from multiple clock sources, with input and output signals connected through the DSI routing. DSI routing allows input and output connections to any device pin and any internal digital signal accessible through the DSI. Each of the four instances has a compare output, terminal count output (optional complementary compare output), and programmable interrupt request line. The Timer/Counter/PWMs are configurable as free running, one shot, or Enable input controlled. The peripheral has timer reset and capture inputs, and a kill input for control of the comparator outputs. The peripheral supports full 16-bit capture.

Timer/Counter/PWM features include:

- 16-bit timer/counter/PWM (down count only)

- Selectable clock source

- PWM comparator (configurable for LT, LTE, EQ, GTE, GT)

- Period reload on start, reset, and terminal count

- Interrupt on terminal count, compare true, or capture

- Dynamic counter reads

- Timer capture mode

- Count while enable signal is asserted mode

- Free run mode

- One Shot mode (stop at end of period)

- Complementary PWM outputs with deadband

- PWM output kill

#### Figure 7-15. Timer/Counter/PWM

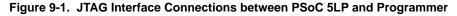

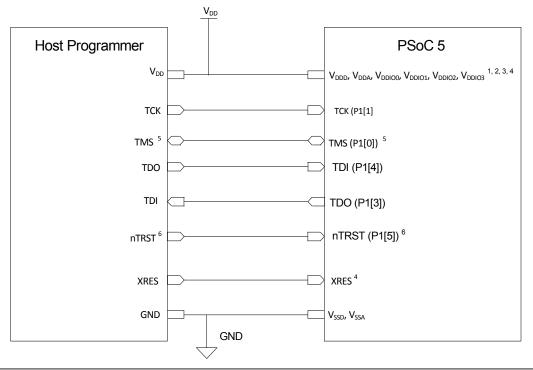

## 9.1 JTAG Interface

The IEEE 1149.1 compliant JTAG interface exists on four or five pins (the nTRST pin is optional). The JTAG clock frequency can be up to 12 MHz, or 1/3 of the CPU clock frequency for 8 and 16-bit transfers, or 1/5 of the CPU clock frequency for 32-bit

transfers, whichever is least. By default, the JTAG pins are enabled on new devices but the JTAG interface can be disabled, allowing these pins to be used as General Purpose I/O (GPIO) instead. The JTAG interface is used for programming the flash memory, debugging, I/O scan chains, and JTAG device chaining.

- The voltage levels of Host Programmer and the PSoC 5 voltage domains involved in Programming should be same. The Port 1 JTAG pins and XRES pin are powered by  $V_{DDI01}$ . So,  $V_{DDI01}$  of PSoC 5 should be at same voltage level as host  $V_{DD}$ . Rest of PSoC 5 voltage domains ( $V_{DDD}$ ,  $V_{DDA}$ ,  $V_{DDI02}$ ,  $V_{DDI03}$ ) need not be at the same voltage level as host Programmer.

- <sup>2</sup> Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 5.

- <sup>3</sup> For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 5. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

- <sup>4</sup> For JTAG Programming, Device reset can also be done without connecting to the XRES pin or Power cycle mode by using the TMS,TCK,TDI, TDO pins of PSoC 5, and writing to a specific register. But this requires that the DPS setting in NVL is not equal to "Debug Ports Disabled".

- <sup>5</sup> By default, PSoC 5 is configured for 4-wire JTAG mode unless user changes the DPS setting. So the TMS pin is unidirectional. But if the DPS setting is changed to non-JTAG mode, the TMS pin in JTAG is bi-directional as the SWD Protocol has to be used for acquiring the PSoC 5 device initially. After switching from SWD to JTAG mode, the TMS pin will be uni-directional. In such a case, unidirectional buffer should not be used on TMS line.

- <sup>3</sup> nTRST JTAG pin (P1[5]) cannot be used to reset the JTAG TAP controllier during first time programming of PSoC 5 as the default setting is 4-wire JTAG (nTRST disabled). Use the TMS, TCK pins to do a reset of JTAG TAP controller.

# 11. Electrical Specifications

Specifications are valid for -40 °C  $\leq T_A \leq 85$  °C and  $T_J \leq 100$  °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. The unique flexibility of the PSoC UDBs and analog blocks enable many functions to be implemented in PSoC Creator components, see the component datasheets for full AC/DC specifications of individual functions. See the "Example Peripherals" section on page 39 for further explanation of PSoC Creator components.

## 11.1 Absolute Maximum Ratings

| Parameter                         | Description                                         | Conditions                                                                               | Min                    | Тур | Max                     | Units |

|-----------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------|------------------------|-----|-------------------------|-------|

| V <sub>DDA</sub>                  | Analog supply voltage relative to V <sub>SSA</sub>  |                                                                                          | -0.5                   | _   | 6                       | V     |

| V <sub>DDD</sub>                  | Digital supply voltage relative to V <sub>SSD</sub> |                                                                                          | -0.5                   | _   | 6                       | V     |

| V <sub>DDIO</sub>                 | I/O supply voltage relative to V <sub>SSD</sub>     |                                                                                          | -0.5                   | _   | 6                       | V     |

| V <sub>CCA</sub>                  | Direct analog core voltage input                    |                                                                                          | -0.5                   | _   | 1.95                    | V     |

| V <sub>CCD</sub>                  | Direct digital core voltage input                   |                                                                                          | -0.5                   | -   | 1.95                    | V     |

| V <sub>SSA</sub>                  | Analog ground voltage                               |                                                                                          | V <sub>SSD</sub> – 0.5 | _   | V <sub>SSD</sub> + 0.5  | V     |

| V <sub>GPIO</sub> <sup>[14]</sup> | DC input voltage on GPIO                            | Includes signals sourced by $V_{\mbox{\scriptsize DDA}}$ and routed internal to the pin. | V <sub>SSD</sub> – 0.5 | -   | V <sub>DDIO</sub> + 0.5 | V     |

| V <sub>SIO</sub>                  | DC input voltage on SIO                             | Output disabled                                                                          | $V_{SSD} - 0.5$        | _   | 7                       | V     |

|                                   |                                                     | Output enabled                                                                           | $V_{SSD} - 0.5$        | -   | 6                       | V     |

| V <sub>IND</sub>                  | Voltage at boost converter input                    |                                                                                          | 0.5                    | -   | 5.5                     | V     |

| V <sub>BAT</sub>                  | Boost converter supply                              |                                                                                          | $V_{SSD} - 0.5$        | -   | 5.5                     | V     |

| I <sub>VDDIO</sub>                | Current per V <sub>DDIO</sub> supply pin            |                                                                                          | -                      | -   | 100                     | mA    |

| I <sub>GPIO</sub>                 | GPIO current                                        |                                                                                          | -30                    | -   | 41                      | mA    |

| I <sub>SIO</sub>                  | SIO current                                         |                                                                                          | -49                    | _   | 28                      | mA    |

| I <sub>USBIO</sub>                | USBIO current                                       |                                                                                          | -56                    | -   | 59                      | mA    |

| LU                                | Latch up current <sup>[15]</sup>                    |                                                                                          | -140                   | _   | 140                     | mA    |

| ESD <sub>HBM</sub>                | Electrostatic discharge voltage                     | Human body model                                                                         | 2000                   | -   | -                       | V     |

| ESD <sub>CDM</sub>                | Electrostatic discharge voltage                     | Charge device model                                                                      | 500                    | -   | -                       | V     |

Notes

14. The V<sub>DDIO</sub> supply voltage must be greater than the maximum voltage on the associated GPIO pins. Maximum voltage on GPIO pin  $\leq$  V<sub>DDIO</sub>  $\leq$  V<sub>DD</sub>

15. Meets or exceeds JEDEC Spec EIA/JESD78 IC Latch-up Test.

<sup>13.</sup> Usage above the absolute maximum conditions listed in Table 11-1 may cause permanent damage to the device. Exposure to Absolute Maximum conditions for extended periods of time may affect device reliability. The Maximum Storage Temperature is 150 °C in compliance with JEDEC Standard JESD22-A103, High Temperature Storage Life. When used below Absolute Maximum conditions but above normal operating conditions, the device may not operate to specification.

| Parameter          | Description                                                                                      | Conditions     | Min  | Тур  | Max  | Units |

|--------------------|--------------------------------------------------------------------------------------------------|----------------|------|------|------|-------|

| L <sub>BOOST</sub> | Boost inductor                                                                                   | 4.7 μH nominal | 3.7  | 4.7  | 5.7  | μH    |

|                    |                                                                                                  | 10 μH nominal  | 8.0  | 10.0 | 12.0 | μH    |

|                    |                                                                                                  | 22 μH nominal  | 17.0 | 22.0 | 27.0 | μH    |

| C <sub>BOOST</sub> | Total capacitance sum of V <sub>DDD</sub> , V <sub>DDA</sub> , V <sub>DDI0</sub> <sup>[29]</sup> |                | 17.0 | 26.0 | 31.0 | μF    |

| C <sub>BAT</sub>   | Battery filter capacitor                                                                         |                | 17.0 | 22.0 | 27.0 | μF    |

| l <sub>F</sub>     | Schottky diode average forward current                                                           |                | 1.0  | _    | -    | A     |

| V <sub>R</sub>     | Schottky reverse voltage                                                                         |                | 20.0 | -    | -    | V     |

## Table 11-7. Recommended External Components for Boost Circuit

## Figure 11-8. T<sub>A</sub> range over $V_{BAT}\,$ and $V_{OUT}$

## Figure 11-10. L\_{BOOST} values over V\_{BAT} and V\_{OUT}

#### Note 29. Based on device characterization (Not production tested).

## Figure 11-9. $I_{OUT}$ range over $V_{BAT}$ and $V_{OUT}$

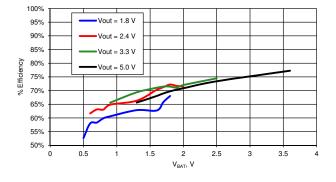

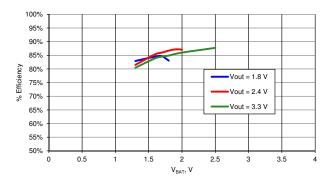

# Figure 11-11. Efficiency vs V<sub>BAT</sub>, $L_{BOOST}$ = 4.7 $\mu$ H <sup>[30]</sup>

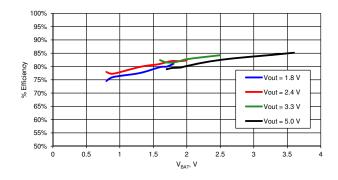

Figure 11-13. Efficiency vs V<sub>BAT</sub>,  $L_{BOOST}$  = 22 µH <sup>[30]</sup>

Figure 11-12. Efficiency vs  $V_{BAT}$ ,  $L_{BOOST}$  = 10  $\mu$ H <sup>[30]</sup>

Figure 11-14. V<sub>RIPPLE</sub> vs V<sub>BAT</sub> <sup>[30]</sup>

#### Note

30. Typical example. Actual values may vary depending on external component selection, PCB layout, and other design parameters.

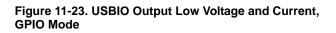

Figure 11-22. USBIO Output High Voltage and Current, GPIO Mode

CYPRESS

# Table 11-14. USBIO AC Specifications<sup>[38]</sup>

| Parameter | Description                                                 | Conditions                                           | Min        | Тур | Max           | Units |

|-----------|-------------------------------------------------------------|------------------------------------------------------|------------|-----|---------------|-------|

| Tdrate    | Full-speed data rate average bit rate                       |                                                      | 12 – 0.25% | 12  | 12 +<br>0.25% | MHz   |

| Tjr1      | Receiver data jitter tolerance to next transition           |                                                      | -8         | -   | 8             | ns    |

| Tjr2      | Receiver data jitter tolerance to pair transition           |                                                      | -5         | -   | 5             | ns    |

| Tdj1      | Driver differential jitter to next transition               |                                                      | -3.5       | -   | 3.5           | ns    |

| Tdj2      | Driver differential jitter to pair transition               |                                                      | -4         | -   | 4             | ns    |

| Tfdeop    | Source jitter for differential transition to SE0 transition |                                                      | -2         | -   | 5             | ns    |

| Tfeopt    | Source SE0 interval of EOP                                  |                                                      | 160        | -   | 175           | ns    |

| Tfeopr    | Receiver SE0 interval of EOP                                |                                                      | 82         | _   | _             | ns    |

| Tfst      | Width of SE0 interval during differential transition        |                                                      | -          | -   | 14            | ns    |

| Fgpio_out | GPIO mode output operating frequency                        | $3 \text{ V} \leq \text{V}_{DDD} \leq 5.5 \text{ V}$ | _          | -   | 20            | MHz   |

|           |                                                             | V <sub>DDD</sub> = 1.71 V                            | _          | -   | 6             | MHz   |

| Tr_gpio   | Rise time, GPIO mode, 10%/90% V <sub>DDD</sub>              | V <sub>DDD</sub> > 3 V, 25 pF load                   | _          | -   | 12            | ns    |

|           |                                                             | V <sub>DDD</sub> = 1.71 V, 25 pF load                | _          | -   | 40            | ns    |

| Tf_gpio   | Fall time, GPIO mode, 90%/10% V <sub>DDD</sub>              | V <sub>DDD</sub> > 3 V, 25 pF load                   | _          | -   | 12            | ns    |

|           |                                                             | V <sub>DDD</sub> = 1.71 V, 25 pF load                | -          | -   | 40            | ns    |

Note 38. Based on device characterization (Not production tested).

## Table 11-27. VDAC DC Specifications (continued)

| Parameter       | Description                         | Conditions | Min | Тур | Max  | Units   |

|-----------------|-------------------------------------|------------|-----|-----|------|---------|

|                 | Monotonicity                        |            | -   | -   | Yes  | -       |

| V <sub>OS</sub> | Zero scale error                    |            | -   | 0   | ±0.9 | LSB     |

| Eg              | Gain error                          | 1 V scale  | -   | -   | ±2.5 | %       |

|                 |                                     | 4 V scale  | -   | -   | ±2.5 | %       |

| TC_Eg           | Temperature coefficient, gain error | 1 V scale  | -   | -   | 0.03 | %FSR/°C |

|                 |                                     | 4 V scale  | -   | -   | 0.03 | %FSR/°C |

| I <sub>DD</sub> | Operating current <sup>[52]</sup>   | Slow mode  | -   | -   | 100  | μA      |

|                 |                                     | Fast mode  | _   | _   | 500  | μA      |

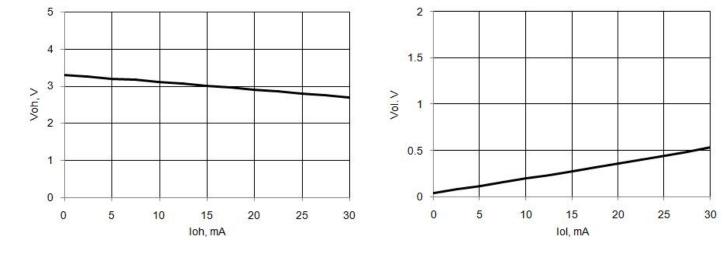

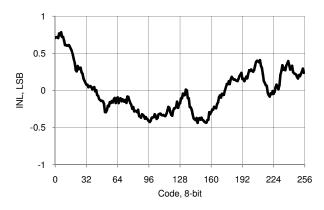

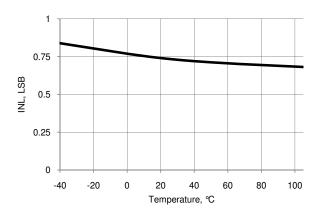

Figure 11-45. VDAC INL vs Input Code, 1 V Mode

Figure 11-47. VDAC INL vs Temperature, 1 V Mode

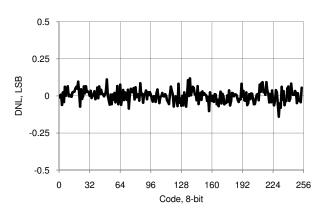

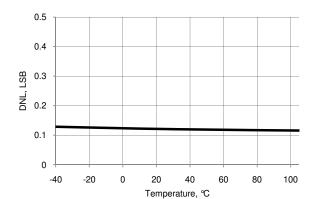

Figure 11-46. VDAC DNL vs Input Code, 1 V Mode

Figure 11-48. VDAC DNL vs Temperature, 1 V Mode

Note 52. Based on device characterization (Not production tested).

## 11.6 Digital Peripherals

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

### 11.6.1 Timer

The following specifications apply to the Timer/Counter/PWM peripheral in timer mode. Timers can also be implemented in UDBs; for more information, see the Timer component datasheet in PSoC Creator.

#### Table 11-32. Timer DC Specifications<sup>[55]</sup>

| Parameter | Description               | Conditions                                    | Min | Тур | Max | Units |

|-----------|---------------------------|-----------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit timer, at listed input clock frequency | -   | _   | -   | μA    |

|           | 3 MHz                     |                                               | -   | 15  | _   | μA    |

|           | 12 MHz                    |                                               | -   | 60  | -   | μA    |

|           | 48 MHz                    |                                               | -   | 260 | -   | μA    |

|           | 80 MHz                    |                                               | -   | 360 | _   | μA    |

#### Table 11-33. Timer AC Specifications<sup>[55]</sup>

| Parameter | Description                                    | Conditions | Min | Тур | Max   | Units |

|-----------|------------------------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency                            |            | DC  | -   | 80.01 | MHz   |

|           | Capture pulse width (Internal) <sup>[56]</sup> |            | 15  | _   | _     | ns    |

|           | Capture pulse width (external)                 |            | 30  | -   | -     | ns    |

|           | Timer resolution <sup>[56]</sup>               |            | 15  | -   | -     | ns    |

|           | Enable pulse width <sup>[56]</sup>             |            | 15  | _   | _     | ns    |

|           | Enable pulse width (external)                  |            | 30  | -   | -     | ns    |

|           | Reset pulse width <sup>[56]</sup>              |            | 15  | -   | -     | ns    |

|           | Reset pulse width (external)                   |            | 30  | -   | -     | ns    |

#### 11.6.2 Counter

The following specifications apply to the Timer/Counter/PWM peripheral, in counter mode. Counters can also be implemented in UDBs; for more information, see the Counter component datasheet in PSoC Creator.

## Table 11-34. Counter DC Specifications<sup>[55]</sup>

| Parameter | Description               | Conditions                                      | Min | Тур | Max | Units |

|-----------|---------------------------|-------------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit counter, at listed input clock frequency | -   | -   | -   | μA    |

|           | 3 MHz                     |                                                 | -   | 15  | _   | μA    |

|           | 12 MHz                    |                                                 | -   | 60  | -   | μA    |

|           | 48 MHz                    |                                                 | -   | 260 | -   | μA    |

|           | 80 MHz                    |                                                 | -   | 360 | -   | μA    |

## Table 11-35. Counter AC Specifications<sup>[55]</sup>

| Parameter | Description                   | Conditions | Min | Тур | Max   | Units |

|-----------|-------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency           |            | DC  | -   | 80.01 | MHz   |

|           | Capture pulse <sup>[56]</sup> |            | 15  | -   | -     | ns    |

|           | Resolution <sup>[56]</sup>    |            | 15  | -   | -     | ns    |

|           | Pulse width <sup>[56]</sup>   |            | 15  | -   | -     | ns    |

|           | Pulse width (external)        |            | 30  |     |       | ns    |

Notes

56. For correct operation, the minimum Timer/Counter/PWM input pulse width is the period of bus clock.

<sup>55.</sup> Based on device characterization (Not production tested).

## 11.6.5 USB

## Table 11-40. USB DC Specifications

| Parameter            | Description                                         | Conditions                                                                                          | Min  | Тур | Max  | Units |

|----------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-----|------|-------|

| V <sub>USB_5</sub>   | Device supply (V <sub>DDD</sub> ) for USB operation | USB configured, USB regulator<br>enabled                                                            | 4.35 | -   | 5.25 | V     |

| V <sub>USB_3.3</sub> |                                                     | USB configured, USB regulator bypassed                                                              | 3.15 | -   | 3.6  | V     |

| V <sub>USB_3</sub>   |                                                     | USB configured, USB regulator bypassed <sup>[59]</sup>                                              | 2.85 | -   | 3.6  | V     |

| IUSB_Configured      | Device supply current in device active              | V <sub>DDD</sub> = 5 V, F <sub>CPU</sub> = 1.5 MHz                                                  | -    | 10  | -    | mA    |

|                      | mode, bus clock and IMO = 24 MHz                    | V <sub>DDD</sub> = 3.3 V, F <sub>CPU</sub> = 1.5 MHz                                                | -    | 8   | -    | mA    |

| IUSB_Suspended       | Device supply current in device sleep mode          | V <sub>DDD</sub> = 5 V, connected to USB<br>host, PICU configured to wake on<br>USB resume signal   | _    | 0.5 | _    | mA    |

|                      |                                                     | V <sub>DDD</sub> = 5 V, disconnected from<br>USB host                                               | Ι    | 0.3 | -    | mA    |

|                      |                                                     | V <sub>DDD</sub> = 3.3 V, connected to USB<br>host, PICU configured to wake on<br>USB resume signal | _    | 0.5 | -    | mA    |

|                      |                                                     | V <sub>DDD</sub> = 3.3 V, disconnected from<br>USB host                                             | -    | 0.3 | -    | mA    |

## 11.7.5 External Memory Interface

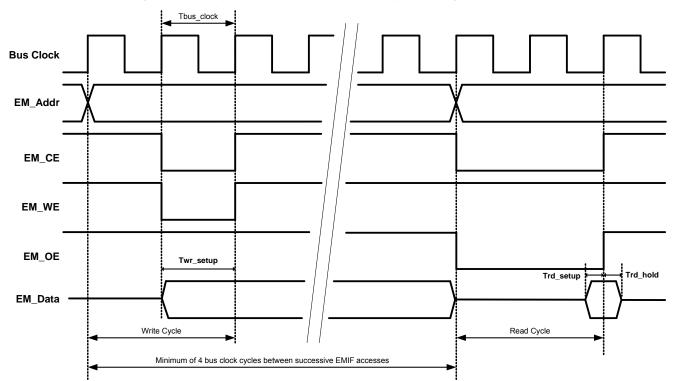

#### Figure 11-58. Asynchronous Write and Read Cycle Timing, No Wait States

Table 11-50. Asynchronous Write and Read Timing Specifications<sup>[63]</sup>

| Parameter  | Description                                                  | Conditions | Min             | Тур | Max | Units |

|------------|--------------------------------------------------------------|------------|-----------------|-----|-----|-------|

| Fbus_clock | Bus clock frequency <sup>[64]</sup>                          |            | -               | -   | 33  | MHz   |

| Tbus_clock | Bus clock period <sup>[65]</sup>                             |            | 30.3            | -   | -   | ns    |

| Twr_Setup  | Time from EM_data valid to rising edge of<br>EM_WE and EM_CE |            | Tbus_clock – 10 | -   | -   | ns    |

| Trd_setup  | Time that EM_data must be valid before rising edge of EM_OE  |            | 5               | -   | -   | ns    |

| Trd_hold   | Time that EM_data must be valid after rising edge of EM_OE   |            | 5               | _   | _   | ns    |

Notes

63. Based on device characterization (Not production tested).

64. EMIF signal timings are limited by GPIO frequency limitations. See "GPIO" section on page 68.

65. EMIF output signals are generally synchronized to bus clock, so EMIF signal timings are dependent on bus clock frequency.

# **15. Document Conventions**

## 15.1 Units of Measure

## Table 15-1. Units of Measure

| Symbol | Unit of Measure        |

|--------|------------------------|

| °C     | degrees Celsius        |

| dB     | decibels               |

| fF     | femtofarads            |

| Hz     | hertz                  |

| KB     | 1024 bytes             |

| kbps   | kilobits per second    |

| Khr    | kilohours              |

| kHz    | kilohertz              |

| kΩ     | kilohms                |

| ksps   | kilosamples per second |

| LSB    | least significant bit  |

| Mbps   | megabits per second    |

| MHz    | megahertz              |

| MΩ     | megaohms               |

| Msps   | megasamples per second |

| μA     | microamperes           |

### Table 15-1. Units of Measure (continued)

| Symbol | Unit of Measure      |

|--------|----------------------|

| μF     | microfarads          |

| μH     | microhenrys          |

| μs     | microseconds         |

| μV     | microvolts           |

| μW     | microwatts           |

| mA     | milliamperes         |

| ms     | milliseconds         |

| mV     | millivolts           |

| nA     | nanoamperes          |

| ns     | nanoseconds          |

| nV     | nanovolts            |

| Ω      | ohms                 |

| pF     | picofarads           |

| ppm    | parts per million    |

| ps     | picoseconds          |

| S      | seconds              |

| sps    | samples per second   |

| sqrtHz | square root of hertz |

| V      | volts                |

# Sales, Solutions, and Legal Information

## Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

### Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

## **PSoC<sup>®</sup> Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

<sup>©</sup> Cypress Semiconductor Corporation, 2012-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and ober countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under these claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware solely for use with Cypress hardware solely for use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to any Unintended Uses of Cypress products.