#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 80MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                               |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                            |

| Number of I/O              | 62                                                                           |

| Program Memory Size        | 256КВ (256К х 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 64K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                 |

| Data Converters            | A/D 1x12b; D/A 1x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-LQFP                                                                     |

| Supplier Device Package    | 100-TQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c5287axi-lp095 |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

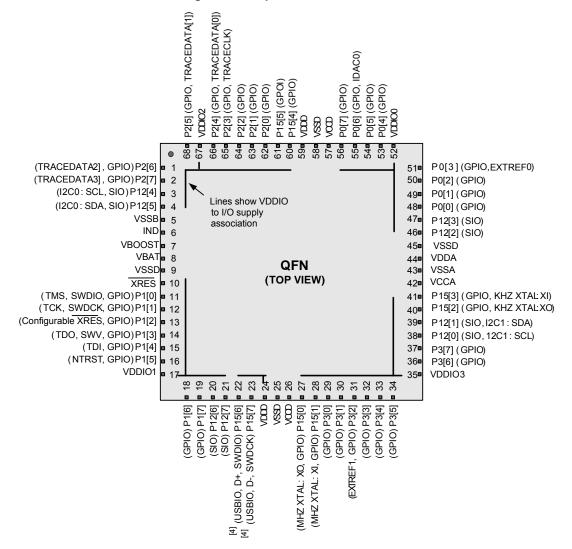

## Figure 2-3. 68-pin QFN Part Pinout<sup>[3]</sup>

Notes

The center pad on the QFN package should be connected to digital ground (VSSD) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal. For more information, see AN72845, Design Guidelines for QFN Devices. 3.

4. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

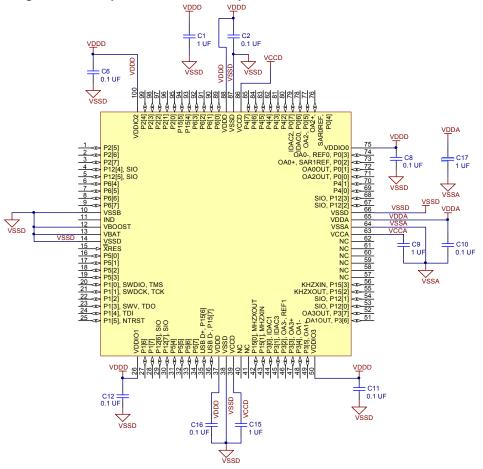

## Figure 2-5. Example Schematic for 100-pin TQFP Part with Power Connections

**Note** The two VCCD pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-6.

For more information on pad layout, refer to http://www.cypress.com/cad-resources/psoc-5lp-cad-libraries.

There are two PHUB masters: the CPU and the DMA controller. Both masters may initiate transactions on the bus. The DMA channels can handle peripheral communication without CPU intervention. The arbiter in the central hub determines which DMA channel is the highest priority if there are multiple requests.

## 4.3.1 PHUB Features

- CPU and DMA controller are both bus masters to the PHUB

- Eight multi-layer AHB bus parallel access paths (spokes) for peripheral access

- Simultaneous CPU and DMA access to peripherals located on different spokes

- Simultaneous DMA source and destination burst transactions on different spokes

- Supports 8-, 16-, 24-, and 32-bit addressing and data

## Table 4-3. PHUB Spokes and Peripherals

| PHUB Spokes | Peripherals                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| 0           | SRAM                                                                                                |

| 1           | IOs, PICU, EMIF                                                                                     |

| 2           | PHUB local configuration, Power manager,<br>Clocks, IC, SWV, EEPROM, Flash<br>programming interface |

| 3           | Analog interface and trim, Decimator                                                                |

| 4           | USB, I <sup>2</sup> C, Timers, Counters, and PWMs                                                   |

| 5           | Reserved                                                                                            |

| 6           | UDBs group 1                                                                                        |

| 7           | UDBs group 2                                                                                        |

## 4.3.2 DMA Features

- 24 DMA channels

- Each channel has one or more transaction descriptors (TDs) to configure channel behavior. Up to 128 total TDs can be defined

- TDs can be dynamically updated

- Eight levels of priority per channel

- Any digitally routable signal, the CPU, or another DMA channel, can trigger a transaction

- Each channel can generate up to two interrupts per transfer

- Transactions can be stalled or canceled

- Supports transaction size of infinite or 1 to 64 k bytes

- Large transactions may be broken into smaller bursts of 1 to 127 bytes

- TDs may be nested and/or chained for complex transactions

## 4.3.3 Priority Levels

The CPU always has higher priority than the DMA controller when their accesses require the same bus resources. Due to the system architecture, the CPU can never starve the DMA. DMA channels of higher priority (lower priority number) may interrupt current DMA transfers. In the case of an interrupt, the current transfer is allowed to complete its current transaction. To ensure latency limits when multiple DMA accesses are requested simultaneously, a fairness algorithm guarantees an interleaved minimum percentage of bus bandwidth for priority levels 2 through 7. Priority levels 0 and 1 do not take part in the fairness algorithm and may use 100% of the bus bandwidth. If a tie occurs on two DMA requests of the same priority level, a simple round robin method is used to evenly share the allocated bandwidth. The round robin allocation can be disabled for each DMA channel, allowing it to always be at the head of the line. Priority levels 2 to 7 are guaranteed the minimum bus bandwidth shown in Table 4-4 after the CPU and DMA priority levels 0 and 1 have satisfied their requirements.

| Priority Level | % Bus Bandwidth |

|----------------|-----------------|

| 0              | 100.0           |

| 1              | 100.0           |

| 2              | 50.0            |

| 3              | 25.0            |

| 4              | 12.5            |

| 5              | 6.2             |

| 6              | 3.1             |

| 7              | 1.5             |

#### Table 4-4. Priority Levels

When the fairness algorithm is disabled, DMA access is granted based solely on the priority level; no bus bandwidth guarantees are made.

#### 4.3.4 Transaction Modes Supported

The flexible configuration of each DMA channel and the ability to chain multiple channels allow the creation of both simple and complex use cases. General use cases include, but are not limited to:

#### 4.3.4.1 Simple DMA

In a simple DMA case, a single TD transfers data between a source and sink (peripherals or memory location). The basic timing diagrams of DMA read and write cycles are shown in Figure 4-2. For more description on other transfer modes, refer to the Technical Reference Manual.

## Table 4-6. Interrupt Vector Table

| Interrupt # | Cortex-M3 Exception # | Fixed Function           | DMA               | UDB          |

|-------------|-----------------------|--------------------------|-------------------|--------------|

| 0           | 16                    | Low voltage detect (LVD) | phub_termout0[0]  | udb_intr[0]  |

| 1           | 17                    | Cache/ECC                | phub_termout0[1]  | udb_intr[1]  |

| 2           | 18                    | Reserved                 | phub_termout0[2]  | udb_intr[2]  |

| 3           | 19                    | Sleep (Pwr Mgr)          | phub_termout0[3]  | udb_intr[3]  |

| 4           | 20                    | PICU[0]                  | phub_termout0[4]  | udb_intr[4]  |

| 5           | 21                    | PICU[1]                  | phub_termout0[5]  | udb_intr[5]  |

| 6           | 22                    | PICU[2]                  | phub_termout0[6]  | udb_intr[6]  |

| 7           | 23                    | PICU[3]                  | phub_termout0[7]  | udb_intr[7]  |

| 8           | 24                    | PICU[4]                  | phub_termout0[8]  | udb_intr[8]  |

| 9           | 25                    | PICU[5]                  | phub_termout0[9]  | udb_intr[9]  |

| 10          | 26                    | PICU[6]                  | phub_termout0[10] | udb_intr[10] |

| 11          | 27                    | PICU[12]                 | phub_termout0[11] | udb_intr[11] |

| 12          | 28                    | PICU[15]                 | phub_termout0[12] | udb_intr[12] |

| 13          | 29                    | Comparators Combined     | phub_termout0[13] | udb_intr[13] |

| 14          | 30                    | Reserved                 | phub_termout0[14] | udb_intr[14] |

| 15          | 31                    | l <sup>2</sup> C         | phub_termout0[15] | udb_intr[15] |

| 16          | 32                    | Reserved                 | phub_termout1[0]  | udb_intr[16] |

| 17          | 33                    | Timer/Counter0           | phub_termout1[1]  | udb_intr[17] |

| 18          | 34                    | Timer/Counter1           | phub_termout1[2]  | udb_intr[18] |

| 19          | 35                    | Timer/Counter2           | phub_termout1[3]  | udb_intr[19] |

| 20          | 36                    | Timer/Counter3           | phub_termout1[4]  | udb_intr[20] |

| 21          | 37                    | USB SOF Int              | phub_termout1[5]  | udb_intr[21] |

| 22          | 38                    | USB Arb Int              | phub_termout1[6]  | udb_intr[22] |

| 23          | 39                    | USB Bus Int              | phub_termout1[7]  | udb_intr[23] |

| 24          | 40                    | USB Endpoint[0]          | phub_termout1[8]  | udb_intr[24] |

| 25          | 41                    | USB Endpoint Data        | phub_termout1[9]  | udb_intr[25] |

| 26          | 42                    | Reserved                 | phub_termout1[10] | udb_intr[26] |

| 27          | 43                    | LCD                      | phub_termout1[11] | udb_intr[27] |

| 28          | 44                    | Reserved                 | phub_termout1[12] | udb_intr[28] |

| 29          | 45                    | Decimator Int            | phub_termout1[13] | udb_intr[29] |

| 30          | 46                    | phub_err_int             | phub_termout1[14] | udb_intr[30] |

| 31          | 47                    | eeprom_fault_int         | phub_termout1[15] | udb_intr[31] |

## 5.5 Nonvolatile Latches (NVLs)

PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-3.

| Table 5-2. | Device | Configuration | NVL | Register Map |

|------------|--------|---------------|-----|--------------|

|------------|--------|---------------|-----|--------------|

| Register Address | 7       | 6         | 5                   | 4 | 3            | 2        | 1            | 0            |  |

|------------------|---------|-----------|---------------------|---|--------------|----------|--------------|--------------|--|

| 0x00             | PRT3RE  | DM[1:0]   | PRT2RDM[1:0]        |   | PRT1RDM[1:0] |          | PRT0         | PRT0RDM[1:0] |  |

| 0x01             | PRT12R  | DM[1:0]   | 1[1:0] PRT6RDM[1:0] |   | PRT5RDM[1:0] |          | PRT4RDM[1:0] |              |  |

| 0x02             | XRESMEN | DBGEN     |                     |   |              | PRT18    | 5RDM[1:0]    |              |  |

| 0x03             |         | DIG_PHS_I | DLY[3:0]            |   | ECCEN        | DPS[1:0] |              | CFGSPEED     |  |

The details for individual fields and their factory default settings are shown in Table 5-3:.

## Table 5-3. Fields and Factory Default Settings

| Field            | Description                                                                                                                            | Settings                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PRTxRDM[1:0]     |                                                                                                                                        | 00b (default) - high impedance analog<br>01b - high impedance digital<br>10b - resistive pull up<br>11b - resistive pull down |

| XRESMEN          | Controls whether pin P1[2] is used as a GPIO or as an external reset. P1[2] is generally used as a GPIO, and not as an external reset. | 0 (default) - GPIO<br>1 - external reset                                                                                      |

| DBGEN            | Debug Enable allows access to the debug system, for third-party programmers.                                                           | 0 - access disabled<br>1 (default) - access enabled                                                                           |

| CFGSPEED         | Controls the speed of the IMO-based clock during the device boot process, for faster boot or low-power operation.                      | 0 (default) - 12-MHz IMO<br>1 - 48-MHz IMO                                                                                    |

| DPS[1:0]         | Controls the usage of various P1 pins as a debug port.<br>See "Programming, Debug Interfaces, Resources" on<br>page 55.                | 00b - 5-wire JTAG<br>01b (default) - 4-wire JTAG<br>10b - SWD<br>11b - debug ports disabled                                   |

| ECCEN            | Controls whether ECC flash is used for ECC or for general configuration and data storage. See "Flash Program Memory" on page 19.       | 0 - ECC disabled<br>1 (default) - ECC enabled                                                                                 |

| DIG_PHS_DLY[3:0] | Selects the digital clock phase delay.                                                                                                 | See the TRM for details.                                                                                                      |

Although PSoC Creator provides support for modifying the device configuration NVLs, the number of NVL erase/write cycles is limited – see "Nonvolatile Latches (NVL)" on page 94.

## 5.7 Memory Map

The Cortex-M3 has a fixed address map, which allows peripherals to be accessed by simple memory access instructions.

## 5.7.1 Address Map

The 4-GB address space is divided into the ranges shown in Table 5-4:

## Table 5-4. Address Map

| Address Range             | Size   | Use                                                                                                                                                    |

|---------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000000-<br>0x1FFFFFF   | 0.5 GB | Program code. This includes<br>the exception vector table at<br>power up, which starts at<br>address 0.                                                |

| 0x20000000–<br>0x3FFFFFFF | 0.5 GB | Static RAM. This includes a 1<br>MByte bit-band region<br>starting at 0x20000000 and a<br>32 Mbyte bit-band alias<br>region starting at<br>0x22000000. |

| 0x40000000–<br>0x5FFFFFF  | 0.5 GB | Peripherals.                                                                                                                                           |

| 0x6000000-<br>0x9FFFFFF   | 1 GB   | External RAM.                                                                                                                                          |

| 0xA0000000–<br>0xDFFFFFF  | 1 GB   | External peripherals.                                                                                                                                  |

| 0xE0000000–<br>0xFFFFFFFF | 0.5 GB | Internal peripherals, including the NVIC and debug and trace modules.                                                                                  |

## Table 5-5. Peripheral Data Address Map

| Address Range         | Purpose                         |

|-----------------------|---------------------------------|

| 0x00000000-0x0003FFFF | 256 K Flash                     |

| 0x1FFF8000–0x1FFFFFFF | 32 K SRAM in Code region        |

| 0x20000000-0x20007FFF | 32 K SRAM in SRAM region        |

| 0x40004000-0x400042FF | Clocking, PLLs, and oscillators |

| 0x40004300-0x400043FF | Power management                |

| 0x40004500-0x400045FF | Ports interrupt control         |

| 0x40004700-0x400047FF | Flash programming interface     |

| 0x40004800-0x400048FF | Cache controller                |

| 0x40004900-0x400049FF | I <sup>2</sup> C controller     |

## Table 5-5. Peripheral Data Address Map (continued)

| Address Range         | Purpose                                                   |

|-----------------------|-----------------------------------------------------------|

| 0x40004E00-0x40004EFF | Decimator                                                 |

| 0x40004F00-0x40004FFF | Fixed timer/counter/PWMs                                  |

| 0x40005000-0x400051FF | I/O ports control                                         |

| 0x40005400–0x400054FF | External Memory Interface<br>(EMIF) control registers     |

| 0x40005800-0x40005FFF | Analog Subsystem Interface                                |

| 0x40006000-0x400060FF | USB Controller                                            |

| 0x40006400-0x40006FFF | UDB Working Registers                                     |

| 0x40007000-0x40007FFF | PHUB Configuration                                        |

| 0x40008000-0x400087FF | EEPROM                                                    |

| 0x4000A000-0x4000A400 | Reserved                                                  |

| 0x40010000-0x4001FFFF | Digital Interconnect Configuration                        |

| 0x48000000-0x48007FFF | Flash ECC Bytes                                           |

| 0x60000000-0x60FFFFF  | External Memory Interface<br>(EMIF)                       |

| 0xE0000000-0xE00FFFF  | Cortex-M3 PPB Registers, including NVIC, debug, and trace |

The bit-band feature allows individual bits in SRAM to be read or written as atomic operations. This is done by reading or writing bit 0 of corresponding words in the bit-band alias region. For example, to set bit 3 in the word at address 0x20000000, write a 1 to address 0x2200000C. To test the value of that bit, read address 0x2200000C and the result is either 0 or 1 depending on the value of the bit.

Most memory accesses done by the Cortex-M3 are aligned, that is, done on word (4-byte) boundary addresses. Unaligned accesses of words and 16-bit half-words on nonword boundary addresses can also be done, although they are less efficient.

## 5.7.2 Address Map and Cortex-M3 Buses

The ICode and DCode buses are used only for accesses within the Code address range, 0–0x1FFFFFF.

The system bus is used for data accesses and debug accesses within the ranges 0x2000000–0xDFFFFFF and 0xE0100000–0xFFFFFFF. Instruction fetches can also be done within the range 0x2000000–0x3FFFFFFF, although these can be slower than instruction fetches via the ICode bus.

The private peripheral bus (PPB) is used within the Cortex-M3 to access system control registers and debug and trace module registers.

The central timewheel can be programmed to wake the system periodically and optionally issue an interrupt. This enables flexible, periodic wakeups from low power modes or coarse timing applications. Systems that require accurate timing should use the RTC capability instead of the central timewheel.

The 100-kHz clock (CLK100K) can be used as a low power system clock to run the CPU. It can also generate time intervals using the fast timewheel.

The fast timewheel is a 5-bit counter, clocked by the 100-kHz clock. It features programmable settings and automatically resets when the terminal count is reached. An optional interrupt can be generated each time the terminal count is reached. This enables flexible, periodic interrupts of the CPU at a higher rate than is allowed using the central timewheel.

The 33-kHz clock (CLK33K) comes from a divide-by-3 operation on CLK100K. This output can be used as a reduced accuracy version of the 32.768-kHz ECO clock with no need for a crystal.

#### 6.1.2 External Oscillators

PRESS

Figure 6-1 shows that there are two external oscillators. They can be routed directly or divided. The direct routes may not have a 50% duty cycle. Divided clocks have a 50% duty cycle.

#### 6.1.2.1 MHz External Crystal Oscillator

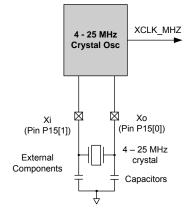

The MHzECO provides high frequency, high precision clocking using an external crystal (see Figure 6-2). It supports a wide variety of crystal types, in the range of 4 to 25 MHz. When used in conjunction with the PLL, it can generate CPU and system clocks up to the device's maximum frequency (see Internal Low Speed Oscillator). The GPIO pins connecting to the external crystal and capacitors are fixed. MHzECO accuracy depends on the crystal chosen.

#### Figure 6-2. MHzECO Block Diagram

#### 6.1.2.2 32.768 kHz ECO

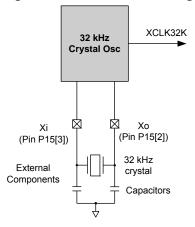

The 32.768-kHz external crystal oscillator (32kHzECO) provides precision timing with minimal power consumption using an external 32.768-kHz watch crystal (see Figure 6-3). The 32kHzECO also connects directly to the sleep timer and provides the source for the RTC. The RTC uses a 1-second interrupt to implement the RTC functionality in firmware.

The oscillator works in two distinct power modes. This allows you to trade off power consumption with noise immunity from neighboring circuits. The GPIO pins connected to the external crystal and capacitors are fixed.

#### Figure 6-3. 32kHzECO Block Diagram

It is recommended that the external 32.768-kHz watch crystal have a load capacitance (CL) of 6 pF or 12.5 pF. Check the crystal manufacturer's datasheet. The two external capacitors, CL1 and CL2, are typically of the same value, and their total capacitance, CL1CL2 / (CL1 + CL2), including pin and trace capacitance, should equal the crystal CL value. For more information, refer to application note AN54439: PSoC 3 and PSoC 5 External Oscillators. See also pin capacitance specifications in the "GPIO" section on page 68.

#### 6.1.2.3 Digital System Interconnect

The DSI provides routing for clocks taken from external clock oscillators connected to I/O. The oscillators can also be generated within the device in the digital system and UDBs.

While the primary DSI clock input provides access to all clocking resources, up to eight other DSI clocks (internally or externally generated) may be routed directly to the eight digital clock dividers. This is only possible if there are multiple precision clock sources.

#### 6.1.3 Clock Distribution

All seven clock sources are inputs to the central clock distribution system. The distribution system is designed to create multiple high precision clocks. These clocks are customized for the design's requirements and eliminate the common problems found with limited resolution prescalers attached to peripherals. The clock distribution system generates several types of clock trees.

- The system clock is used to select and supply the fastest clock in the system for general system clock requirements and clock synchronization of the PSoC device.

- Bus Clock 16-bit divider uses the system clock to generate the system's bus clock used for data transfers and the CPU. The CPU clock is directly derived from the bus clock.

- Eight fully programmable 16-bit clock dividers generate digital system clocks for general use in the digital system, as configured by the design's requirements. Digital system clocks can generate custom clocks derived from any of the seven clock sources for any purpose. Examples include baud rate generators, accurate PWM periods, and timer clocks, and many others. If more than eight digital clock dividers are required, the Universal Digital Blocks (UDBs) and fixed function timer/counter/PWMs can also generate clocks.

## 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the VDDIO pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both GPIO and special I/O (SIO) provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[8]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of VDDA and for programmable output voltages.

- Features supported by both GPIO and SIO:

- User programmable port reset state

- Separate I/O supplies and voltages for up to four groups of I/O

- Digital peripherals use DSI to connect the pins

Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- LCD segment drive on LCD equipped devices

- CapSense<sup>[8]</sup>

- Analog input and output capability

- □ Continuous 100 µA clamp current capability

- Standard drive strength down to 1.71 V

- Additional features only provided on SIO pins:

- B Higher drive strength than GPIO

- Hot swap capability (5 V tolerance at any operating VDD)

Programmable and regulated high input and output drive

- le Programmable and regulated high input and output drive levels down to 1.2 V

- No analog input, CapSense, or LCD capability

- $\blacksquare$  Over voltage tolerance up to 5.5 V

- SIO can act as a general purpose analog comparator

<sup>8.</sup> GPIOs with opamp outputs are not recommended for use with CapSense.

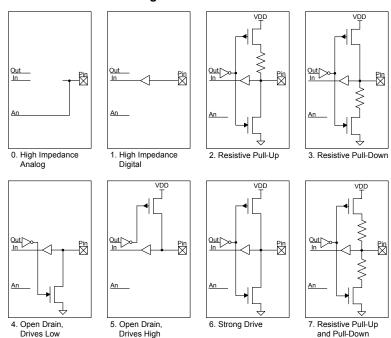

## 6.4.1 Drive Modes

Each GPIO and SIO pin is individually configurable into one of the eight drive modes listed in Table 6-6. Three configuration bits are used for each pin (DM[2:0]) and set in the PRTxDM[2:0] registers. Figure 6-12 depicts a simplified pin view based on each of the eight drive modes. Table 6-6 shows the I/O pin's drive state based on the port data register value or digital array signal

if bypass mode is selected. Note that the actual I/O pin voltage is determined by a combination of the selected drive mode and the load at the pin. For example, if a GPIO pin is configured for resistive pull up mode and driven high while the pin is floating, the voltage measured at the pin is a high logic state. If the same GPIO pin is externally tied to ground then the voltage unmeasured at the pin is a low logic state.

Figure 6-12. Drive Mode

The 'Out' connection is driven from either the Digital System (when the Digital Output terminal is connected) or the Data Register (when HW connection is disabled). The 'In' connection drives the Pin State register, and the Digital System if the Digital Input terminal is enabled and connected

The 'An' connection connects to the Analog System

## Table 6-6. Drive Modes

| Diagram | Drive Mode                                     | PRTxDM2 | PRTxDM1 | PRTxDM0 | PRTxDR = 1    | PRTxDR = 0   |

|---------|------------------------------------------------|---------|---------|---------|---------------|--------------|

| 0       | High impedance analog                          | 0       | 0       | 0       | High-Z        | High-Z       |

| 1       | High Impedance digital                         | 0       | 0       | 1       | High-Z        | High-Z       |

| 2       | Resistive pull-up <sup>[9]</sup>               | 0       | 1       | 0       | Res High (5K) | Strong Low   |

| 3       | Resistive pull-down <sup>[9]</sup>             | 0       | 1       | 1       | Strong High   | Res Low (5K) |

| 4       | Open drain, drives low                         | 1       | 0       | 0       | High-Z        | Strong Low   |

| 5       | Open drain, drive high                         | 1       | 0       | 1       | Strong High   | High-Z       |

| 6       | Strong drive                                   | 1       | 1       | 0       | Strong High   | Strong Low   |

| 7       | Resistive pull-up and pull-down <sup>[9]</sup> | 1       | 1       | 1       | Res High (5K) | Res Low (5K) |

## 6.4.5 Pin Interrupts

All GPIO and SIO pins are able to generate interrupts to the system. All eight pins in each port interface to their own port interrupt control unit (PICU) and associated interrupt vector. Each pin of the port is independently configurable to detect rising edge, falling edge, both edge interrupts, or to not generate an interrupt.

Depending on the configured mode for each pin, each time an interrupt event occurs on a pin, its corresponding status bit of the interrupt status register is set to "1" and an interrupt request is sent to the interrupt controller. Each PICU has its own interrupt vector in the interrupt controller and the pin status register providing easy determination of the interrupt source down to the pin level.

Port pin interrupts remain active in all sleep modes allowing the PSoC device to wake from an externally generated interrupt.

While level sensitive interrupts are not directly supported; UDBs provide this functionality to the system when needed.

## 6.4.6 Input Buffer Mode

GPIO and SIO input buffers can be configured at the port level for the default CMOS input thresholds or the optional LVTTL input thresholds. All input buffers incorporate Schmitt triggers for input hysteresis. Additionally, individual pin input buffers can be disabled in any drive mode.

## 6.4.7 I/O Power Supplies

Up to four I/O pin power supplies are provided depending on the device and package. Each I/O supply must be less than or equal to the voltage on the chip's analog (VDDA) pin. This feature allows you to provide different I/O voltage levels for different pins on the device. Refer to the specific device package pinout to determine VDDIO capability for a given port and pin.

The SIO port pins support an additional regulated high output capability, as described in Adjustable Output Level.

#### 6.4.8 Analog Connections

These connections apply only to GPIO pins. All GPIO pins may be used as analog inputs or outputs. The analog voltage present on the pin must not exceed the VDDIO supply voltage to which the GPIO belongs. Each GPIO may connect to one of the analog global busses or to one of the analog mux buses to connect any pin to any internal analog resource such as ADC or comparators. In addition, one select pin provides direct connection to the high current DAC.

## 6.4.9 CapSense

This section applies only to GPIO pins. All GPIO pins may be used to create CapSense buttons and sliders<sup>[10]</sup>. See the "CapSense" section on page 54 for more information.

## 6.4.10 LCD Segment Drive

This section applies only to GPIO pins. All GPIO pins may be used to generate Segment and Common drive signals for direct glass drive of LCD glass. See the "LCD Direct Drive" section on page 53 for details.

## 6.4.11 Adjustable Output Level

This section applies only to SIO pins. SIO port pins support the ability to provide a regulated high output level for interface to external signals that are lower in voltage than the SIO's respective VDDIO. SIO pins are individually configurable to output either the standard VDDIO level or the regulated output, which is based on an internally generated reference. Typically the voltage DAC (VDAC) is used to generate the reference (see Figure 6-13). The DAC on page 54 has more details on VDAC use and reference routing to the SIO pins. Resistive pull up and pull down drive modes are not available with SIO in regulated output mode.

## 6.4.12 Adjustable Input Level

This section applies only to SIO pins. SIO pins by default support the standard CMOS and LVTTL input levels but also support a differential mode with programmable levels. SIO pins are grouped into pairs. Each pair shares a reference generator block which, is used to set the digital input buffer reference level for interface to external signals that differ in voltage from VDDIO. The reference sets the pins voltage threshold for a high logic level (see Figure 6-13). Available input thresholds are:

- 0.5 × VDDIO

- 0.4 × VDDIO

- 0.5 × VREF

- VREF

Typically the voltage DAC (VDAC) generates the VREF reference. The DAC on page 54 has more details on VDAC use and reference routing to the SIO pins.

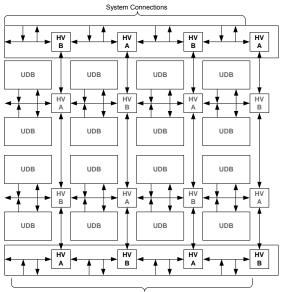

## 7.3 UDB Array Description

Figure 7-7 shows an example of a 16 UDB array. In addition to the array core, there are a DSI routing interfaces at the top and bottom of the array. Other interfaces that are not explicitly shown include the system interfaces for bus and clock distribution. The UDB array includes multiple horizontal and vertical routing channels each comprised of 96 wires. The wire connections to UDBs, at horizontal/vertical intersection and at the DSI interface are highly permutable providing efficient automatic routing in PSoC Creator. Additionally the routing allows wire by wire segmentation along the vertical and horizontal routing to further increase routing flexibility and capability.

## Figure 7-7. Digital System Interface Structure

System Connections

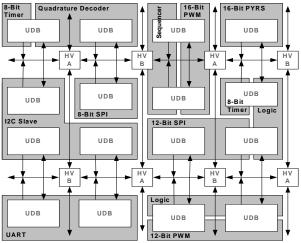

## 7.3.1 UDB Array Programmable Resources

Figure 7-8 shows an example of how functions are mapped into a bank of 16 UDBs. The primary programmable resources of the UDB are two PLDs, one datapath and one status/control register. These resources are allocated independently, because they have independently selectable clocks, and therefore unused blocks are allocated to other unrelated functions.

An example of this is the 8-bit timer in the upper left corner of the array. This function only requires one datapath in the UDB, and therefore the PLD resources may be allocated to another function. A function such as a Quadrature Decoder may require more PLD logic than one UDB can supply and in this case can

utilize the unused PLD blocks in the 8-bit timer UDB. Programmable resources in the UDB array are generally homogeneous so functions can be mapped to arbitrary boundaries in the array.

## Figure 7-8. Function Mapping Example in a Bank of UDBs

## 7.4 DSI Routing Interface Description

The DSI routing interface is a continuation of the horizontal and vertical routing channels at the top and bottom of the UDB array core. It provides general purpose programmable routing between device peripherals, including UDBs, I/Os, analog peripherals, interrupts, DMA and fixed function peripherals.

Figure 7-9 illustrates the concept of the digital system interconnect, which connects the UDB array routing matrix with other device peripherals. Any digital core or fixed function peripheral that needs programmable routing is connected to this interface.

Signals in this category include:

- Interrupt requests from all digital peripherals in the system.

- DMA requests from all digital peripherals in the system.

- Digital peripheral data signals that need flexible routing to I/Os.

- Digital peripheral data signals that need connections to UDBs.

- Connections to the interrupt and DMA controllers.

- Connection to I/O pins.

- Connection to analog system digital signals.

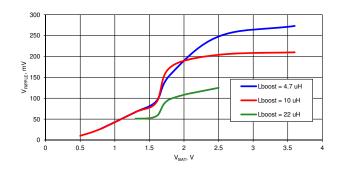

| Parameter          | Description                                                                                      | Conditions     | Min  | Тур  | Max  | Units |

|--------------------|--------------------------------------------------------------------------------------------------|----------------|------|------|------|-------|

| L <sub>BOOST</sub> | Boost inductor                                                                                   | 4.7 μH nominal | 3.7  | 4.7  | 5.7  | μH    |

|                    |                                                                                                  | 10 μH nominal  | 8.0  | 10.0 | 12.0 | μH    |

|                    |                                                                                                  | 22 μH nominal  | 17.0 | 22.0 | 27.0 | μH    |

| C <sub>BOOST</sub> | Total capacitance sum of V <sub>DDD</sub> , V <sub>DDA</sub> , V <sub>DDI0</sub> <sup>[29]</sup> |                | 17.0 | 26.0 | 31.0 | μF    |

| C <sub>BAT</sub>   | Battery filter capacitor                                                                         |                | 17.0 | 22.0 | 27.0 | μF    |

| l <sub>F</sub>     | Schottky diode average forward current                                                           |                | 1.0  | _    | -    | A     |

| V <sub>R</sub>     | Schottky reverse voltage                                                                         |                | 20.0 | -    | -    | V     |

## Table 11-7. Recommended External Components for Boost Circuit

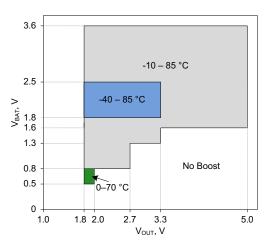

## Figure 11-8. $T_{A}$ range over $V_{BAT}\,$ and $V_{OUT}$

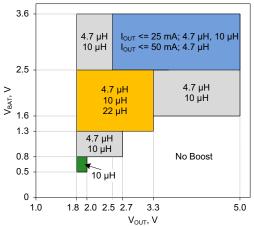

## Figure 11-10. L\_{BOOST} values over V\_{BAT} and V\_{OUT}

#### Note 29. Based on device characterization (Not production tested).

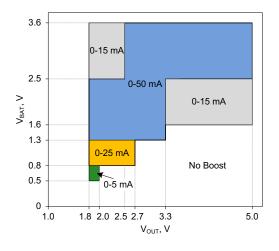

## Figure 11-9. $I_{OUT}$ range over $V_{BAT}$ and $V_{OUT}$

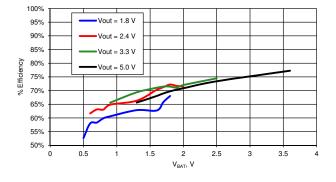

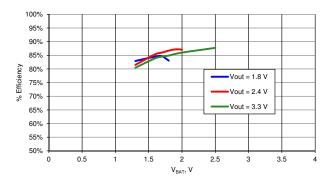

# Figure 11-11. Efficiency vs V<sub>BAT</sub>, $L_{BOOST}$ = 4.7 $\mu$ H <sup>[30]</sup>

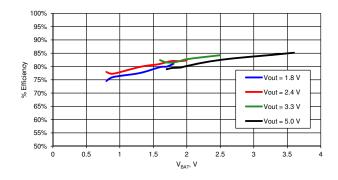

Figure 11-13. Efficiency vs V<sub>BAT</sub>,  $L_{BOOST}$  = 22 µH <sup>[30]</sup>

Figure 11-12. Efficiency vs  $V_{BAT}$ ,  $L_{BOOST}$  = 10  $\mu$ H <sup>[30]</sup>

Figure 11-14. V<sub>RIPPLE</sub> vs V<sub>BAT</sub> <sup>[30]</sup>

#### Note

30. Typical example. Actual values may vary depending on external component selection, PCB layout, and other design parameters.

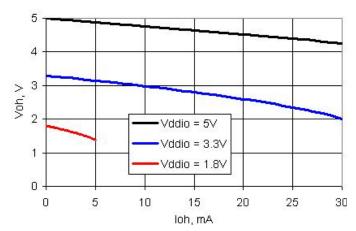

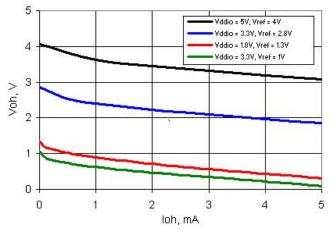

Figure 11-17. SIO Output High Voltage and Current, Unregulated Mode

Figure 11-19. SIO Output High Voltage and Current, Regulated Mode

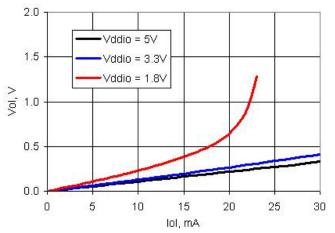

Figure 11-18. SIO Output Low Voltage and Current, Unregulated Mode

# Table 11-12. SIO Comparator Specifications<sup>[37]</sup>

| Parameter | Description                    | Conditions                | Min | Тур | Max | Units |

|-----------|--------------------------------|---------------------------|-----|-----|-----|-------|

| Vos       | Offset voltage                 | V <sub>DDIO</sub> = 2 V   | -   | -   | 68  | mV    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | -   | -   | 72  |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | -   | -   | 82  |       |

| TCVos     | Offset voltage drift with temp |                           | -   | -   | 250 | µV/°C |

| CMRR      | Common mode rejection ratio    | V <sub>DDIO</sub> = 2 V   | 30  | -   | -   | dB    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | 35  | -   | -   |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | 40  | -   | _   |       |

| Tresp     | Response time                  |                           | -   | -   | 30  | ns    |

## 11.4.3 USBIO

For operation in GPIO mode, the standard range for V<sub>DDD</sub> applies, see Device Level Specifications on page 61.

## Table 11-13. USBIO DC Specifications

| Parameter       | Description                                            | Conditions                                         | Min            | Тур | Max            | Units |

|-----------------|--------------------------------------------------------|----------------------------------------------------|----------------|-----|----------------|-------|

| Rusbi           | USB D+ pull-up resistance <sup>[37]</sup>              | With idle bus                                      | 0.900          | -   | 1.575          | kΩ    |

| Rusba           | USB D+ pull-up resistance <sup>[37]</sup>              | While receiving traffic                            | 1.425          | -   | 3.090          | kΩ    |

| Vohusb          | Static output high <sup>[37]</sup>                     | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | 2.8            | -   | 3.6            | V     |

| Volusb          | Static output low <sup>[37]</sup>                      | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | _              | -   | 0.3            | V     |

| Vihgpio         | Input voltage high, GPIO mode <sup>[37]</sup>          | V <sub>DDD</sub> = 1.8 V                           | 1.5            | -   | -              | V     |

|                 |                                                        | V <sub>DDD</sub> = 3.3 V                           | 2              | I   | _              | V     |

|                 |                                                        | V <sub>DDD</sub> = 5.0 V                           | 2              | I   | _              | V     |

| Vilgpio         | Input voltage low, GPIO mode <sup>[37]</sup>           | V <sub>DDD</sub> = 1.8 V                           | _              | -   | 0.8            | V     |

|                 |                                                        | V <sub>DDD</sub> = 3.3 V                           | _              | -   | 0.8            | V     |

|                 |                                                        | V <sub>DDD</sub> = 5.0 V                           | _              | -   | 0.8            | V     |

| Vohgpio         | Output voltage high, GPIO mode <sup>[37]</sup>         | I <sub>OH</sub> = 4 mA, V <sub>DDD</sub> = 1.8 V   | 1.6            | -   | -              | V     |

|                 |                                                        | I <sub>OH</sub> = 4 mA, V <sub>DDD</sub> = 3.3 V   | 3.1            | -   | _              | V     |

|                 |                                                        | I <sub>OH</sub> = 4 mA, V <sub>DDD</sub> = 5.0 V   | 4.2            | I   | _              | V     |

| Volgpio         | Output voltage low, GPIO mode <sup>[37]</sup>          | I <sub>OL</sub> = 4 mA, V <sub>DDD</sub> = 1.8 V   | -              | I   | 0.3            | V     |

|                 |                                                        | I <sub>OL</sub> = 4 mA, V <sub>DDD</sub> = 3.3 V   | -              | -   | 0.3            | V     |

|                 |                                                        | I <sub>OL</sub> = 4 mA, V <sub>DDD</sub> = 5.0 V   | -              | -   | 0.3            | V     |

| Vdi             | Differential input sensitivity                         | (D+)–(D–)                                          | -              | I   | 0.2            | V     |

| Vcm             | Differential input common mode range                   |                                                    | 0.8            | I   | 2.5            | V     |

| Vse             | Single ended receiver threshold                        |                                                    | 0.8            | -   | 2              | V     |

| Rps2            | PS/2 pull-up resistance <sup>[37]</sup>                | In PS/2 mode, with PS/2 pull-up enabled            | 3              | -   | 7              | kΩ    |

| Rext            | External USB series resistor <sup>[37]</sup>           | In series with each USB pin                        | 21.78<br>(–1%) | 22  | 22.22<br>(+1%) | Ω     |

| Zo              | USB driver output impedance <sup>[37]</sup>            | Including Rext                                     | 28             | _   | 44             | Ω     |

| C <sub>IN</sub> | USB transceiver input capacitance                      |                                                    | -              | _   | 20             | pF    |

| IIL             | Input leakage current (absolute value) <sup>[37]</sup> | 25 °C, V <sub>DDD</sub> = 3.0 V                    | -              | -   | 2              | nA    |

#### Note

37. Based on device characterization (Not production tested).

## 11.5.3 Analog Globals

**CYPRESS**

## Table 11-21. Analog Globals DC Specifications

| Parameter                                | Description                                              | Conditions                | Min | Тур  | Max  | Units |

|------------------------------------------|----------------------------------------------------------|---------------------------|-----|------|------|-------|

|                                          | Resistance pin-to-pin through                            | V <sub>DDA</sub> = 3.0 V  | -   | 1500 | 2200 | Ω     |

|                                          | P2[4], AGLÓ, DSM INP, AGL1,<br>P2[5] <sup>[43, 45]</sup> | V <sub>DDA</sub> = 1.71 V | -   | 1200 | 1700 | Ω     |

| Rppmuxbus                                | Resistance pin-to-pin through                            | V <sub>DDA</sub> = 3.0 V  | -   | 700  | 1100 | Ω     |

| P2[3], amuxbusL, P2[4] <sup>[44, 4</sup> |                                                          | V <sub>DDA</sub> = 1.71 V | -   | 600  | 900  | Ω     |

## Table 11-22. Analog Globals AC Specifications

| Parameter | Description                                            | Conditions                      | Min | Тур | Max | Units |

|-----------|--------------------------------------------------------|---------------------------------|-----|-----|-----|-------|

|           | Inter-pair crosstalk for analog routes <sup>[45]</sup> |                                 | 106 | I   | Ι   | dB    |

| BWag      | Analog globals 3 db bandwidth <sup>[45]</sup>          | V <sub>DDA</sub> = 3.0 V, 25 °C | -   | 26  | -   | MHz   |

Notes

43. Based on device characterization (Not production tested).

44. The resistance of the analog global and analog mux bus is high if V<sub>DDA</sub> ≤ 2.7 V, and the chip is in either sleep or hibernate mode. Use of analog global and analog mux bus under these conditions is not recommended.

45. Pin P6[4] to del-sig ADC input; calculated, not measured.

## 11.5.4 Comparator

# Table 11-23. Comparator DC Specifications<sup>[46, 47]</sup>

| Parameter         | Description                                     | Conditions                                           | Min              | Тур | Max                        | Units |

|-------------------|-------------------------------------------------|------------------------------------------------------|------------------|-----|----------------------------|-------|

| V <sub>OS</sub>   | Input offset voltage in fast mode               | Factory trim, $V_{DDA} > 2.7 V$ , $V_{IN} \ge 0.5 V$ | -                |     | 10                         | mV    |

|                   | Input offset voltage in slow mode               | Factory trim, $V_{IN} \ge 0.5 V$                     | -                |     | 9                          | mV    |

| Maria             | Input offset voltage in fast mode               | Custom trim                                          | -                | -   | 4                          | mV    |

| V <sub>OS</sub>   | Input offset voltage in slow mode               | Custom trim                                          | -                | -   | 4                          | mV    |

| V <sub>OS</sub>   | Input offset voltage in ultra low<br>power mode |                                                      | -                | ±12 | -                          | mV    |

| TCVos             | Temperature coefficient, input offset           | V <sub>CM</sub> = V <sub>DDA</sub> / 2, fast mode    | -                | 63  | 85                         | µV/°C |

|                   | voltage                                         | $V_{CM} = V_{DDA} / 2$ , slow mode                   | -                | 15  | 20                         |       |

| V <sub>HYST</sub> | Hysteresis                                      | Hysteresis enable mode                               | -                | 10  | 32                         | mV    |

| V <sub>ICM</sub>  | Input common mode voltage                       | High current / fast mode                             | V <sub>SSA</sub> | -   | V <sub>DDA</sub>           | V     |

|                   |                                                 | Low current / slow mode                              | V <sub>SSA</sub> | _   | V <sub>DDA</sub>           | V     |

|                   |                                                 | Ultra low power mode                                 | V <sub>SSA</sub> | -   | V <sub>DDA</sub> –<br>1.15 | V     |

| CMRR              | Common mode rejection ratio                     |                                                      | -                | 50  | -                          | dB    |

| I <sub>CMP</sub>  | High current mode/fast mode                     |                                                      | -                | -   | 400                        | μA    |

|                   | Low current mode/slow mode                      |                                                      | -                | -   | 100                        | μA    |

|                   | Ultra low power mode                            |                                                      | -                | 6   | -                          | μA    |

# Table 11-24. Comparator AC Specifications<sup>[46, 47]</sup>

| Parameter         | Description                         | Тур                                     | Max | Units |     |    |

|-------------------|-------------------------------------|-----------------------------------------|-----|-------|-----|----|

|                   | Response time, high current mode    | 50 mV overdrive, measured<br>pin-to-pin | -   | 75    | 110 | ns |

| T <sub>RESP</sub> | Response time, low current mode     | 50 mV overdrive, measured pin-to-pin    | _   | 155   | 200 | ns |

|                   | Response time, ultra low power mode | 50 mV overdrive, measured pin-to-pin    | _   | 55    | _   | μs |

46. The recommended procedure for using a custom trim value for the on-chip comparators are found in the TRM.

47. Based on device characterization (Not production tested).

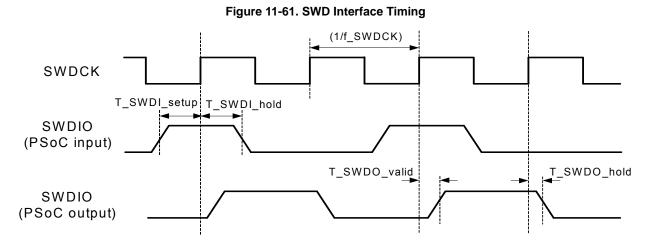

## 11.8.5 SWD Interface

## Table 11-58. SWD Interface AC Specifications<sup>[74]</sup>

| Parameter    | Description                         | Conditions                                         | Min | Тур | Max                 | Units |

|--------------|-------------------------------------|----------------------------------------------------|-----|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3~V \leq V_{DDD} \leq 5~V$                      | -   | -   | 12 <sup>[75]</sup>  | MHz   |

|              |                                     | $1.71~V \leq V_{DDD} < 3.3~V$                      | -   | _   | 7 <sup>[75]</sup>   | MHz   |

|              |                                     | $1.71~V \leq V_{DDD}$ < 3.3 V, SWD over USBIO pins | -   | -   | 5.5 <sup>[75]</sup> | MHz   |

| T_SWDI_setup | SWDIO input setup before SWDCK high | T = 1/f_SWDCK max                                  | T/4 | -   | -                   |       |

| T_SWDI_hold  | SWDIO input hold after SWDCK high   | T = 1/f_SWDCK max                                  | T/4 | -   | -                   |       |

| T_SWDO_valid | SWDCK high to SWDIO output          | T = 1/f_SWDCK max                                  | _   | -   | T/2                 |       |

| T_SWDO_hold  | SWDIO output hold after SWDCK high  | T = 1/f_SWDCK max                                  | 1   | -   | _                   | ns    |

## 11.8.6 TPIU Interface

# Table 11-59. TPIU Interface AC Specifications<sup>[74]</sup>

| Parameter | Description                    | Conditions | Min | Тур | Max                | Units |

|-----------|--------------------------------|------------|-----|-----|--------------------|-------|

|           | TRACEPORT (TRACECLK) frequency |            | -   | -   | 33 <sup>[76]</sup> | MHz   |

|           | SWV bit rate                   |            | -   | -   | 33 <sup>[76]</sup> | Mbit  |

#### Notes

74. Based on device characterization (Not production tested).

75. f\_SWDCK must also be no more than 1/3 CPU clock frequency.

76. TRACEPORT signal frequency and bit rate are limited by GPIO output frequency, see Table 11-9 on page 69.

# **12. Ordering Information**

In addition to the features listed in Table 12-1, every CY8C52LP device includes: up to 256 KB flash, 64 KB SRAM, 2 KB EEPROM, a precision on-chip voltage reference, precision oscillators, flash, ECC, DMA, a fixed function I<sup>2</sup>C, JTAG/SWD programming and debug, external memory interface, boost, and more. In addition to these features, the flexible UDBs and analog subsection support a wide range of peripherals. To assist you in selecting the ideal part, PSoC Creator makes a part recommendation after you choose the components required by your application. All CY8C52LP derivatives incorporate device and flash security in user-selectable security levels; see the TRM for details.

|                                   |                 | ICU        | Core      | <b>;</b>    |                   | A            | nal | og          |                     |        |     |          | D                    | igita            | al     |           | I/O  | [85] |       |          |                         |

|-----------------------------------|-----------------|------------|-----------|-------------|-------------------|--------------|-----|-------------|---------------------|--------|-----|----------|----------------------|------------------|--------|-----------|------|------|-------|----------|-------------------------|

| Part Number                       | CPU Speed (MHz) | Flash (KB) | SRAM (KB) | EEPROM (KB) | LCD Segment Drive | ADC          | DAC | Comparators | SC/CT Analog Blocks | Opamps | DFB | CapSense | UDBs <sup>[84]</sup> | 16-bit Timer/PWM | FS USB | Total I/O | GPIO | SIO  | USBIO | Package  | JTAG ID <sup>[86]</sup> |

| CY8C5268LTI-LP030                 | 67              | 256        | 64        | 2           | ~                 | 1x12-bit SAR | 1   | 2           | 0                   | 0      | -   | ~        | 24                   | 4                | ~      | 48        | 38   | 8    | 2     | 68-QFN   | 0x2E11E069              |

| CY8C5268AXI-LP047                 | 67              | 256        | 64        | 2           | ~                 | 1x12-bit SAR | 1   | 2           | 0                   | 0      | -   | ~        | 24                   | 4                | ~      | 72        | 62   | 8    | 2     | 100-TQFP | 0x2E12F069              |

| CY8C5267AXI-LP051                 | 67              | 128        | 32        | 2           | ~                 | 1x12-bit SAR | 1   | 2           | 0                   | 0      | -   | ~        | 24                   | 4                | ~      | 72        | 62   | 8    | 2     | 100-TQFP | 0x2E133069              |

| CY8C5267LTI-LP089                 | 67              | 128        | 32        | 2           | ~                 | 1x12-bit SAR | 1   | 2           | 0                   | 0      | -   | ~        | 24                   | 4                | ~      | 48        | 38   | 8    | 2     | 68-QFN   | 0x2E159069              |

| CY8C5266LTI-LP029                 | 67              | 64         | 16        | 2           | ~                 | 1x12-bit SAR | 1   | 2           | 0                   | 0      | -   | ~        | 20                   | 4                | ~      | 48        | 38   | 8    | 2     | 68-QFN   | 0x2E11D069              |

| CY8C5266AXI-LP033                 | 67              | 64         | 16        | 2           | ~                 | 1x12-bit SAR | 1   | 2           | 0                   | 0      | -   | ~        | 20                   | 4                | ~      | 72        | 62   | 8    | 2     | 100-TQFP | 0x2E121069              |

| CY8C5266AXI-LP132                 | 67              | 64         | 16        | 2           | ~                 | 1x12-bit SAR | 1   | 2           | 0                   | 0      | -   | ~        | 20                   | 4                | -      | 70        | 62   | 8    | 0     | 100-TQFP | 0x2E184069              |

| CY8C5266LTI-LP150                 | 67              | 64         | 16        | 2           | ~                 | 1x12-bit SAR | 1   | 2           | 0                   | 0      | -   | ~        | 20                   | 4                | -      | 46        | 38   | 8    | 0     | 68-QFN   | 0x2E196069              |

| CY8C5265LTI-LP050                 | 67              | 32         | 8         | 2           | ~                 | 1x12-bit SAR | 1   | 0           | 0                   | 0      | -   | ~        | 20                   | 4                | ~      | 48        | 38   | 8    | 2     | 68-QFN   | 0x2E132069              |

| CY8C5265AXI-LP056                 | 67              | 32         | 8         | 2           | ~                 | 1x12-bit SAR | 1   | 0           | 0                   | 0      | -   | ~        | 20                   | 4                | ~      | 72        | 62   | 8    | 2     | 100-TQFP | 0x2E138069              |

| CY8C5265LTI-LP058                 | 67              | 32         | 8         | 2           | ~                 | 1x12-bit SAR | 1   | 2           | 0                   | 0      | -   | ~        | 20                   | 4                | ~      | 48        | 38   | 8    | 2     | 68-QFN   | 0x2E13A069              |

| CY8C5265AXI-LP082                 | 67              | 32         | 8         | 2           | ~                 | 1x12-bit SAR | 1   | 2           | 0                   | 0      | -   | ~        | 20                   | 4                | ~      | 72        | 62   | 8    | 2     | 100-TQFP | 0x2E152069              |

| CY8C5287AXI-LP095 <sup>[87]</sup> | 80              | 256        | 64        | 2           | ~                 | 1x12-bit SAR | 1   | 2           | 0                   | 0      | -   | ~        | 24                   | 4                | ~      | 72        | 62   | 8    | 2     | 100-TQFP | 0x2E15F069              |

| CY8C5288LTI-LP090                 | 80              | 256        | 64        | 2           | ~                 | 1x12-bit SAR | 1   | 2           | 0                   | 0      | -   | ~        | 24                   | 4                | ~      | 48        | 38   | 8    | 2     | 68-QFN   | 0x2E15A069              |

| CY8C5288FNI-LP213                 | 80              | 256        | 64        | 2           | ~                 | 1x12-bit SAR | 1   | 2           | 0                   | 0      | -   | ~        | 24                   | 4                | ~      | 72        | 62   | 8    | 2     | 99-WLCSP | 0x2E1D5069              |

## Table 12-1. CY8C52LP Family with ARM Cortex-M3 CPU

Notes

86. The JTAG ID has three major fields. The most significant nibble (left digit) is the version, followed by a 2 byte part number and a 3 nibble manufacturer ID.

<sup>84.</sup> UDBs support a wide variety of functionality including SPI, LIN, UART, timer, counter, PWM, PRS, and others. Individual functions may use a fraction of a UDB or multiple UDBs. Multiple functions can share a single UDB. See Example Peripherals on page 39 for more information on how UDBs can be used.

85. The I/O Count includes all types of digital I/O: GPIO, SIO, and the two USB I/O. See I/O System and Routing on page 32 for details on the functionality of each of

<sup>85.</sup> The I/O Count includes all types of digital I/O: GPIO, SIO, and the two USB I/O. See I/O System and Routing on page 32 for details on the functionality of each of these types of I/O.

85. The I/O D has three types the types the types and a 2 with the type and a 2 with the types and a 2 with the types of I/O.

<sup>87.</sup> This part varies from the numbering conventions described in Table 12-1. It has 256 KB flash, not 128 KB.

# 14. Acronyms

## Table 14-1. Acronyms Used in this Document

| Acronym | Description                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------|

| abus    | analog local bus                                                                                        |

| ADC     | analog-to-digital converter                                                                             |

| AG      | analog global                                                                                           |

| АНВ     | AMBA (advanced microcontroller bus archi-<br>tecture) high-performance bus, an ARM data<br>transfer bus |

| ALU     | arithmetic logic unit                                                                                   |

| AMUXBUS | analog multiplexer bus                                                                                  |

| API     | application programming interface                                                                       |

| APSR    | application program status register                                                                     |

| ARM®    | advanced RISC machine, a CPU architecture                                                               |

| ATM     | automatic thump mode                                                                                    |

| BW      | bandwidth                                                                                               |

| CMRR    | common-mode rejection ratio                                                                             |

| CPU     | central processing unit                                                                                 |

| CRC     | cyclic redundancy check, an error-checking protocol                                                     |

| DAC     | digital-to-analog converter, see also IDAC, VDAC                                                        |

| DFB     | digital filter block                                                                                    |

| DIO     | digital input/output, GPIO with only digital capabilities, no analog. See GPIO.                         |

| DMA     | direct memory access, see also TD                                                                       |

| DNL     | differential nonlinearity, see also INL                                                                 |

| DNU     | do not use                                                                                              |

| DR      | port write data registers                                                                               |

| DSI     | digital system interconnect                                                                             |

| DWT     | data watchpoint and trace                                                                               |

| ECC     | error correcting code                                                                                   |

| ECO     | external crystal oscillator                                                                             |

| EEPROM  | electrically erasable programmable read-only memory                                                     |

| EMI     | electromagnetic interference                                                                            |

| EMIF    | external memory interface                                                                               |

| EOC     | end of conversion                                                                                       |

| EOF     | end of frame                                                                                            |

| EPSR    | execution program status register                                                                       |

| ESD     | electrostatic discharge                                                                                 |

| ETM     | embedded trace macrocell                                                                                |

| FIR     | finite impulse response, see also IIR                                                                   |

| FPB     | flash patch and breakpoint                                                                              |

## Table 14-1. Acronyms Used in this Document (continued)

| Acronym                  | Description                                            |

|--------------------------|--------------------------------------------------------|

| FS                       | full-speed                                             |

| GPIO                     | general-purpose input/output, applies to a PSoC pin    |

| HVI                      | high-voltage interrupt, see also LVI, LVD              |

| IC                       | integrated circuit                                     |

| IDAC                     | current DAC, see also DAC, VDAC                        |

| IDE                      | integrated development environment                     |

| I <sup>2</sup> C, or IIC | Inter-Integrated Circuit, a communications protocol    |

| IIR                      | infinite impulse response, see also FIR                |

| ILO                      | internal low-speed oscillator, see also IMO            |

| IMO                      | internal main oscillator, see also ILO                 |

| INL                      | integral nonlinearity, see also DNL                    |

| I/O                      | input/output, see also GPIO, DIO, SIO, USBIO           |

| IPOR                     | initial power-on reset                                 |

| IPSR                     | interrupt program status register                      |

| IRQ                      | interrupt request                                      |

| ITM                      | instrumentation trace macrocell                        |

| LCD                      | liquid crystal display                                 |

| LIN                      | Local Interconnect Network, a communications protocol. |

| LR                       | link register                                          |

| LUT                      | lookup table                                           |

| LVD                      | low-voltage detect, see also LVI                       |

| LVI                      | low-voltage interrupt, see also HVI                    |

| LVTTL                    | low-voltage transistor-transistor logic                |

| MAC                      | multiply-accumulate                                    |

| MCU                      | microcontroller unit                                   |

| MISO                     | master-in slave-out                                    |

| NC                       | no connect                                             |

| NMI                      | nonmaskable interrupt                                  |

| NRZ                      | non-return-to-zero                                     |

| NVIC                     | nested vectored interrupt controller                   |

| NVL                      | nonvolatile latch, see also WOL                        |

| opamp                    | operational amplifier                                  |

| PAL                      | programmable array logic, see also PLD                 |

| PC                       | program counter                                        |

| РСВ                      | printed circuit board                                  |

| PGA                      | programmable gain amplifier                            |

| PHUB                     | peripheral hub                                         |

| PHY                      | physical layer                                         |