#### Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | 740                                                                             |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 16.8MHz                                                                         |

| Connectivity               | SIO, UART/USART                                                                 |

| Peripherals                | LED, PWM, WDT                                                                   |

| Number of I/O              | 56                                                                              |

| Program Memory Size        | 48KB (48K x 8)                                                                  |

| Program Memory Type        | QzROM                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LFQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m38039gchhp-u0 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

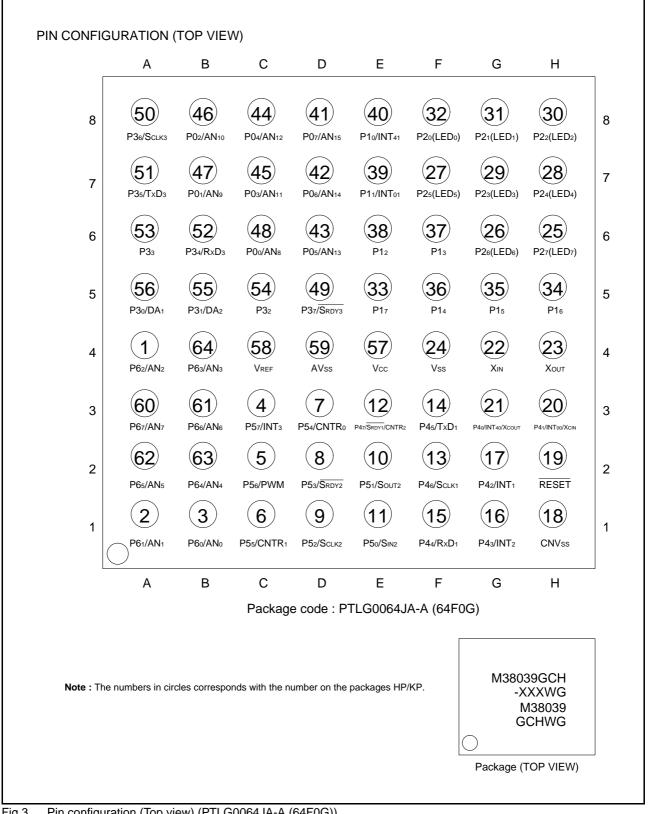

Pin configuration (Top view) (PTLG0064JA-A (64F0G)) Fig 3.

# Table 1 Performance overview

| Parameter                            |                                |                                         | Function                                                              |                                                                          |  |  |  |

|--------------------------------------|--------------------------------|-----------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|--|

| Number of basic in                   | structions                     |                                         |                                                                       | 71                                                                       |  |  |  |

| Minimum instructio                   | n execution time               |                                         |                                                                       | 0.24 μs (Oscillation frequency 16.8 MHz)                                 |  |  |  |

| Oscillation frequency                |                                |                                         |                                                                       | 16.8 MHz (Maximum)                                                       |  |  |  |

| Memory sizes                         |                                |                                         | ROM                                                                   | 16 to 48 Kbytes                                                          |  |  |  |

| RAM                                  |                                |                                         | 2048 Kbytes                                                           |                                                                          |  |  |  |

| I/O port P0, P1, P2, P3, P4, P5, P6  |                                |                                         |                                                                       | 56 pins                                                                  |  |  |  |

| Software pull-up re                  | sistors                        |                                         |                                                                       | Built-in                                                                 |  |  |  |

| Interrupt                            |                                |                                         | 21 sources, 16 vectors (8 external, 12 internal, 1 software)          |                                                                          |  |  |  |

| Timer                                |                                |                                         |                                                                       | 8-bit $\times$ 4 (with 8-bit prescaler)<br>16-bit $\times$ 1             |  |  |  |

| Serial interface                     |                                |                                         |                                                                       | 8-bit × 2 (UART or Clock-synchronized)<br>8-bit × 1 (Clock-synchronized) |  |  |  |

| PWM                                  |                                |                                         |                                                                       | 8-bit × 1 (with 8-bit prescaler)                                         |  |  |  |

| A/D converter                        |                                |                                         |                                                                       | 10-bit × 16 channels (8-bit reading enabled)                             |  |  |  |

| D/A converter                        |                                |                                         |                                                                       | 8-bit × 2 channels                                                       |  |  |  |

| Watchdog timer                       |                                |                                         | 16-bit × 1                                                            |                                                                          |  |  |  |

| LED direct drive port                |                                |                                         | 8 (average current: 10 mA, peak current: 20 mA, total current: 80 mA) |                                                                          |  |  |  |

| Clock generating circuits            |                                |                                         |                                                                       | Built-in 2 circuits                                                      |  |  |  |

|                                      |                                |                                         | (connect to external ceramic resonator or quartz-crystal oscillator)  |                                                                          |  |  |  |

| Power source                         | In high-speed mode             | At 16.8 MHz                             |                                                                       | 4.5 to 5.5 V                                                             |  |  |  |

| voltage                              |                                | At 12.5 MHz<br>At 8.4 MHz<br>At 4.2 MHz |                                                                       | 4.0 to 5.5 V                                                             |  |  |  |

|                                      |                                |                                         |                                                                       | 2.7 to 5.5 V                                                             |  |  |  |

|                                      |                                |                                         |                                                                       | 2.2 to 5.5 V                                                             |  |  |  |

|                                      |                                | At 2.1 MHz                              |                                                                       | 2.0 to 5.5 V                                                             |  |  |  |

|                                      | In middle-speed mode           | At 16.8 MHz                             |                                                                       | 4.5 to 5.5 V                                                             |  |  |  |

|                                      |                                | At 12.5 MHz<br>At 8.4 MHz<br>At 6.3 MHz |                                                                       | 2.7 to 5.5 V                                                             |  |  |  |

|                                      |                                |                                         |                                                                       | 2.2 to 5.5 V<br>1.8 to 5.5 V                                             |  |  |  |

|                                      |                                |                                         |                                                                       |                                                                          |  |  |  |

|                                      | In low-speed mode              | At 32 kHz                               |                                                                       | 1.8 to 5.5 V                                                             |  |  |  |

| Power dissipation In high-speed mode |                                |                                         | Std. 40 mW (Vcc=5.0V, f(XIN)=16.8 MHz, Ta=25 °C)                      |                                                                          |  |  |  |

|                                      | In low-speed mode              |                                         |                                                                       | Std. 45 μW (Vcc=3.0V, f(XiN)=Stop, f(XciN)=32kHz, Ta=25 °C)              |  |  |  |

| Input/Output                         | Input/Output withstand voltage |                                         |                                                                       | Vcc                                                                      |  |  |  |

| characteristics                      | acteristics Output current     |                                         |                                                                       | 10 mA                                                                    |  |  |  |

| Operating temperature range          |                                |                                         | -20 to 85 °C                                                          |                                                                          |  |  |  |

| Device structure                     |                                |                                         | CMOS silicon gate                                                     |                                                                          |  |  |  |

| Package                              |                                |                                         |                                                                       | 64-pin plastic molded SDIP/LQFP/FLGA                                     |  |  |  |

#### Support products Table 3

| Product name         QzROM size (bytes)<br>ROM size for User in ()         RAM size<br>(bytes)         Package         Remarks           M38039G4H-XXXHP         16384         PLQP0064KB-A (64P6Q-A)         PLQP0064KB-A (64P6Q-A)         PLQP0064GA-A (64P6U-A)         PLQP0064GA-A (64P6U-A)         PLQP0064KB-A (64P6Q-A)         PLQP0064KB-A (64P6Q-A)         PLQP0064KB-A (64P6Q-A)         PLQP0064KB-A (64P6Q-A)         PLQP0064GA-A (64P6U-A)         PLQP0064GA-A ( |                 |                                 |         | 1                      | 1                        |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------|---------|------------------------|--------------------------|--|--|

| M38039G4H-XXXHP         16384         PLQP0064KB-A (64P6Q-A)           M38039G4H-XXXKP         (16254) (3)         PLQP0064KB-A (64P6Q-A)           M38039G6H-XXXHP         24576         PLQP0064KB-A (64P6Q-A)           M38039G8H-XXXHP         32768         PLQP0064KB-A (64P6Q-A)           M38039GCH-XXXKP         (32638) (3)         PLQP0064KB-A (64P6Q-A)           M38039GCH-XXXKP         (32638) (3)         PLQP0064KB-A (64P6Q-A)           M38039GCH-XXXKP         49152         PLQP0064KB-A (64P6Q-A)           M38039GCH-XXXWG         49152         PLQP0064KB-A (64P6Q-A)           M38039GCH-XXXWG         16384         PLQP0064KB-A (64P6Q-A)           M38039GCH-XXXWG         16384         PLQP0064KB-A (64P6Q-A)           M38039GCH-XXXWG         16384         PLQP0064KB-A (64P6Q-A)           M38039GCH-XXXWG         16384         PLQP0064KB-A (64P6Q-A)           M38039G6HHP         16384         PLQP0064KB-A (64P6Q-A)           M38039G6HSP         24576         PLQP0064KB-A (64P6Q-A)           M38039G6HKP         24576         PLQP0064KB-A (64P6Q-A)           M38039G6HKP         24576         PLQP0064KB-A (64P6Q-A)           M38039G6HKP         24576         PLQP0064KB-A (64P6Q-A)           M38039G6HKP         32768         PLQP0064KB-A (64P6                                                                                                                                                                                                                                                                                                         | Product name    |                                 |         | Package                | Remarks                  |  |  |

| M38039G4H-XXXKP       (16254) ( <sup>3</sup> )       PLQP0064GA-A (64P6U-A)       QzROM version         M38039G6H-XXXKP       (24446) ( <sup>3</sup> )       PLQP0064KB-A (64P6Q-A)       QzROM version         M38039G6H-XXXKP       (24446) ( <sup>3</sup> )       PLQP0064KB-A (64P6Q-A)       QzROM version         M38039G6H-XXXKP       (32638) ( <sup>3</sup> )       PLQP0064GA-A (64P6Q-A)       PLQP0064GA-A (64P6Q-A)       PLQP0064GA-A (64P6Q-A)         M38039GCH-XXXKP       (32638) ( <sup>3</sup> )       PLQP0064GA-A (64P6Q-A)       PLQP0064GA-A (64P6Q-A)       Programmed shipment         M38039GCH-XXXWG       49152       (49022) ( <sup>3</sup> )       PLQP0064GA-A (64P6Q-A)       PLQP0064GA-A (64P6Q-A)       Programmed shipment         M38039GCH-XXXWG       16384       (16254) ( <sup>3</sup> )       PLQP0064GA-A (64P6Q-A)       PLQP0064BA-A (64P6Q-A)       PLQP0064BA-A (64P6Q-A)         M38039G6HHP       24576       24576       PLQP0064GA-A (64P6Q-A)       PLQP0064GA-A (64P6Q-A)       PLQP0064GA-A (64P6Q-A)       QzROM version (blank) ( <sup>2</sup> )         M38039G6HKP       32768       PLQP0064GA-A (64P6Q-A)       PLQP0064GA-A (64P6Q-A)       QzROM version (blank) ( <sup>2</sup> )                                                                                                                                                                                                                                                                                                                                                                  |                 | .,                              | (bytes) |                        |                          |  |  |

| M38039G6H-XXXHP       24576         M38039G6H-XXXKP       (24446) (3)         M38039G6H-XXXKP       (24446) (3)         M38039G8H-XXXHP       32768         M38039G8H-XXXKP       (32638) (3)         M38039GCH-XXXKP       (32638) (3)         M38039GCH-XXXKP       (32638) (3)         M38039GCH-XXXKP       (49022) (3)         M38039GCH-XXXWG       PLQP0064KB-A (64P6Q-A)         M38039GCH-XXXWG       PLQP0064KB-A (64F0G)         M38039GAHKP       16384         M38039G6HSP       24576         M38039G6HKP       24576         M38039G6HKP       PLQP0064KB-A (64P6Q-A)         PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)         PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)         PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)         PLQP0064KB-A (64P4B)       PLQP0064KB-A (64P4B)         M38039G8HSP       32768       PLQP0064KB-A (64P4B)         M38039G8HHP       32768                                                                                                                                                                                                                                                                                                                                                                                                                        | M38039G4H-XXXHP |                                 |         | . ,                    |                          |  |  |

| M38039G6H-XXXKP       (24446) ( <sup>3</sup> )       PLQP0064GA-A (64P6U-A)       QzROM version         M38039G8H-XXXKP       (32638) ( <sup>3</sup> )       PLQP0064KB-A (64P6Q-A)       PLQP0064GA-A (64P6U-A)       PLQP0064GA-A (64P6U-A)         M38039GCH-XXXKP       (49022) ( <sup>3</sup> )       PLQP0064GA-A (64P6U-A)       PLQP0064GA-A (64P6U-A)       PLQP0064GA-A (64P6U-A)         M38039GCH-XXXWG       49152       (49022) ( <sup>3</sup> )       PLQP0064GA-A (64P6U-A)       PLQP0064GA-A (64P6U-A)         M38039GCH-XXXWG       16384       (16254) ( <sup>3</sup> )       PTLG0064JA-A (64F0G)       PTLG0064JA-A (64F6Q-A)         M38039G6HSP       16384       (16254) ( <sup>3</sup> )       2048       PLQP0064GA-A (64P6Q-A)       PLQP0064GA-A (64P6Q-A)         M38039G6HSP       24576       (24446) ( <sup>3</sup> )       PLQP0064GA-A (64P6Q-A)       PLQP0064GA-A (64P6Q-A)       QzROM version (blank) ( <sup>2</sup> )         M38039G8HSP       32768       92768       PLQP0064BA-A (64P6Q-A)       PLQP0064BA-A (64P6Q-A)       QzROM version (blank) ( <sup>2</sup> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | M38039G4H-XXXKP | (16254) <sup>(3)</sup>          |         | PLQP0064GA-A (64P6U-A) |                          |  |  |

| M38039G8H-XXXHP       32768       QzROM version         M38039G8H-XXXKP       (32638) (3)       PLQP0064KB-A (64P6Q-A)       Programmed shipment         M38039G8H-XXXKP       (32638) (3)       PLQP0064KB-A (64P6Q-A)       Programmed shipment         M38039GCH-XXXKP       (49022) (3)       PLQP0064KB-A (64P6Q-A)       Programmed shipment         M38039GCH-XXXWG       (49022) (3)       PLQP0064KB-A (64P6Q-A)       Programmed shipment         M38039GCH-XXXWG       16384       PLQP0064KB-A (64P6Q-A)       Programmed shipment         M38039G4HSP       16384       PLQP0064KB-A (64F0G)       Programmed shipment         M38039G6HSP       24576       PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)         M38039G6HKP       24576       PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)         M38039G6HKP       24576       PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)         M38039G6HKP       24576       PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)         M38039G8HSP       32768       PLQP0064KB-A (64P6Q-A)       QzROM version (blank) (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | M38039G6H-XXXHP | 24576                           |         | PLQP0064KB-A (64P6Q-A) |                          |  |  |

| M38039G8H-XXXHP       32768       PLQP0064KB-A (64P6Q-A)       Programmed shipment         M38039GCH-XXXKP       (32638) (3)       PLQP0064KB-A (64P6U-A)       PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)         M38039GCH-XXXKP       (49022) (3)       PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)         M38039GCH-XXXWG       16384       (16254) (3)       PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)         M38039G6HSP       16384       (16254) (3)       2048       PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)         M38039G6HSP       24576       (24446) (3)       PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)         M38039G6HKP       32768       32768       PLQP0064KB-A (64P4B)       QzROM version (blank) (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | M38039G6H-XXXKP | (24446) <sup>(3)</sup>          |         | PLQP0064GA-A (64P6U-A) |                          |  |  |

| M38039G8H-XXXKP       (32638) (3)         M38039GCH-XXXKP       49152         M38039GCH-XXXKP       (49022) (3)         M38039GCH-XXXWG       PLQP0064GA-A (64P6Q-A)         M38039GCH-XXXWG       PLQP0064GA-A (64P6Q-A)         M38039GCH-XXXWG       PLQP0064GA-A (64P6Q-A)         M38039GAHSP       16384         M38039G4HKP       (16254) (3)         M38039G6HSP       24576         M38039G6HKP       24576         M38039G6HKP       24576         M38039G8HSP       32768                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | M38039G8H-XXXHP | 32768                           |         | PLQP0064KB-A (64P6Q-A) |                          |  |  |

| M38039GCH-XXXKP       49152<br>(49022) <sup>(3)</sup> M38039GCH-XXXWG       PLQP0064GA-A (64P6U-A)         M38039GCH-XXXWG       PTLG0064JA-A (64F0G)         M38039GCH-XXXWG       PRDP0064BA-A (64F0G)         M38039G4HSP       16384<br>(16254) <sup>(3)</sup> M38039G6HSP       24576<br>(24446) <sup>(3)</sup> M38039G6HKP       24576<br>(24446) <sup>(3)</sup> M38039G6HKP       24576<br>(24446) <sup>(3)</sup> M38039G8HSP       32768                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | M38039G8H-XXXKP | (32638) <sup>(3)</sup>          |         | PLQP0064GA-A (64P6U-A) | (i rogrammed snipment) ( |  |  |

| M38039GCH-XXXKP       (49022) (3)         M38039GCH-XXXWG       (49022) (3)         M38039GCH-XXXWG       PLQP0064GA-A (64P6U-A)         M38039G4HSP       16384         M38039G4HKP       (16254) (3)         M38039G6HSP       24576         M38039G6HKP       24576         M38039G6HKP       (24446) (3)         M38039G8HSP       32768                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | M38039GCH-XXXHP | 40152                           |         | PLQP0064KB-A (64P6Q-A) |                          |  |  |

| M38039GCH-XXXWG       PTLG0064JA-A (64F0G)         M38039G4HSP       16384         M38039G4HKP       (16254) (3)         M38039G6HSP       24576         M38039G6HHP       (24446) (3)         M38039G6HKP       24576         M38039G8HSP       32768                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | M38039GCH-XXXKP |                                 |         | PLQP0064GA-A (64P6U-A) |                          |  |  |

| M38039G4HHP       16384<br>(16254) <sup>(3)</sup> 2048       PLQP0064KB-A (64P6Q-A)<br>PLQP0064GA-A (64P6U-A)         M38039G6HSP       24576<br>(24446) <sup>(3)</sup> PLQP0064KB-A (64P4B)       PLQP0064KB-A (64P6Q-A)         M38039G6HKP       24576<br>(24446) <sup>(3)</sup> PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)         M38039G8HSP       32768       PLQP0064KB-A (64P4B)       QzROM version<br>(blank) <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | M38039GCH-XXXWG | (49022) (9                      |         | PTLG0064JA-A (64F0G)   |                          |  |  |

| M38039G4HHP       (16254) <sup>(3)</sup> 2048       PLQP0064KB-A (64P6Q-A)         M38039G6HSP       24576       PLQP0064KB-A (64P4B)         M38039G6HKP       24576       PLQP0064KB-A (64P6Q-A)         M38039G6HKP       24576       PLQP0064KB-A (64P6Q-A)         M38039G6HKP       PLQP0064KB-A (64P6Q-A)       PLQP0064KB-A (64P6Q-A)         M38039G8HSP       32768       PLQP0064KB-A (64P4B)         M38039G8HHP       32768       PLQP0064KB-A (64P6Q-A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | M38039G4HSP     | 16204                           |         | PRDP0064BA-A (64F4B)   |                          |  |  |

| M38039G4HKP       PLQP0064GA-A (64P6U-A)         M38039G6HSP       24576         M38039G6HHP       (24446) ( <sup>3</sup> )         M38039G6HKP       PLQP0064KB-A (64P6Q-A)         M38039G8HSP       32768         M38039G8HHP       32768                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | M38039G4HHP     |                                 | 2049    | PLQP0064KB-A (64P6Q-A) |                          |  |  |

| M38039G6HHP         24576<br>(24446) <sup>(3)</sup> PLQP0064KB-A (64P6Q-A)         QzROM version           M38039G6HKP         32768         PLQP0064KB-A (64P4B)         QzROM version           M38039G8HHP         32768         PLQP0064KB-A (64P6Q-A)         QzROM version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | M38039G4HKP     | (10234)                         | 2040    | PLQP0064GA-A (64P6U-A) |                          |  |  |

| M38039G6HHP         PLQP0064KB-A (64P6Q-A)           M38039G6HKP         PLQP0064GA-A (64P6U-A)           M38039G8HSP         32768           M38039G8HHP         32768                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | M38039G6HSP     | 24576                           |         | PRDP0064BA-A (64P4B)   |                          |  |  |

| M38039G6HKP         PLQP0064GA-A (64P6U-A)         QzROM version           M38039G8HSP         32768         PRDP0064BA-A (64P4B)         (blank) <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | M38039G6HHP     |                                 |         | PLQP0064KB-A (64P6Q-A) |                          |  |  |

| M38039G8HSP 32768 PRDP0064BA-A (64P4B) (blank) <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | M38039G6HKP     | (24440) (37                     |         | PLQP0064GA-A (64P6U-A) |                          |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | M38039G8HSP     | 32768<br>(32638) <sup>(3)</sup> |         | PRDP0064BA-A (64P4B)   |                          |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | M38039G8HHP     |                                 |         | PLQP0064KB-A (64P6Q-A) |                          |  |  |

| M38039G8HKP PLQP0064GA-A (64P6U-A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | M38039G8HKP     |                                 |         | PLQP0064GA-A (64P6U-A) |                          |  |  |

| M38039GCHSP PRDP0064BA-A (64P4B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | M38039GCHSP     |                                 |         | PRDP0064BA-A (64P4B)   | 1                        |  |  |

| M38039GCHHP 49152 PLQP0064KB-A (64P6Q-A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | M38039GCHHP     | 49152                           |         | PLQP0064KB-A (64P6Q-A) | ]                        |  |  |

| M38039GCHKP (49022) <sup>(3)</sup> PLQP0064GA-A (64P6U-A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | M38039GCHKP     | (49022) <sup>(3)</sup>          |         | PLQP0064GA-A (64P6U-A) | 1                        |  |  |

| M38039GCHWG PTLG0064JA-A (64F0G)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | M38039GCHWG     |                                 |         | PTLG0064JA-A (64F0G)   | 1                        |  |  |

NOTES:

This means a shipment of which User ROM has been programmed.

The user ROM area of a blank product is blank.

ROM size includes the ID code protect area.

## [Processor status register (PS)]

The processor status register is an 8-bit register consisting of 5 flags which indicate the status of the processor after an arithmetic operation and 3 flags which decide MCU operation. Branch operations can be performed by testing the Carry (C) flag, Zero (Z) flag, Overflow (V) flag, or the Negative (N) flag. In decimal mode, the Z, V, N flags are not valid.

## Bit 0: Carry flag (C)

The C flag contains a carry or borrow generated by the arithmetic logic unit (ALU) immediately after an arithmetic operation. It can also be changed by a shift or rotate instruction.

## Bit 1: Zero flag (Z)

The Z flag is set if the result of an immediate arithmetic operation or a data transfer is "0", and cleared if the result is anything other than "0".

## Bit 2: Interrupt disable flag (I)

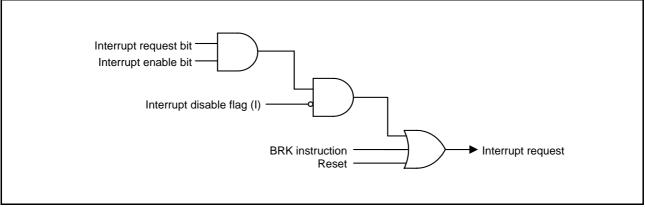

The I flag disables all interrupts except for the interrupt generated by the BRK instruction. Interrupts are disabled when the I flag is "1".

## Bit 3: Decimal mode flag (D)

The D flag determines whether additions and subtractions are executed in binary or decimal. Binary arithmetic is executed when this flag is "0"; decimal arithmetic is executed when it is "1".

Decimal correction is automatic in decimal mode. Only the ADC and SBC instructions can execute decimal arithmetic.

## Bit 4: Break flag (B)

The B flag is used to indicate that the current interrupt was generated by the BRK instruction. The BRK flag in the processor status register is always "0". When the BRK instruction is used to generate an interrupt, the processor status register is pushed onto the stack with the break flag set to "1".

## Bit 5: Index X mode flag (T)

When the T flag is "0", arithmetic operations are performed between accumulator and memory. When the T flag is "1", direct arithmetic operations and direct data transfers are enabled between memory locations.

## Bit 6: Overflow flag (V)

The V flag is used during the addition or subtraction of one byte of signed data. It is set if the result exceeds +127 to -128. When the BIT instruction is executed, bit 6 of the memory location operated on by the BIT instruction is stored in the overflow flag.

## Bit 7: Negative flag (N)

The N flag is set if the result of an arithmetic operation or data transfer is negative. When the BIT instruction is executed, bit 7 of the memory location operated on by the BIT instruction is stored in the negative flag.

Table 5Set and clear instructions of each bit of processor status register

|                   | C flag | Z flag | l flag | D flag | B flag | T flag | V flag | N flag |

|-------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Set instruction   | SEC    | -      | SEI    | SED    | -      | SET    | -      | -      |

| Clear instruction | CLC    | -      | CLI    | CLD    | -      | CLT    | CLV    | —      |

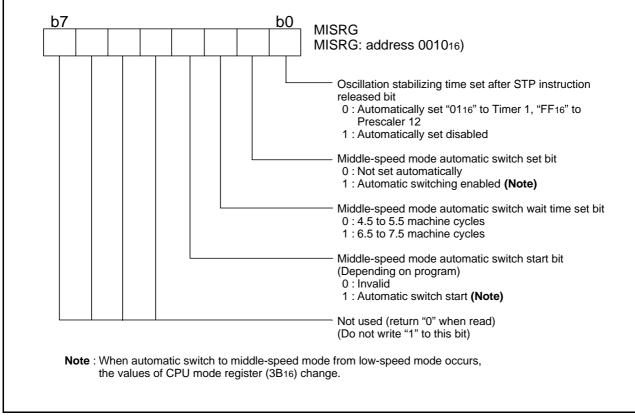

## MISRG

# (1) Bit 0 of address 001016: Oscillation stabilizing time set after STP instruction released bit

When the MCU stops the clock oscillation by the STP instruction and the STP instruction has been released by an external interrupt source, usually, the fixed values of Timer 1 and Prescaler 12 (Timer 1 = 0116, Prescaler 12 = FF16) are automatically reloaded in order for the oscillation to stabilize. The user can inhibit the automatic setting by setting "1" to bit 0 of MISRG (address 001016).

However, by setting this bit to "1", the previous values, set just before the STP instruction was executed, will remain in Timer 1 and Prescaler 12. Therefore, you will need to set an appropriate value to each register, in accordance with the oscillation stabilizing time, before executing the STP instruction.

Figure 10 shows the structure of MISRG.

#### (2) Bits 1, 2, 3 of address 001016: Middle-speed Mode Automatic Switch Function

In order to switch the clock mode of an MCU which has a sub-clock, the following procedure is necessary:

set CPU mode register (003B16) --> start main clock oscillation --> wait for oscillation stabilization --> switch to middle-speed mode (or high-speed mode).

However, the 3803 group (Spec.H QzROM version) has the built-in function which automatically switches from low to middle-speed mode by program.

#### Middle-speed mode automatic switch by program

The middle-speed mode can also be automatically switched by program while operating in low-speed mode. By setting the middle-speed automatic switch start bit (bit 3) of MISRG (address 001016) to "1" in the condition that the middlespeed mode automatic switch set bit is "1" while operating in low-speed mode, the MCU will automatically switch to middle-speed mode. In this case, the oscillation stabilizing time of the main clock can be selected by the middle-speed automatic switch wait time set bit (bit 2) of MISRG (address 001016).

Fig 10. Structure of MISRG

Fig 20. Interrupt control diagram

## • Interrupt Disable Flag

The interrupt disable flag is assigned to bit 2 of the processor status register. This flag controls the acceptance of all interrupt requests except for the BRK instruction. When this flag is set to "1", the acceptance of interrupt requests is disabled. When it is set to "0", acceptance of interrupt requests is enabled. This flag is set to "1" with the SET instruction and set to "0" with the CLI instruction.

When an interrupt request is accepted, the contents of the processor status register are pushed onto the stack while the interrupt disable flag remains set to "0". Subsequently, this flag is automatically set to "1" and multiple interrupts are disabled. To use multiple interrupts, set this flag to "0" with the CLI instruction within the interrupt processing routine.

The contents of the processor status register are popped off the stack with the RTI instruction.

## Interrupt Request Bits

Once an interrupt request is generated, the corresponding interrupt request bit is set to "1" and remains "1" until the request is accepted. When the request is accepted, this bit is automatically set to "0".

Each interrupt request bit can be set to "0", but cannot be set to "1", by software.

## • Interrupt Enable Bits

The interrupt enable bits control the acceptance of the corresponding interrupt requests. When an interrupt enable bit is set to "0", the acceptance of the corresponding interrupt request is disabled. If an interrupt request occurs in this condition, the corresponding interrupt request bit is set to "1", but the interrupt request is not accepted. When an interrupt enable bit is set to "1", acceptance of the corresponding interrupt request is enabled. Each interrupt enable bit can be set to "0" or "1" by software. The interrupt enable bit for an unused interrupt should be set to "0".

## Interrupt Source Selection

Any of the following combinations can be selected by the interrupt source selection register (003916).

- 1. INT0 or timer Z

- 2. CNTR1 or Serial I/O3 reception

- 3. Serial I/O2 or timer Z

- 4. INT4 or CNTR2

- 5. A/D conversion or serial I/O3 transmission

#### • External Interrupt Pin Selection

For external interrupts INT0 and INT4, the INT0, INT4 interrupt switch bit in the interrupt edge selection register (bit 6 of address 003A16) can be used to select INT00 and INT40 pin input or INT01 and INT41 pin input.

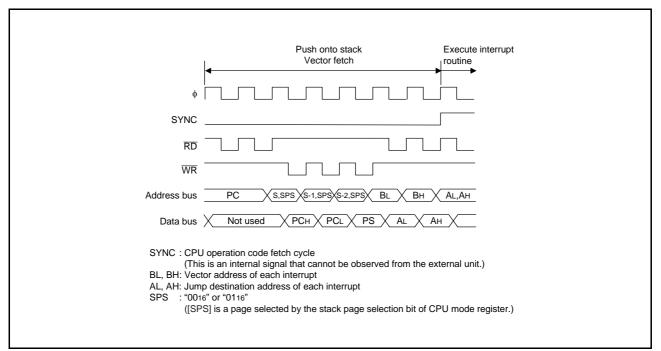

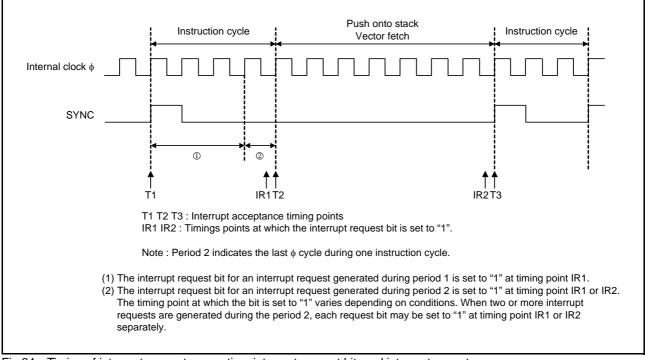

Fig 23. Interrupt sequence

### <Notes>

- The interrupt request bit may be set to "1" in the following cases.

- When setting the external interrupt active edge

- Related bits:

- INT0 interrupt edge selection bit

(bit 0 of interrupt edge selection register (address 003A16)) INT1 interrupt edge selection bit

- (bit 1 of interrupt edge selection register (address 003A16))

- INT2 interrupt edge selection bit

- (bit 3 of interrupt edge selection register (address 003A16))

- INT3 interrupt edge selection bit

- (bit 4 of interrupt edge selection register (address 003A16)) INT4 interrupt edge selection bit

- (bit 5 of interrupt edge selection register (address 003A16)) CNTR0 activate edge switch bit

- (bit 2 of timer XY mode register (address 002316))

- CNTR1 activate edge switch bit

- (bits 6 of timer XY mode register (address 002316))

- CNTR2 activate edge switch bit

- (bits 5 of timer Z mode register (address 002A16))

- When switching the interrupt sources of an interrupt vector address where two or more interrupt sources are assigned Related bits: INT0, INT4 interrupt switch bit (bit 6 of interrupt edge selection register (address 003A16)) INT0/Timer Z interrupt source selection bit (bit 0 of interrupt source selection register (address 003916)) Serial I/O2/Timer Z interrupt source selection bit

- (bit 1 of interrupt source selection register (address 003916)) INT4/CNTR2 interrupt source selection bit

- (bit 4 of interrupt source selection register (address 003916)) CNTR1/Serial I/O3 receive interrupt source selection bit

- (bit 6 of interrupt source selection register (address 003916)) AD conversion/Serial I/O3 transmit interrupt source selection bit

- (bit 6 of interrupt source selection register (address 003916)) If it is not necessary to generate an interrupt synchronized with

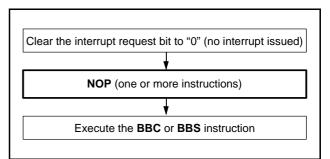

- these settings, take the following sequence.

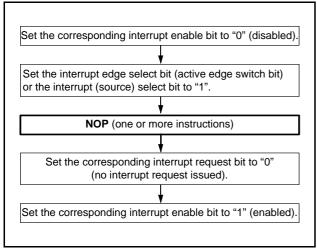

- (1) Set the corresponding enable bit to "0" (disabled).

- (2) Set the interrupt edge selection bit (the active edge switch bit) or the interrupt source bit.

- (3) Set the corresponding interrupt request bit to "0" after one or more instructions have been executed.

- (4) Set the corresponding interrupt enable bit to "1" (enabled).

# TIMERS

#### 8-bit Timers

The 3803 group (Spec.H QzROM version) has four 8-bit timers: timer 1, timer 2, timer X, and timer Y.

The timer 1 and timer 2 use one prescaler in common, and the timer X and timer Y use each prescaler. Those are 8-bit prescalers. Each of the timers and prescalers has a timer latch or a prescaler latch.

The division ratio of each timer or prescaler is given by 1/(n + 1), where n is the value in the corresponding timer or prescaler latch. All timers are down-counters. When the timer reaches "0016", an underflow occurs at the next count pulse and the contents of the corresponding timer latch are reloaded into the timer and the count is continued. When the timer underflows, the interrupt request bit corresponding to that timer is set to "1".

#### • Timer divider

The divider count source is switched by the main clock division ratio selection bits of CPU mode register (bits 7 and 6 at address 003B16). When these bits are "00" (high-speed mode) or "01" (middle-speed mode), XIN is selected. When these bits are "10" (low-speed mode), XCIN is selected.

#### • Prescaler 12

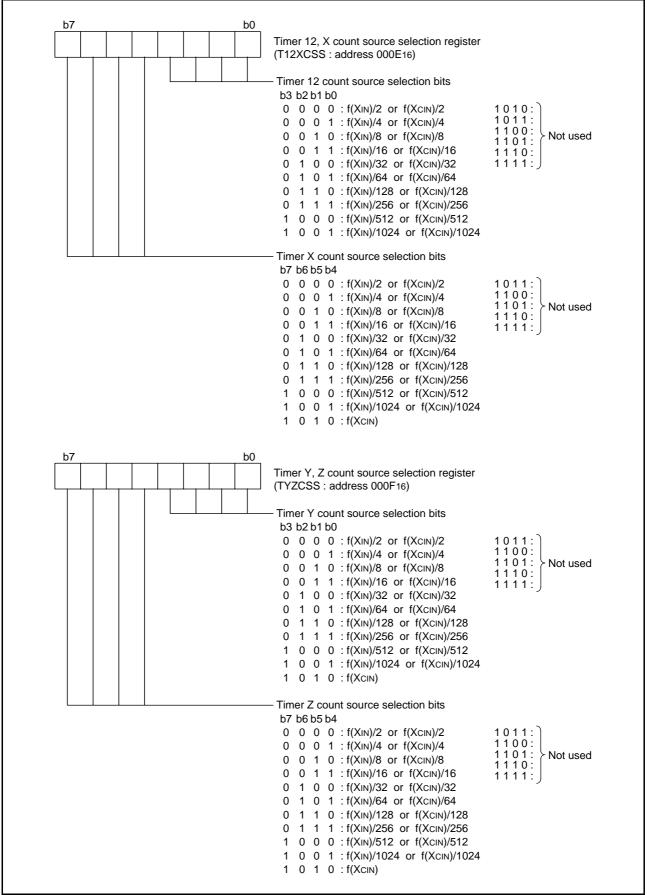

The prescaler 12 counts the output of the timer divider. The count source is selected by the timer 12, X count source selection register among 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1/128, 1/256, 1/512, 1/1024 of f(XIN) or f(XCIN).

#### • Timer 1 and Timer 2

The timer 1 and timer 2 counts the output of prescaler 12 and periodically set the interrupt request bit.

#### • Prescaler X and prescaler Y

The prescaler X and prescaler Y count the output of the timer divider or f(XCIN). The count source is selected by the timer 12, X count source selection register (address 000E16) and the timer Y, Z count source selection register (address 000F16) among 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1/128, 1/256, 1/512, and 1/1024 of f(XIN) or f(XCIN); and f(XCIN).

## • Timer X and Timer Y

The timer X and timer Y can each select one of four operating modes by setting the timer XY mode register (address 002316).

## (1) Timer mode

#### Mode selection

This mode can be selected by setting "00" to the timer X operating mode bits (bits 1 and 0) and the timer Y operating mode bits (bits 5 and 4) of the timer XY mode register (address 002316).

#### · Explanation of operation

The timer count operation is started by setting "0" to the timer X count stop bit (bit 3) and the timer Y count stop bit (bit 7) of the timer XY mode register (address 002316).

When the timer reaches "0016", an underflow occurs at the next count pulse and the contents of timer latch are reloaded into the timer and the count is continued.

#### (2) Pulse Output Mode

#### Mode selection

This mode can be selected by setting "01" to the timer X operating mode bits (bits 1 and 0) and the timer Y operating mode bits (bits 5 and 4) of the timer XY mode register (address 002316).

#### • Explanation of operation

The operation is the same as the timer mode's. Moreover the pulse which is inverted each time the timer underflows is output from CNTR0/CNTR1 pin. Regardless of the timer counting or not the output of CNTR0/CNTR1 pin is initialized to the level of specified by their active edge switch bits when writing to the timer. When the CNTR0 active edge switch bit (bit 2) and the CNTR1 active edge switch bit (bit 6) of the timer XY mode register (address 002316) is "0", the output starts with "H" level. When it is "1", the output starts with "L" level.

Switching the CNTR0 or CNTR1 active edge switch bit will reverse the output level of the corresponding CNTR0 or CNTR1 pin.

#### • Precautions

Set the double-function port of CNTR0/CNTR1 pin and port P54/P55 to output in this mode.

#### (3) Event Counter Mode

#### Mode selection

This mode can be selected by setting "10" to the timer X operating mode bits (bits 1 and 0) and the timer Y operating mode bits (bits 5 and 4) of the timer XY mode register (address 002316).

• Explanation of operation

The operation is the same as the timer mode's except that the timer counts signals input from the CNTR0 or CNTR1 pin. The valid edge for the count operation depends on the CNTR0 active edge switch bit (bit 2) or the CNTR1 active edge switch bit (bit 6) of the timer XY mode register (address 002316). When it is "0", the rising edge is valid. When it is "1", the falling edge is valid.

#### • Precautions

Set the double-function port of CNTR0/CNTR1 pin and port P54/P55 to input in this mode.

Fig 27. Structure of timer 12, X and timer Y, Z count source selection registers

#### <Notes regarding all modes>

#### • Timer Z write control

Which write control can be selected by the timer Z write control bit (bit 3) of the timer Z mode register (address 002A16), writing data to both the latch and the timer at the same time or writing data only to the latch.

When the operation "writing data only to the latch" is selected, the value is set to the timer latch by writing data to the address of timer Z and the timer is updated at next underflow. After reset release, the operation "writing data to both the latch and the timer at the same time" is selected, and the value is set to both the latch and the timer at the same time by writing data to the address of timer Z.

In the case of writing data only to the latch, if writing data to the latch and an underflow are performed almost at the same time, the timer value may become undefined.

#### · Timer Z read control

A read-out of timer value is impossible in pulse period measurement mode and pulse width measurement mode. In the other modes, a read-out of timer value is possible regardless of count operating or stopped. However, a read-out of timer latch value is impossible. · Switch of interrupt active edge of CNTR2 and INT1

Each interrupt active edge depends on setting of the CNTR2 active edge switch bit and the INT1 active edge selection bit.

#### • Switch of count source

When switching the count source by the timer Z count source selection bits, the value of timer count is altered in inconsiderable amount owing to generating of thin pulses on the count input signals.

Therefore, select the timer count source before setting the value to the prescaler and the timer.

#### Usage of CNTR2 pin as normal I/O port P47

To use the CNTR2 pin as normal I/O port P47, set timer Z operating mode bits (b2, b1, b0) of timer Z mode register (address 002A16) to "000".

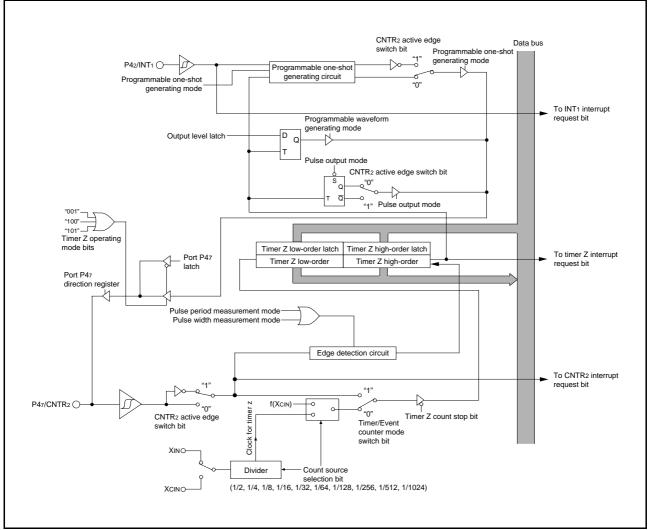

Fig 28. Block diagram of timer Z

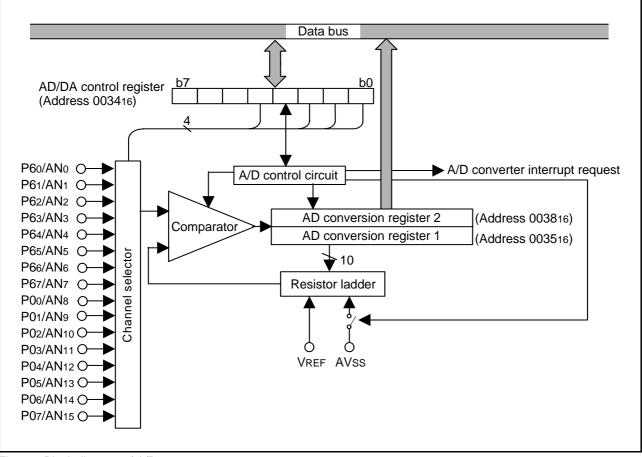

Fig 56. Block diagram of A/D converter

# **RESET CIRCUIT**

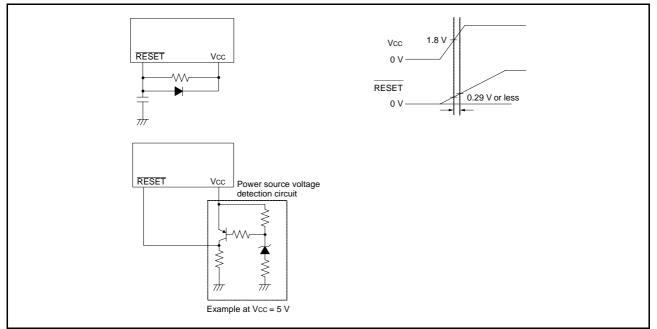

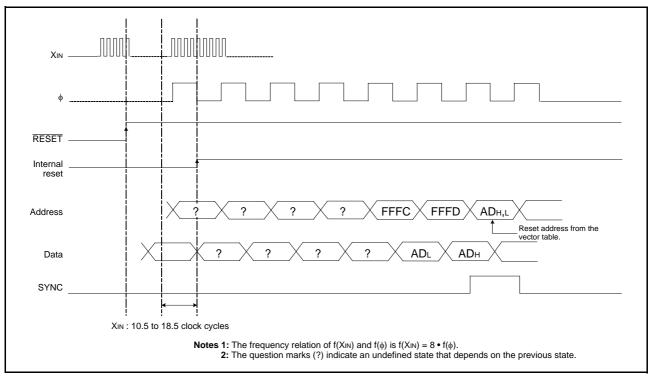

To reset the microcomputer, RESET pin should be held at an "L" level for 16 cycles or more of XIN. Then the RESET pin is returned to an "H" level (the power source voltage should be between 1.8 V and 5.5 V, and the oscillation should be stable), reset is released. After the reset is completed, the program starts from the address contained in address FFFD16 (high-order byte) and address FFFC16 (low-order byte). Make sure that the reset input voltage is less than 0.29 V for VCC of 1.8 V.

Fig 61. Reset circuit example

Fig 62. Reset sequence

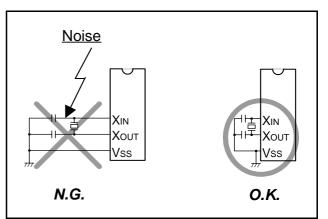

## **CLOCK GENERATING CIRCUIT**

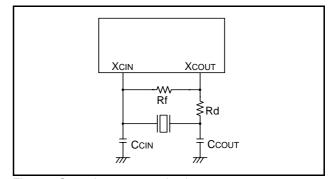

The 3803 group (Spec.H QzROM version) has two built-in oscillation circuits: main clock XIN-XOUT oscillation circuit and sub clock XCIN-XCOUT oscillation circuit. An oscillation circuit can be formed by connecting a resonator between XIN and XOUT (XCIN and XCOUT). Use the circuit constants in accordance with the resonator manufacturer's recommended values. No external resistor is needed between XIN and XOUT since a feed-back resistor exists on-chip.(An external feed-back resistor may be needed depending on conditions.) However, an external feed-back resistor is needed between XCIN and XCOUT.

Immediately after power on, only the XIN oscillation circuit starts oscillating, and XCIN and XCOUT pins function as I/O ports.

#### • Frequency Control

### (1) Middle-speed mode

The internal clock  $\phi$  is the frequency of XIN divided by 8. After reset is released, this mode is selected.

#### (2) High-speed mode

The internal clock  $\phi$  is half the frequency of XIN.

## (3) Low-speed mode

The internal clock  $\phi$  is half the frequency of XCIN.

#### (4) Low power dissipation mode

The low power consumption operation can be realized by stopping the main clock XIN in low-speed mode. To stop the main clock, set bit 5 of the CPU mode register to "1". When the main clock XIN is restarted (by setting the main clock stop bit to "0"), set sufficient time for oscillation to stabilize.

The sub-clock XCIN-XCOUT oscillating circuit can not directly input clocks that are generated externally. Accordingly, make sure to cause an external resonator to oscillate.

# **Oscillation Control**

## (1) Stop mode

If the STP instruction is executed, the internal clock  $\phi$  stops at an "H" level, and XIN and XCIN oscillators stop. When the oscillation stabilizing time set after STP instruction released bit (bit 0 of address 001016) is "0", the prescaler 12 is set to "FF16" and timer 1 is set to "0116". When the oscillation stabilizing time set after STP instruction released bit is "1", set the sufficient time for oscillation of used oscillator to stabilize since nothing is set to the prescaler 12 and timer 1.

After STP instruction is released, the input of the prescaler 12 is connected to count source which had set at executing the STP instruction, and the output of the prescaler 12 is connected to timer 1. Oscillator restarts when an external interrupt is received, but the internal clock  $\phi$  is not supplied to the CPU (remains at "H") until timer 1 underflows. The internal clock  $\phi$  is supplied for the first time, when timer 1 underflows. This ensures time for the clock oscillation using the ceramic resonators to be stabilized. When the oscillator is restarted by reset, apply "L" level to the RESET pin until the oscillation is stable since a wait time will not be generated.

## (2) Wait mode

If the WIT instruction is executed, the internal clock  $\phi$  stops at an "H" level, but the oscillator does not stop. The internal clock  $\phi$  restarts at reset or when an interrupt is received. Since the oscillator does not stop, normal operation can be started immediately after the clock is restarted.

To ensure that the interrupts will be received to release the STP or WIT state, their interrupt enable bits must be set to "1" before executing of the STP or WIT instruction.

When releasing the STP state, the prescaler 12 and timer 1 will start counting the clock XIN divided by 16. Accordingly, set the timer 1 interrupt enable bit to "0" before executing the STP instruction.

#### <Notes>

- If you switch the mode between middle/high-speed and low-speed, stabilize both XIN and XCIN oscillations. The sufficient time is required for the sub clock to stabilize, especially immediately after power on and at returning from stop mode. When switching the mode between middle/high-speed and low-speed, set the frequency on condition that  $f(XIN) > 3 \times f(XCIN)$ .

- When using the quartz-crystal oscillator of high frequency, such as 16 MHz etc., it may be necessary to select a specific oscillator with the specification demanded.

- When using the oscillation stabilizing time set after STP instruction released bit set to "1", evaluate time to stabilize oscillation of the used oscillator and set the value to the timer 1 and prescaler 12.

## 6. Serial Interface

In clock synchronous serial I/O, if <u>the receive</u> side is using an external clock and it is to output the SRDY signal, set the transmit enable bit, the receive enable bit, and the  $\overline{SRDY}$  output enable bit to "1".

Serial I/O1 continues to output the final bit from the TxD1 pin after transmission is completed. SOUT2 pin for serial I/O2 goes to high impedance after transfer is completed.

When in serial I/Os 1 and 3 (clock-synchronous mode) or in serial I/O2, an external clock is used as synchronous clock, write transmission data to the transmit buffer register or serial I/O2 register, during transfer clock is "H".

# 7. A/D Converter

The comparator uses capacitive coupling amplifier whose charge will be lost if the clock frequency is too low.

Therefore, make sure that  $\hat{f}(XIN)$  in the middle/high-speed mode is at least on 500 kHz during an A/D conversion.

Do not execute the STP instruction during an A/D conversion.

## 8. D/A Converter

The accuracy of the D/A converter becomes rapidly poor under the Vcc = 4.0 V or less condition; a supply voltage of Vcc  $\ge$  4.0 V is recommended. When a D/A converter is not used, set all values of DAi conversion registers (i=1, 2) to "0016".

## 9. Instruction Execution Time

The instruction execution time is obtained by multiplying the period of the internal clock  $\phi$  by the number of cycles needed to execute an instruction.

The number of cycles required to execute an instruction is shown in the list of machine instructions.

The period of the internal clock  $\boldsymbol{\varphi}$  is double of the XIN period in high-speed mode.

## 10.Reserved Area, Reserved Bit

Do not write any data to the reserved area in the SFR area and the special page. (Do not change the contents after reset.)

# 11.CPU Mode Register

Be sure to fix bit 3 of the CPU mode register (address  $003B_{16}$ ) to "1".

# **COUNTERMEASURES AGAINST NOISE**

- (1) Shortest wiring length

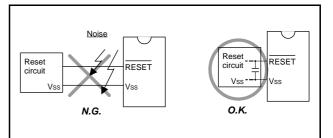

- 1. Wiring for RESET pin

Make the length of wiring which is connected to the RESET pin as short as possible. Especially, connect a capacitor across the RESET pin and the Vss pin with the shortest possible wiring (within 20 mm).

## Reason