Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betalls                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | 8051                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 33MHz                                                                   |

| Connectivity               | EBI/EMI, UART/USART                                                     |

| Peripherals                | POR, PWM, WDT                                                           |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                            |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

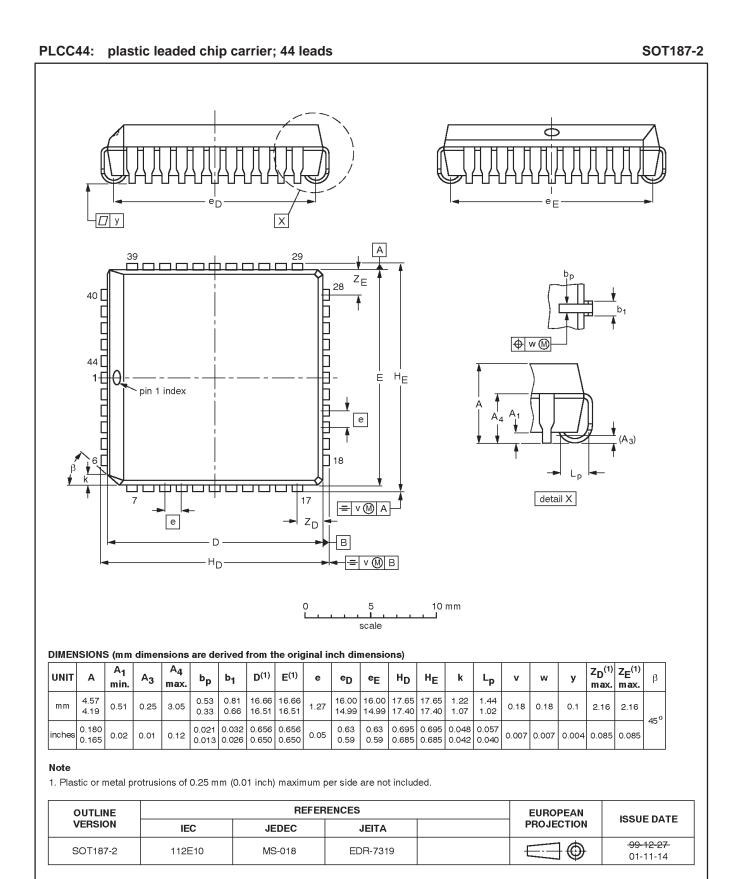

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p87c51ra2fa-512 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Product data

#### DESCRIPTION

The devices are Single-Chip 8-Bit Microcontrollers manufactured in an advanced CMOS process and are derivatives of the 80C51 microcontroller family. The instruction set is 100% compatible with the 80C51 instruction set.

The devices support 6-clock/12-clock mode selection by programming an OTP bit (OX2) using parallel programming. In addition, an SFR bit (X2) in the clock control register (CKCON) also selects between 6-clock/12-clock mode.

The devices also have four 8-bit I/O ports, three 16-bit timer/event counters, a multi-source, four-priority-level, nested interrupt structure, an enhanced UART and on-chip oscillator and timing circuits.

The added features of the P87C51RA2/RB2/RC2/RD2 make it a powerful microcontroller for applications that require pulse width modulation, high-speed I/O and up/down counting capabilities such as motor control.

#### FEATURES

- 80C51 Central Processing Unit

- 8 kbytes OTP (87C51RA2)

- 16 kbytes OTP (87C51RB2)

- 32 kbytes OTP (87C51RC2)

- 64 kbytes OTP (87C51RD2)

- 512 byte RAM (87C51RA2/RB2/RC2)

- 1 kbyte RAM (87C51RD2)

- Boolean processor

- Fully static operation

- Low voltage (2.7 V to 5.5 V at 16 MHz) operation

- 12-clock operation with selectable 6-clock operation (via software or via parallel programmer)

- Memory addressing capability

- Up to 64 kbytes ROM and 64 kbytes RAM

- Power control modes:

- Clock can be stopped and resumed

- Idle mode

- Power-down mode

- CMOS and TTL compatible

- Two speed ranges at V<sub>CC</sub> = 5 V

- 0 to 30 MHz with 6-clock operation

- 0 to 33 MHz with 12-clock operation

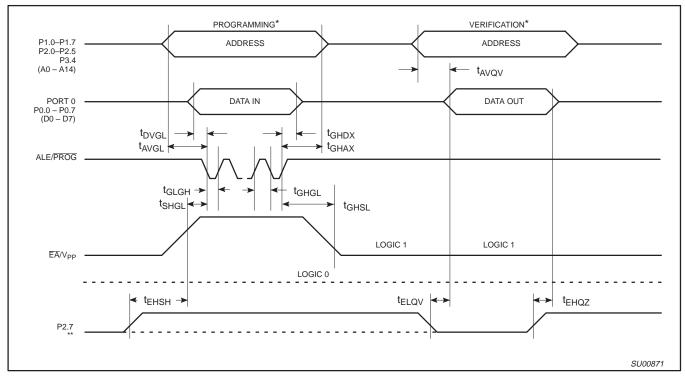

- Parallel programming with 87C51 compatible hardware interface to programmer

- RAM expandable externally to 64 kbytes

- Programmable Counter Array (PCA)

- PWM

- Capture/compare

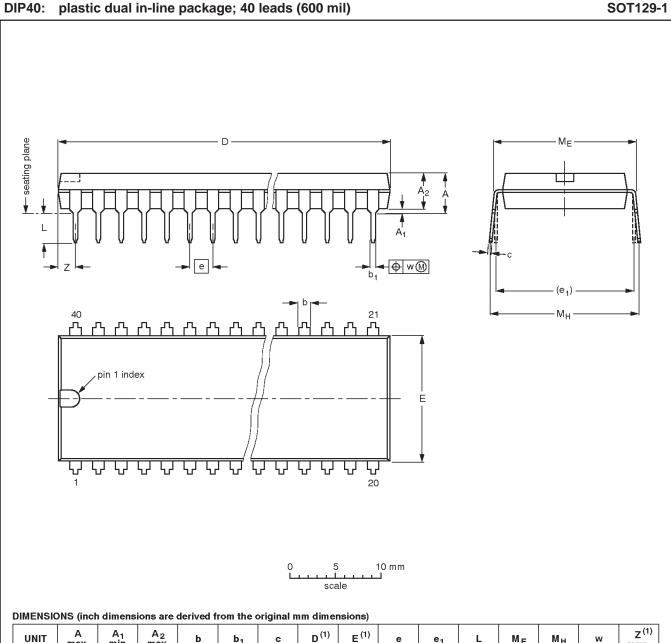

- PLCC, LQFP, or DIP package

- Extended temperature ranges

- Dual Data Pointers

- Security bits (3 bits)

- Encryption array 64 bytes

- Seven interrupt sources

- 4 interrupt priority levels

- Four 8-bit I/O ports

- Full-duplex enhanced UART

- Framing error detection

- Automatic address recognition

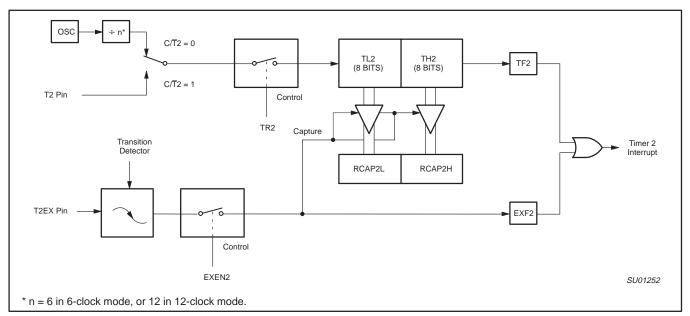

- Three 16-bit timers/counters T0, T1 (standard 80C51) and additional T2 (capture and compare)

- Programmable clock-out pin

- Asynchronous port reset

- Low EMI (inhibit ALE, slew rate controlled outputs, and 6-clock mode)

- Wake-up from Power Down by an external interrupt

## P87C51RA2/RB2/RC2/RD2

#### **PIN DESCRIPTIONS**

|                 | Р     | IN NUMBE     | R             |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-------|--------------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC        | PDIP  | PLCC         | LQFP          | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SS</sub> | 20    | 22           | 16            | I    | Ground: 0 V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>CC</sub> | 40    | 44           | 38            | I    | <b>Power Supply:</b> This is the power supply voltage for normal, idle, and power-down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P0.0–0.7        | 39–32 | 43–36        | 37–30         | I/O  | <b>Port 0:</b> Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application, it uses strong internal pull-ups when emitting 1s.                                                                                                                                                                                                                                                                                                                                                                                                         |

| P1.0-P1.7       | 1–8   | 2–9          | 40–44,<br>1–3 | I/O  | <b>Port 1:</b> Port 1 is an 8-bit bidirectional I/O port with internal pull-ups on all pins. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 1 pins that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: $I_{IL}$ ).                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |       |              |               |      | Alternate functions for P87C51RA2/RB2/RC2/RD2 Port 1 include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 | 1     | 2            | 40            | I/O  | T2 (P1.0): Timer/Counter 2 external count input/Clockout (see Programmable Clock-Out)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 2     | 3            | 41            | 1    | T2EX (P1.1): Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 | 3     | 4            | 42            | 1    | ECI (P1.2): External Clock Input to the PCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 4     | 5            | 43            | I/O  | CEX0 (P1.3): Capture/Compare External I/O for PCA module 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 5     | 6            | 44            | I/O  | CEX1 (P1.4): Capture/Compare External I/O for PCA module 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 6     | 7            | 1             | I/O  | CEX2 (P1.5): Capture/Compare External I/O for PCA module 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 7     | 8            | 2             | I/O  | CEX3 (P1.6): Capture/Compare External I/O for PCA module 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 8     | 9            | 3             | I/O  | CEX4 (P1.7): Capture/Compare External I/O for PCA module 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P2.0–P2.7       | 21–28 | 24–31        | 18–25         | I/O  | <b>Port 2:</b> Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 2 pins that are externally being pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: $I_{IL}$ ). Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOV @Ri), port 2 emits the contents of the P2 special function register. |

| P3.0–P3.7       | 10–17 | 11,<br>13–19 | 5, 7–13       | I/O  | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins that are externally being pulled low will source current because of the pull-ups. (See DC Electrical Characteristics: $I_{IL}$ ). Port 3 also serves the special features of the P87C51RA2/RB2/RC2/RD2, as listed below:                                                                                                                                                                                                                                                                                                               |

|                 | 10    | 11           | 5             | 1    | RxD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 | 11    | 13           | 7             | 0    | TxD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 | 12    | 14           | 8             | 1    | INTO (P3.2): External interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 13    | 15           | 9             |      | INT1 (P3.3): External interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 14    | 16           | 10            |      | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 | 15    | 17           | 11            |      | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 | 16    | 18           | 12            | 0    | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | 17    | 19           | 13            | 0    | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RST             | 9     | 10           | 4             | I    | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ALE             | 30    | 33           | 27            | 0    | Address Latch Enable: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted twice every machine cycle, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. ALE can be disabled by setting SFR auxiliary.0. With this bit set, ALE will be active only during a MOVX instruction.                                                                                                                                                                                                                                                                                                                       |

## P87C51RA2/RB2/RC2/RD2

| MNEMONIC           | Р    | IN NUMBE | R    | ТҮРЕ | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------|------|----------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WINEMONIC          | PDIP | PLCC     | LQFP |      | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PSEN               | 29   | 32       | 26   | 0    | <b>Program Store Enable:</b> The read strobe to external program memory. When executing code from the external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.                                                                                                    |

| EA/V <sub>PP</sub> | 31   | 35       | 29   | I    | <b>External Access Enable/Programming Supply Voltage:</b> EA must be externally held low to enable the device to fetch code from external program memory locations. If EA is held high, the device executes from internal program memory. The value on the EA pin is latched when RST is released and any subsequent changes have no effect. This pin also receives the programming supply voltage (V <sub>PP</sub> ) during programming. |

| XTAL1              | 19   | 21       | 15   | I    | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                         |

| XTAL2              | 18   | 20       | 14   | 0    | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                |

#### NOTE:

To avoid "latch-up" effect at power-on, the voltage on any pin (other than  $V_{PP}$ ) must not be higher than  $V_{CC}$  + 0.5 V or less than  $V_{SS}$  – 0.5 V.

### P87C51RA2/RB2/RC2/RD2

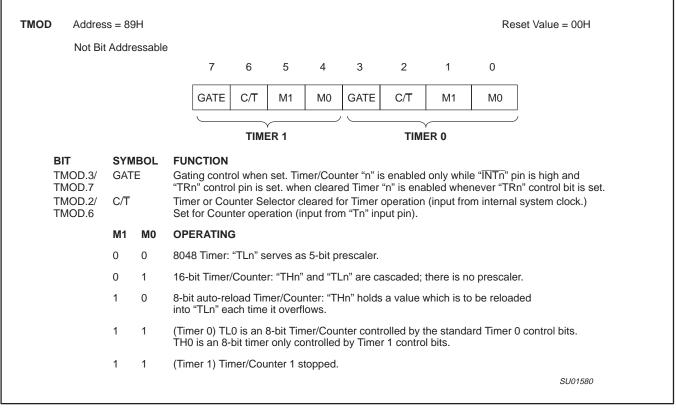

#### **TIMER 0 AND TIMER 1 OPERATION**

#### Timer 0 and Timer 1

The "Timer" or "Counter" function is selected by control bits C/T in the Special Function Register TMOD. These two Timer/Counters have four operating modes, which are selected by bit-pairs (M1, M0) in TMOD. Modes 0, 1, and 2 are the same for both Timers/Counters. Mode 3 is different. The four operating modes are described in the following text.

#### Mode 0

Putting either Timer into Mode 0 makes it look like an 8048 Timer, which is an 8-bit Counter with a divide-by-32 prescaler. Figure 3 shows the Mode 0 operation.

In this mode, the Timer register is configured as a 13-bit register. As the count rolls over from all 1s to all 0s, it sets the Timer interrupt flag TFn. The counted input is enabled to the Timer when TRn = 1 and either GATE = 0 or  $\overline{INTn}$  = 1. (Setting GATE = 1 allows the Timer to be controlled by external input  $\overline{INTn}$ , to facilitate pulse width measurements). TRn is a control bit in the Special Function Register TCON (Figure 4).

The 13-bit register consists of all 8 bits of THn and the lower 5 bits of TLn. The upper 3 bits of TLn are indeterminate and should be ignored. Setting the run flag (TRn) does not clear the registers.

Mode 0 operation is the same for Timer 0 as for Timer 1. There are two different GATE bits, one for Timer 1 (TMOD.7) and one for Timer 0 (TMOD.3).

#### Mode 1

Mode 1 is the same as Mode 0, except that the Timer register is being run with all 16 bits.

#### Mode 2

Mode 2 configures the Timer register as an 8-bit Counter (TLn) with automatic reload, as shown in Figure 5. Overflow from TLn not only sets TFn, but also reloads TLn with the contents of THn, which is preset by software. The reload leaves THn unchanged.

Mode 2 operation is the same for Timer 0 as for Timer 1.

#### Mode 3

Timer 1 in Mode 3 simply holds its count. The effect is the same as setting TR1 = 0.

Timer 0 in Mode 3 establishes TL0 and TH0 as two separate counters. The logic for Mode 3 on Timer 0 is shown in Figure 6. TL0 uses the Timer 0 control bits:  $C/\overline{T}$ , GATE, TR0, and TF0 as well as pin INT0. TH0 is locked into a timer function (counting machine cycles) and takes over the use of TR1 and TF1 from Timer 1. Thus, TH0 now controls the "Timer 1" interrupt.

Mode 3 is provided for applications requiring an extra 8-bit timer on the counter. With Timer 0 in Mode 3, an 80C51 can look like it has three Timer/Counters. When Timer 0 is in Mode 3, Timer 1 can be turned on and off by switching it out of and into its own Mode 3, or can still be used by the serial port as a baud rate generator, or in fact, in any application not requiring an interrupt.

Figure 2. Timer/Counter 0/1 Mode Control (TMOD) Register

80C51 8-bit microcontroller family 8KB/16KB/32KB/64KB OTP with 512B/1KB RAM, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

#### Table 3. Timer 2 Operating Modes

| RCLK + TCLK | CP/RL2 | TR2 | MODE                |

|-------------|--------|-----|---------------------|

| 0           | 0      | 1   | 16-bit Auto-reload  |

| 0           | 1      | 1   | 16-bit Capture      |

| 1           | Х      | 1   | Baud rate generator |

| Х           | Х      | 0   | (off)               |

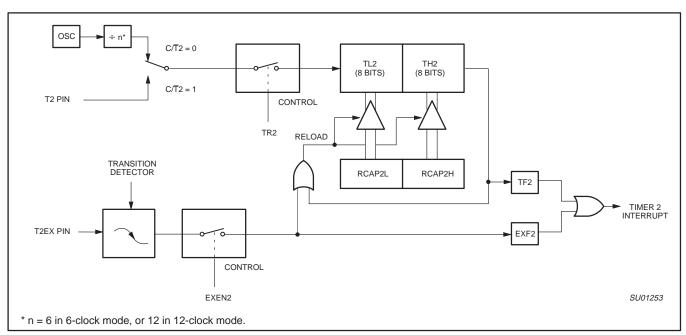

Figure 2. Timer 2 in Capture Mode

|        | Not Dit | Addressat  |               |                |             |             |              |             |         |  |

|--------|---------|------------|---------------|----------------|-------------|-------------|--------------|-------------|---------|--|

|        |         | Audressa   | Jie           |                | 1           |             |              |             |         |  |

|        |         | —          | —             | _              | _           | —           | _            | T2OE        | DCEN    |  |

|        | Bit     | 7          | 6             | 5              | 4           | 3           | 2            | 1           | 0       |  |

| Symbol | Functi  | on         |               |                |             |             |              |             |         |  |

| _      | Not im  | plemented  | d, reserved f | or future use  | э.*         |             |              |             |         |  |

| T2OE   | Timer   | 2 Output E | nable bit.    |                |             |             |              |             |         |  |

|        | Down    | Count Ena  | able bit. Whe | en set, this a | llows Timer | 2 to be con | figured as a | n up/down c | ounter. |  |

| DCEN   |         |            |               |                |             |             |              |             |         |  |

Figure 3. Timer 2 Mode (T2MOD) Control Register

## 80C51 8-bit microcontroller family 8KB/16KB/32KB/64KB OTP with 512B/1KB RAM, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

Figure 4. Timer 2 in Auto-Reload Mode (DCEN = 0)

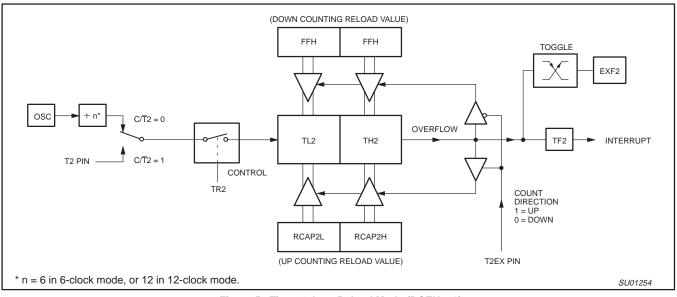

Figure 5. Timer 2 Auto Reload Mode (DCEN = 1)

## P87C51RA2/RB2/RC2/RD2

|      |           | 7      | 6                          | 5             | 4      | 3   | 2   | 1   | 0      |

|------|-----------|--------|----------------------------|---------------|--------|-----|-----|-----|--------|

|      | IP (0B8H) | -      | PPC                        | PT2           | PS     | PT1 | PX1 | PT0 | PX0    |

|      |           |        | Bit = 1 ass<br>Bit = 0 ass |               |        |     |     |     |        |

| BIT  | SYMBOL    | FUNC   | TION                       |               |        |     |     |     |        |

| IP.7 | -         | -      |                            |               |        |     |     |     |        |

| IP.6 | PPC       | PCA ir | nterrupt pr                | iority bit    |        |     |     |     |        |

| IP.5 | PT2       | Timer  | 2 interrup                 | priority b    | it.    |     |     |     |        |

| IP.4 | PS        | Serial | Port interi                | upt priorit   | y bit. |     |     |     |        |

| IP.3 | PT1       | Timer  | 1 interrup                 | priority b    | it.    |     |     |     |        |

| IP.2 | PX1       | Extern | al interrup                | ot 1 priority | y bit. |     |     |     |        |

| IP.1 | PT0       | Timer  | 0 interrup                 | priority b    | it.    |     |     |     |        |

| IP.0 | PX0       | Extern | al interrup                | ot 0 priority | y bit. |     |     |     | SU0129 |

#### Figure 16. IP Registers

|       | _      | 7      | 6                          | 5             | 4           | 3    | 2    | 1    | 0     |

|-------|--------|--------|----------------------------|---------------|-------------|------|------|------|-------|

| IPH   | (B7H)  | -      | PPCH                       | PT2H          | PSH         | PT1H | PX1H | PT0H | PX0H  |

|       |        |        | Bit = 1 ass<br>Bit = 0 ass |               |             |      |      |      |       |

| BIT   | SYMBOL | FUNC   | TION                       |               |             |      |      |      |       |

| IPH.7 | -      | -      |                            |               |             |      |      |      |       |

| IPH.6 | PPCH   | PCA ir | nterrupt pr                | iority bit    |             |      |      |      |       |

| IPH.5 | PT2H   | Timer  | 2 interrupt                | priority b    | it high.    |      |      |      |       |

| IPH.4 | PSH    | Serial | Port interr                | upt priorit   | y bit high. |      |      |      |       |

| IPH.3 | PT1H   | Timer  | 1 interrupt                | priority b    | it high.    |      |      |      |       |

| IPH.2 | PX1H   | Extern | al interrup                | t 1 priority  | / bit high. |      |      |      |       |

| IPH.1 | PT0H   | Timer  | 0 interrup                 | priority b    | it high.    |      |      |      |       |

| IPH.0 | PX0H   | Extern | al interrup                | ot 0 priority | / bit high. |      |      |      | SU012 |

#### Figure 17. IPH Registers

### Reduced EMI Mode

The AO bit (AUXR.0) in the AUXR register when set disables the ALE output unless the CPU needs to perform an off-chip memory access.

#### **Reduced EMI Mode**

#### AUXR (8EH)

| 7                | 6 | 5            | 4 | 3 | 2 | 1      | 0  |

|------------------|---|--------------|---|---|---|--------|----|

| -                | - | -            | - | - | - | EXTRAM | AO |

| AUXR.1<br>AUXR.0 |   | EXTRAN<br>AO | 1 |   |   |        |    |

See more detailed description in Figure 32.

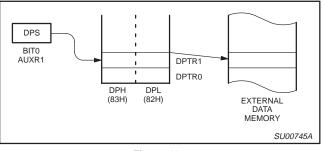

#### **Dual DPTR**

The dual DPTR structure (see Figure 18) is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1/bit0 that allows the program code to switch between them.

- New Register Name: AUXR1#

- SFR Address: A2H

- Reset Value: xxxxxx0B

DPTR1

#### AUXR1 (A2H)

| 7             | 6      | 5          | 4         | 3       | 2       | 1        | 0   |

|---------------|--------|------------|-----------|---------|---------|----------|-----|

| -             | -      | -          | -         | GF2     | 0       | -        | DPS |

| Where:<br>DPS | = AUXR | 1/bit0 = S | witches t | petween | DPTR0 a | and DPTI | R1. |

|               | Sele   | ect Reg    |           |         | DF      | PS       |     |

|               | DI     | PTR0       |           |         | 0       | )        |     |

1

The DPS bit status should be saved by software when switching between DPTR0 and DPTR1.

The GF2 bit is a general purpose user-defined flag. Note that bit 2 is not writable and is always read as a zero. This allows the DPS bit to be quickly toggled simply by executing an INC AUXR1 instruction without affecting the GF2 bit.

P87C51RA2/RB2/RC2/RD2

Figure 18.

#### **DPTR Instructions**

The instructions that refer to DPTR refer to the data pointer that is currently selected using the AUXR1/bit 0 register. The six instructions that use the DPTR are as follows:

| INC DPTR          | Increments the data pointer by 1          |

|-------------------|-------------------------------------------|

| MOV DPTR, #data16 | Loads the DPTR with a 16-bit constant     |

| MOV A, @ A+DPTR   | Move code byte relative to DPTR to ACC    |

| MOVX A, @ DPTR    | Move external RAM (16-bit address) to ACC |

| MOVX @ DPTR , A   | Move ACC to external RAM (16-bit address) |

| JMP @ A + DPTR    | Jump indirect relative to DPTR            |

The data pointer can be accessed on a byte-by-byte basis by specifying the low or high byte in an instruction which accesses the SFRs. See *Application Note AN458* for more details.

## P87C51RA2/RB2/RC2/RD2

|            | СМС          | D Addres                  | ss = D9H                             |                  |                    |                          |              |                          | R               | eset Value = 00XX X000B |

|------------|--------------|---------------------------|--------------------------------------|------------------|--------------------|--------------------------|--------------|--------------------------|-----------------|-------------------------|

|            |              |                           |                                      |                  |                    |                          |              |                          |                 |                         |

|            | ſ            | CIDL                      | WDTE                                 | -                | -                  | -                        | CPS1         | CPS0                     | ECF             |                         |

|            | Bit:         | 7                         | 6                                    | 5                | 4                  | 3                        | 2            | 1                        | 0               | -                       |

| Symbol     | Func         | tion                      |                                      |                  |                    |                          |              |                          |                 |                         |

| CIDL       |              |                           | ntrol: CIDL =<br>f during idle.      |                  | ns the PCA         | Counter to               | continue fui | nctioning du             | ring idle M     | ode. CIDL = 1 programs  |

| WDTE       | Watcl        | hdog Time                 | r Enable: W                          | DTE = 0 di       | sables Wate        | chdog Time               | r function o | n PCA Mod                | ule 4. WDT      | E = 1 enables it.       |

| -          | Not ir       | nplemente                 | d, reserved                          | for future u     | ise.*              |                          |              |                          |                 |                         |

| CPS1       | PCA          | Count Puls                | se Select bit                        | 1.               |                    |                          |              |                          |                 |                         |

| CPS0       | PCA<br>CPS1  |                           | se Select bit<br>Selecte             | 0.<br>ed PCA Inj | out**              |                          |              |                          |                 |                         |

|            | 0            | 0                         | 0                                    | Intern           | al clock, for      | c/6 in 6-clo             | ock mode (f  |                          | 2-clock mod     | le)                     |

|            | 0            | 1                         | 1                                    |                  |                    |                          | ock mode (f  | 500                      |                 | ,                       |

|            | 1            | 0                         | 2                                    | Timer            | 0 overflow         | -                        |              |                          |                 |                         |

|            | 1            | 1                         | 3                                    | Exterr           | nal clock at       | ECI/P1.2 pi              | n            |                          |                 |                         |

|            |              |                           |                                      | (ma              | x. rate = $f_{OS}$ | <sub>SC</sub> /4 in 6-cl | ock mode, f  | <sub>OCS</sub> /8 in 12- | clock mode      | e)                      |

| ECF        |              | Enable Co<br>unction of ( |                                      | ow interrup      | ot: ECF = 1        | enables CF               | bit in CCO   | N to genera              | te an interr    | upt. ECF = 0 disables   |

|            | e new bit wi | ll be 0, and its          | reserved bits. T<br>active value wil |                  |                    |                          |              | oke new feature          | s. In that case | , the reset or inactive |

| 1030 - 566 |              | ,                         |                                      |                  |                    |                          |              |                          |                 | SU01318                 |

#### Figure 22. CMOD: PCA Counter Mode Register

|                         | Bit Ad                                                | dressable                                                                                   |                                                                                                |                                                                                            |                                                                                    |                                                                           |                                                            |                                                                      |                                                                     | _                                                          |

|-------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------|

|                         |                                                       | CF                                                                                          | CR                                                                                             | -                                                                                          | CCF4                                                                               | CCF3                                                                      | CCF2                                                       | CCF1                                                                 | CCF0                                                                |                                                            |

|                         | Bit:                                                  | 7                                                                                           | 6                                                                                              | 5                                                                                          | 4                                                                                  | 3                                                                         | 2                                                          | 1                                                                    | 0                                                                   | -                                                          |

| Symbol                  | Funct                                                 | ion                                                                                         |                                                                                                |                                                                                            |                                                                                    |                                                                           |                                                            |                                                                      |                                                                     |                                                            |

| CF                      | PCA (                                                 | Counter O                                                                                   | verflow flag                                                                                   | . Set bv ha                                                                                | rdware whe                                                                         | n the counte                                                              | er rolls over                                              | . CF flags a                                                         | n interrupt                                                         | if bit ECF in CMOD is                                      |

|                         |                                                       |                                                                                             |                                                                                                |                                                                                            | or software                                                                        |                                                                           | ly be cleare                                               |                                                                      |                                                                     |                                                            |

| -                       | set. C                                                | F may be<br>Counter Ri                                                                      | set by eithe                                                                                   | er hardware                                                                                | or software                                                                        | but can on                                                                |                                                            | d by softwa                                                          | are.                                                                | oftware to turn the PC                                     |

| -                       | set. C<br>PCA (<br>counte                             | F may be<br>Counter Ri<br>er off.                                                           | set by eithe                                                                                   | er hardware<br>it. Set by se                                                               | or software                                                                        | but can on                                                                |                                                            | d by softwa                                                          | are.                                                                |                                                            |

| CR<br>-                 | set. C<br>PCA (<br>counte<br>Not im                   | F may be<br>Counter Ri<br>er off.<br>nplemente                                              | set by eithe<br>un control b<br>d, reserved                                                    | er hardware<br>it. Set by se<br>for future u                                               | or software<br>oftware to tu<br>use*.                                              | but can on<br>urn the PCA                                                 | counter on                                                 | d by softwa<br>. Must be c                                           | are.<br>leared by s                                                 |                                                            |

| CR<br>-<br>CCF4<br>CCF3 | set. C<br>PCA (<br>counte<br>Not im<br>PCA N          | F may be<br>Counter Re<br>er off.<br>nplemente<br>Module 4 in                               | set by eithe<br>un control b<br>d, reserved<br>nterrupt flag                                   | er hardware<br>it. Set by set<br>for future u<br>g. Set by ha                              | or software<br>oftware to tu<br>use*.<br>ardware whe                               | but can on<br>urn the PCA<br>en a match o                                 | counter on                                                 | d by softwa<br>. Must be c<br>ccurs. Mus                             | are.<br>leared by s<br>t be cleared                                 | oftware to turn the PC                                     |

| CR<br>-<br>CCF4         | set. C<br>PCA (<br>counte<br>Not im<br>PCA N<br>PCA N | F may be<br>Counter Ri<br>er off.<br>nplemente<br>Module 4 in<br>Module 3 in                | set by eithe<br>un control b<br>d, reserved<br>nterrupt flag<br>nterrupt flag                  | r hardware<br>it. Set by so<br>for future u<br>g. Set by ha<br>g. Set by ha                | or software<br>oftware to tu<br>use*.<br>ardware whe<br>ardware whe                | but can on<br>urn the PCA<br>an a match o<br>an a match o                 | counter on<br>or capture c                                 | d by softwa<br>. Must be c<br>ccurs. Mus<br>ccurs. Mus               | are.<br>leared by s<br>t be cleared<br>t be cleared                 | oftware to turn the PC<br>d by software.                   |

| CR<br>-<br>CCF4<br>CCF3 | set. C<br>PCA (<br>counte<br>Not im<br>PCA N<br>PCA N | F may be<br>Counter Ri<br>er off.<br>nplemente<br>Module 4 in<br>Module 3 in<br>Module 2 in | set by eithe<br>un control b<br>d, reserved<br>nterrupt flag<br>nterrupt flag<br>nterrupt flag | r hardware<br>it. Set by s<br>for future u<br>g. Set by ha<br>g. Set by ha<br>g. Set by ha | or software<br>oftware to tu<br>use*.<br>ardware whe<br>ardware whe<br>ardware whe | but can on<br>urn the PCA<br>en a match o<br>en a match o<br>en a match o | counter on<br>or capture c<br>or capture c<br>or capture c | d by softwa<br>. Must be c<br>ccurs. Mus<br>ccurs. Mus<br>ccurs. Mus | are.<br>leared by s<br>t be cleared<br>t be cleared<br>t be cleared | oftware to turn the PC<br>d by software.<br>d by software. |

SU01319

#### Figure 23. CCON: PCA Counter Control Register

SU01320

P87C51RA2/RB2/RC2/RD2

## 80C51 8-bit microcontroller family 8KB/16KB/32KB/64KB OTP with 512B/1KB RAM, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

| CCAPMn | Address | CCAF<br>CCAF<br>CCAF<br>CCAF<br>CCAF       | PM1 ODE<br>PM2 ODC<br>PM3 ODE | SH<br>CH<br>DH |              |               |              |             | K             | eset Value = X000 0000l |  |  |

|--------|---------|--------------------------------------------|-------------------------------|----------------|--------------|---------------|--------------|-------------|---------------|-------------------------|--|--|

|        | Not Bi  | t Addressa                                 | ble                           |                |              |               |              |             |               | _                       |  |  |

|        |         | -                                          | ECOMn                         | CAPPn          | CAPNn        | MATn          | TOGn         | PWMn        | ECCFn         |                         |  |  |

|        | Bit:    | 7                                          | 6                             | 5              | 4            | 3             | 2            | 1           | 0             |                         |  |  |

| Symbol | Func    | tion                                       |                               |                |              |               |              |             |               |                         |  |  |

| _      | Not ir  | Not implemented, reserved for future use*. |                               |                |              |               |              |             |               |                         |  |  |

| ECOMn  | Enab    | le Compar                                  | ator. ECOM                    | n = 1 enabl    | es the com   | parator fund  | ction.       |             |               |                         |  |  |

| CAPPn  | Capti   | ure Positiv                                | e, CAPPn =                    | 1 enables p    | positive edg | e capture.    |              |             |               |                         |  |  |

| CAPNn  | Capti   | ure Negativ                                | ve, CAPNn :                   | = 1 enables    | negative e   | dge capture   | <b>)</b> .   |             |               |                         |  |  |

| MATn   |         |                                            | ATn = 1, a r<br>set, flagging |                |              | ter with this | module's c   | compare/ca  | pture registe | er causes the CCFn bit  |  |  |

| TOGn   |         | e. When T<br>toggle.                       | OGn = 1, a                    | match of th    | e PCA cour   | nter with thi | s module's   | compare/ca  | apture regis  | ter causes the CEXn     |  |  |

| PWMn   | Pulse   | Width Mo                                   | dulation Mo                   | de. PWMn       | = 1 enables  | the CEXn      | pin to be us | sed as a pu | lse width me  | odulated output.        |  |  |

| ECCFn  | Enab    | le CCE int                                 | errunt Engh                   | les compar     | e/canture fl | ag CCEn in    | the CCON     | register to | generate ar   | interrunt               |  |  |

\*User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

Figure 24. CCAPMn: PCA Modules Compare/Capture Registers

| - | ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMn | ECCFn | MODULE FUNCTION                                   |  |  |

|---|-------|-------|-------|------|------|------|-------|---------------------------------------------------|--|--|

| Х | 0     | 0     | 0     | 0    | 0    | 0    | 0     | No operation                                      |  |  |

| Х | Х     | 1     | 0     | 0    | 0    | 0    | Х     | 16-bit capture by a positive-edge trigger on CEXn |  |  |

| Х | Х     | 0     | 1     | 0    | 0    | 0    | Х     | 16-bit capture by a negative trigger on CEXn      |  |  |

| Х | Х     | 1     | 1     | 0    | 0    | 0    | Х     | 16-bit capture by a transition on CEXn            |  |  |

| Х | 1     | 0     | 0     | 1    | 0    | 0    | Х     | 16-bit Software Timer                             |  |  |

| Х | 1     | 0     | 0     | 1    | 1    | 0    | Х     | 16-bit High Speed Output                          |  |  |

| Х | 1     | 0     | 0     | 0    | 0    | 1    | 0     | 8-bit PWM                                         |  |  |

| Х | 1     | 0     | 0     | 1    | Х    | 0    | Х     | Watchdog Timer                                    |  |  |

Figure 25. PCA Module Modes (CCAPMn Register)

#### PCA Capture Mode

To use one of the PCA modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated. Refer to Figure 26.

#### 16-bit Software Timer Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (see Figure 27).

#### High Speed Output Mode

In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA

counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set (see Figure 28).

#### Pulse Width Modulator Mode

All of the PCA modules can be used as PWM outputs. Figure 29 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. the allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

## 80C51 8-bit microcontroller family 8KB/16KB/32KB/64KB OTP with 512B/1KB RAM, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

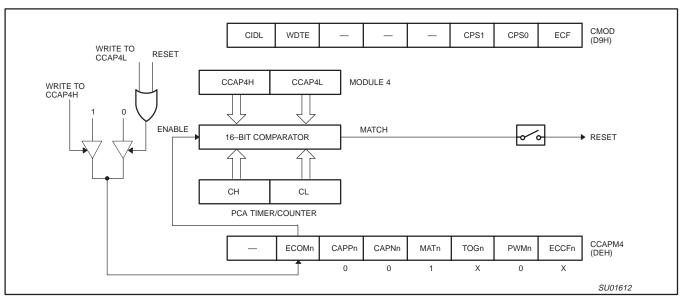

Figure 30. PCA Watchdog Timer mode (Module 4 only)

#### PCA Watchdog Timer

An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed.

Figure 30 shows a diagram of how the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

- 1. periodically change the compare value so it will never match the PCA timer,

- 2. periodically change the PCA timer value so it will never match the compare values, or

- 3. disable the watchdog by clearing the WDTE bit before a match occurs and then re-enable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for **all** modules; changing the time base for other modules would not be a good idea. Thus, in most applications the first solution is the best option.

Figure 31 shows the code for initializing the watchdog timer. Module 4 can be configured in either compare mode, and the WDTE bit in CMOD must also be set. The user's software then must periodically change (CCAP4H,CCAP4L) to keep a match from occurring with the PCA timer (CH,CL). This code is given in the WATCHDOG routine in Figure 31.

This routine should not be part of an interrupt service routine, because if the program counter goes astray and gets stuck in an infinite loop, interrupts will still be serviced and the watchdog will keep getting reset. Thus, the purpose of the watchdog would be defeated. Instead, call this subroutine from the main program within  $2^{16}$  count of the PCA timer.

#### **ABSOLUTE MAXIMUM RATINGS1, 2, 3**

| PARAMETER                                                                                    | RATING                 | UNIT |

|----------------------------------------------------------------------------------------------|------------------------|------|

| Operating temperature under bias                                                             | 0 to +70 or -40 to +85 | °C   |

| Storage temperature range                                                                    | -65 to +150            | °C   |

| Voltage on $\overline{EA}/V_{PP}$ pin to V <sub>SS</sub>                                     | 0 to +13.0             | V    |

| Voltage on any other pin to V <sub>SS</sub> <sup>4</sup>                                     | -0.5 to +6.0           | V    |

| Maximum I <sub>OL</sub> per I/O pin                                                          | 15                     | mA   |

| Power dissipation (based on package heat transfer limitations, not device power consumption) | 1.5                    | W    |

NOTES:

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section of this specification is not implied. 1.

This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise

noted.

4. Transient voltage only.

#### **AC ELECTRICAL CHARACTERISTICS**

$T_{amb} = 0^{\circ}C$  to +70°C or -40°C to +85°C

|                     |        |                      |                |                         | CLOCK FREG<br>RANGI |     |      |

|---------------------|--------|----------------------|----------------|-------------------------|---------------------|-----|------|

| SYMBOL              | FIGURE | PARAMETER            | OPERATING MODE | POWER SUPPLY<br>VOLTAGE | MIN                 | MAX | UNIT |

| 1/t <sub>CLCL</sub> | 38     | Oscillator frequency | 6-clock        | $5 V \pm 10\%$          | 0                   | 30  | MHz  |

|                     |        |                      | 6-clock        | 2.7 V to 5.5 V          | 0                   | 16  | MHz  |

|                     |        |                      | 12-clock       | $5 V \pm 10\%$          | 0                   | 33  | MHz  |

|                     |        |                      | 12-clock       | 2.7 V to 5.5 V          | 0                   | 16  | MHz  |

### P87C51RA2/RB2/RC2/RD2

#### AC ELECTRICAL CHARACTERISTICS (12-CLOCK MODE, 2.7 V TO 5.5 V OPERATION)

$T_{amb} = 0 \text{ °C to } +70 \text{ °C or } -40 \text{ °C to } +85 \text{ °C}$ ;  $V_{CC} = 2.7 \text{ V to } 5.5 \text{ V}, \text{ V}_{SS} = 0 \text{ V}^{1,2,3,4}$

| Symbol              | Figure | Parameter                                          | Limits                   |                                       | 16 MHz | Clock | Unit |

|---------------------|--------|----------------------------------------------------|--------------------------|---------------------------------------|--------|-------|------|

|                     |        |                                                    | MIN                      | MAX                                   | MIN    | MAX   |      |

| 1/t <sub>CLCL</sub> | 38     | Oscillator frequency                               | 0                        | 16                                    |        |       | MHz  |

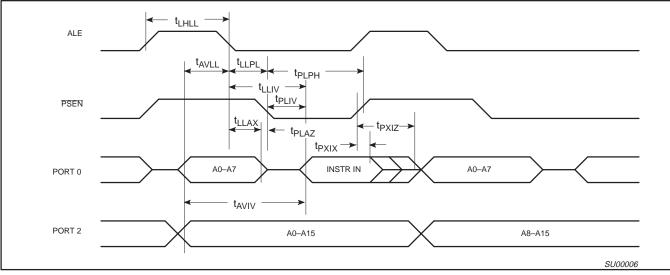

| LHLL                | 34     | ALE pulse width                                    | 2t <sub>CLCL</sub> -10   |                                       | 115    |       | ns   |

| t <sub>AVLL</sub>   | 34     | Address valid to ALE low                           | t <sub>CLCL</sub> –15    |                                       | 47.5   |       | ns   |

| t <sub>LLAX</sub>   | 34     | Address hold after ALE low                         | t <sub>CLCL</sub> –25    |                                       | 37.5   |       | ns   |

| t <sub>LLIV</sub>   | 34     | ALE low to valid instruction in                    |                          | 4 t <sub>CLCL</sub> –55               |        | 195   | ns   |

| t <sub>LLPL</sub>   | 34     | ALE low to PSEN low                                | t <sub>CLCL</sub> –15    |                                       | 47.5   |       | ns   |

| t <sub>PLPH</sub>   | 34     | PSEN pulse width                                   | 3 t <sub>CLCL</sub> –15  |                                       | 172.5  |       | ns   |

| t <sub>PLIV</sub>   | 34     | PSEN low to valid instruction in                   |                          | 3 t <sub>CLCL</sub> –55               |        | 132.5 | ns   |

| t <sub>PXIX</sub>   | 34     | Input instruction hold after PSEN                  | 0                        |                                       | 0      |       | ns   |

| t <sub>PXIZ</sub>   | 34     | Input instruction float after PSEN                 |                          | t <sub>CLCL</sub> –10                 |        | 52.5  | ns   |

| t <sub>AVIV</sub>   | 34     | Address to valid instruction in                    |                          | 5 t <sub>CLCL</sub> –50               |        | 262.5 | ns   |

| t <sub>PLAZ</sub>   | 34     | PSEN low to address float                          |                          | 10                                    |        | 10    | ns   |

| Data Men            | nory   | ·                                                  |                          | •                                     | •      | •     |      |

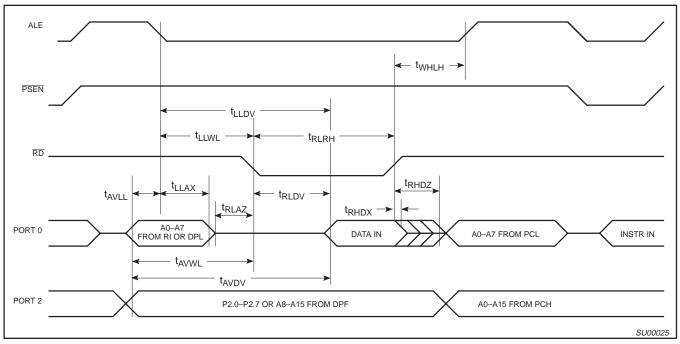

| t <sub>RLRH</sub>   | 35     | RD pulse width                                     | 6 t <sub>CLCL</sub> –25  |                                       | 350    |       | ns   |

| twlwh               | 36     | WR pulse width                                     | 6 t <sub>CLCL</sub> –25  |                                       | 350    |       | ns   |

| t <sub>RLDV</sub>   | 35     | RD low to valid data in                            |                          | 5 t <sub>CLCL</sub> –50               |        | 262.5 | ns   |

| t <sub>RHDX</sub>   | 35     | Data hold after RD                                 | 0                        |                                       | 0      |       | ns   |

| t <sub>RHDZ</sub>   | 35     | Data float after RD                                |                          | 2 t <sub>CLCL</sub> –20               |        | 105   | ns   |

| t <sub>LLDV</sub>   | 35     | ALE low to valid data in                           |                          | 8 t <sub>CLCL</sub> –55               |        | 445   | ns   |

| t <sub>AVDV</sub>   | 35     | Address to valid data in                           |                          | 9 t <sub>CLCL</sub> –50               |        | 512.5 | ns   |

| t <sub>LLWL</sub>   | 35, 36 | ALE low to RD or WR low                            | 3 t <sub>CLCL</sub> –20  | 3 t <sub>CLCL</sub> +20               | 167.5  | 207.5 | ns   |

| tavwl               | 35, 36 | Address valid to WR low or RD low                  | 4 t <sub>CLCL</sub> –20  |                                       | 230    |       | ns   |

| t <sub>QVWX</sub>   | 36     | Data valid to WR transition                        | t <sub>CLCL</sub> -30    |                                       | 32.5   |       | ns   |

| t <sub>WHQX</sub>   | 36     | Data hold after WR                                 | t <sub>CLCL</sub> –20    |                                       | 42.5   |       | ns   |

| t <sub>QVWH</sub>   | 36     | Data valid to WR high                              | 7 t <sub>CLCL</sub> –10  |                                       | 427.5  |       | ns   |

| t <sub>RLAZ</sub>   | 35     | RD low to address float                            |                          | 0                                     |        | 0     | ns   |

| t <sub>WHLH</sub>   | 35, 36 | RD or WR high to ALE high                          | t <sub>CLCL</sub> –15    | t <sub>CLCL</sub> +15                 | 47.5   | 77.5  | ns   |

| External            | Clock  | •                                                  |                          | •                                     | •      |       |      |

| tCHCX               | 38     | High time                                          | 0.32 t <sub>CLCL</sub>   | t <sub>CLCL</sub> - t <sub>CLCX</sub> |        |       | ns   |

| t <sub>CLCX</sub>   | 38     | Low time                                           | 0.32 t <sub>CLCL</sub>   | t <sub>CLCL</sub> - t <sub>CHCX</sub> |        |       | ns   |

| t <sub>CLCH</sub>   | 38     | Rise time                                          |                          | 5                                     |        |       | ns   |

| t <sub>CHCL</sub>   | 38     | Fall time                                          |                          | 5                                     |        |       | ns   |

| Shift regi          | ster   | ·                                                  |                          | •                                     | •      | •     | •    |

| t <sub>XLXL</sub>   | 37     | Serial port clock cycle time                       | 12 t <sub>CLCL</sub>     |                                       | 750    |       | ns   |

| t <sub>QVXH</sub>   | 37     | Output data setup to clock rising edge             | 10 t <sub>CLCL</sub> –25 |                                       | 600    |       | ns   |

| t <sub>XHQX</sub>   | 37     | Output data hold after clock rising edge           | 2 t <sub>CLCL</sub> –15  |                                       | 110    |       | ns   |

| t <sub>XHDX</sub>   | 37     | Input data hold after clock rising edge            | 0                        |                                       | 0      |       | ns   |

| t <sub>XHDV</sub>   | 37     | Clock rising edge to input data valid <sup>5</sup> |                          | 10 t <sub>CLCL</sub> –133             |        | 492   | ns   |

#### NOTES:

Parameters are valid over operating temperature range unless otherwise specified.

Load capacitance for port 0, ALE, and PSEN = 100 pF, load capacitance for all outputs = 80 pF

3. Interfacing the microcontroller to devices with float time up to 45 ns is permitted. This limited bus contention will not cause damage to port 0 drivers.

4. Parts are guaranteed by design to operate down to 0 Hz. 5. Below 16 MHz this parameter is 8  $t_{CLCL}$  – 133.

### P87C51RA2/RB2/RC2/RD2

#### AC ELECTRICAL CHARACTERISTICS (6-CLOCK MODE, 5 V ±10% OPERATION)

$T_{amb} = 0 \degree C$  to +70  $\degree C$  or -40  $\degree C$  to +85  $\degree C$  :  $V_{CC} = 5 \lor \pm 10\%$ .  $V_{SS} = 0 \lor^{1,2,3,4,5}$

| Symbol              | Figure | Parameter                                          | Limits                    |                                       | 16 MHz ( | Clock  | Unit |