Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 120MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 100K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

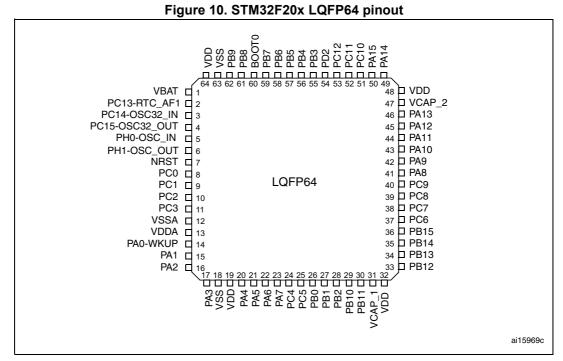

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205rct6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of tables

| Table 1.  | Device summary                                                                 | 1  |

|-----------|--------------------------------------------------------------------------------|----|

| Table 2.  | STM32F205xx features and peripheral counts                                     | 14 |

| Table 3.  | STM32F207xx features and peripheral counts                                     | 15 |

| Table 4.  | Regulator ON/OFF and internal reset ON/OFF availability                        |    |

| Table 5.  | Timer feature comparison                                                       | 32 |

| Table 6.  | USART feature comparison                                                       | 35 |

| Table 7.  | Legend/abbreviations used in the pinout table                                  |    |

| Table 8.  | STM32F20x pin and ball definitions                                             |    |

| Table 9.  | FSMC pin definition                                                            |    |

| Table 10. | Alternate function mapping                                                     |    |

| Table 11. | Voltage characteristics                                                        |    |

| Table 12. | Current characteristics                                                        |    |

| Table 13. | Thermal characteristics                                                        | 71 |

| Table 14. | General operating conditions                                                   |    |

| Table 15. | Limitations depending on the operating power supply range                      |    |

| Table 16. | VCAP1/VCAP2 operating conditions                                               |    |

| Table 17. | Operating conditions at power-up / power-down (regulator ON)                   |    |

| Table 18. | Operating conditions at power-up / power-down (regulator OFF)                  |    |

| Table 19. | Embedded reset and power control block characteristics.                        |    |

| Table 20. | Typical and maximum current consumption in Run mode, code with data processing |    |

|           | running from Flash memory (ART accelerator enabled) or RAM                     | 78 |

| Table 21. | Typical and maximum current consumption in Run mode, code with data processing | -  |

|           | running from Flash memory (ART accelerator disabled)                           | 79 |

| Table 22. | Typical and maximum current consumption in Sleep mode                          |    |

| Table 23. | Typical and maximum current consumptions in Stop mode                          |    |

| Table 24. | Typical and maximum current consumptions in Standby mode                       |    |

| Table 25. | Typical and maximum current consumptions in V <sub>BAT</sub> mode              |    |

| Table 26. | Peripheral current consumption                                                 |    |

| Table 27. | Low-power mode wakeup timings                                                  |    |

| Table 28. | High-speed external user clock characteristics.                                |    |

| Table 29. | Low-speed external user clock characteristics                                  |    |

| Table 30. | HSE 4-26 MHz oscillator characteristics                                        |    |

| Table 31. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                 |    |

| Table 32. | HSI oscillator characteristics                                                 |    |

| Table 33. | LSI oscillator characteristics                                                 |    |

| Table 34. | Main PLL characteristics.                                                      |    |

| Table 35. | PLLI2S (audio PLL) characteristics                                             |    |

| Table 36. | SSCG parameters constraint                                                     |    |

| Table 37. | Flash memory characteristics                                                   |    |

| Table 38. | Flash memory programming.                                                      |    |

| Table 39. | Flash memory programming with $V_{PP}$                                         |    |

| Table 40. | Flash memory endurance and data retention                                      |    |

| Table 41. | EMS characteristics                                                            |    |

| Table 42. | EMI characteristics                                                            |    |

| Table 43. | ESD absolute maximum ratings                                                   |    |

| Table 44. | Electrical sensitivities                                                       |    |

| Table 45. | I/O current injection susceptibility                                           |    |

| Table 46. | I/O static characteristics                                                     |    |

|           |                                                                                |    |

There are three power modes configured by software when the regulator is ON:

- MR is used in the nominal regulation mode

- LPR is used in Stop modes

The LP regulator mode is configured by software when entering Stop mode.

• Power-down is used in Standby mode.

The Power-down mode is activated only when entering Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost).

Two external ceramic capacitors should be connected on  $V_{CAP_1}$  and  $V_{CAP_2}$  pin. Refer to *Figure 19: Power supply scheme* and *Table 16: VCAP1/VCAP2 operating conditions*.

All packages have the regulator ON feature.

### 3.16.2 Regulator OFF

This feature is available only on packages featuring the REGOFF pin. The regulator is disabled by holding REGOFF high. The regulator OFF mode allows to supply externally a V12 voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins.

The two 2.2 µF ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Figure 19: Power supply scheme*.

When the regulator is OFF, there is no more internal monitoring on V12. An external power supply supervisor should be used to monitor the V12 of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on V12 power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset the part of the 1.2 V logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used at power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection at reset or pre-reset is required.

### Regulator OFF/internal reset ON

On WLCSP64+2 package, this mode is activated by connecting REGOFF pin to V<sub>DD</sub> and IRROFF pin to V<sub>SS</sub>. On UFBGA176 package, only REGOFF must be connected to V<sub>DD</sub> (IRROFF not available). In this mode,  $V_{DD}/V_{DDA}$  minimum value is 1.8 V.

The regulator OFF/internal reset ON mode allows to supply externally a 1.2 V voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins, in addition to V<sub>DD</sub>.

# 3.20 Timers and watchdogs

The STM32F20x devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

*Table 5* compares the features of the advanced-control, general-purpose and basic timers.

| Timer type           | Timer           | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>output | Max<br>interface<br>clock | Max<br>timer<br>clock |

|----------------------|-----------------|-----------------------|-------------------------|---------------------------------------|------------------------------|---------------------------------|-------------------------|---------------------------|-----------------------|

| Advanced-<br>control | TIM1,<br>TIM8   | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | Yes                     | 60<br>MHz                 | 120<br>MHz            |

| General              | TIM2,<br>TIM5   | 32-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                      | 30<br>MHz                 | 60<br>MHz             |

| purpose              | TIM3,<br>TIM4   | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                      | 30<br>MHz                 | 60<br>MHz             |

| Basic                | TIM6,<br>TIM7   | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                      | 30<br>MHz                 | 60<br>MHz             |

|                      | TIM9            | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 2                               | No                      | 60<br>MHz                 | 120<br>MHz            |

| General              | TIM10,<br>TIM11 | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 1                               | No                      | 60<br>MHz                 | 120<br>MHz            |

| purpose              | TIM12           | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 2                               | No                      | 30<br>MHz                 | 60<br>MHz             |

|                      | TIM13,<br>TIM14 | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 1                               | No                      | 30<br>MHz                 | 60<br>MHz             |

Table 5. Timer feature comparison

## 3.20.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The TIM1 and TIM8 counters can be frozen in debug mode. Many of the advanced-control timer features are shared with those of the standard TIMx timers which have the same architecture. The advanced-control timer can therefore work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

### 3.20.2 General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F20x devices (see *Table 5* for differences).

### TIM2, TIM3, TIM4, TIM5

The STM32F20x include 4 full-featured general-purpose timers. TIM2 and TIM5 are 32-bit timers, and TIM3 and TIM4 are 16-bit timers. The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

The counters of TIM2, TIM3, TIM4, TIM5 can be frozen in debug mode. Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

### TIM10, TIM11 and TIM9

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10 and TIM11 feature one independent channel, whereas TIM9 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

### TIM12, TIM13 and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM13 and TIM14 feature one independent channel, whereas TIM12 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers.

They can also be used as simple time bases.

### 3.20.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

DocID15818 Rev 13

| USART<br>name | Standard<br>features | Modem<br>(RTS/CTS) | LIN | SPI<br>master | irDA | Smartcard<br>(ISO 7816) | Max. baud rate<br>in Mbit/s<br>(oversampling<br>by 16) | Max. baud rate<br>in Mbit/s<br>(oversampling<br>by 8) | APB<br>mapping        |  |

|---------------|----------------------|--------------------|-----|---------------|------|-------------------------|--------------------------------------------------------|-------------------------------------------------------|-----------------------|--|

| USART1        | х                    | х                  | х   | х             | Х    | х                       | 1.87                                                   | 7.5                                                   | APB2 (max.<br>60 MHz) |  |

| USART2        | х                    | х                  | х   | х             | х    | х                       | 1.87                                                   | 3.75                                                  | APB1 (max.<br>30 MHz) |  |

| USART3        | х                    | х                  | х   | х             | х    | х                       | 1.87                                                   | 3.75                                                  | APB1 (max.<br>30 MHz) |  |

| UART4         | х                    | -                  | х   | -             | х    | -                       | 1.87                                                   | 3.75                                                  | APB1 (max.<br>30 MHz) |  |

| UART5         | х                    | -                  | х   | -             | х    | -                       | 3.75                                                   | 3.75                                                  | APB1 (max.<br>30 MHz) |  |

| USART6        | х                    | х                  | х   | х             | х    | х                       | 3.75                                                   | 7.5                                                   | APB2 (max.<br>60 MHz) |  |

Table 6. USART feature comparison

# 3.23 Serial peripheral interface (SPI)

The STM32F20x devices feature up to three SPIs in slave and master modes in full-duplex and simplex communication modes. SPI1 can communicate at up to 30 Mbits/s, while SPI2 and SPI3 can communicate at up to 15 Mbit/s. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes. All SPIs can be served by the DMA controller.

The SPI interface can be configured to operate in TI mode for communications in master mode and slave mode.

# 3.24 Inter-integrated sound (I<sup>2</sup>S)

Two standard I<sup>2</sup>S interfaces (multiplexed with SPI2 and SPI3) are available. They can operate in master or slave mode, in half-duplex communication modes, and can be configured to operate with a 16-/32-bit resolution as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All I2Sx interfaces can be served by the DMA controller.

## 3.25 SDIO

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

DocID15818 Rev 13

# 3.37 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

# 3.38 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F20x through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

# 4 Pinouts and pin description

1. The above figure shows the package top view.

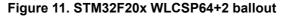

|   | 1    | 2      | 3      | 4   | 5   | 6     | 7      | 8      | 9                |

|---|------|--------|--------|-----|-----|-------|--------|--------|------------------|

| А | PA14 | PA15   | PC12   | PB3 | PB5 | PB7   | PB9    | VDD    | V <sub>BAT</sub> |

| В | VSS  | PA13   | PC10   | PB4 | PB6 | BOOT0 | PB8    | PC13   | PC14             |

| С | PA12 | VCAP_2 | PC11   |     |     |       | PD2    | IRROFF | PC15             |

| D | PC9  | PA11   | PA10   |     |     |       | PC2    | VSS    | VDD              |

| E | VDD  | PA8    | PA9    |     |     |       | PA0    | NRST   | PH0-<br>OSC_IN   |

| F | VSS  | PC7    | PC8    |     |     |       | VREF+  | PC1    | PH1-<br>OSC_OUT  |

| G | PB15 | PC6    | PC5    |     |     |       | PA3    | PC3    | PC0              |

| н | PB14 | PB13   | PB10   | PC4 | PA6 | PA5   | REGOFF | PA1    | VSS_5            |

| J | PB12 | PB11   | VCAP_1 | PB2 | PB1 | PB0   | PA7    | PA4    | PA2              |

|   |      |        |        |     |     |       |        |        |                  |

|   |      |        |        |     |     |       |        |        |                  |

1. The above figure shows the package top view.

1. RFU means "reserved for future use". This pin can be tied to  $V_{\text{DD}}, V_{\text{SS}}$  or left unconnected.

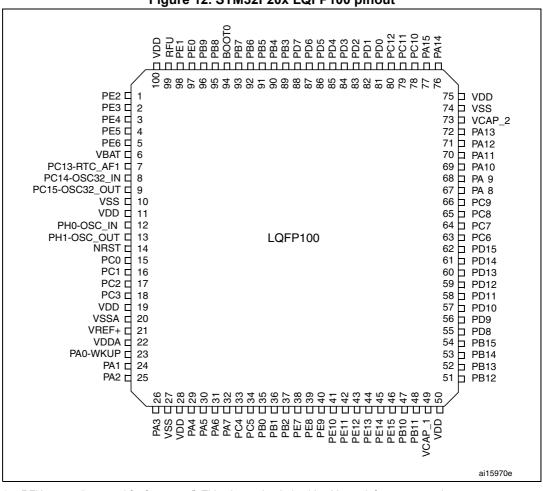

2. The above figure shows the package top view.

| Table 8. STM32 | F20> | c pin | and | ball definitions |

|----------------|------|-------|-----|------------------|

|                |      |       |     |                  |

|        |           | Pi      | ns      |         |          | Table 8. STM32                                       |          |               |        |                                                      |                          |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|--------|------------------------------------------------------|--------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note   | Alternate functions                                  | Additional<br>functions  |

| -      | -         | 1       | 1       | 1       | A2       | PE2                                                  | I/O      | FT            | -      | TRACECLK, FSMC_A23,<br>ETH_MII_TXD3, EVENTOUT        | -                        |

| -      | -         | 2       | 2       | 2       | A1       | PE3                                                  | I/O      | FT            | -      | TRACED0,FSMC_A19,<br>EVENTOUT                        | -                        |

| -      | -         | 3       | 3       | 3       | B1       | PE4                                                  | I/O      | FT            | -      | TRACED1,FSMC_A20,<br>DCMI_D4, EVENTOUT               | -                        |

| -      | -         | 4       | 4       | 4       | B2       | PE5                                                  | I/O      | FT            | -      | TRACED2, FSMC_A21,<br>TIM9_CH1, DCMI_D6,<br>EVENTOUT | -                        |

| -      | -         | 5       | 5       | 5       | В3       | PE6                                                  | I/O      | FT            | -      | TRACED3, FSMC_A22,<br>TIM9_CH2, DCMI_D7,<br>EVENTOUT | -                        |

| 1      | A9        | 6       | 6       | 6       | C1       | V <sub>BAT</sub>                                     | S        |               | -      | -                                                    | -                        |

| -      | -         | -       | -       | 7       | D2       | PI8                                                  | I/O      | FT            | (2)(3) | EVENTOUT                                             | RTC_AF2                  |

| 2      | B8        | 7       | 7       | 8       | D1       | PC13                                                 | I/O      | FT            | (2)(3) | EVENTOUT                                             | RTC_AF1                  |

| 3      | В9        | 8       | 8       | 9       | E1       | PC14/OSC32_IN<br>(PC14)                              | I/O      | FT            | (2)(3) | EVENTOUT                                             | OSC32_IN <sup>(4)</sup>  |

| 4      | C9        | 9       | 9       | 10      | F1       | PC15-OSC32_OUT<br>(PC15)                             | I/O      | FT            | (2)(3) | EVENTOUT                                             | OSC32_OUT <sup>(4)</sup> |

| -      | -         | -       | -       | 11      | D3       | PI9                                                  | I/O      | FT            | -      | CAN1_RX,EVENTOUT                                     | -                        |

| -      | -         | -       | -       | 12      | E3       | PI10                                                 | I/O      | FT            | -      | ETH_MII_RX_ER,<br>EVENTOUT                           | -                        |

| -      | -         | -       | -       | 13      | E4       | PI11                                                 | I/O      | FT            | -      | OTG_HS_ULPI_DIR,<br>EVENTOUT                         | -                        |

| -      | -         | -       | -       | 14      | F2       | V <sub>SS</sub>                                      | S        |               | -      | -                                                    | -                        |

| -      | -         | -       | -       | 15      | F3       | V <sub>DD</sub>                                      | S        |               | -      | -                                                    | -                        |

| -      | -         | -       | 10      | 16      | E2       | PF0                                                  | I/O      | FT            | -      | FSMC_A0, I2C2_SDA,<br>EVENTOUT                       | -                        |

| -      | -         | -       | 11      | 17      | H3       | PF1                                                  | I/O      | FT            | -      | FSMC_A1, I2C2_SCL,<br>EVENTOUT                       | -                        |

| -      | -         | -       | 12      | 18      | H2       | PF2                                                  | I/O      | FT            | -      | FSMC_A2, I2C2_SMBA,<br>EVENTOUT                      | -                        |

| -      | -         | -       | 13      | 19      | J2       | PF3                                                  | I/O      | FT            | (4)    | FSMC_A3, EVENTOUT                                    | ADC3_IN9                 |

| Pins   |           |         |         |         |          |                                                      |          |               |      |                                                                                                               |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|---------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions                                                                                           | Additional<br>functions |

| 22     | H5        | 31      | 42      | 52      | P3       | PA6                                                  | I/O      | FT            | (4)  | SPI1_MISO, TIM8_BKIN,<br>TIM13_CH1, DCMI_PIXCLK,<br>TIM3_CH1, TIM1_BKIN,<br>EVENTOUT                          | ADC12_IN6               |

| 23     | J7        | 32      | 43      | 53      | R3       | PA7                                                  | I/O      | FT            | (4)  | SPI1_MOSI, TIM8_CH1N,<br>TIM14_CH1, TIM3_CH2,<br>ETH_MII_RX_DV,<br>TIM1_CH1N,<br>ETH_RMII_CRS_DV,<br>EVENTOUT | ADC12_IN7               |

| 24     | H4        | 33      | 44      | 54      | N5       | PC4                                                  | I/O      | FT            | (4)  | ETH_RMII_RXD0,<br>ETH_MII_RXD0,<br>EVENTOUT                                                                   | ADC12_IN14              |

| 25     | G3        | 34      | 45      | 55      | P5       | PC5                                                  | I/O      | FT            | (4)  | ETH_RMII_RXD1,<br>ETH_MII_RXD1,<br>EVENTOUT                                                                   | ADC12_IN15              |

| 26     | J6        | 35      | 46      | 56      | R5       | PB0                                                  | I/O      | FT            | (4)  | TIM3_CH3, TIM8_CH2N,<br>OTG_HS_ULPI_D1,<br>ETH_MII_RXD2,<br>TIM1_CH2N, EVENTOUT                               | ADC12_IN8               |

| 27     | J5        | 36      | 47      | 57      | R4       | PB1                                                  | I/O      | FT            | (4)  | TIM3_CH4, TIM8_CH3N,<br>OTG_HS_ULPI_D2,<br>ETH_MII_RXD3,<br>TIM1_CH3N, EVENTOUT                               | ADC12_IN9               |

| 28     | J4        | 37      | 48      | 58      | M6       | PB2/BOOT1 (PB2)                                      | I/O      | FT            | -    | EVENTOUT                                                                                                      | -                       |

| -      | -         | -       | 49      | 59      | R6       | PF11                                                 | I/O      | FT            | -    | DCMI_D12, EVENTOUT                                                                                            |                         |

| -      | -         | -       | 50      | 60      | P6       | PF12                                                 | I/O      | FT            | -    | FSMC_A6, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 51      | 61      | M8       | V <sub>SS</sub>                                      | S        |               | -    | -                                                                                                             | -                       |

| -      | -         | -       | 52      | 62      | N8       | V <sub>DD</sub>                                      | S        |               | -    | -                                                                                                             | -                       |

| -      | -         | -       | 53      | 63      | N6       | PF13                                                 | I/O      | FT            | -    | FSMC_A7, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 54      | 64      | R7       | PF14                                                 | I/O      | FT            | -    | FSMC_A8, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 55      | 65      | P7       | PF15                                                 | I/O      | FT            | -    | FSMC_A9, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 56      | 66      | N7       | PG0                                                  | I/O      | FT            | -    | FSMC_A10, EVENTOUT                                                                                            | -                       |

| -      | -         | -       | 57      | 67      | M7       | PG1                                                  | I/O      | FT            | -    | FSMC_A11, EVENTOUT                                                                                            | -                       |

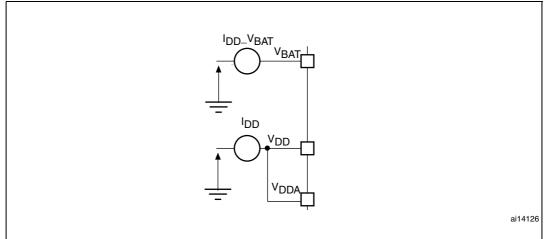

## 6.1.7 Current consumption measurement

### Figure 20. Current consumption measurement scheme

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 11: Voltage characteristics*, *Table 12: Current characteristics*, and *Table 13: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                                       | Min                                                      | Max                 | Unit |

|-----------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------|---------------------|------|

| $V_{DD} - V_{SS}$                 | External main supply voltage (including $V_{DDA}$ , $V_{DD}$ ) <sup>(1)</sup> | -0.3                                                     | 4.0                 |      |

| V                                 | Input voltage on five-volt tolerant pin <sup>(2)</sup>                        | V <sub>SS</sub> -0.3                                     | V <sub>DD</sub> +4  | V    |

| V <sub>IN</sub>                   | Input voltage on any other pin                                                | V <sub>SS</sub> -0.3                                     | 4.0                 |      |

| $ \Delta V_{DDx} $                | Variations between different $V_{DD}$ power pins                              | -                                                        | 50                  | mV   |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins                              | -                                                        | 50                  | 1110 |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                            | see Sectio<br>Absolute n<br>ratings (ele<br>sensitivity) | naximum<br>ectrical | -    |

#### Table 11. Voltage characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

V<sub>IN</sub> maximum value must always be respected. Refer to *Table 12* for the values of the maximum allowed injected current.

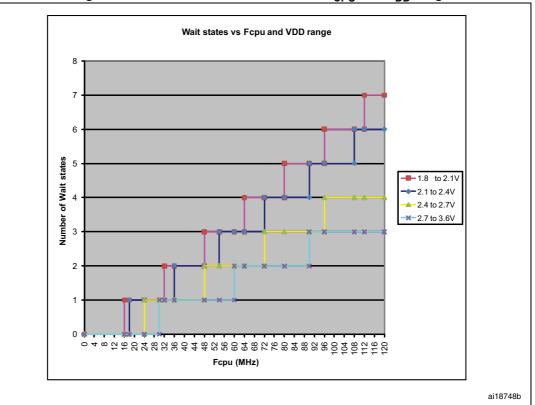

Figure 21. Number of wait states versus  $f_{\mbox{CPU}}$  and  $V_{\mbox{DD}}$  range

1. The supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range and IRROFF is set to  $V_{DD}$ .

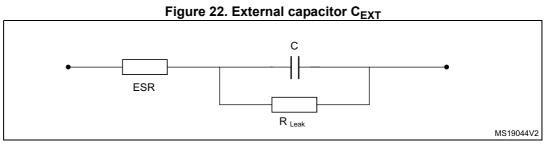

### 6.3.2 VCAP1/VCAP2 external capacitor

Stabilization for the main regulator is achieved by connecting an external capacitor to the VCAP1/VCAP2 pins.  $C_{EXT}$  is specified in *Table 16*.

1. Legend: ESR is the equivalent series resistance.

### Table 16. VCAP1/VCAP2 operating conditions<sup>(1)</sup>

| Symbol | Parameter                         | Conditions |

|--------|-----------------------------------|------------|

| CEXT   | Capacitance of external capacitor | 2.2 µF     |

| ESR    | ESR of external capacitor         | < 2 Ω      |

1. When bypassing the voltage regulator, the two 2.2  $\mu F$  V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

|      | Peripheral <sup>(1)</sup> | Typical consumption at 25 °C | Unit |

|------|---------------------------|------------------------------|------|

|      | SDIO                      | 0.69                         |      |

|      | TIM1                      | 1.06                         |      |

|      | TIM8                      | 1.03                         |      |

|      | TIM9                      | 0.58                         |      |

|      | TIM10                     | 0.37                         |      |

| 4002 | TIM11                     | 0.39                         | m۸   |

| APB2 | ADC1 <sup>(4)</sup>       | 2.13                         | mA   |

|      | ADC2 <sup>(4)</sup>       | 2.04                         |      |

|      | ADC3 <sup>(4)</sup>       | 2.12                         |      |

|      | SPI1                      | 1.20                         |      |

|      | USART1                    | 0.38                         |      |

|      | USART6                    | 0.37                         |      |

Table 26. Peripheral current consumption (continued)

1. External clock is 25 MHz (HSE oscillator with 25 MHz crystal) and PLL is on.

2. EN1 bit is set in DAC\_CR register.

3. EN2 bit is set in DAC\_CR register.

4.  $f_{ADC} = f_{PCLK2}/2$ , ADON bit set in ADC\_CR2 register.

### 6.3.7 Wakeup time from low-power mode

The wakeup times given in *Table 27* is measured on a wakeup phase with a 16 MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                                 | Parameter                                                                                    | Min <sup>(1)</sup> | Тур <sup>(1)</sup> | Max <sup>(1)</sup> | Unit |

|----------------------------------------|----------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

| t <sub>WUSLEEP</sub> <sup>(2)</sup>    | Wakeup from Sleep mode                                                                       | -                  | 1                  | -                  | μs   |

|                                        | Wakeup from Stop mode (regulator in Run mode)                                                | -                  | 13                 | -                  |      |

| t <sub>WUSTOP</sub> <sup>(2)</sup>     | Wakeup from Stop mode (regulator in low-power mode)                                          | -                  | 17                 | 40                 | μs   |

|                                        | Wakeup from Stop mode (regulator in low-power mode and Flash memory in Deep power down mode) | -                  | 110                | -                  | F -  |

| t <sub>WUSTDBY</sub> <sup>(2)(3)</sup> | Wakeup from Standby mode                                                                     | 260                | 375                | 480                | μs   |

1. Guaranteed by characterization results, not tested in production.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first instruction.

3.  $t_{WUSTDBY}$  minimum and maximum values are given at 105 °C and –45 °C, respectively.

## 6.3.8 External clock source characteristics

### High-speed external user clock generated from an external source

The characteristics given in *Table 28* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                     | Parameter                                           | Conditions                       | Min         | Тур                | Max      | Unit |

|--------------------------------------------|-----------------------------------------------------|----------------------------------|-------------|--------------------|----------|------|

| f <sub>HSE_ext</sub>                       | External user clock source frequency <sup>(1)</sup> |                                  | 1           | -                  | 26       | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                 |                                  | $0.7V_{DD}$ | -                  | $V_{DD}$ | V    |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                  | $V_{SS}$                         | -           | $0.3V_{\text{DD}}$ | v        |      |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>              |                                  | 5           | -                  | -        | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>             |                                  | -           | -                  | 20       | 115  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>             | -                                | -           | 5                  | -        | pF   |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                                          | -                                | 45          | -                  | 55       | %    |

| ١L                                         | OSC_IN Input leakage current                        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -           | -                  | ±1       | μA   |

Table 28. High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

### Low-speed external user clock generated from an external source

The characteristics given in *Table 29* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                     | Parameter                                           | Conditions                       | Min         | Тур    | Max                | Unit |

|--------------------------------------------|-----------------------------------------------------|----------------------------------|-------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source frequency <sup>(1)</sup> |                                  | -           | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage               |                                  | $0.7V_{DD}$ | -      | $V_{DD}$           | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                |                                  | $V_{SS}$    | -      | $0.3V_{\text{DD}}$ | v    |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>            | -                                | 450         | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>           |                                  | -           | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>           | -                                | -           | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                          | -                                | 30          | -      | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage current                      | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -           | -      | ±1                 | μA   |

| Table 29. Low-speed external use | r clock characteristics |

|----------------------------------|-------------------------|

|----------------------------------|-------------------------|

1. Guaranteed by design, not tested in production.

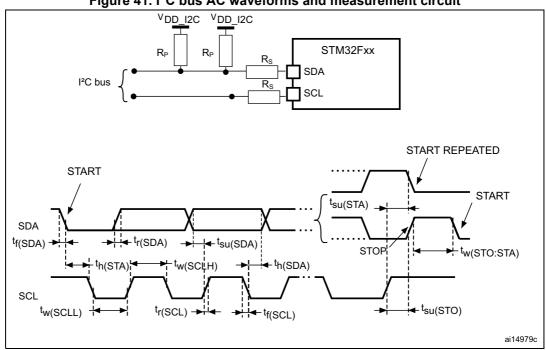

Figure 41. I<sup>2</sup>C bus AC waveforms and measurement circuit

- 1.  $R_S$ = series protection resistor.

- 2. R<sub>P</sub> = external pull-up resistor.

- 3.  $V_{DD_{12C}}$  is the I<sup>2</sup>C bus power supply.

| f (kU-)                | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x8019                  |

| 300                    | 0x8021                  |

| 200                    | 0x8032                  |

| 100                    | 0x0096                  |

| 50                     | 0x012C                  |

| 20                     | 0x02EE                  |

## Table 53. SCL frequency (f<sub>PCLK1</sub>= 30 MHz., V<sub>DD</sub> = 3.3 V)<sup>(1)(2)</sup>

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  = I<sup>2</sup>C speed,

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

| Symbol                                                 | Parameter Conditions                                                  |                                                                                            | Min     | Max                             | Unit |

|--------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|---------------------------------|------|

| f <sub>CK</sub><br>1/t <sub>c(CK)</sub>                | I <sup>2</sup> S clock frequency                                      | Master, 16-bit data,<br>audio frequency = 48 kHz, main<br>clock disabled                   | 1.23    | 1.24                            | MHz  |

| 0(01)                                                  |                                                                       | Slave                                                                                      | 0       | 64F <sub>S</sub> <sup>(1)</sup> |      |

| t <sub>r(CK)</sub><br>t <sub>f(CK)</sub>               | $I^2S$ clock rise and fall time Capacitive load $C_L = 50 \text{ pF}$ |                                                                                            | -       | (2)                             |      |

| t <sub>v(WS)</sub> <sup>(3)</sup>                      | WS valid time                                                         | Master                                                                                     | 0.3     | -                               |      |

| t <sub>h(WS)</sub> <sup>(3)</sup>                      | WS hold time                                                          | Master                                                                                     | 0       | -                               |      |

| t <sub>su(WS)</sub> <sup>(3)</sup>                     | WS setup time                                                         | Slave                                                                                      | 3       | -                               |      |

| t <sub>h(WS)</sub> <sup>(3)</sup>                      | WS hold time                                                          | Slave                                                                                      | 0       | -                               | •    |

| t <sub>w(CKH)</sub> (3)<br>t <sub>w(CKL)</sub> (3)     | CK high and low time                                                  | Master f <sub>PCLK</sub> = 30 MHz                                                          | 396     | -                               | •    |

| $t_{su(SD\_MR)}^{(3)}_{(3)}$<br>$t_{su(SD\_SR)}^{(3)}$ | Data input setup time                                                 | Master receiver<br>Slave receiver                                                          | 45<br>0 | -                               | ns   |

| $t_{h(SD_MR)}^{(3)(4)}_{(3)(4)} t_{h(SD_SR)}^{(3)(4)}$ | Data input hold time                                                  | Master receiver: f <sub>PCLK</sub> = 30 MHz,<br>Slave receiver: f <sub>PCLK</sub> = 30 MHz | 13<br>0 | -                               |      |

| t <sub>v(SD_ST)</sub> (3)(4)                           | Data output valid time                                                | Slave transmitter (after enable edge)                                                      | -       | 30                              | *    |

| t <sub>h(SD_ST)</sub> <sup>(3)</sup>                   | Data output hold time                                                 | Slave transmitter (after enable edge)                                                      | 10      | -                               | *    |

| t <sub>v(SD_MT)</sub> <sup>(3)(4)</sup>                | Data output valid time                                                | Master transmitter (after enable edge)                                                     | -       | 6                               | 1    |

| t <sub>h(SD_MT)</sub> <sup>(3)</sup>                   | Data output hold time                                                 | Master transmitter (after enable edge)                                                     | 0       | -                               | 1    |

## Table 55. I<sup>2</sup>S characteristics

F<sub>S</sub> is the sampling frequency. Refer to the I2S section of the STM32F20xxx/21xxx reference manual for more details. f<sub>CK</sub> values reflect only the digital peripheral behavior which leads to a minimum of (I2SDIV/(2\*I2SDIV+ODD), a maximum of (I2SDIV+ODD)/(2\*I2SDIV+ODD) and F<sub>S</sub> maximum values for each mode/condition.

2. Refer to Table 48: I/O AC characteristics.

3. Guaranteed by design, not tested in production.

4. Depends on  $f_{PCLK}.$  For example, if  $f_{PCLK}$ =8 MHz, then  $T_{PCLK}$  = 1/f\_{PLCLK} =125 ns.

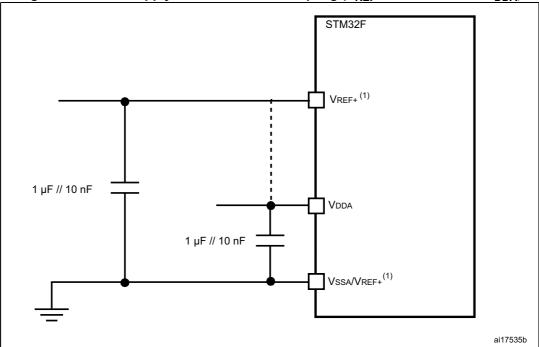

### General PCB design guidelines

Power supply decoupling should be performed as shown in *Figure 54* or *Figure 55*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

V<sub>REF+</sub> and V<sub>REF</sub> inputs are both available on UFBGA176 package. V<sub>REF+</sub> is also available on all packages except for LQFP64. When V<sub>REF+</sub> and V<sub>REF</sub> are not available, they are internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

|                                      | Table 68. DAC characteristics (continued)                                                                                                                             |     |     |                          |      |                                                                                                              |  |  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|------|--------------------------------------------------------------------------------------------------------------|--|--|

| Symbol                               | Parameter                                                                                                                                                             | Min | Тур | Max                      | Unit | Comments                                                                                                     |  |  |

| DAC_OUT<br>min <sup>(2)</sup>        | Lower DAC_OUT voltage<br>with buffer OFF                                                                                                                              | -   | 0.5 | -                        | mV   | It gives the maximum output excursion                                                                        |  |  |

| DAC_OUT<br>max <sup>(2)</sup>        | Higher DAC_OUT voltage<br>with buffer OFF                                                                                                                             | -   | -   | V <sub>REF+</sub> – 1LSB | V    | of the DAC.                                                                                                  |  |  |

| . (4)                                | DAC DC V <sub>REF</sub> current consumption in quiescent                                                                                                              | -   | 170 | 240                      | μA   | With no load, worst code (0x800) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs |  |  |

| I <sub>VREF+</sub> <sup>(4)</sup>    | mode (Standby mode)                                                                                                                                                   | -   | 50  | 75                       | μ    | With no load, worst code (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs |  |  |

|                                      | DAC DC V <sub>DDA</sub> current                                                                                                                                       | -   | 280 | 380                      | μA   | With no load, middle code (0x800) on the inputs                                                              |  |  |

| I <sub>DDA</sub> <sup>(4)</sup>      | consumption in quiescent mode <sup>(3)</sup>                                                                                                                          | -   | 475 | 625                      | μA   | With no load, worst code (0xF1C) at $V_{REF+} = 3.6 V$ in terms of DC consumption on the inputs              |  |  |

| DNL <sup>(4)</sup>                   | Differential non linearity<br>Difference between two                                                                                                                  | -   | -   | ±0.5                     | LSB  | Given for the DAC in 10-bit configuration.                                                                   |  |  |

| consecutive code-1LSB)               |                                                                                                                                                                       | -   | -   | ±2                       | LSB  | Given for the DAC in 12-bit configuration.                                                                   |  |  |

|                                      | Integral non linearity<br>(difference between<br>measured value at Code i<br>and the value at Code i on<br>a line drawn between<br>Code 0 and last Code<br>1023)      | -   | -   | ±1                       | LSB  | Given for the DAC in 10-bit configuration.                                                                   |  |  |

| INL <sup>(4)</sup>                   |                                                                                                                                                                       | -   | -   | ±4                       | LSB  | Given for the DAC in 12-bit configuration.                                                                   |  |  |

|                                      | Offset error                                                                                                                                                          | -   | -   | ±10                      | mV   | -                                                                                                            |  |  |

| Offset <sup>(4)</sup>                | (difference between<br>measured value at Code                                                                                                                         | -   | -   | ±3                       | LSB  | Given for the DAC in 10-bit at V <sub>REF+</sub> =<br>3.6 V                                                  |  |  |

|                                      | (0x800) and the ideal<br>value = V <sub>REF+</sub> /2)                                                                                                                | -   | -   | ±12                      | LSB  | Given for the DAC in 12-bit at $V_{REF+}$ = 3.6 V                                                            |  |  |

| Gain<br>error <sup>(4)</sup>         | Gain error                                                                                                                                                            | -   | -   | ±0.5                     | %    | Given for the DAC in 12-bit configuration                                                                    |  |  |

| t <sub>SETTLING</sub> <sup>(4)</sup> | Settling time (full scale: for<br>a 10-bit input code<br>transition between the<br>lowest and the highest<br>input codes when<br>DAC_OUT reaches final<br>value ±4LSB | -   | 3   | 6                        | μs   | C <sub>LOAD</sub> ≤ 50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ                                                       |  |  |

| THD <sup>(4)</sup>                   | Total Harmonic Distortion<br>Buffer ON                                                                                                                                | -   | -   | -                        | dB   | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                            |  |  |

### Table 68. DAC characteristics (continued)

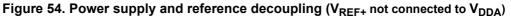

Figure 58. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

| Table 73. A | Asynchronous non-multiplexed SRAM | M/PSRAM/NO | R write timin | gs <sup>(1)(2)</sup> |

|-------------|-----------------------------------|------------|---------------|----------------------|

|             |                                   |            |               |                      |

| Symbol                   | Parameter                                | Min                     | Мах                     | Unit |

|--------------------------|------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>       | FSMC_NE low time                         | 3T <sub>HCLK</sub>      | 3T <sub>HCLK</sub> + 4  | ns   |

| t <sub>v(NWE_NE</sub> )  | FSMC_NEx low to FSMC_NWE low             | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>w(NWE)</sub>      | FSMC_NWE low time                        | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 3   | ns   |

| t <sub>h(NE_NWE)</sub>   | FSMC_NWE high to FSMC_NE high hold time  | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>v(A_NE)</sub>     | FSMC_NEx low to FSMC_A valid             | -                       | 0                       | ns   |

| t <sub>h(A_NWE)</sub>    | Address hold time after FSMC_NWE high    | T <sub>HCLK</sub> - 3   | -                       | ns   |

| t <sub>v(BL_NE)</sub>    | FSMC_NEx low to FSMC_BL valid            | -                       | 0.5                     | ns   |

| t <sub>h(BL_NWE)</sub>   | FSMC_BL hold time after FSMC_NWE<br>high | T <sub>HCLK</sub> – 1   | -                       | ns   |

| t <sub>v(Data_NE)</sub>  | Data to FSMC_NEx low to Data valid       | -                       | T <sub>HCLK</sub> + 5   | ns   |

| t <sub>h(Data_NWE)</sub> | Data hold time after FSMC_NWE high       | T <sub>HCLK</sub> +0.5  | -                       | ns   |

| t <sub>v(NADV_NE)</sub>  | FSMC_NEx low to FSMC_NADV low            | -                       | 2                       | ns   |

| t <sub>w(NADV)</sub>     | FSMC_NADV low time                       | -                       | T <sub>HCLK</sub> + 1.5 | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

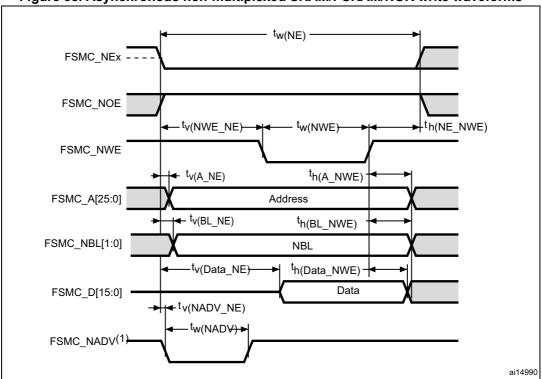

# 7.2 WLCSP64+2 package information

Figure 79. WLCSP64+2 - 66-ball, 3.639 x 3.971 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

| Table 88. WLCSP64+2 - 66-ball, 4.539 x 4.911 mm, 0.4 mm pitch wafer level chip scale |

|--------------------------------------------------------------------------------------|

| package mechanical data                                                              |

| Symbol           |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |

|------------------|-------|-------------|-------|-----------------------|--------|--------|--|

| Symbol           | Min   | Тур         | Max   | Min                   | Тур    | Мах    |  |

| А                | 0.540 | 0.570       | 0.600 | 0.0213                | 0.0224 | 0.0236 |  |

| A1               | -     | 0.190       | -     | -                     | 0.0075 | -      |  |

| A2               | -     | 0.380       | -     | -                     | 0.0150 | -      |  |

| A3               | -     | 0.025       | -     | -                     | 0.010  | -      |  |

| b <sup>(2)</sup> | 0.240 | 0.270       | 0.300 | 0.0094                | 0.0106 | 0.0118 |  |

| D                | 3.604 | 3.939       | 3.674 | 0.1419                | 0.1551 | 0.1446 |  |

| E                | 3.936 | 3.971       | 4.006 | 0.1550                | 0.1563 | 0.1577 |  |

| е                | -     | 0.400       | -     | -                     | 0.0157 | -      |  |

| e1               | -     | 3.200       | -     | -                     | 0.1260 | -      |  |

| e2               | -     | 3.200       | -     | -                     | 0.1260 | -      |  |