Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | ARM® Cortex®-M3                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 120MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT      |

| Number of I/O              | 51                                                                     |

| Program Memory Size        | 1MB (1M x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 132K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

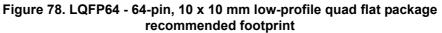

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205rgt6w |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 84. | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline      | 158 |

|------------|--------------------------------------------------------------------------|-----|

| Figure 85. | LQFP144 - 144-pin,20 x 20 mm low-profile quad flat package               |     |

|            | recommended footprint                                                    | 160 |

| Figure 86. | LQFP144 marking (package top view)                                       | 161 |

|            | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline      |     |

| Figure 88. | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package              |     |

| U          | recommended footprint                                                    | 164 |

| Figure 89. | UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch,                       |     |

| U          | ultra fine pitch ball grid array package outline                         | 165 |

| Figure 90. | UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball |     |

| U          | grid array package recommended footprint                                 | 166 |

#### Table 2. STM32F205xx features and peripheral counts (continued)

| Peripherals            | ST                                                  | M32F205Rx               |  |                    | STM32F205Vx | STM32F205Zx |  |  |  |

|------------------------|-----------------------------------------------------|-------------------------|--|--------------------|-------------|-------------|--|--|--|

| Operating temperatures | Ambient temperatures: -40 to +85 °C /-40 to +105 °C |                         |  |                    |             |             |  |  |  |

|                        | Junction temperature: -40 to + 125 °C               |                         |  |                    |             |             |  |  |  |

| Package                | LQFP64                                              | LQFP64<br>WLCSP64<br>+2 |  | FP64<br>CSP6<br>+2 | LQFP100     | LQFP144     |  |  |  |

For the LQFP100 package, only FSMC Bank1 or Bank2 are available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select. Bank2 can only support a 16- or 8-bit NAND Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available in this package.

2. The SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I2S audio mode.

On devices in WLCSP64+2 package, if IRROFF is set to V<sub>DD</sub>, the supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor (see Section 3.16).

|                   | Peripherals             |                    | STM3 | 2F207Vx |      | STM32F207Zx |     |     |      | STM32F207Ix |     |  |  |  |  |  |

|-------------------|-------------------------|--------------------|------|---------|------|-------------|-----|-----|------|-------------|-----|--|--|--|--|--|

| Flash memory in I | Kbytes                  | 256                | 512  | 768     | 1024 | 256         | 512 | 768 | 1024 | 256         | 512 |  |  |  |  |  |

| SRAM in Kbytes    | System<br>(SRAM1+SRAM2) | 128<br>(112+16)    |      |         |      |             |     |     |      |             |     |  |  |  |  |  |

|                   | Backup                  | 4                  |      |         |      |             |     |     |      |             |     |  |  |  |  |  |

| FSMC memory co    | ontroller               | Yes <sup>(1)</sup> |      |         |      |             |     |     |      |             |     |  |  |  |  |  |

| Ethernet          |                         | Yes                |      |         |      |             |     |     |      |             |     |  |  |  |  |  |

|                   | General-purpose         | 10                 |      |         |      |             |     |     |      |             |     |  |  |  |  |  |

|                   | Advanced-control        | 2                  |      |         |      |             |     |     |      |             |     |  |  |  |  |  |

| Timers            | Basic                   | 2                  |      |         |      |             |     |     |      |             |     |  |  |  |  |  |

|                   | IWDG                    | Yes                |      |         |      |             |     |     |      |             |     |  |  |  |  |  |

|                   | WWDG                    | Yes                |      |         |      |             |     |     |      |             |     |  |  |  |  |  |

| RTC               |                         | Yes                |      |         |      |             |     |     |      |             |     |  |  |  |  |  |

| Random number     | generator               | Yes                |      |         |      |             |     |     |      |             |     |  |  |  |  |  |

#### Table 3. STM32F207xx features and peripheral counts

# 3.4 Embedded Flash memory

The STM32F20x devices embed a 128-bit wide Flash memory of 128 Kbytes, 256 Kbytes, 512 Kbytes, 768 Kbytes or 1 Mbyte available for storing programs and data.

The devices also feature 512 bytes of OTP memory that can be used to store critical user data such as Ethernet MAC addresses or cryptographic keys.

# 3.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 3.6 Embedded SRAM

All STM32F20x products embed:

- Up to 128 Kbytes of system SRAM accessed (read/write) at CPU clock speed with 0 wait states

- 4 Kbytes of backup SRAM.

The content of this area is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

## 3.7 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS) and the slaves (Flash memory, RAM, FSMC, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

There are three power modes configured by software when the regulator is ON:

- MR is used in the nominal regulation mode

- LPR is used in Stop modes

The LP regulator mode is configured by software when entering Stop mode.

• Power-down is used in Standby mode.

The Power-down mode is activated only when entering Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost).

Two external ceramic capacitors should be connected on  $V_{CAP_1}$  and  $V_{CAP_2}$  pin. Refer to *Figure 19: Power supply scheme* and *Table 16: VCAP1/VCAP2 operating conditions*.

All packages have the regulator ON feature.

## 3.16.2 Regulator OFF

This feature is available only on packages featuring the REGOFF pin. The regulator is disabled by holding REGOFF high. The regulator OFF mode allows to supply externally a V12 voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins.

The two 2.2 µF ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Figure 19: Power supply scheme*.

When the regulator is OFF, there is no more internal monitoring on V12. An external power supply supervisor should be used to monitor the V12 of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on V12 power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset the part of the 1.2 V logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used at power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection at reset or pre-reset is required.

### Regulator OFF/internal reset ON

On WLCSP64+2 package, this mode is activated by connecting REGOFF pin to V<sub>DD</sub> and IRROFF pin to V<sub>SS</sub>. On UFBGA176 package, only REGOFF must be connected to V<sub>DD</sub> (IRROFF not available). In this mode,  $V_{DD}/V_{DDA}$  minimum value is 1.8 V.

The regulator OFF/internal reset ON mode allows to supply externally a 1.2 V voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins, in addition to V<sub>DD</sub>.

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The TIM1 and TIM8 counters can be frozen in debug mode. Many of the advanced-control timer features are shared with those of the standard TIMx timers which have the same architecture. The advanced-control timer can therefore work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

### 3.20.2 General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F20x devices (see *Table 5* for differences).

#### TIM2, TIM3, TIM4, TIM5

The STM32F20x include 4 full-featured general-purpose timers. TIM2 and TIM5 are 32-bit timers, and TIM3 and TIM4 are 16-bit timers. The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

The counters of TIM2, TIM3, TIM4, TIM5 can be frozen in debug mode. Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

#### TIM10, TIM11 and TIM9

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10 and TIM11 feature one independent channel, whereas TIM9 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

#### TIM12, TIM13 and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM13 and TIM14 feature one independent channel, whereas TIM12 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers.

They can also be used as simple time bases.

### 3.20.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

DocID15818 Rev 13

### Pinouts and pin description

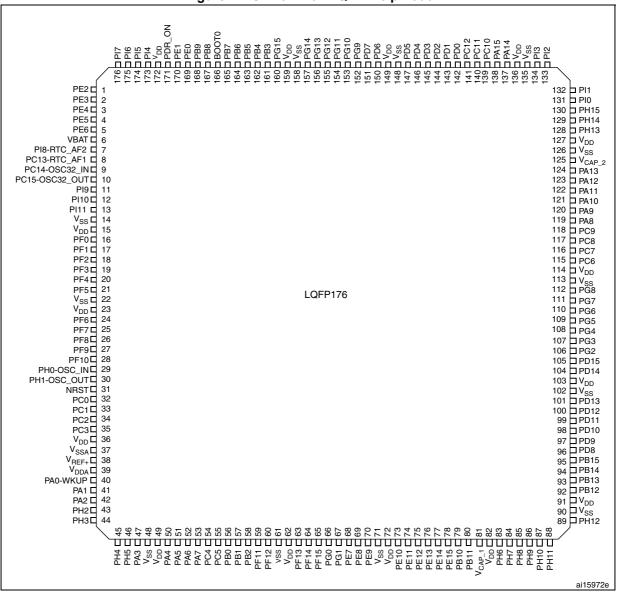

| Figure 14. | STM32F20x L | .QFP176 pi | nout |

|------------|-------------|------------|------|

|------------|-------------|------------|------|

1. RFU means "reserved for future use". This pin can be tied to  $V_{DD}$ ,  $V_{SS}$  or left unconnected.

2. The above figure shows the package top view.

|        |           | Pi      | ns      |         |          |                                                      |                                        |                                                                 |      |                                                                                                      |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type                               | I/O structure                                                   | Note | Alternate functions                                                                                  | Additional<br>functions |

| -      | -         | 38      | 58      | 68      | R8       | PE7                                                  | I/O                                    | FT                                                              | -    | FSMC_D4,TIM1_ETR,<br>EVENTOUT                                                                        | -                       |

| -      | -         | 39      | 59      | 69      | P8       | PE8                                                  | I/O                                    | FT                                                              | -    | FSMC_D5,TIM1_CH1N,<br>EVENTOUT                                                                       | -                       |

| -      | -         | 40      | 60      | 70      | P9       | PE9                                                  | I/O                                    | FT                                                              | -    | FSMC_D6,TIM1_CH1,<br>EVENTOUT                                                                        | -                       |

| -      | -         | -       | 61      | 71      | M9       | V <sub>SS</sub>                                      | S                                      |                                                                 | -    | -                                                                                                    | -                       |

| -      | -         | -       | 62      | 72      | N9       | V <sub>DD</sub>                                      | S                                      |                                                                 | -    | -                                                                                                    | -                       |

| -      | -         | 41      | 63      | 73      | R9       | PE10                                                 | I/O                                    | /O FT - FSMC_D7,TIM1_CH2N,<br>EVENTOUT                          |      | -                                                                                                    |                         |

| -      | -         | 42      | 64      | 74      | P10      | PE11                                                 | I/O FT - FSMC_D8,TIM1_CH2,<br>EVENTOUT |                                                                 | -    |                                                                                                      |                         |

| -      | -         | 43      | 65      | 75      | R10      | PE12                                                 | I/O                                    | FT                                                              | -    | FSMC_D9,TIM1_CH3N,<br>EVENTOUT                                                                       | -                       |

| -      | -         | 44      | 66      | 76      | N11      | PE13                                                 | I/O                                    | FT                                                              | -    | FSMC_D10,TIM1_CH3,<br>EVENTOUT                                                                       | -                       |

| -      | -         | 45      | 67      | 77      | P11      | PE14                                                 | I/O                                    | FT                                                              | -    | FSMC_D11,TIM1_CH4,<br>EVENTOUT                                                                       | -                       |

| -      | -         | 46      | 68      | 78      | R11      | PE15                                                 | I/O                                    | FT                                                              | -    | FSMC_D12,TIM1_BKIN,<br>EVENTOUT                                                                      | -                       |

| 29     | H3        | 47      | 69      | 79      | R12      | PB10                                                 | I/O                                    | FT                                                              | -    | SPI2_SCK, I2S2_SCK,<br>I2C2_SCL,USART3_TX,OT<br>G_HS_ULPI_D3,ETH_MII_R<br>X_ER,TIM2_CH3,<br>EVENTOUT | -                       |

| 30     | J2        | 48      | 70      | 80      | R13      | PB11                                                 | I/O                                    | I/O FT - ETH_MII_TX_EN,<br>ETH_MII_TX_EN,<br>TIM2_CH4, EVENTOUT |      | -                                                                                                    |                         |

| 31     | J3        | 49      | 71      | 81      | M10      | V <sub>CAP_1</sub>                                   | S                                      |                                                                 | -    | -                                                                                                    | -                       |

| 32     | -         | 50      | 72      | 82      | N10      | V <sub>DD</sub>                                      | S                                      |                                                                 | -    | -                                                                                                    | -                       |

| -      | -         | -       | -       | 83      | M11      | PH6                                                  | I/O                                    | FT                                                              | -    | I2C2_SMBA, TIM12_CH1,<br>ETH_MII_RXD2,<br>EVENTOUT                                                   | -                       |

| Table 8. STM32F20x pin and ball definitions (continue | d) |

|-------------------------------------------------------|----|

|                                                       | ,  |

60/182

DocID15818 Rev 13

|        | Table 10. Alternate function mapping |                |                        |           |              |                |                |                     |            |                    |                           |                    |                                            |                      |            |       |          |

|--------|--------------------------------------|----------------|------------------------|-----------|--------------|----------------|----------------|---------------------|------------|--------------------|---------------------------|--------------------|--------------------------------------------|----------------------|------------|-------|----------|

|        |                                      | AF0            | AF1                    | AF2       | AF3          | AF4            | AF5            | AF6                 | AF7        | AF8                | AF9                       | AF10               | AF11                                       | AF12                 | AF13       |       |          |

|        | Port                                 | SYS            | TIM1/2                 | TIM3/4/5  | TIM8/9/10/11 | 12C1/12C2/12C3 | SPI1/SPI2/I2S2 | SPI3/I2S3           | USART1/2/3 | UART4/5/<br>USART6 | CAN1/CAN2/<br>TIM12/13/14 | OTG_FS/ OTG_HS     | ЕТН                                        | FSMC/SDIO/<br>OTG_HS | DCMI       | AF014 | AF15     |

|        | PA0-WKUP                             | -              | TIM2_CH1_ETR           | TIM 5_CH1 | TIM8_ETR     | -              | -              |                     | USART2_CTS | UART4_TX           | -                         | -                  | ETH_MII_CRS                                | -                    | -          | -     | EVENTOUT |

|        | PA1                                  | -              | TIM2_CH2               | TIM5_CH2  | -            | -              | -              |                     | USART2_RTS | UART4_RX           | -                         | -                  | ETH_MII<br>_RX_CLK<br>ETH_RMII<br>_REF_CLK | -                    | -          | -     | EVENTOUT |

|        | PA2                                  | -              | TIM2_CH3               | TIM5_CH3  | TIM9_CH1     | -              | -              |                     | USART2_TX  | -                  | -                         | -                  | ETH_MDIO                                   | -                    | -          | -     | EVENTOUT |

|        | PA3                                  | -              | TIM2_CH4               | TIM5_CH4  | TIM9_CH2     | -              | -              |                     | USART2_RX  | -                  | -                         | OTG_HS_ULPI_D0     | ETH _MII_COL                               | -                    | -          | -     | EVENTOUT |

|        | PA4                                  | -              | -                      | -         | -            | -              | SPI1_NSS       | SPI3_NSS<br>I2S3_WS | USART2_CK  | -                  | -                         |                    | -                                          | OTG_HS_SOF           | DCMI_HSYNC | -     | EVENTOUT |

|        | PA5                                  | -              | TIM2_CH1_ETR           | -         | TIM8_CH1N    | -              | SPI1_SCK       | -                   | -          | -                  | -                         | OTG_HS_ULPI_C<br>K | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA6                                  | -              | TIM1_BKIN              | TIM3_CH1  | TIM8_BKIN    | -              | SPI1_MISO      | -                   | -          | -                  | TIM13_CH1                 | -                  | -                                          | -                    | DCMI_PIXCK | -     | EVENTOUT |

| Port A | PA7                                  | -              | TIM1_CH1N              | TIM3_CH2  | TIM8_CH1N    | -              | SPI1_MOSI      | -                   | -          | -                  | TIM14_CH1                 | -                  | ETH_MII_RX_DV<br>ETH_RMII<br>_CRS_DV       | -                    | -          | -     | EVENTOUT |

|        | PA8                                  | MCO1           | TIM1_CH1               | -         | -            | I2C3_SCL       | -              | -                   | USART1_CK  | -                  | -                         | OTG_FS_SOF         | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA9                                  | -              | TIM1_CH2               | -         | -            | I2C3_SMBA      | -              | -                   | USART1_TX  | -                  | -                         |                    | -                                          | -                    | DCMI_D0    | -     | EVENTOUT |

|        | PA10                                 | -              | TIM1_CH3               | -         | -            | -              | -              | -                   | USART1_RX  | -                  | -                         | OTG_FS_ID          | -                                          | -                    | DCMI_D1    | -     | EVENTOUT |

|        | PA11                                 | -              | TIM1_CH4               | -         | -            | -              | -              | -                   | USART1_CTS | -                  | CAN1_RX                   | OTG_FS_DM          | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA12                                 | -              | TIM1_ETR               | -         | -            | -              | -              | -                   | USART1_RTS | -                  | CAN1_TX                   | OTG_FS_DP          | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA13                                 | JTMS-<br>SWDIO | -                      | -         | -            | -              | -              | -                   | -          | -                  | -                         | -                  | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA14                                 | JTCK-<br>SWCLK | -                      | -         | -            | -              | -              | -                   | -          | -                  | -                         | -                  | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA15                                 | JTDI           | TIM 2_CH1<br>TIM 2_ETR | -         | -            | -              | SPI1_NSS       | SPI3_NSS<br>I2S3_WS | -          | -                  | -                         | -                  | -                                          | -                    | -          | -     | EVENTOUT |

5

## 6.3.5 Embedded reset and power control block characteristics

The parameters given in *Table 19* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                              | Parameter                                     | Conditions                     | Min  | Тур  | Мах                                                                                                                                                                                            | Unit |

|-------------------------------------|-----------------------------------------------|--------------------------------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                     |                                               | PLS[2:0]=000 (rising edge)     | 2.09 | 2.14 | 2.19                                                                                                                                                                                           | V    |

|                                     |                                               | PLS[2:0]=000 (falling<br>edge) | 1.98 | 2.04 | 2.08                                                                                                                                                                                           | V    |

|                                     |                                               | PLS[2:0]=001 (rising edge)     | 2.23 | 2.30 | 2.37                                                                                                                                                                                           | V    |

|                                     |                                               | PLS[2:0]=001 (falling<br>edge) | 2.13 | 2.19 | 2.25                                                                                                                                                                                           | V    |

|                                     |                                               | PLS[2:0]=010 (rising edge)     | 2.39 | 2.45 | 2.51                                                                                                                                                                                           | V    |

|                                     |                                               | PLS[2:0]=010 (falling edge)    | 2.29 | 2.35 | 2.39                                                                                                                                                                                           | V    |

|                                     |                                               | PLS[2:0]=011 (rising edge)     | 2.54 | 2.60 | 2.65                                                                                                                                                                                           | V    |

| V <sub>PVD</sub>                    | Programmable voltage detector level selection | PLS[2:0]=011 (falling<br>edge) | 2.44 | 2.51 | 2.56                                                                                                                                                                                           | V    |

|                                     |                                               | PLS[2:0]=100 (rising edge)     | 2.70 | 2.76 | 2.82                                                                                                                                                                                           | V    |

|                                     |                                               | PLS[2:0]=100 (falling<br>edge) | 2.59 | 2.66 | 2.71                                                                                                                                                                                           | V    |

|                                     |                                               | PLS[2:0]=101 (rising edge)     | 2.86 | 2.93 | 2.99                                                                                                                                                                                           | V    |

|                                     |                                               | PLS[2:0]=101 (falling<br>edge) | 2.65 | 2.84 | 3.02                                                                                                                                                                                           | V    |

|                                     |                                               | PLS[2:0]=110 (rising edge)     | 2.96 | 3.03 | 2.65<br>2.56<br>2.82<br>2.71<br>2.99                                                                                                                                                           | V    |

|                                     |                                               | PLS[2:0]=110 (falling<br>edge) | 2.85 | 2.93 | 2.99                                                                                                                                                                                           | V    |

|                                     |                                               | PLS[2:0]=111 (rising edge)     | 3.07 | 3.14 | 3.02<br>3.10<br>2.99                                                                                                                                                                           | V    |

|                                     |                                               | PLS[2:0]=111 (falling<br>edge) | 2.95 | 3.03 | 3.09                                                                                                                                                                                           | V    |

| V <sub>PVDhyst</sub> <sup>(1)</sup> | PVD hysteresis                                | -                              | -    | 100  | -                                                                                                                                                                                              | mV   |

|                                     | Power-on/power-down                           | Falling edge                   | 1.60 | 1.68 | 1.76                                                                                                                                                                                           | V    |

| V <sub>POR/PDR</sub>                | reset threshold                               | Rising edge                    | 1.64 | 1.72 | 1.80                                                                                                                                                                                           | V    |

| V <sub>PDRhyst</sub> <sup>(1)</sup> | PDR hysteresis                                | -                              | -    | 40   | -                                                                                                                                                                                              | mV   |

|                                     | Brownout level 1                              | Falling edge                   | 2.13 | 2.19 | 2.24                                                                                                                                                                                           | V    |

| V <sub>BOR1</sub>                   | threshold                                     | Rising edge                    | 2.23 | 2.29 | 2.19<br>2.08<br>2.37<br>2.25<br>2.51<br>2.51<br>2.39<br>2.65<br>2.56<br>2.56<br>2.82<br>2.71<br>2.99<br>3.02<br>3.10<br>2.99<br>3.02<br>3.10<br>2.99<br>3.21<br>3.09<br>-<br>1.76<br>1.80<br>- | V    |

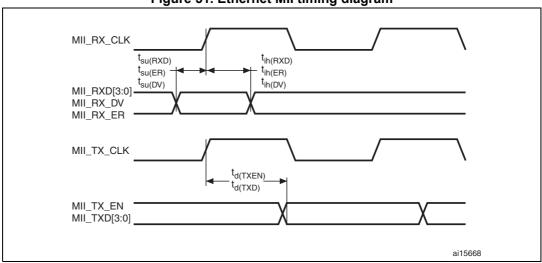

*Table 65* gives the list of Ethernet MAC signals for MII and *Figure 50* shows the corresponding timing diagram.

| Table 65, Dy | namics char | acteristics:  | Ethernet | MAC sid | anals for M   | 111 |

|--------------|-------------|---------------|----------|---------|---------------|-----|

|              |             | uotor 15t105. | Ethornot | MIAO SI | jiiuis ioi ii |     |

| Symbol               | Rating                           | Min | Тур | Мах | Unit |

|----------------------|----------------------------------|-----|-----|-----|------|

| t <sub>su(RXD)</sub> | Receive data setup time          | 7.5 | -   | -   | ns   |

| t <sub>ih(RXD)</sub> | Receive data hold time           | 1   | -   | -   | ns   |

| t <sub>su(DV)</sub>  | Data valid setup time            | 4   | -   | -   | ns   |

| t <sub>ih(DV)</sub>  | Data valid hold time             | 0   | -   | -   | ns   |

| t <sub>su(ER)</sub>  | Error setup time                 | 3.5 | -   | -   | ns   |

| t <sub>ih(ER)</sub>  | Error hold time                  | 0   | -   | -   | ns   |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time | -   | 11  | 14  | ns   |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | -   | 11  | 14  | ns   |

## CAN (controller area network) interface

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CANTX and CANRX).

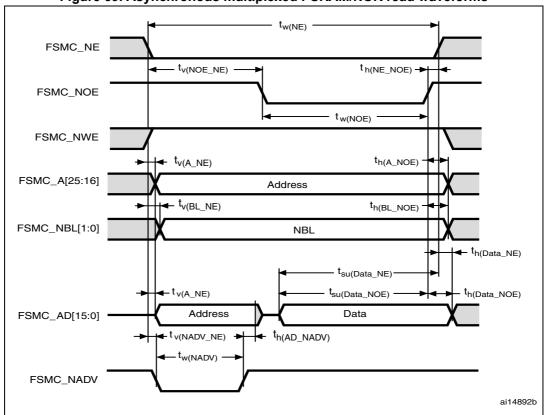

Figure 59. Asynchronous multiplexed PSRAM/NOR read waveforms

Table 74. Asynchronous multiplexed PSRAM/NOR read timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                                                | Min                     | Max                     | Unit |

|---------------------------|----------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                                         | 3T <sub>HCLK</sub> -1   | 3T <sub>HCLK</sub> +1   | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low                             | 2T <sub>HCLK</sub>      | 2T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                                        | T <sub>HCLK</sub> -1    | T <sub>HCLK</sub> +1    | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time                  | 0                       | -                       | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                             | -                       | 2                       | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                            | 1                       | 2.5                     | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                                       | T <sub>HCLK</sub> – 1.5 | T <sub>HCLK</sub>       | ns   |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD(adress) valid hold time after<br>FSMC_NADV high) | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high                    | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL time after FSMC_NOE high                         | 0                       | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                            | -                       | 1                       | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time                         | T <sub>HCLK</sub> + 2   | -                       | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOE high setup time                         | T <sub>HCLK</sub> + 3   | -                       | ns   |

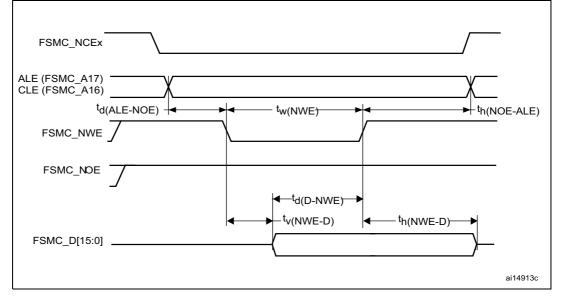

| Symbol                    | Parameter                             | Min                     | Мах                  | Unit |

|---------------------------|---------------------------------------|-------------------------|----------------------|------|

| t <sub>h(A_NWE)</sub>     | Address hold time after FSMC_NWE high | T <sub>HCLK</sub> – 0.5 | -                    | ns   |

| t <sub>h(BL_NWE)</sub>    | FSMC_BL hold time after FSMC_NWE high | T <sub>HCLK</sub> - 1   | -                    | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid         | -                       | 0.5                  | ns   |

| t <sub>v(Data_NADV)</sub> | FSMC_NADV high to Data valid          | -                       | T <sub>HCLK</sub> +2 | ns   |

| t <sub>h(Data_NWE)</sub>  | Data hold time after FSMC_NWE high    | Т <sub>НСLК</sub> – 0.5 | -                    | ns   |

Table 75. Asynchronous multiplexed PSRAM/NOR write timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

### Synchronous waveforms and timings

*Figure 61* through *Figure 64* represent synchronous waveforms, and *Table 77* through *Table 79* provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

- BurstAccessMode = FSMC\_BurstAccessMode\_Enable;

- MemoryType = FSMC\_MemoryType\_CRAM;

- WriteBurst = FSMC\_WriteBurst\_Enable;

- CLKDivision = 1; (0 is not supported, see the STM32F20xxx/21xxx reference manual)

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

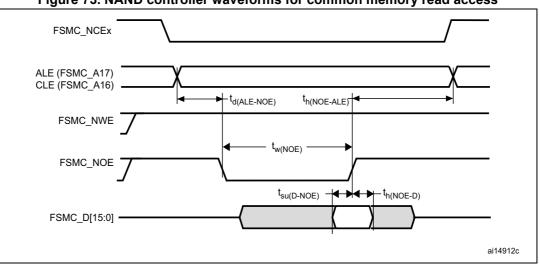

Figure 73. NAND controller waveforms for common memory read access

Figure 74. NAND controller waveforms for common memory write access

Table 82. Switching characteristics for NAND Flash read cycles<sup>(1)(2)</sup>

| Symbol                  | Parameter                                    | Min                    | Мах                    | Unit |

|-------------------------|----------------------------------------------|------------------------|------------------------|------|

| t <sub>w(N0E)</sub>     | FSMC_NOE low width                           | 4T <sub>HCLK</sub> - 1 | 4T <sub>HCLK</sub> + 2 | ns   |

| t <sub>su(D-NOE)</sub>  | FSMC_D[15-0] valid data before FSMC_NOE high | 9                      | -                      | ns   |

| t <sub>h(NOE-D</sub> )  | FSMC_D[15-0] valid data after FSMC_NOE high  | 3                      | -                      | ns   |

| t <sub>d(ALE-NOE)</sub> | FSMC_ALE valid before FSMC_NOE low           | -                      | 3T <sub>HCLK</sub>     | ns   |

| t <sub>h(NOE-ALE)</sub> | FSMC_NWE high to FSMC_ALE invalid            | 3T <sub>HCLK</sub> + 2 | -                      | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Мах   | Min    | Тур                   | Мах    |

| С      | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |

| D      | -     | 12.000      | -     | -      | 0.4724                | -      |

| D1     | -     | 10.000      | -     | -      | 0.3937                | -      |

| D3     | -     | 7.500       | -     | -      | 0.2953                | -      |

| Е      | -     | 12.000      | -     | -      | 0.4724                | -      |

| E1     | -     | 10.000      | -     | -      | 0.3937                | -      |

| E3     | -     | 7.500       | -     | -      | 0.2953                | -      |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |

| К      | 0°    | 3.5°        | 7°    | 0°     | 3.5°                  | 7°     |

| L      | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |

| L1     | -     | 1.000       | -     | -      | 0.0394                | -      |

| CCC    | -     | -           | 0.080 | -      | -                     | 0.0031 |

# Table 87. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

# Table 88. WLCSP64+2 - 66-ball, 4.539 x 4.911 mm, 0.4 mm pitch wafer level chip scale package mechanical data (continued)

| Symbol | millimeters |       |       |     | inches <sup>(1)</sup> |        |

|--------|-------------|-------|-------|-----|-----------------------|--------|

| Symbol | Min         | Тур   | Мах   | Min | Тур                   | Max    |

| F      | -           | 0.220 | -     | -   | 0.0087                | -      |

| G      | -           | 0.386 | -     | -   | 0.0152                | -      |

| ааа    | -           | -     | 0.100 | -   | -                     | 0.0039 |

| bbb    | -           | -     | 0.100 | -   | -                     | 0.0039 |

| CCC    | -           | -     | 0.100 | -   | -                     | 0.0039 |

| ddd    | -           | -     | 0.050 | -   | -                     | 0.0020 |

| eee    | -           | -     | 0.050 | -   | -                     | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

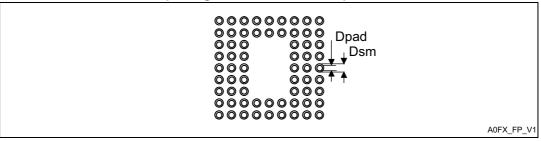

# Figure 80. WLCSP64+2 - 66-ball, 4.539 x 4.911 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

#### Table 89. WLCSP64 recommended PCB design rules (0.4 mm pitch)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.4                                                              |

| Dpad              | 0.225 mm                                                         |

| Dsm               | 0.290 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.250 mm                                                         |

| Stencil thickness | 0.100 mm                                                         |

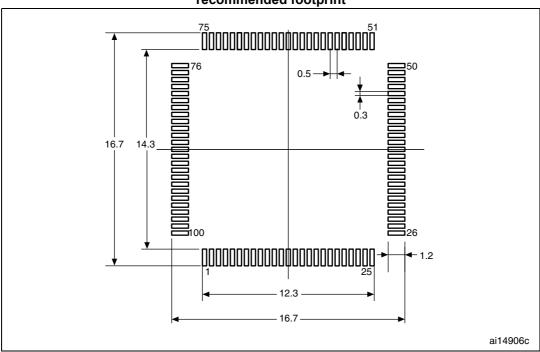

| Currente e l |        | millimeters |        |        | inches <sup>(1)</sup> |        |

|--------------|--------|-------------|--------|--------|-----------------------|--------|

| Symbol       | Min    | Тур         | Мах    | Min    | Тур                   | Max    |

| D3           | -      | 12.000      | -      | -      | 0.4724                | -      |

| Е            | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |

| E1           | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |

| E3           | -      | 12.000      | -      | -      | 0.4724                | -      |

| е            | -      | 0.500       | -      | -      | 0.0197                | -      |

| L            | 0.450  | 0.600       | 0.750  | 0.0177 | 0.0236                | 0.0295 |

| L1           | -      | 1.000       | -      | -      | 0.0394                | -      |

| k            | 0.0°   | 3.5°        | 7.0°   | 0.0°   | 3.5°                  | 7.0°   |

| CCC          | -      | -           | 0.080  | -      | -                     | 0.0031 |

# Table 90. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat packagemechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

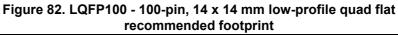

# 7.4 LQFP144 package information

Figure 84. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline

1. Drawing is not to scale.

| O mark of | millimeters |        |        |        | inches <sup>(1)</sup> |        |

|-----------|-------------|--------|--------|--------|-----------------------|--------|

| Symbol    | Min         | Тур    | Мах    | Min    | Тур                   | Max    |

| А         | -           | -      | 1.600  | -      | -                     | 0.0630 |

| A1        | 0.050       | -      | 0.150  | 0.0020 | -                     | 0.0059 |

| A2        | 1.350       | 1.400  | 1.450  | 0.0531 | 0.0551                | 0.0571 |

| b         | 0.170       | 0.220  | 0.270  | 0.0067 | 0.0087                | 0.0106 |

| С         | 0.090       | -      | 0.200  | 0.0035 | -                     | 0.0079 |

| D         | 21.800      | 22.000 | 22.200 | 0.8583 | 0.8661                | 0.8740 |

| D1        | 19.800      | 20.000 | 20.200 | 0.7795 | 0.7874                | 0.7953 |

| D3        | -           | 17.500 | -      | -      | 0.6890                | -      |

| Е         | 21.800      | 22.000 | 22.200 | 0.8583 | 0.8661                | 0.8740 |

| E1        | 19.800      | 20.000 | 20.200 | 0.7795 | 0.7874                | 0.7953 |

| E3        | -           | 17.500 | -      | -      | 0.6890                | -      |

| е         | -           | 0.500  | -      | -      | 0.0197                | -      |

| L         | 0.450       | 0.600  | 0.750  | 0.0177 | 0.0236                | 0.0295 |

| L1        | -           | 1.000  | -      | -      | 0.0394                | -      |

| k         | 0°          | 3.5°   | 7°     | 0°     | 3.5°                  | 7°     |

| CCC       | -           | -      | 0.080  | -      | -                     | 0.0031 |

# Table 91. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat packagemechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# 8 Part numbering

| Table 96. Ordering information scheme            |     |   |    |   |      |

|--------------------------------------------------|-----|---|----|---|------|

| Example: STM32 F                                 | 205 | R | ΞT | 6 | Vxxx |

|                                                  |     |   |    |   |      |

| Device family                                    |     |   |    |   |      |

| STM32 = ARM-based 32-bit microcontroller         |     |   |    |   |      |

| Product type                                     |     |   |    |   |      |

| F = general-purpose                              |     |   |    |   |      |

| Device subfamily                                 |     |   |    |   |      |

| 205 = STM32F20x, connectivity                    |     |   |    |   |      |

| 207= STM32F20x, connectivity, camera interface,  |     |   |    |   |      |

| Ethernet                                         |     |   |    |   |      |

| Pin count                                        |     |   |    |   |      |

| R = 64 pins or 66 pins <sup>(1)</sup>            |     |   |    |   |      |

| V = 100 pins                                     |     |   |    |   |      |

| Z = 144 pins                                     |     |   |    |   |      |

| I = 176 pins                                     |     |   |    |   |      |

|                                                  |     |   |    |   |      |

| Flash memory size                                |     |   |    |   |      |

| B = 128 Kbytes of Flash memory                   |     |   |    |   |      |

| C = 256 Kbytes of Flash memory                   |     |   |    |   |      |

| E = 512 Kbytes of Flash memory                   |     |   |    |   |      |

| F = 768 Kbytes of Flash memory                   |     |   |    |   |      |

| G = 1024 Kbytes of Flash memory                  |     |   |    |   |      |

| Package                                          |     |   |    |   |      |

| T = LQFP                                         |     |   |    |   |      |

| H = UFBGA                                        |     |   |    |   |      |

| Y = WLCSP                                        |     |   |    |   |      |

| Temperature range                                |     |   |    |   |      |

| 6 = Industrial temperature range, -40 to 85 °C.  |     |   |    |   |      |

| 7 = Industrial temperature range, –40 to 105 °C. |     |   |    |   |      |

| Software option                                  |     |   |    |   |      |

| Internal code or Blank                           |     |   |    |   |      |

| Options                                          |     |   |    |   |      |

xxx = programmed parts TR = tape and reel

1. The 66 pins is available on WLCSP package only.

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

| Table 97. Document revision history (continued) |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                     |  |  |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                                            | Revision                                                                                                                                                                                                                                                                                           | Changes                                                                                                                                                                                                                             |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Update I/Os in <i>Section : Features</i> .<br>Added WLCSP64+2 package. Added note 1 related to LQFP176 on                                                                                                                           |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | cover page.                                                                                                                                                                                                                         |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Added trademark for ART accelerator. Updated Section 3.2: Adaptive real-time memory accelerator (ART Accelerator™).                                                                                                                 |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Updated Figure 5: Multi-AHB matrix.                                                                                                                                                                                                 |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Added case of BOR inactivation using IRROFF on WLCSP devices in <i>Section 3.15: Power supply supervisor</i> .                                                                                                                      |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Reworked <i>Section 3.16: Voltage regulator</i> to clarify regulator off modes.<br>Renamed PDROFF, IRROFF in the whole document.                                                                                                    |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Added Section 3.19: VBAT operation.                                                                                                                                                                                                 |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Updated LIN and IrDA features for UART4/5 in Table 6: USART feature comparison.                                                                                                                                                     |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | <i>Table 8: STM32F20x pin and ball definitions</i> : Modified V <sub>DD_3</sub> pin, and added note related to the FSMC_NL pin; renamed BYPASS-REG REGOFF, and add IRROFF pin; renamed USART4/5 UART4/5. USART4 pins renamed UART4. |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Changed $V_{SS}$ SA to $V_{SS}$ , and $V_{DD}$ SA pin reserved for future use.                                                                                                                                                      |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Updated maximum HSE crystal frequency to 26 MHz.                                                                                                                                                                                    |  |  |

|                                                 | Section 6.2: Absolute maximum ratings: Updated V <sub>IN</sub> minimum and maximum values and note related to five-volt tolerant inputs in <i>Table 11</i> . Voltage characteristics. Updated I <sub>INJ(PIN)</sub> maximum values and related notes in <i>Table 12: Current characteristics</i> . |                                                                                                                                                                                                                                     |  |  |

| 25-Nov-2010                                     | 5                                                                                                                                                                                                                                                                                                  | Updated V <sub>DDA</sub> minimum value in <i>Table 14: General operating conditions</i> .                                                                                                                                           |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Added Note 2 and updated Maximum CPU frequency in <i>Table 15:</i><br><i>Limitations depending on the operating power supply range</i> , and added<br><i>Figure 21: Number of wait states versus fCPU and VDD range</i> .           |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Added brownout level 1, 2, and 3 thresholds in <i>Table 19: Embedded</i> reset and power control block characteristics.                                                                                                             |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Changed f <sub>OSC_IN</sub> maximum value in <i>Table 30: HSE 4-26 MHz oscillator characteristics</i> .                                                                                                                             |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Changed f <sub>PLL_IN</sub> maximum value in <i>Table 34: Main PLL characteristics</i> , and updated jitter parameters in <i>Table 35: PLLI2S (audio PLL) characteristics</i> .                                                     |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Section 6.3.16: I/O port characteristics: updated V <sub>IH</sub> and V <sub>IL</sub> in Table 48. I/O AC characteristics.                                                                                                          |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Added Note 1 below Table 47: Output voltage characteristics.                                                                                                                                                                        |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Updated R <sub>PD</sub> and R <sub>PU</sub> parameter description in <i>Table 57: USB OTG FS</i><br>DC electrical characteristics.                                                                                                  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Updated V <sub>REF+</sub> minimum value in <i>Table 66: ADC characteristics</i> .                                                                                                                                                   |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Updated Table 71: Embedded internal reference voltage.                                                                                                                                                                              |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Removed Ethernet and USB2 for 64-pin devices in <i>Table 101: Main applications versus package for STM32F2xxx microcontrollers</i> .                                                                                                |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                    | Added A.2: USB OTG full speed (FS) interface solutions, removed<br>"OTG FS connection with external PHY" figure, updated Figure 87,<br>Figure 88, and Figure 90 to add STULPI01B.                                                   |  |  |

Table 97. Document revision history (continued)