# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details |  |

|---------|--|

|---------|--|

| 2 0 0 0 0 0                |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 120MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 82                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 68K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205vbt6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 9 | Revis  | ion history                     | 169 |

|---|--------|---------------------------------|-----|

| 8 | Part r | numbering                       | 168 |

|   | 7.7    | Thermal characteristics         | 167 |

|   | 7.6    | UFBGA176+25 package information | 165 |

|   | 7.5    | LQFP176 package information     | 162 |

|   | 7.4    | LQFP144 package information     | 158 |

|                               |                         | Table                 | 2. STM3   | 82F205    | xx feat | ures a        | nd perip      | heral co                  | ounts        | 5 |                          |     |                |      |      |

|-------------------------------|-------------------------|-----------------------|-----------|-----------|---------|---------------|---------------|---------------------------|--------------|---|--------------------------|-----|----------------|------|------|

|                               | Peripherals             |                       | ST        | /132F205R | Rx      |               |               | STM32                     | F205V        | x |                          | S   | TM32F2         | 05Zx |      |

| Flash memory in               | n Kbytes                | 128                   | 256       | 512       | 768     | 1024          | 128           | 256                       | 512 768 1024 |   |                          | 256 | 512            | 768  | 1024 |

| SRAM in Kbytes                | System<br>(SRAM1+SRAM2) | 64<br>(48+16)         |           |           |         | 64<br>(48+16) | 96<br>(80+16) | 128<br>(112+16)           |              |   | 96 128<br>(80+16) (112+1 |     | 128<br>(112+16 | 3)   |      |

|                               | Backup                  |                       |           | 4         |         |               |               |                           | 4            |   |                          |     | 4              |      |      |

| FSMC memory of                | controller              | No Yes <sup>(1)</sup> |           |           |         |               |               |                           |              |   |                          |     |                |      |      |

| Ethernet                      | No                      |                       |           |           |         |               |               |                           |              |   |                          |     |                |      |      |

|                               | General-purpose         | 10                    |           |           |         |               |               |                           |              |   |                          |     |                |      |      |

|                               | Advanced-control        |                       |           |           |         |               |               | 2                         |              |   |                          |     |                |      |      |

| Timers                        | Basic                   |                       |           |           |         |               |               | 2                         |              |   |                          |     |                |      |      |

|                               | IWDG                    |                       | Yes       |           |         |               |               |                           |              |   |                          |     |                |      |      |

|                               | WWDG                    |                       | Yes       |           |         |               |               |                           |              |   |                          |     |                |      |      |

| RTC                           |                         |                       |           |           |         |               |               | Yes                       |              |   |                          |     |                |      |      |

| Random numbei                 | r generator             |                       | Yes       |           |         |               |               |                           |              |   |                          |     |                |      |      |

|                               | SPI/(I <sup>2</sup> S)  | 3/(2) <sup>(2)</sup>  |           |           |         |               |               |                           |              |   |                          |     |                |      |      |

|                               | l <sup>2</sup> C        | 3                     |           |           |         |               |               |                           |              |   |                          |     |                |      |      |

| Comm.<br>interfaces           | USART<br>UART           | 4 2                   |           |           |         |               |               |                           |              |   |                          |     |                |      |      |

| interfaces                    | USB OTG FS              | Yes                   |           |           |         |               |               |                           |              |   |                          |     |                |      |      |

|                               | USB OTG HS              | Yes                   |           |           |         |               |               |                           |              |   |                          |     |                |      |      |

|                               | CAN                     | 2                     |           |           |         |               |               |                           |              |   |                          |     |                |      |      |

| Camera interface              | e                       | No                    |           |           |         |               |               |                           |              |   |                          |     |                |      |      |

| GPIOs                         |                         |                       | 51 82 114 |           |         |               |               |                           |              |   |                          |     |                |      |      |

| SDIO                          |                         | Yes                   |           |           |         |               |               |                           |              |   |                          |     |                |      |      |

| 12-bit ADC                    |                         |                       | 3         |           |         |               |               |                           |              |   |                          |     |                |      |      |

| Number of chan                | 16 16 24                |                       |           |           |         |               |               |                           |              |   |                          |     |                |      |      |

| 12-bit DAC<br>Number of chanı | nels                    | Yes<br>2              |           |           |         |               |               |                           |              |   |                          |     |                |      |      |

| Maximum CPU f                 | frequency               |                       |           |           |         |               | 1             | I20 MHz                   |              |   |                          |     |                |      |      |

| Operating voltag              | e                       |                       |           |           |         |               | 1.8           | V to 3.6 V <sup>(3)</sup> |              |   |                          |     |                |      |      |

5

14/182

#### Table 2. STM32F205xx features and peripheral counts (continued)

| Peripherals            | ST                                                  | M32F205Rx               |  |                    | STM32F205Vx | STM32F205Zx |  |  |  |

|------------------------|-----------------------------------------------------|-------------------------|--|--------------------|-------------|-------------|--|--|--|

| Operating temperatures | Ambient temperatures: -40 to +85 °C /-40 to +105 °C |                         |  |                    |             |             |  |  |  |

|                        | Junction temperature: -40 to + 125 °C               |                         |  |                    |             |             |  |  |  |

| Package                | LQFP64                                              | LQFP64<br>WLCSP64<br>+2 |  | FP64<br>CSP6<br>+2 | LQFP100     | LQFP144     |  |  |  |

For the LQFP100 package, only FSMC Bank1 or Bank2 are available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select. Bank2 can only support a 16- or 8-bit NAND Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available in this package.

2. The SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I2S audio mode.

On devices in WLCSP64+2 package, if IRROFF is set to V<sub>DD</sub>, the supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor (see Section 3.16).

|                   | Peripherals             |                 | STM3                              | 2F207Vx |  |  |  | F207Zx |    | STM32F207Ix |     |     |      |  |

|-------------------|-------------------------|-----------------|-----------------------------------|---------|--|--|--|--------|----|-------------|-----|-----|------|--|

| Flash memory in I | Kbytes                  | 256             | 256 512 768 1024 256 512 768 1024 |         |  |  |  |        |    | 256         | 512 | 768 | 1024 |  |

| SRAM in Kbytes    | System<br>(SRAM1+SRAM2) | 128<br>(112+16) |                                   |         |  |  |  |        |    |             |     |     |      |  |

|                   | Backup                  |                 | 4                                 |         |  |  |  |        |    |             |     |     |      |  |

| FSMC memory co    | ontroller               |                 | Yes <sup>(1)</sup>                |         |  |  |  |        |    |             |     |     |      |  |

| Ethernet          |                         |                 |                                   |         |  |  |  | Ye     | es |             |     |     |      |  |

|                   | General-purpose         | 10              |                                   |         |  |  |  |        |    |             |     |     |      |  |

|                   | Advanced-control        | 2               |                                   |         |  |  |  |        |    |             |     |     |      |  |

| Timers            | Basic                   | 2               |                                   |         |  |  |  |        |    |             |     |     |      |  |

|                   | IWDG                    | Yes             |                                   |         |  |  |  |        |    |             |     |     |      |  |

|                   | WWDG                    | Yes             |                                   |         |  |  |  |        |    |             |     |     |      |  |

| RTC               | 1                       | Yes             |                                   |         |  |  |  |        |    |             |     |     |      |  |

| Random number     | generator               | Yes             |                                   |         |  |  |  |        |    |             |     |     |      |  |

#### Table 3. STM32F207xx features and peripheral counts

# 3.11 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 23 edge-detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 140 GPIOs can be connected to the 16 external interrupt lines.

# 3.12 Clocks and startup

On reset the 16 MHz internal RC oscillator is selected as the default CPU clock. The 16 MHz internal RC oscillator is factory-trimmed to offer 1% accuracy. The application can then select as system clock either the RC oscillator or an external 4-26 MHz clock source. This clock is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator and a software interrupt is generated (if enabled). Similarly, full interrupt management of the PLL clock entry is available when necessary (for example if an indirectly used external oscillator fails).

The advanced clock controller clocks the core and all peripherals using a single crystal or oscillator. In particular, the ethernet and USB OTG FS peripherals can be clocked by the system clock.

Several prescalers and PLLs allow the configuration of the three AHB buses, the highspeed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the three AHB buses is 120 MHz and the maximum frequency the high-speed APB domains is 60 MHz. The maximum allowed frequency of the low-speed APB domain is 30 MHz.

The devices embed a dedicate PLL (PLLI2S) which allow to achieve audio class performance. In this case, the  $I^2S$  master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

## 3.13 Boot modes

At startup, boot pins are used to select one out of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART1 (PA9/PA10), USART3 (PC10/PC11 or PB10/PB11), CAN2 (PB5/PB13), USB OTG FS in Device mode (PA11/PA12) through DFU (device firmware upgrade).

# 3.14 Power supply schemes

V<sub>DD</sub> = 1.8 to 3.6 V: external power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins. On devices in WLCSP64+2 package, if IRROFF is set to V<sub>DD</sub>, the supply voltage can drop to 1.7 V when the device operates

# 3.30 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S application. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an  $I^2S$  sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 kHz to 192 kHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I2S flow with an external PLL (or Codec output).

# 3.31 Digital camera interface (DCMI)

The camera interface is not available in STM32F205xx devices.

STM32F207xx products embed a camera interface that can connect with camera modules and CMOS sensors through an 8-bit to 14-bit parallel interface, to receive video data. The camera interface can sustain up to 27 Mbyte/s at 27 MHz or 48 Mbyte/s at 48 MHz. It features:

- Programmable polarity for the input pixel clock and synchronization signals

- Parallel data communication can be 8-, 10-, 12- or 14-bit

- Supports 8-bit progressive video monochrome or raw Bayer format, YCbCr 4:2:2 progressive video, RGB 565 progressive video or compressed data (like JPEG)

- Supports continuous mode or snapshot (a single frame) mode

- Capability to automatically crop the image

## 3.32 True random number generator (RNG)

All STM32F2xxx products embed a true RNG that delivers 32-bit random numbers produced by an integrated analog circuit.

# 3.33 GPIOs (general-purpose inputs/outputs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O alternate function configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

To provide fast I/O handling, the GPIOs are on the fast AHB1 bus with a clock up to 120 MHz that leads to a maximum I/O toggling speed of 60 MHz.

|   | 1                  | 2             | 3            | 4      | 5   | 6     | 7    | 8    | 9    | 10     | 11   | 12   | 13     | 14   | 15   |

|---|--------------------|---------------|--------------|--------|-----|-------|------|------|------|--------|------|------|--------|------|------|

| А | PE3                | PE2           | PE1          | PE0    | PB8 | PB5   | PG14 | PG13 | PB4  | PB3    | PD7  | PC12 | PA15   | PA14 | PA13 |

| в | PE4                | PE5           | PE6          | PB9    | PB7 | PB6   | PG15 | PG12 | PG11 | PG10   | PD6  | PD0  | PC11   | PC10 | PA12 |

| С | VBAT               | PI7           | PI6          | PI5    | VDD | RFU   | VDD  | VDD  | VDD  | PG9    | PD5  | PD1  | PI3    | Pl2  | PA11 |

| D | PC13-<br>TAMP1     | PI8-<br>TAMP2 | PI9          | PI4    | VSS | BOOT0 | VSS  | VSS  | VSS  | PD4    | PD3  | PD2  | PH15   | PI1  | PA10 |

| Е | PC14-<br>OSC32_IN  | PF0           | PI10         | PI11   |     |       |      |      |      |        |      | PH13 | PH14   | P10  | PA9  |

| F | PC15-<br>OSC32_OUT | VSS           | VDD          | PH2    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | VSS  | VCAP_2 | PC9  | PA8  |

| G | PH0-<br>OSC_IN     | VSS           | VDD          | PH3    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | VSS  | VDD    | PC8  | PC7  |

| н | PH1-<br>OSC_OUT    | PF2           | PF1          | PH4    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | VSS  | VDD    | PG8  | PC6  |

| J | NRST               | PF3           | PF4          | PH5    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | VDD  | VDD    | PG7  | PG6  |

| к | PF7                | PF6           | PF5          | VDD    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | PH12 | PG5    | PG4  | PG3  |

| L | PF10               | PF9           | PF8          | REGOFF |     |       |      |      |      |        |      | PH11 | PH10   | PD15 | PG2  |

| м | VSSA               | PC0           | PC1          | PC2    | PC3 | PB2   | PG1  | VSS  | VSS  | VCAP_1 | PH6  | PH8  | PH9    | PD14 | PD13 |

| N | VREF-              | PA1           | PA0-<br>WKUP | PA4    | PC4 | PF13  | PG0  | VDD  | VDD  | VDD    | PE13 | PH7  | PD12   | PD11 | PD10 |

| Ρ | VREF+              | PA2           | PA6          | PA5    | PC5 | PF12  | PF15 | PE8  | PE9  | PE11   | PE14 | PB12 | PB13   | PD9  | PD8  |

| R | VDDA               | PA3           | PA7          | PB1    | PB0 | PF11  | PF14 | PE7  | PE10 | PE12   | PE15 | PB10 | PB11   | PB14 | PB15 |

Figure 15. STM32F20x UFBGA176 ballout

1. RFU means "reserved for future use". This pin can be tied to  $V_{\text{DD}}, V_{\text{SS}}$  or left unconnected.

2. The above figure shows the package top view.

|  | Table 7. Legend/abbreviations used in the p | inout table |

|--|---------------------------------------------|-------------|

|--|---------------------------------------------|-------------|

| Name                   | Abbreviation                                                     | Definition                                                                                         |  |  |  |  |  |  |  |  |

|------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Pin name               |                                                                  | specified in brackets below the pin name, the pin function during and after as the actual pin name |  |  |  |  |  |  |  |  |

|                        | S Supply pin                                                     |                                                                                                    |  |  |  |  |  |  |  |  |

| Pin type               | I Input only pin                                                 |                                                                                                    |  |  |  |  |  |  |  |  |

|                        | I/O                                                              | I/O Input/ output pin                                                                              |  |  |  |  |  |  |  |  |

|                        | FT 5 V tolerant I/O                                              |                                                                                                    |  |  |  |  |  |  |  |  |

| I/O structure          | TTa                                                              | 3.3 V tolerant I/O                                                                                 |  |  |  |  |  |  |  |  |

| NO structure           | B Dedicated BOOT0 pin                                            |                                                                                                    |  |  |  |  |  |  |  |  |

|                        | RST Bidirectional reset pin with embedded weak pull-up resistor  |                                                                                                    |  |  |  |  |  |  |  |  |

| Notes                  | Unless otherwise                                                 | specified by a note, all I/Os are set as floating inputs during and after reset                    |  |  |  |  |  |  |  |  |

| Alternate<br>functions | Functions selected                                               | Functions selected through GPIOx_AFR registers                                                     |  |  |  |  |  |  |  |  |

| Additional functions   | Functions directly selected/enabled through peripheral registers |                                                                                                    |  |  |  |  |  |  |  |  |

|        |           | Pi      | ns      |         |          |                                                      |          |               |      |                                                                                                               |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|---------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions                                                                                           | Additional<br>functions |

| 22     | H5        | 31      | 42      | 52      | P3       | PA6                                                  | I/O      | FT            | (4)  | SPI1_MISO, TIM8_BKIN,<br>TIM13_CH1, DCMI_PIXCLK,<br>TIM3_CH1, TIM1_BKIN,<br>EVENTOUT                          | ADC12_IN6               |

| 23     | J7        | 32      | 43      | 53      | R3       | PA7                                                  | I/O      | FT            | (4)  | SPI1_MOSI, TIM8_CH1N,<br>TIM14_CH1, TIM3_CH2,<br>ETH_MII_RX_DV,<br>TIM1_CH1N,<br>ETH_RMII_CRS_DV,<br>EVENTOUT | ADC12_IN7               |

| 24     | H4        | 33      | 44      | 54      | N5       | PC4                                                  | I/O      | FT            | (4)  | ETH_RMII_RXD0,<br>ETH_MII_RXD0,<br>EVENTOUT                                                                   | ADC12_IN14              |

| 25     | G3        | 34      | 45      | 55      | P5       | PC5                                                  | I/O      | FT            | (4)  | ETH_RMII_RXD1,<br>ETH_MII_RXD1,<br>EVENTOUT                                                                   | ADC12_IN15              |

| 26     | J6        | 35      | 46      | 56      | R5       | PB0                                                  | I/O      | FT            | (4)  | TIM3_CH3, TIM8_CH2N,<br>OTG_HS_ULPI_D1,<br>ETH_MII_RXD2,<br>TIM1_CH2N, EVENTOUT                               | ADC12_IN8               |

| 27     | J5        | 36      | 47      | 57      | R4       | PB1                                                  | I/O      | FT            | (4)  | TIM3_CH4, TIM8_CH3N,<br>OTG_HS_ULPI_D2,<br>ETH_MII_RXD3,<br>TIM1_CH3N, EVENTOUT                               | ADC12_IN9               |

| 28     | J4        | 37      | 48      | 58      | M6       | PB2/BOOT1 (PB2)                                      | I/O      | FT            | -    | EVENTOUT                                                                                                      | -                       |

| -      | -         | -       | 49      | 59      | R6       | PF11                                                 | I/O      | FT            | -    | DCMI_D12, EVENTOUT                                                                                            |                         |

| -      | -         | -       | 50      | 60      | P6       | PF12                                                 | I/O      | FT            | -    | FSMC_A6, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 51      | 61      | M8       | V <sub>SS</sub>                                      | S        |               | -    | -                                                                                                             | -                       |

| -      | -         | -       | 52      | 62      | N8       | V <sub>DD</sub>                                      | S        |               | -    | -                                                                                                             | -                       |

| -      | -         | -       | 53      | 63      | N6       | PF13                                                 | I/O      | FT            | -    | FSMC_A7, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 54      | 64      | R7       | PF14                                                 | I/O      | FT            | -    | FSMC_A8, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 55      | 65      | P7       | PF15                                                 | I/O      | FT            | -    | FSMC_A9, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 56      | 66      | N7       | PG0                                                  | I/O      | FT            | -    | FSMC_A10, EVENTOUT                                                                                            | -                       |

| -      | -         | -       | 57      | 67      | M7       | PG1                                                  | I/O      | FT            | -    | FSMC_A11, EVENTOUT                                                                                            | -                       |

|        |           | Pi      | ns      |         |          |                                                      |          |               |      |                                   |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|-----------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions               | Additional<br>functions |

| -      | -         | 98      | 142     | 170     | A3       | PE1                                                  | I/O      | FT            | -    | FSMC_NBL1, DCMI_D3,<br>EVENTOUT   | -                       |

| -      | -         | -       | -       | -       | D5       | V <sub>SS</sub>                                      | S        | -             | -    | -                                 | -                       |

| 63     | D8        | I       | -       | -       | I        | V <sub>SS</sub>                                      | S        | -             | I    | -                                 | -                       |

| -      | -         | 99      | 143     | 171     | C6       | RFU                                                  | -        | -             | (7)  | -                                 | -                       |

| 64     | D9        | 100     | 144     | 172     | C5       | V <sub>DD</sub>                                      | S        | -             | -    | -                                 | -                       |

| -      | -         | -       | -       | 173     | D4       | Pl4                                                  | I/O      | FT            | -    | TIM8_BKIN, DCMI_D5,<br>EVENTOUT   | -                       |

| -      | -         | -       | I       | 174     | C4       | PI5                                                  | I/O      | FT            | I    | TIM8_CH1, DCMI_VSYNC,<br>EVENTOUT | -                       |

| -      | -         | -       | -       | 175     | C3       | Pl6                                                  | I/O      | FT            | -    | TIM8_CH2, DCMI_D6,<br>EVENTOUT    | -                       |

| -      | -         | -       | -       | 176     | C2       | PI7                                                  | I/O      | FT            | -    | TIM8_CH3, DCMI_D7,<br>EVENTOUT    | -                       |

| -      | C8        | -       | -       | -       | -        | IRROFF                                               | I/O      | -             | -    | -                                 | -                       |

Table 8. STM32F20x pin and ball definitions (continued)

1. Function availability depends on the chosen device.

PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these I/Os must not be used as a current source (e.g. to drive an LED).

Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F20x and STM32F21x reference manual, available from the STMicroelectronics website: www.st.com.

4. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

5. If the device is delivered in an UFBGA176 package and if the REGOFF pin is set to V<sub>DD</sub> (Regulator OFF), then PA0 is used as an internal Reset (active low).

6. FSMC\_NL pin is also named FSMC\_NADV on memory devices.

7. RFU means "reserved for future use". This pin can be tied to  $V_{DD}$ ,  $V_{SS}$  or left unconnected.

#### Table 9. FSMC pin definition

| Pins  |    | LQFP100        |               |             |         |

|-------|----|----------------|---------------|-------------|---------|

| FIIIS | CF | NOR/PSRAM/SRAM | NOR/PSRAM Mux | NAND 16 bit | LQFF100 |

| PE2   | -  | A23            | A23           | -           | Yes     |

| PE3   | -  | A19            | A19           | -           | Yes     |

| PE4   | -  | A20            | A20           | -           | Yes     |

|       |       |                | n definition (continu | ed)         |         |

|-------|-------|----------------|-----------------------|-------------|---------|

| Pins  |       | F              | SMC                   |             | LQFP100 |

| 1 113 | CF    | NOR/PSRAM/SRAM | NOR/PSRAM Mux         | NAND 16 bit | Lairio  |

| PE5   | -     | A21            | A21                   | -           | Yes     |

| PE6   | -     | A22            | A22                   | -           | Yes     |

| PF0   | A0    | A0             | -                     | -           | -       |

| PF1   | A1    | A1             | -                     | -           | -       |

| PF2   | A2    | A2             | -                     | -           | -       |

| PF3   | A3    | A3             | -                     | -           | -       |

| PF4   | A4    | A4             | -                     | -           | -       |

| PF5   | A5    | A5             | -                     | -           | -       |

| PF6   | NIORD | -              | -                     | -           | -       |

| PF7   | NREG  | -              | -                     | -           | -       |

| PF8   | NIOWR | -              | -                     | -           | -       |

| PF9   | CD    | -              | -                     | -           | -       |

| PF10  | INTR  | -              | -                     | -           | -       |

| PF12  | A6    | A6             | -                     | -           | -       |

| PF13  | A7    | A7             | -                     | -           | -       |

| PF14  | A8    | A8             | -                     | -           | -       |

| PF15  | A9    | A9             | -                     | -           | -       |

| PG0   | A10   | A10            | -                     | -           | -       |

| PG1   | -     | A11            | -                     | -           | -       |

| PE7   | D4    | D4             | DA4                   | D4          | Yes     |

| PE8   | D5    | D5             | DA5                   | D5          | Yes     |

| PE9   | D6    | D6             | DA6                   | D6          | Yes     |

| PE10  | D7    | D7             | DA7                   | D7          | Yes     |

| PE11  | D8    | D8             | DA8                   | D8          | Yes     |

| PE12  | D9    | D9             | DA9                   | D9          | Yes     |

| PE13  | D10   | D10            | DA10                  | D10         | Yes     |

| PE14  | D11   | D11            | DA11                  | D11         | Yes     |

| PE15  | D12   | D12            | DA12                  | D12         | Yes     |

| PD8   | D13   | D13            | DA13                  | D13         | Yes     |

| PD9   | D14   | D14            | DA14                  | D14         | Yes     |

| PD10  | D15   | D15            | DA15                  | D15         | Yes     |

| PD11  | -     | A16            | A16                   | CLE         | Yes     |

| PD12  | -     | A17            | A17                   | ALE         | Yes     |

|       | 1     |                |                       |             | 1       |

Table 9. FSMC pin definition (continued)

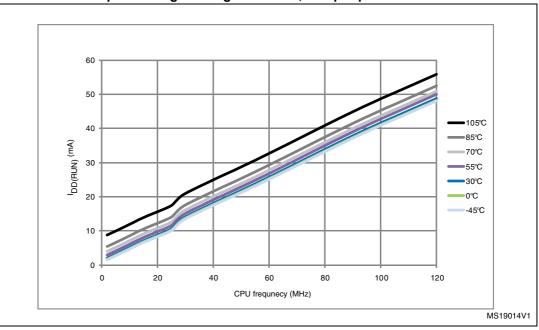

Figure 23. Typical current consumption vs. temperature, Run mode, code with data processing running from RAM, and peripherals ON

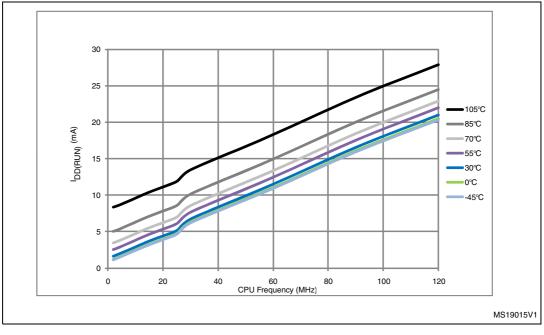

Figure 24. Typical current consumption vs. temperature, Run mode, code with data processing running from RAM, and peripherals OFF

|                        |                                                                                  |                                                                                                                                                  | Тур                       |                           | Max                       |                            |      |  |

|------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|----------------------------|------|--|

| Symbol                 | Parameter                                                                        | Conditions                                                                                                                                       | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |  |

| I <sub>DD_STOP</sub> - | Supply current<br>in Stop mode                                                   | Flash in Stop mode, low-speed and high-speed<br>internal RC oscillators and high-speed oscillator<br>OFF (no independent watchdog)               | 0.55                      | 1.2                       | 11.00                     | 20.00                      |      |  |

|                        | with main<br>regulator in<br>Run mode                                            | Flash in Deep power down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.50                      | 1.2                       | 11.00                     | 20.00                      |      |  |

|                        | Supply current<br>in Stop mode<br>with main<br>regulator in<br>Low-power<br>mode | Flash in Stop mode, low-speed and high-speed<br>internal RC oscillators and high-speed oscillator<br>OFF (no independent watchdog)               | 0.35                      | 1.1                       | 8.00                      | 15.00                      | mA   |  |

|                        |                                                                                  | Flash in Deep power down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.30                      | 1.1                       | 8.00                      | 15.00                      |      |  |

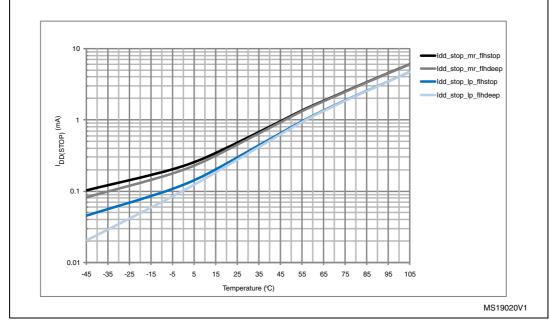

Table 23. Typical and maximum current consumptions in Stop mode

Figure 29. Typical current consumption vs. temperature in Stop mode

All typical and maximum values from table 18 and figure 26 will be reduced over time by up to 50% as part

of ST continuous improvement of test procedures. New versions of the datasheet will be released to reflect

these changes

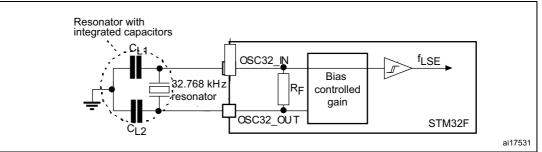

| Symbol                              | Parameter                   | Conditions                    | Min | Тур  | Max | Unit |  |  |  |  |

|-------------------------------------|-----------------------------|-------------------------------|-----|------|-----|------|--|--|--|--|

| R <sub>F</sub>                      | Feedback resistor           | -                             | -   | 18.4 | -   | MΩ   |  |  |  |  |

| I <sub>DD</sub>                     | LSE current consumption     | -                             | -   | -    | 1   | μA   |  |  |  |  |

| 9 <sub>m</sub>                      | Oscillator Transconductance | -                             | 2.8 | -    | -   | µA/V |  |  |  |  |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | startup time                | V <sub>DD</sub> is stabilized | -   | 2    | -   | S    |  |  |  |  |

Table 31. LSE oscillator characteristics ( $f_{LSE} = 32.768 \text{ kHz}$ )<sup>(1)</sup>

1. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

Note: For information on electing the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 33. Typical application with a 32.768 kHz crystal

## 6.3.9 Internal clock source characteristics

The parameters given in *Table 32* and *Table 33* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

#### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                             | Conditions                           | Min | Тур | Max | Unit |

|-------------------------------------|---------------------------------------|--------------------------------------|-----|-----|-----|------|

| f <sub>HSI</sub>                    | Frequency                             | -                                    | -   | 16  | -   | MHz  |

| ACC <sub>HSI</sub>                  | HSI user-trimming step <sup>(2)</sup> | -                                    | -   | -   | 1   | %    |

|                                     |                                       | $T_A = -40$ to 105 °C <sup>(3)</sup> | - 8 | -   | 4.5 | %    |

|                                     | Accuracy of the<br>HSI oscillator     | $T_A = -10$ to 85 °C <sup>(3)</sup>  | - 4 | -   | 4   | %    |

|                                     |                                       | $T_A = 25 \ ^{\circ}C^{(4)}$         | – 1 | -   | 1   | %    |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time           | -                                    | -   | 2.2 | 4.0 | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power consumption      | -                                    | -   | 60  | 80  | μA   |

Table 32. HSI oscillator characteristics <sup>(1)</sup>

1.  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design, not tested in production.

- 3. Guaranteed by characterization results.

- 4. Factory calibrated, parts not soldered.

| Symbol                            | Parameter                                                                     | Conditions                                                 | Min                    | Max | Unit |  |

|-----------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------|------------------------|-----|------|--|

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | CMOS ports<br>I <sub>IO</sub> = +8 mA                      | -                      | 0.4 | v    |  |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time | $1_{O} - 70 \text{ mA}$<br>2.7 V < V <sub>DD</sub> < 3.6 V | V <sub>DD</sub> -0.4   | -   | V    |  |

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | TTL ports<br>I <sub>IO</sub> =+ 8mA                        | -                      | 0.4 | V    |  |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time | $2.7 V < V_{DD} < 3.6 V$                                   | 2.4                    | -   | v    |  |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | l <sub>IO</sub> = +20 mA                                   | -                      | 1.3 | V    |  |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2.7 V < V <sub>DD</sub> < 3.6 V                            | V <sub>DD</sub> -1.3   | -   | v    |  |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> = +6 mA                                    | -                      | 0.4 | V    |  |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2 V < V <sub>DD</sub> < 2.7 V                              | V <sub>DD</sub> -0.4 - |     | v    |  |

PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these I/Os must not be used as a current source (e.g. to drive an LED).

- 2. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 12* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

- 3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 12 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

- 4. Guaranteed by characterization results, not tested in production.

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 39* and *Table 48*, respectively.

Unless otherwise specified, the parameters given in *Table 48* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                                  | Min | Тур | Max | Unit |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

|                                               | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(2)</sup>                                                | $C_L$ = 50 pF, $V_{DD}$ > 2.70 V                            | -   | -   | 4   |      |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 2   | MHz  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 8   |      |

| 00                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 4   |      |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.8 V to<br>3.6 V | -   | -   | 100 | ns   |

| Table 4 | 48. | I/O | AC | characteristics <sup>(1)</sup> |

|---------|-----|-----|----|--------------------------------|

|---------|-----|-----|----|--------------------------------|

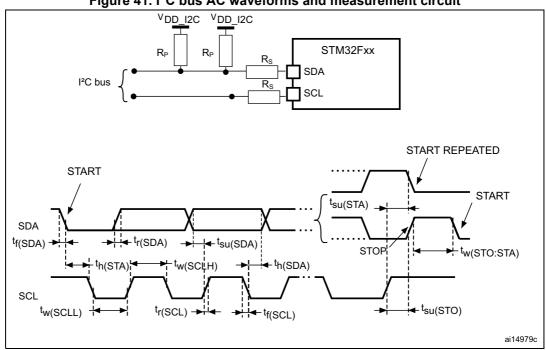

Figure 41. I<sup>2</sup>C bus AC waveforms and measurement circuit

- 1.  $R_S$ = series protection resistor.

- 2. R<sub>P</sub> = external pull-up resistor.

- 3.  $V_{DD_{12C}}$  is the I<sup>2</sup>C bus power supply.

| f (kU-)                | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x8019                  |

| 300                    | 0x8021                  |

| 200                    | 0x8032                  |

| 100                    | 0x0096                  |

| 50                     | 0x012C                  |

| 20                     | 0x02EE                  |

## Table 53. SCL frequency (f<sub>PCLK1</sub>= 30 MHz., V<sub>DD</sub> = 3.3 V)<sup>(1)(2)</sup>

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  = I<sup>2</sup>C speed,

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

#### **USB OTG FS characteristics**

The USB OTG interface is USB-IF certified (Full-Speed). This interface is present in both the USB OTG HS and USB OTG FS controllers.

| Symbol Parameter                    |                                     | Мах | Unit |  |  |  |

|-------------------------------------|-------------------------------------|-----|------|--|--|--|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG FS transceiver startup time | 1   | μs   |  |  |  |

Table 56. USB OTG FS startup time

1. Guaranteed by design, not tested in production.

| Sym             | bol                                  | Parameter                                                 | Conditions                                                       | Min. <sup>(1)</sup> | Тур. | Max. <sup>(1)</sup> | Unit |

|-----------------|--------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------|---------------------|------|---------------------|------|

|                 | $V_{DD}$                             | USB OTG FS operating<br>voltage                           |                                                                  | 3.0 <sup>(2)</sup>  | -    | 3.6                 | V    |

| Input           | V <sub>DI</sub> <sup>(3)</sup>       | Differential input sensitivity                            | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)                                 | 0.2                 | -    | -                   |      |

| levels          | V <sub>CM</sub> <sup>(3)</sup>       | Differential common mode range                            | Includes V <sub>DI</sub> range                                   | 0.8                 | -    | 2.5                 | V    |

|                 | $V_{SE}^{(3)}$                       | Single ended receiver threshold                           |                                                                  | 1.3                 | -    | 2.0                 |      |

| Output          | V <sub>OL</sub>                      | Static output level low                                   | $\rm R_L$ of 1.5 k\Omega to 3.6 $\rm V^{(4)}$                    | -                   | -    | 0.3                 | V    |

| levels          | V <sub>OH</sub>                      | Static output level high                                  | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}{}^{(4)}$ | 2.8                 | -    | 3.6                 | v    |

| R <sub>P</sub>  |                                      | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | V <sub>IN</sub> = V <sub>DD</sub>                                | 17                  | 21   | 24                  |      |

|                 | D                                    | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | VIN - VDD                                                        | 0.65                | 1.1  | 2.0                 | kΩ   |

|                 | PA12, PB15 (USB_FS_DP,<br>USB_HS_DP) |                                                           | V <sub>IN</sub> = V <sub>SS</sub>                                | 1.5                 | 1.8  | 2.1                 |      |

| R <sub>PU</sub> |                                      | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>SS</sub>                                | 0.25                | 0.37 | 0.55                |      |

#### Table 57. USB OTG FS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. The STM32F205xx and STM32F207xx USB OTG FS functionality is ensured down to 2.7 V but not the full USB OTG FS electrical characteristics which are degraded in the 2.7-to-3.0 V  $V_{DD}$  voltage range.

3. Guaranteed by design, not tested in production.

4. R<sub>L</sub> is the load connected on the USB OTG FS drivers

## 6.3.20 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 66* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 14*.

| Symbol                             | Parameter                                       | Conditions                                          | Min                                                         | Тур      | Max               | Unit               |

|------------------------------------|-------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------|----------|-------------------|--------------------|

| V <sub>DDA</sub>                   | Power supply                                    | -                                                   | 1.8 <sup>(1)</sup>                                          | -        | 3.6               | V                  |

| V <sub>REF+</sub>                  | Positive reference voltage                      | -                                                   | 1.8 <sup>(1)(2)</sup>                                       | -        | V <sub>DDA</sub>  | V                  |

| £                                  | ADC clock frequency                             | $V_{DDA}$ = 1.8 <sup>(1)</sup> to 2.4 V             | 0.6                                                         | -        | 15                | MHz                |

| f <sub>ADC</sub>                   | ADC Clock frequency                             | V <sub>DDA</sub> = 2.4 to 3.6 V                     | 0.6                                                         | -        | 30                | MHz                |

| f <sub>TRIG</sub> <sup>(3)</sup>   | External trigger frequency                      | f <sub>ADC</sub> = 30 MHz with<br>12-bit resolution | -                                                           | -        | 1764              | kHz                |

|                                    |                                                 | -                                                   | -                                                           | -        | 17                | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range <sup>(4)</sup>         | -                                                   | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -        | V <sub>REF+</sub> | V                  |

| R <sub>AIN</sub> <sup>(3)</sup>    | External input impedance                        | See <i>Equation 1</i> for details                   | -                                                           | -        | 50                | kΩ                 |

| R <sub>ADC</sub> <sup>(3)(5)</sup> | Sampling switch resistance                      | -                                                   | 1.5                                                         | -        | 6                 | kΩ                 |

| C <sub>ADC</sub> <sup>(3)</sup>    | Internal sample and hold capacitor              | -                                                   | -                                                           | 4        | -                 | pF                 |

| t <sub>lat</sub> (3)               | Injection trigger conversion latency            | f <sub>ADC</sub> = 30 MHz                           | -                                                           | -        | 0.100             | μs                 |

| 'lat` ´                            |                                                 | -                                                   | -                                                           | -        | 3 <sup>(6)</sup>  | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (3)              | Regular trigger conversion latency              | f <sub>ADC</sub> = 30 MHz                           | -                                                           | -        | 0.067             | μs                 |

| 4atr` ´                            | Regular ingger conversion latency               | -                                                   | -                                                           | -        | 2 <sup>(6)</sup>  | 1/f <sub>ADC</sub> |

| t <sub>S</sub> <sup>(3)</sup>      | Sampling time                                   | f <sub>ADC</sub> = 30 MHz                           | 0.100                                                       | -        | 16                | μs                 |

| LS(*)                              | Sampling une                                    | -                                                   | 3                                                           | -        | 480               | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(3)</sup>   | Power-up time                                   | -                                                   | -                                                           | 2        | 3                 | μs                 |

| t <sub>CONV</sub> <sup>(3)</sup>   | Total conversion time (including sampling time) | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution      | 0.5                                                         | -        | 16.40             | μs                 |

|                                    |                                                 | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution      | 0.43                                                        | -        | 16.34             | μs                 |

|                                    |                                                 | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution       | 0.37                                                        | -        | 16.27             | μs                 |

|                                    |                                                 | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution       | 0.3                                                         | -        | 16.20             | μs                 |

|                                    |                                                 | 9 to 492 (t <sub>S</sub> for samplir approximation) | ng +n-bit resolutior                                        | for succ | cessive           | 1/f <sub>ADC</sub> |

| Table | 66. / | ADC | characteristics |

|-------|-------|-----|-----------------|

| Table |       |     | Characteristics |

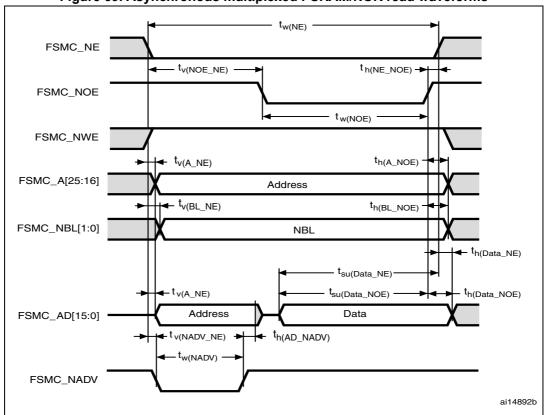

Figure 59. Asynchronous multiplexed PSRAM/NOR read waveforms

Table 74. Asynchronous multiplexed PSRAM/NOR read timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                                                | Min                     | Max                     | Unit |

|---------------------------|----------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                                         | 3T <sub>HCLK</sub> -1   | 3T <sub>HCLK</sub> +1   | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low                             | 2T <sub>HCLK</sub>      | 2T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                                        | T <sub>HCLK</sub> -1    | T <sub>HCLK</sub> +1    | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time                  | 0                       | -                       | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                             | -                       | 2                       | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                            | 1                       | 2.5                     | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                                       | T <sub>HCLK</sub> – 1.5 | T <sub>HCLK</sub>       | ns   |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD(adress) valid hold time after<br>FSMC_NADV high) | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high                    | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL time after FSMC_NOE high                         | 0                       | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                            | -                       | 1                       | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time                         | T <sub>HCLK</sub> + 2   | -                       | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOE high setup time                         | T <sub>HCLK</sub> + 3   | -                       | ns   |

| Symbol                     | Parameter                                    | Min | Max | Unit |

|----------------------------|----------------------------------------------|-----|-----|------|

| t <sub>d(CLKL-NWEL)</sub>  | FSMC_CLK low to FSMC_NWE low                 | -   | 1   | ns   |

| t <sub>d(CLKL-NWEH)</sub>  | FSMC_CLK low to FSMC_NWE high                | 0   | -   | ns   |

| t <sub>d(CLKL-ADIV)</sub>  | FSMC_CLK low to FSMC_AD[15:0] invalid        | 0   | -   | ns   |

| t <sub>d(CLKL-DATA</sub> ) | FSMC_A/D[15:0] valid data after FSMC_CLK low | -   | 2   | ns   |

| t <sub>d(CLKL-NBLH)</sub>  | FSMC_CLK low to FSMC_NBL high                | 0.5 | -   | ns   |

Table 77. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

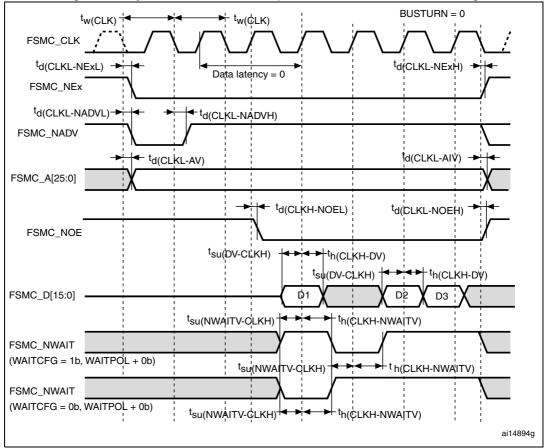

### Figure 63. Synchronous non-multiplexed NOR/PSRAM read timings

| able 78. Synchronous non-multiplexed NOR/PSRAM read timings <sup>(1)(2)</sup> | ) |

|-------------------------------------------------------------------------------|---|

| able 10. Synchronous non-multiplexed NOIVI SIXAM read unnings                 |   |

| Symbol                     | Parameter                             | Min                | Max | Unit |

|----------------------------|---------------------------------------|--------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                       | 2T <sub>HCLK</sub> | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x=02)   | -                  | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x= 02) | 1                  | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low         | -                  | 2.5 | ns   |

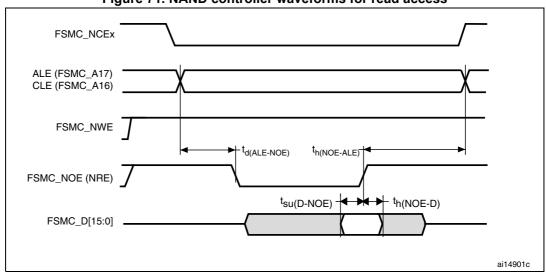

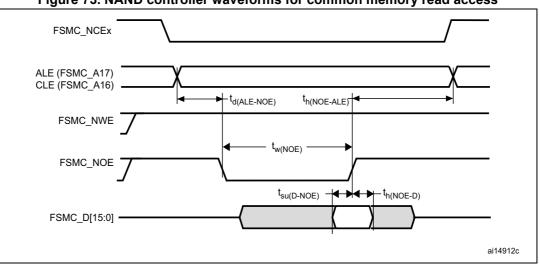

Figure 71. NAND controller waveforms for read access

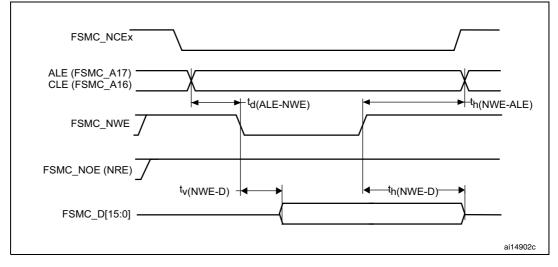

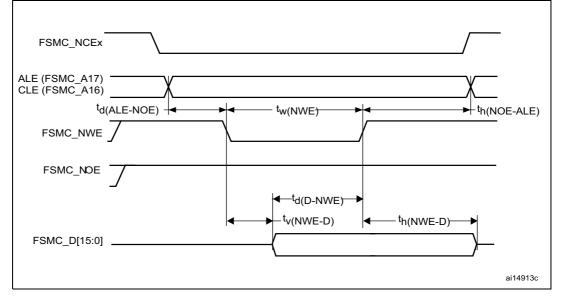

Figure 72. NAND controller waveforms for write access

Figure 73. NAND controller waveforms for common memory read access

Figure 74. NAND controller waveforms for common memory write access

Table 82. Switching characteristics for NAND Flash read cycles<sup>(1)(2)</sup>

| Symbol                  | Parameter                                    | Min                    | Мах                    | Unit |

|-------------------------|----------------------------------------------|------------------------|------------------------|------|

| t <sub>w(N0E)</sub>     | FSMC_NOE low width                           | 4T <sub>HCLK</sub> - 1 | 4T <sub>HCLK</sub> + 2 | ns   |

| t <sub>su(D-NOE)</sub>  | FSMC_D[15-0] valid data before FSMC_NOE high | 9                      | -                      | ns   |

| t <sub>h(NOE-D</sub> )  | FSMC_D[15-0] valid data after FSMC_NOE high  | 3                      | -                      | ns   |

| t <sub>d(ALE-NOE)</sub> | FSMC_ALE valid before FSMC_NOE low           | -                      | 3T <sub>HCLK</sub>     | ns   |

| t <sub>h(NOE-ALE)</sub> | FSMC_NWE high to FSMC_ALE invalid            | 3T <sub>HCLK</sub> + 2 | -                      | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.